## SN8F27E60 Series

#### **USER'S MANUAL**

Version 2.1

SN8F27E65

SN8F27E64

SN8F27E62

**SN8F27E65L**

**SN8F27E64L**

SN8F27E63L

**SN8F27E62L**

### **SONIX 8-Bit Micro-Controller**

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of the part.

#### AMENDENT HISTORY

| Version | Date       | Description                                                                     |

|---------|------------|---------------------------------------------------------------------------------|

| VER 0.1 | Oct. 2009  | First issue.                                                                    |

| VER 0.2 | Dec. 2009  | Update electrical characteristic.                                               |

|         |            | 2. Modify development tool section.                                             |

| VER 0.3 | Dec. 2009  | Update electrical characteristic.                                               |

|         |            | 2. Modify UART section.                                                         |

| VER 0.4 | Jan. 2010  | Update electrical characteristic.                                               |

|         |            | 2. Add PB-Free part number.                                                     |

|         |            | 3. Add QFN package type.                                                        |

| VER 0.5 | Feb. 2010  | 1. Fix SN8F27E65LF pin 31/32 VDD name.                                          |

|         |            | 2. Modify Wafer Form part number as "S8F27E65W".                                |

| VER 1.0 | Jul. 2010  | Update electrical characteristic.                                               |

|         |            | 2. Modify MSP section.                                                          |

|         |            | 3. Modify QFN 4x4 package dimension.                                            |

| VER 1.1 | Jun. 2011  | Update ROM programming pin.                                                     |

|         |            | 2. Modify QFN 4x4 package dimension.                                            |

|         |            | 3. Add AVREFH pin name in SN8F27E64 and SN8F27E62.                              |

|         |            | 4. Modify SN8F27E65 starter-kit section.                                        |

|         |            | 5. Update electrical characteristic maximum rating.                             |

| VER 1.2 | Jul. 2011  | Add SDIP package type.                                                          |

| VER 1.3 | Jun. 2012  | Add the schematic of SN8F27E65 starter-kit.                                     |

| VER 1.4 | May 2013   | Modify ADC section.                                                             |

| VER 1.5 | Mar. 2014  | 1. Add SN8F27E63LJ part number.                                                 |

| VER 1.6 | Oct. 2014  | Modify ISP section.                                                             |

| VER 1.7 | Nov. 2014  | Modify QFN 5x5 package dimension.                                               |

| VER 1.8 | Jun. 2015  | Add Junction temperature specification in electrical characteristic section.    |

| VER 1.9 | July. 2015 | Modify Junction temperature specification in electrical characteristic section. |

| VER 2.0 | Jan. 2016  | Add asynchronous signal description in interrupt section.                       |

| VER 2.1 | May 2017   | Modify SN8F27E63L operating voltage in features selection table.                |

## **Table of Content**

| AMENDENT HISTORY                          |    |

|-------------------------------------------|----|

| PRODUCT OVERVIEW                          |    |

| 1.1 FEATURES                              |    |

| 1.2 SYSTEM BLOCK DIAGRAM                  |    |

| 1.3 PIN ASSIGNMENT                        | 11 |

| 1.4 PIN DESCRIPTIONS                      |    |

| 1.5 PIN CIRCUIT DIAGRAMS                  | 14 |

| CENTRAL PROCESSOR UNIT (CPU)              |    |

| 2.1 PROGRAM MEMORY (FLASH ROM)            | 16 |

| 2.1.1 RESET VECTOR (0000H)                |    |

| 2.1.2 INTERRUPT VECTOR (0008H~0014H)      |    |

| 2.1.3 LOOK-UP TABLE DESCRIPTION           |    |

| 2.1.4 JUMP TABLE DESCRIPTION              |    |

| 2.1.5 CHECKSUM CALCULATION                | 24 |

| 2.2 DATA MEMORY (RAM)                     |    |

| 2.2.1 SYSTEM REGISTER                     |    |

| 2.2.1.1 SYSTEM REGISTER TABLE             |    |

| 2.2.1.2 SYSTEM REGISTER DESCRIPTION       |    |

| 2.2.1.3 BIT DEFINITION of SYSTEM REGISTER |    |

| 2.2.2 ACCUMULATOR                         |    |

| 2.2.3 PROGRAM FLAG                        |    |

| 2.2.4 PROGRAM COUNTER                     |    |

| 2.2.5 H, L REGISTERS                      |    |

| 2.2.6 X REGISTERS                         |    |

| 2.2.7 Y, Z REGISTERS                      |    |

| 2.2.8 R REGISTER                          |    |

| 2.2.9 W REGISTERS                         |    |

| 2.3 ADDRESSING MODE                       |    |

| 2.3.1 IMMEDIATE ADDRESSING MODE           |    |

| 2.3.2 DIRECTLY ADDRESSING MODE            |    |

| 2.3.3 INDIRECTLY ADDRESSING MODE          |    |

| 2.4 STACK OPERATION                       |    |

| 2.4.1 OVERVIEW                            |    |

| 2.4.2 STACK POINTER                       |    |

| 2.4.3 STACK BUFFER                        |    |

| 2.4.5 STACK OPERATION EXAMPLE             |    |

| 2.5 CODE OPTION TABLE                     |    |

| 2.5.1 Fcpu Code Option                    |    |

| 2.5.2 Reset_Pin code option               |    |

| 2.5.3 Security code option                |    |

| 2.5.4 Noise Filter code option            |    |

| RESET                                     |    |

| 3.1 OVERVIEW                              |    |

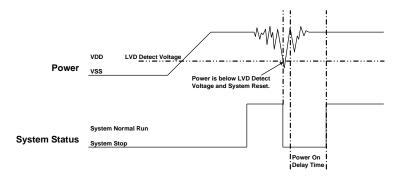

| 3.2 POWER ON RESET                        |    |

| 3.3 WATCHDOG RESET                        |    |

| 3.4 BROWN OUT RESET                       |    |

| 3.4.1 THE SYSTEM OPERATING VOLTAGE        |    |

|                                           |    |

| 3.4.2 LOW VOLTAGE DETECTOR (LVD)                    | 46 |

|-----------------------------------------------------|----|

| 3.4.3 BROWN OUT RESET IMPROVEMENT                   | 48 |

| 3.5 EXTERNAL RESET                                  |    |

| 3.6 EXTERNAL RESET CIRCUIT                          | 49 |

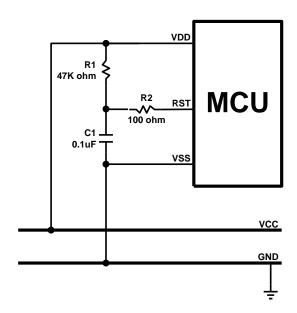

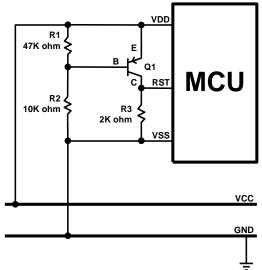

| 3.6.1 Simply RC Reset Circuit                       | 49 |

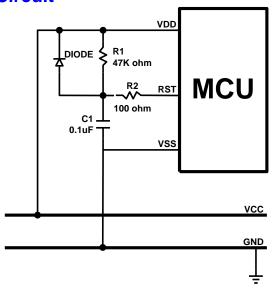

| 3.6.2 Diode & RC Reset Circuit                      | 50 |

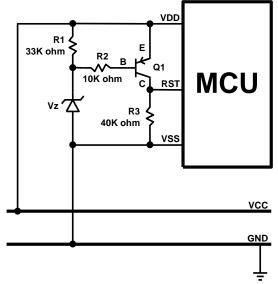

| 3.6.3 Zener Diode Reset Circuit                     | 50 |

| 3.6.4 Voltage Bias Reset Circuit                    | 51 |

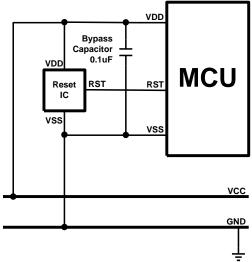

| 3.6.5 External Reset IC                             | 51 |

| 4 SYSTEM CLOCK                                      | 52 |

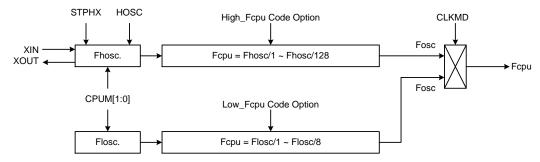

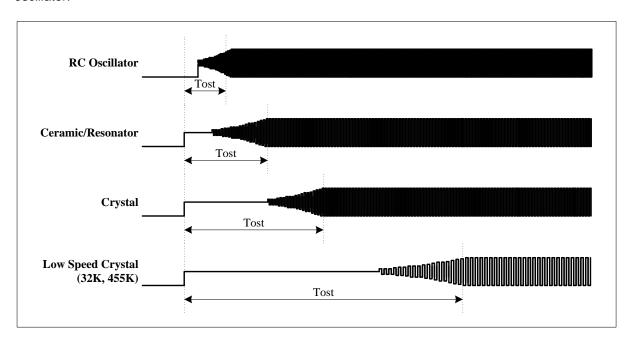

| 4.1 OVERVIEW                                        | 52 |

| 4.2 FCPU (INSTRUCTION CYCLE)                        | 52 |

| 4.3 NOISE FILTER                                    |    |

| 4.4 SYSTEM HIGH-SPEED CLOCK                         | 52 |

| 4.4.1 HIGH_CLK CODE OPTION                          |    |

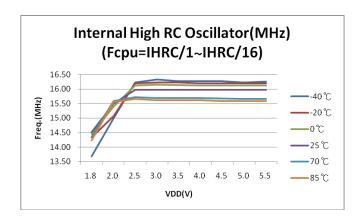

| 4.4.2 INTERNAL HIGH-SPEED OSCILLATOR RC TYPE (IHRC) | 53 |

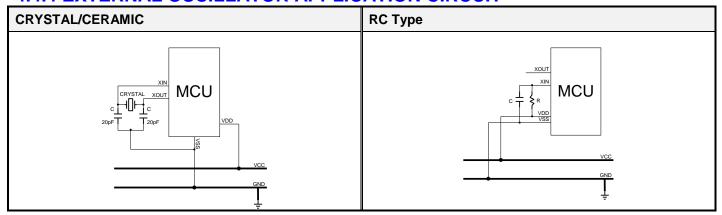

| 4.4.3 EXTERNAL HIGH-SPEED OSCILLATOR                |    |

| 4.4.4 EXTERNAL OSCILLATOR APPLICATION CIRCUIT       | 53 |

| 4.5 SYSTEM LOW-SPEED CLOCK                          |    |

| 4.6 OSCM REGISTER                                   | 54 |

| 4.7 SYSTEM CLOCK MEASUREMENT                        | 55 |

| 4.8 SYSTEM CLOCK TIMING                             | 55 |

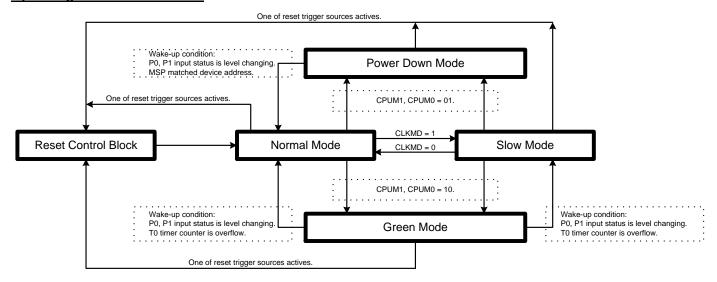

| <b>5</b> SYSTEM OPERATION MODE                      |    |

| 5.1 OVERVIEW                                        |    |

| 5.2 NORMAL MODE                                     |    |

| 5.3 SLOW MODE                                       | 60 |

| 5.4 POWER DOWN MDOE                                 | 60 |

| 5.5 GREEN MODE                                      |    |

| 5.6 OPERATING MODE CONTROL MACRO                    | 62 |

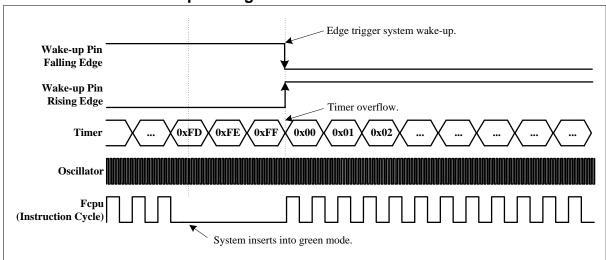

| 5.7 WAKEUP                                          | 63 |

| 5.7.1 OVERVIEW                                      | 63 |

| 5.7.2 WAKEUP TIME                                   | 63 |

| 5.7.3 P1W WAKEUP CONTROL REGISTER                   | 64 |

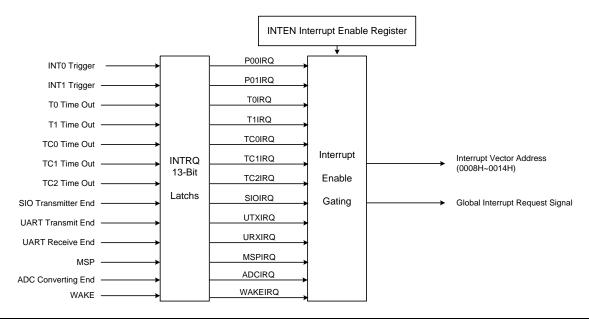

| 6 INTERRUPT                                         | 65 |

| 6.1 OVERVIEW                                        |    |

| 6.2 Interrupt Operation                             | 66 |

| 6.3 INTEN INTERRUPT ENABLE REGISTER                 | 67 |

| 6.4 INTRQ INTERRUPT REQUEST REGISTER                |    |

| 6.5 GIE GLOBAL INTERRUPT OPERATION                  | 69 |

| 6.6 EXTERNAL INTERRUPT OPERATION (INT0~INT1)        | 70 |

| 6.7 T0 INTERRUPT OPERATION                          |    |

| 6.8 TC0 INTERRUPT OPERATION                         | 72 |

| 6.9 TC1 INTERRUPT OPERATION                         |    |

| 6.10 TC2 INTERRUPT OPERATION                        |    |

| 6.11 T1 INTERRUPT OPERATION                         |    |

| 6.12 ADC INTERRUPT OPERATION                        |    |

| 6.13 SIO INTERRUPT OPERATION                        |    |

| 6.14 UART INTERRUPT OPERATION                       |    |

| 6.15 MULTI-INTERRUPT OPERATION                      |    |

| <b>Ϡ</b> I/O PORT                                   |    |

| 7.1 OVERVIEW                                        |    |

| 7.2 I/O PORT MODE                                   | 81 |

|   | 7.3 I/O PULL UP REGISTER                        | 82  |

|---|-------------------------------------------------|-----|

|   | 7.4 I/O PORT DATA REGISTER                      |     |

|   | 7.5 PORT 4, PORT 5 ADC SHARE PIN                | 84  |

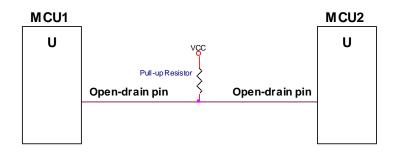

|   | 7.6 OPEN-DRAIN REGISTER                         | 86  |

| 8 | TIMERS                                          |     |

|   | 8.1 WATCHDOG TIMER                              | 87  |

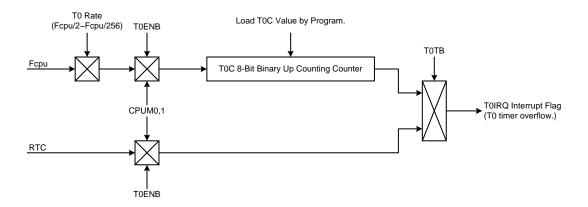

|   | 8.2 TO 8-BIT BASIC TIMER                        | 89  |

|   | 8.2.1 OVERVIEW                                  | 89  |

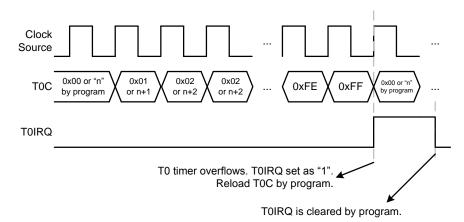

|   | 8.2.2 T0 Timer Operation                        | 90  |

|   | 8.2.3 T0M MODE REGISTER                         |     |

|   | 8.2.4 TOC COUNTING REGISTER                     |     |

|   | 8.2.5 TO TIMER OPERATION EXPLAME                | 92  |

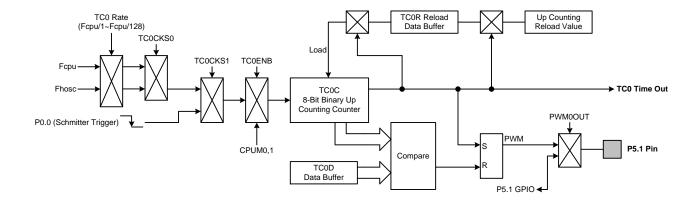

|   | 8.3 TC0 8-BIT TIMER/COUNTER                     | 93  |

|   | 8.3.1 OVERVIEW                                  | 93  |

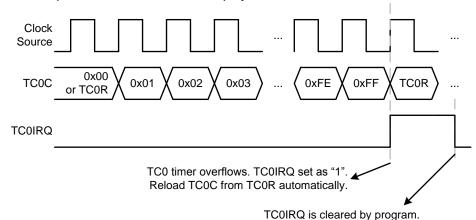

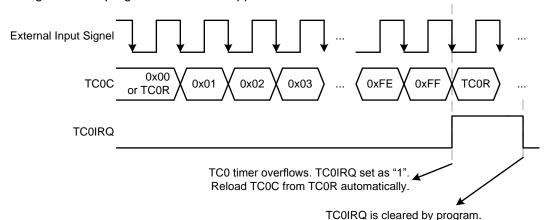

|   | 8.3.2 TC0 TIMER OPERATION                       | 94  |

|   | 8.3.3 TC0M MODE REGISTER                        |     |

|   | 8.3.4 TC0C COUNTING REGISTER                    |     |

|   | 8.3.5 TC0R AUTO-RELOAD REGISTER                 | 96  |

|   | 8.3.6 TC0D PWM DUTY REGISTER                    | 96  |

|   | 8.3.7 TC0 EVENT COUNTER                         | 97  |

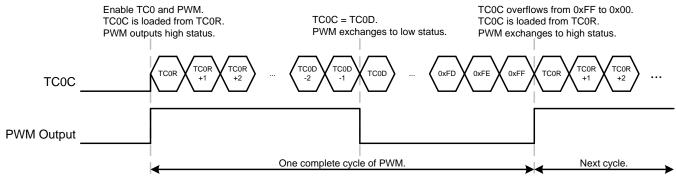

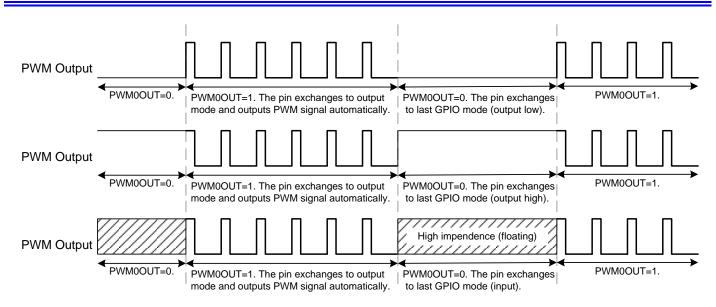

|   | 8.3.8 PULSE WIDTH MODULATION (PWM)              |     |

|   | 8.3.9 TC0 TIMER OPERATION EXPLAME               |     |

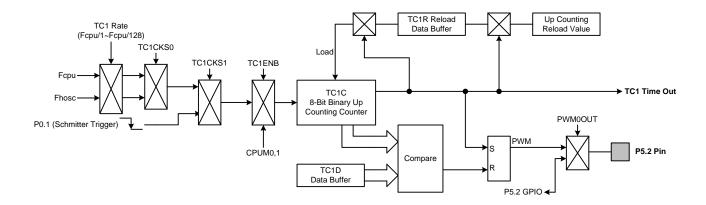

|   | 8.4 TC1 8-BIT TIMER/COUNTER                     |     |

|   | 8.4.1 OVERVIEW                                  |     |

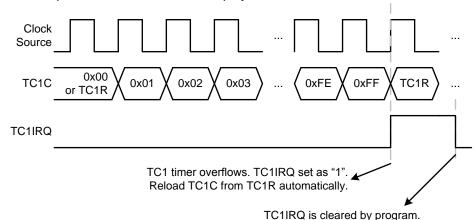

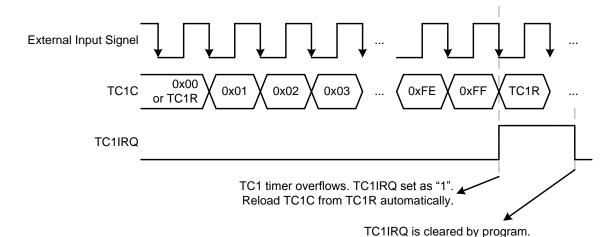

|   | 8.4.2 TC1 TIMER OPERATION                       |     |

|   | 8.4.3 TC1M MODE REGISTER                        |     |

|   | 8.4.4 TC1C COUNTING REGISTER                    |     |

|   | 8.4.5 TC1R AUTO-RELOAD REGISTER                 |     |

|   | 8.4.6 TC1D PWM DUTY REGISTER                    |     |

|   | 8.4.7 TC1 EVENT COUNTER                         |     |

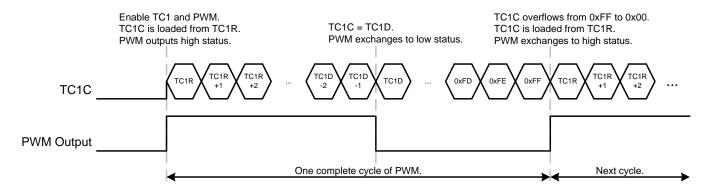

|   | 8.4.8 PULSE WIDTH MODULATION (PWM)              |     |

|   | 8.4.9 TC1 TIMER OPERATION EXPLAME               |     |

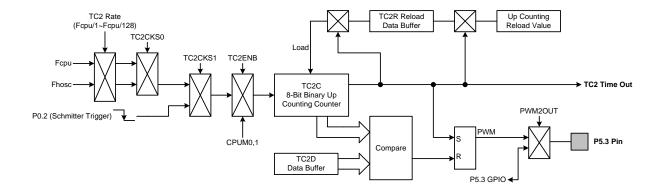

|   | 8.5 TC2 8-BIT TIMER/COUNTER                     | 107 |

|   | 8.5.1 OVERVIEW                                  |     |

|   | 8.5.2 TC2 TIMER OPERATION                       |     |

|   | 8.5.3 TC2M MODE REGISTER                        |     |

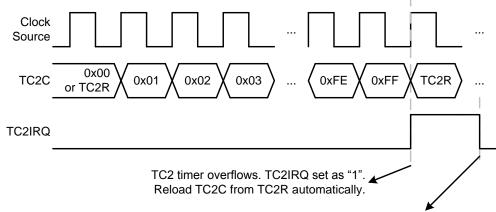

|   | 8.5.4 TC2C COUNTING REGISTER                    |     |

|   | 8.5.5 TC2R AUTO-RELOAD REGISTER                 |     |

|   | 8.5.6 TC2D PWM DUTY REGISTER                    |     |

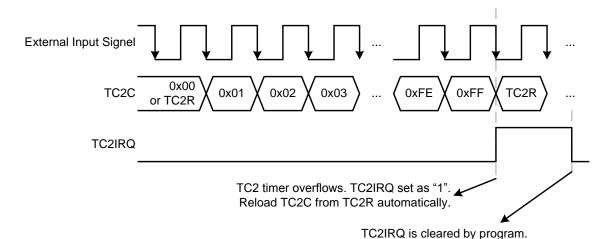

|   | 8.5.7 TC2 EVENT COUNTER                         |     |

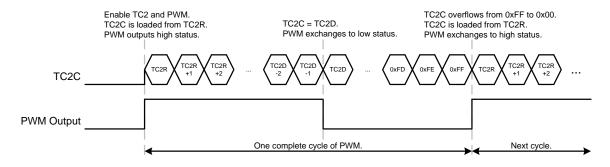

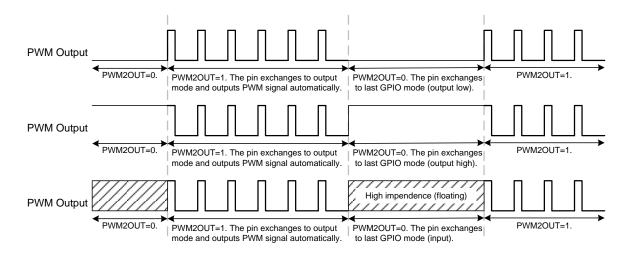

|   | 8.5.8 PULSE WIDTH MODULATION (PWM)              |     |

|   | 8.5.9 TC2 TIMER OPERATION EXPLAME               |     |

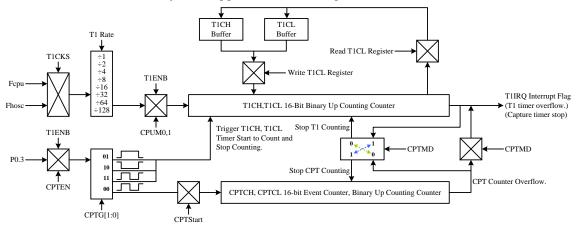

|   | 8.6 T1 16-BIT TIMER WITH CAPTURE TIMER FUNCTION |     |

|   | 8.6.1 OVERVIEW                                  |     |

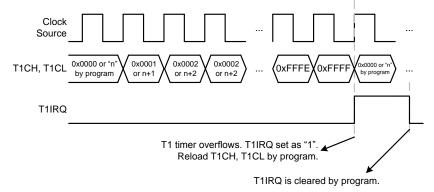

|   | 8.6.2 T1 TIMER OPERATION                        |     |

|   | 8.6.3 T1M MODE REGISTER                         |     |

|   | 8.6.4 T1CH, T1CL 16-bit COUNTING REGISTERS      |     |

|   | 8.6.5 T1 CPATURE TIMER                          |     |

|   | 8.6.5.1 Capture Timer                           |     |

|   | 8.6.5.2 High Pulse Width Measurement            |     |

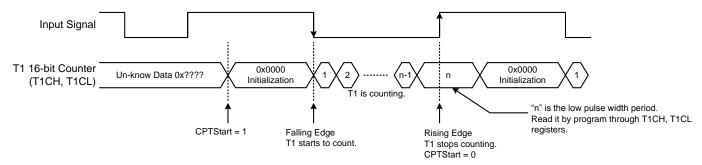

|   | 8.6.5.3 Low Pulse Width Measurement             |     |

|   | 8.6.5.4 Input Cycle Measurement                 | 119 |

| 8.6.6 CAPTURE TIMER CONTROL REGISTERS                 | 119 |

|-------------------------------------------------------|-----|

| 8.6.7 T1 TIMER OPERATION EXPLAME                      | 120 |

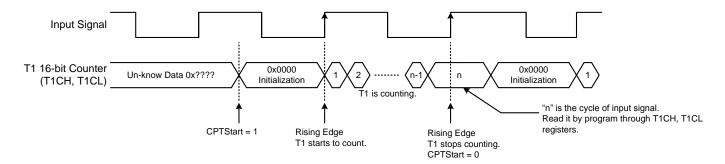

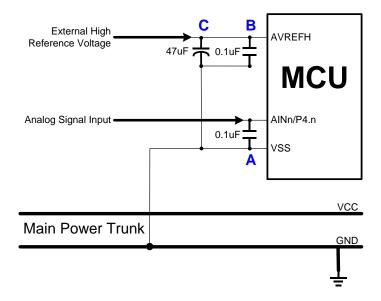

| <b>9</b> 12 CHANNEL ANALOG TO DIGITAL CONVERTER (ADC) | 123 |

| 9.1 OVERVIEW                                          |     |

| 9.2 ADC MODE REGISTER                                 |     |

| 9.3 ADC DATA BUFFER REGISTERS                         |     |

| 9.4 ADC OPERATION DESCRIPTION AND NOTIC               |     |

| 9.4.1 ADC SIGNAL FORMAT                               |     |

| 9.4.2 ADC CONVERTING TIME                             |     |

| 9.4.3 ADC PIN CONFIGURATION                           |     |

| 9.4.4 ADC OPERATION EXAMLPE                           |     |

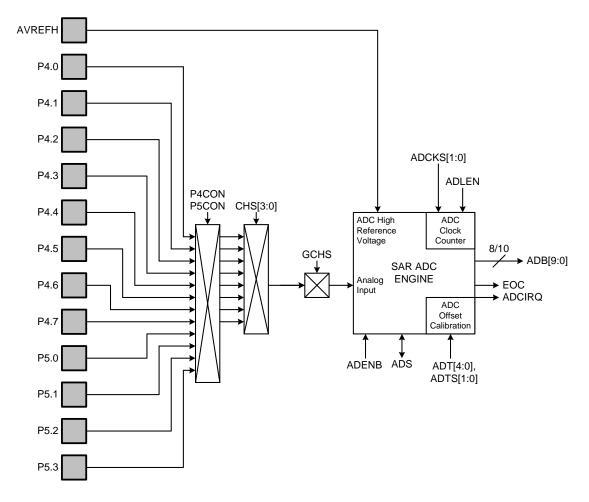

| 9.5 ADC APPLICATION CIRCUIT                           |     |

| 10 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UAR   |     |

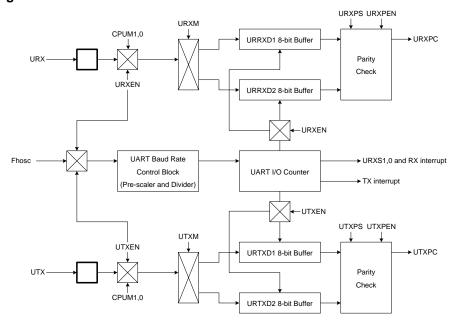

| 10.1 OVERVIEW                                         | 131 |

| 10.2 UART OPERATION                                   |     |

| 10.3 UART BAUD RATE                                   |     |

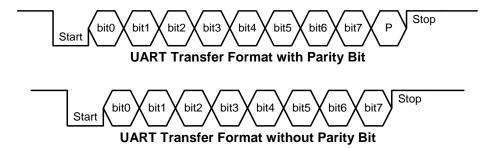

| 10.4 UART transfer format                             |     |

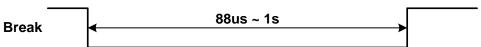

| 10.5 BREAK POCKET                                     |     |

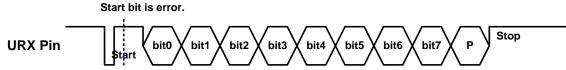

| 10.6 ABNORMAL POCKET                                  |     |

| 10.7 UART RECEIVER CONTROL REGISTER                   |     |

| 10.8 UART TRANSMITTER CONTROL REGISTER                |     |

| 10.9 UART DATA BUFFER                                 |     |

| 10.10 UART OPERATION EXAMLPE                          |     |

| 11 SERIAL INPUT/OUTPUT TRANSCEIVER (SIO)              | 140 |

| 11.1 OVERVIEW                                         |     |

| 11.2 SIO OPERATION                                    |     |

| 11.3 SIOM MODE REGISTER                               |     |

| 11.4 SIOB DATA BUFFER                                 |     |

| 11.5 SIOR REGISTER DESCRIPTION                        |     |

| 12 MAIN SERIAL PORT (MSP)                             |     |

| 12.1 OVERVIEW                                         |     |

| 12.2 MSP STATUS REGISTER                              |     |

| 12.3 MSP MODE REGISTER 1                              |     |

| 12.4 MSP MODE REGISTER 2                              |     |

| 12.5 MSP MSPBUF REGISTER                              |     |

| 12.6 MSP MSPADR REGISTER                              |     |

| 12.7 SLAVE MODE OPERATION                             |     |

| 12.7.1 Addressing                                     |     |

| 12.7.2 Slave Receiving                                |     |

| 12.7.3 Slave Transmission                             |     |

| 12.7.4 General Call Address                           |     |

| 12.7.5 Slave Wake up                                  |     |

| 12.8 MASTER MODE                                      |     |

| 12.8.1 Mater Mode Support                             |     |

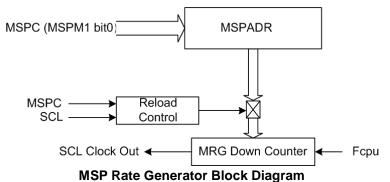

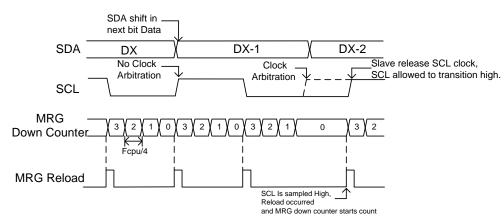

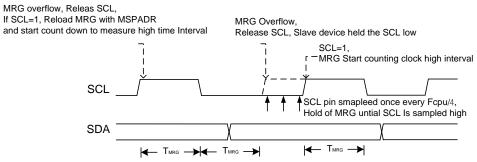

| 12.8.2 MSP Nate Generator                             |     |

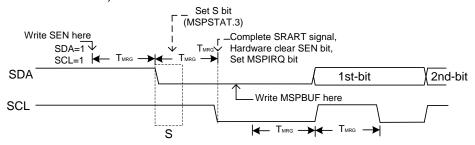

| 12.8.3 MSP Mater START Condition                      |     |

| 12.8.3.1 WCOL Status Flag                             |     |

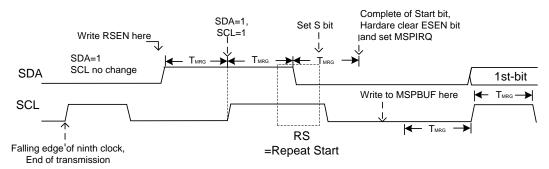

| 12.8.4 MSP Master mode Repeat START Condition         |     |

| 12.8.4.1 WCOL Status Flag                             |     |

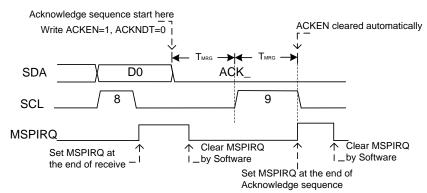

| 12.8.5 Acknowledge Sequence Timing                    |     |

| 12.8.5.1 WCOL Status Flag                             |     |

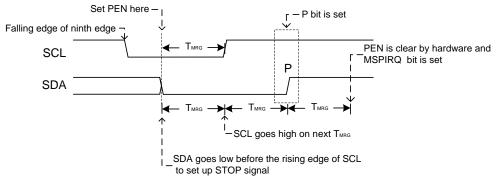

| 12.8.6 STOP Condition Timing.                         |     |

|    |                                                           | _   |

|----|-----------------------------------------------------------|-----|

|    | 12.8.6.1 WCOL Status Flag                                 | 156 |

|    | 12.8.7 Clock Arbitration                                  |     |

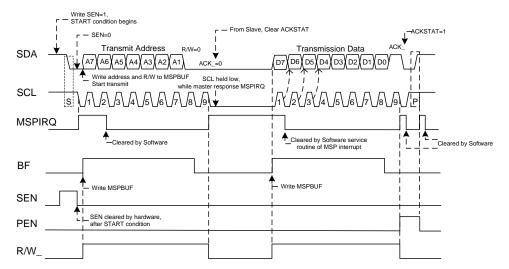

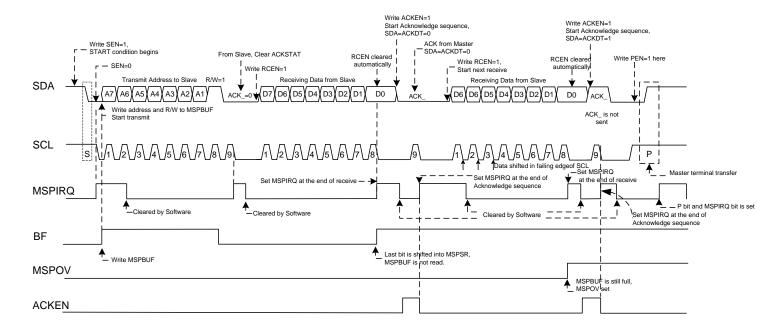

|    | 12.8.8 Master Mode Transmission                           | 157 |

|    | 12.8.8.1 BF Status Flag                                   | 157 |

|    | 12.8.8.2 WCOL Flag                                        | 157 |

|    | 12.8.8.3 ACKSTAT Status Flag                              | 157 |

|    | 12.8.9 Master Mode Receiving                              | 158 |

|    | 12.8.9.1 BF Status Flag                                   | 158 |

|    | 12.8.9.2 MSPOV Flag                                       | 158 |

|    | 12.8.9.3 WCOL Flag                                        |     |

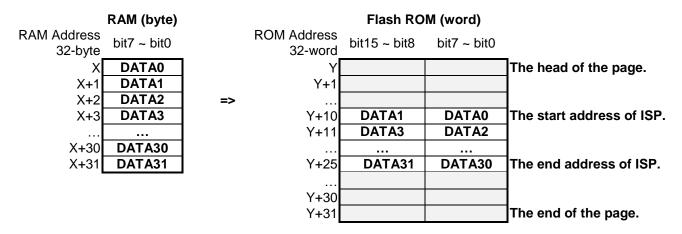

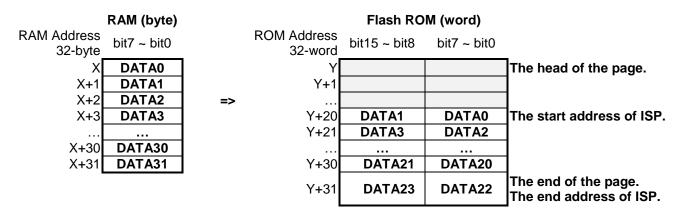

| 13 | IN SYSTEM PROGRAM FLASH ROM                               | 159 |

|    | 13.1 OVERVIEW                                             |     |

|    | 13.2 ISP FLASH ROM ERASE OPERATION                        |     |

|    | 13.3 ISP FLASH ROM PROGRAM OPERATION                      |     |

|    | 13.4 ISP PROGRAM/ERASE CONTROL REGISTER                   | 164 |

|    | 13.5 ISP ROM ADDRESS REGISTER                             |     |

|    | 13.6 ISP RAM ADDRESS REGISTER                             |     |

|    | 13.7 ISP ROM PROGRAMMING LENGTH REGISTER                  |     |

|    | INSTRUCTION TABLE                                         |     |

|    | ELECTRICAL CHARACTERISTIC                                 |     |

|    | 15.1 ABSOLUTE MAXIMUM RATING                              |     |

|    | 15.2 ELECTRICAL CHARACTERISTIC                            |     |

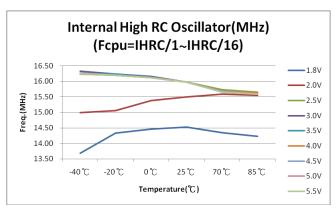

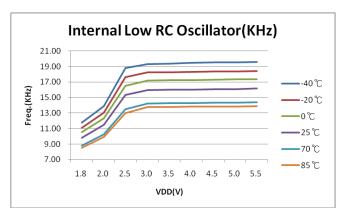

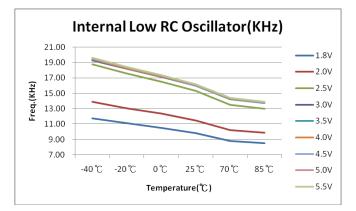

|    | 15.3 CHARACTERISTIC GRAPHS                                |     |

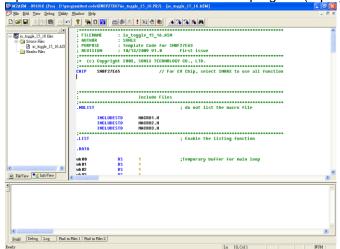

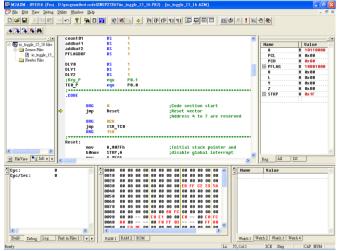

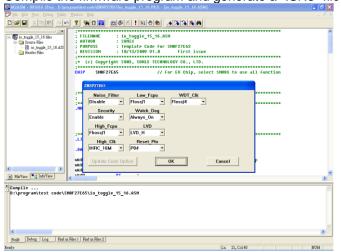

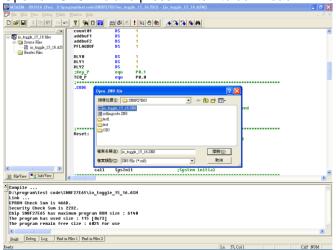

|    | DEVELOPMENT TOOL                                          |     |

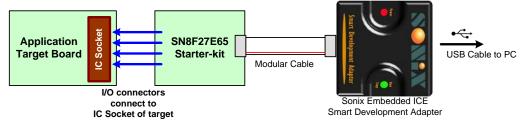

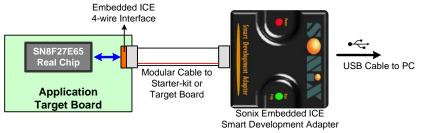

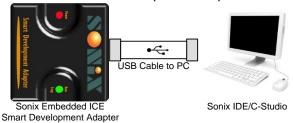

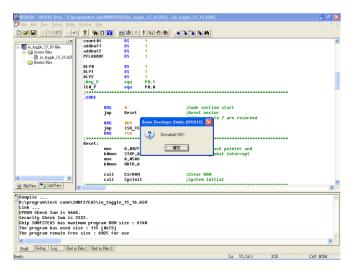

|    | 16.1 Smart Development Adapter                            |     |

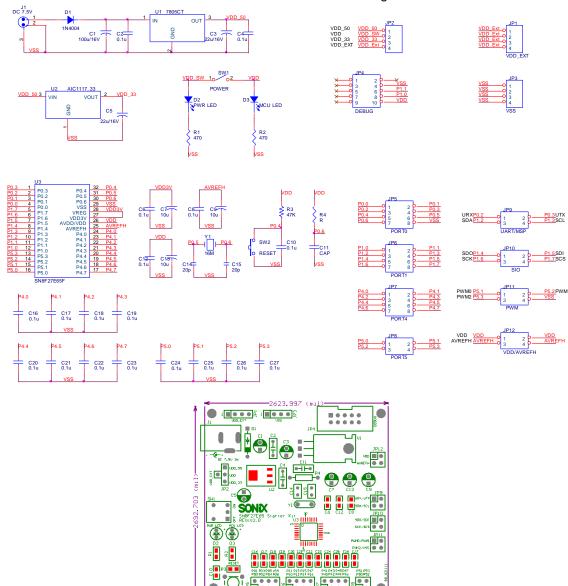

|    | 16.2 SN8F27E65 Starter-kit                                |     |

|    | 16.3 EMULATOR/DEBUGGER INSTALLATION                       |     |

|    | 16.4 PROGRAMMER INSTALLATION                              |     |

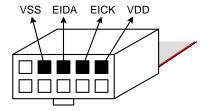

|    | ROM PROGRAMMING PIN                                       |     |

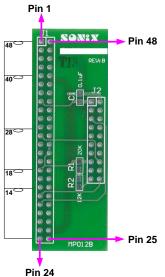

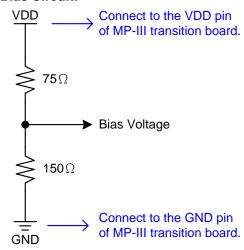

|    | 17.1 MP-III WRITER TRANSITION BOARD SOCKET PIN ASSIGNMENT |     |

|    | 17.2 MP-III WRITER PROGRAMMING PIN MAPPING:               |     |

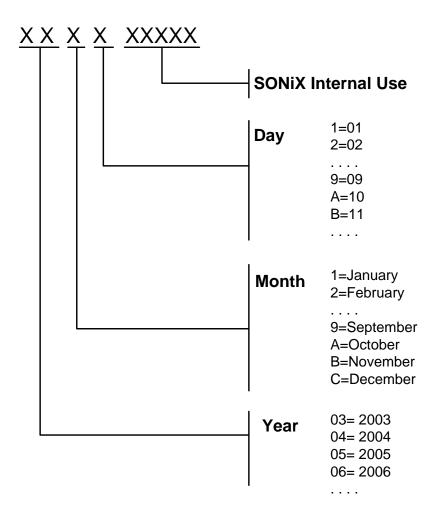

|    | MARKING DEFINITION                                        |     |

|    | 18.1 INTRODUCTION                                         |     |

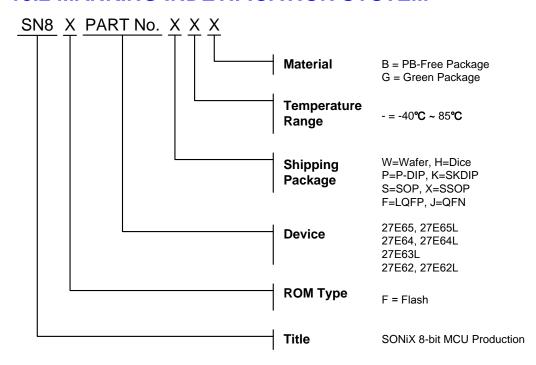

|    | 18.2 MARKING INDETIFICATION SYSTEM                        |     |

|    |                                                           |     |

|    | 18.3 MARKING EXAMPLE                                      |     |

|    | 18.4 DATECODE SYSTEM                                      |     |

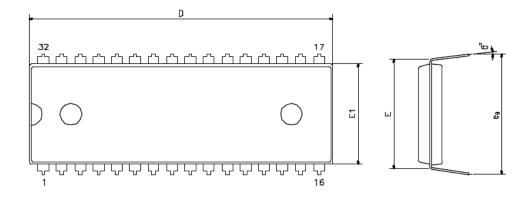

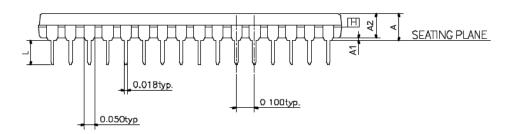

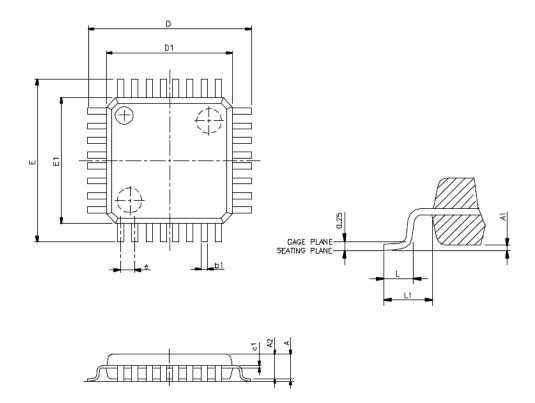

|    | PACKAGE INFORMATION                                       |     |

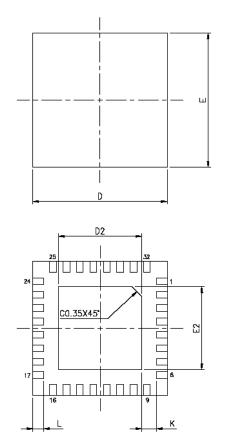

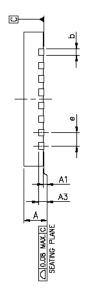

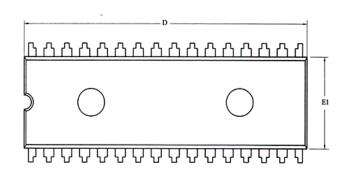

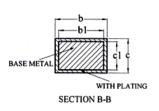

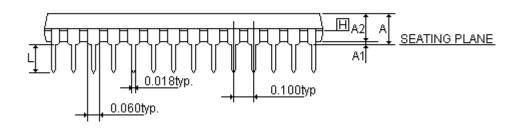

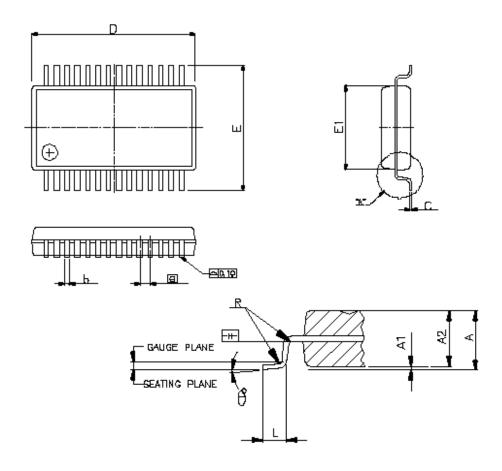

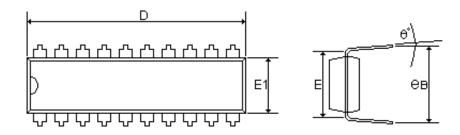

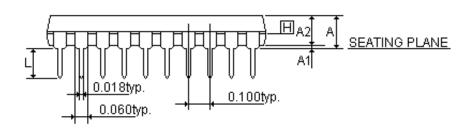

|    | 19.1 P-DIP 32 PIN                                         |     |

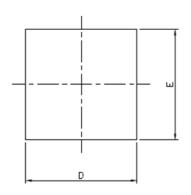

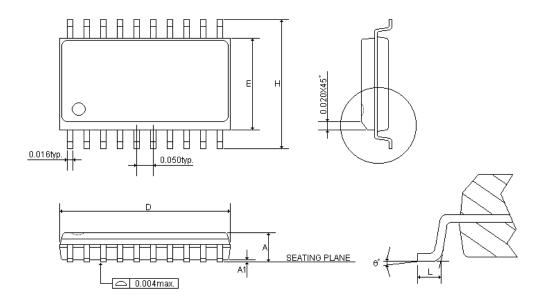

|    | 19.2 LQFP 32 PIN                                          |     |

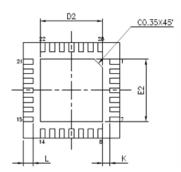

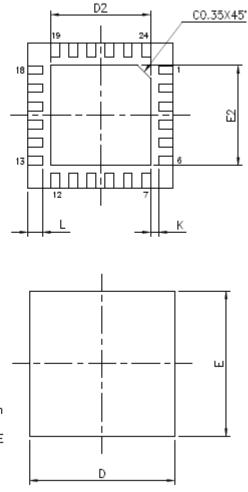

|    | 19.3 QFN 5x5 32 PIN                                       |     |

|    | 19.4 S-DIP 32 PIN                                         |     |

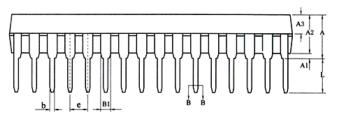

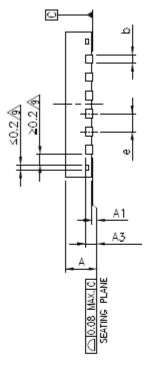

|    | 19.5 SK-DIP 28 PIN                                        |     |

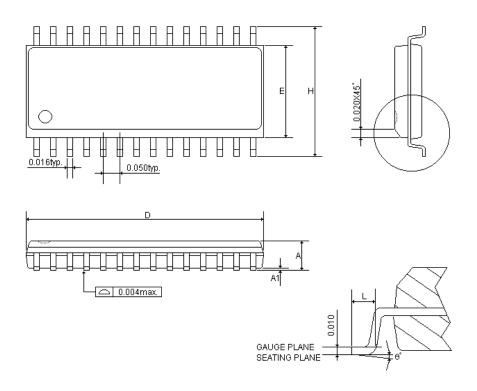

|    | 19.6 SOP 28 PIN                                           |     |

|    | 19.7 SSOP 28 PIN                                          |     |

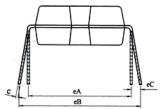

|    | 19.8 QFN 4x4 28 PIN                                       |     |

|    | 19.9 QFN 4x4 24 PIN                                       |     |

|    | 19.10 P-DIP 20 PIN                                        |     |

|    | 19.11 SOP 20 PIN                                          | 193 |

## PRODUCT OVERVIEW

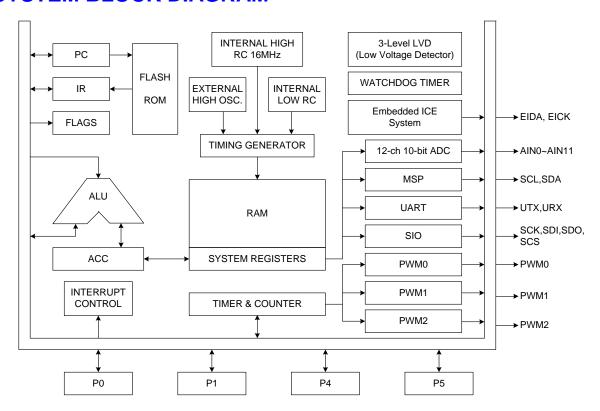

SN8F27E60 series 8-bit micro-controller is a new series production applied advanced semiconductor technology to implement flash ROM architecture. Under flash ROM platform, SN8F27E60 builds in in-system-programming (ISP) function extending to EEPROM emulation and Embedded ICE function. It offers high performance 12-ch 10-bit ADC, 3-set individual programmable PWMs, 3-type serial interfaces and flexible operating modes. Powerful functionality, high reliability and low power consumption can apply to AC power application and battery level application easily.

#### 1.1 FEATURES

#### **Memory configuration**

Flash ROM size: 6K x 16 bits. Including EEROM emulation. (In system programming) RAM size: 512 x 8 bits.

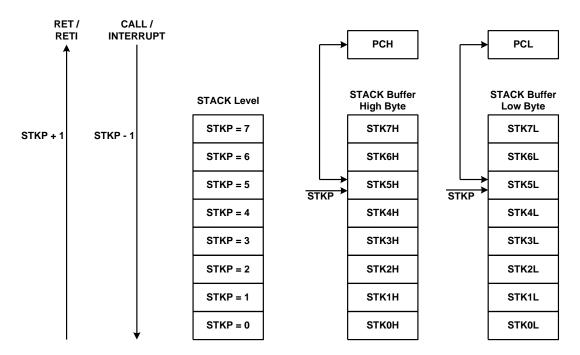

- 8 levels stack buffer.

- 13 interrupt sources

11 internal interrupts: T0, TC0, TC1, TC2, T1, ADC, SIO, MSP, UTX(UART TX), URX(UART RX), WAKE 2 external interrupts: INT0, INT1

Multi-interrupt vector structure.

Each of interrupt sources has a unique interrupt vector. ◆ Serial Interface: SIO, UART, MSP

#### I/O pin configuration

Bi-directional: P0, P1, P4, P5. Wakeup: P0, P1 level change. Pull-up resisters: P0, P1, P4, P5. External interrupt: P0.0, P0.1 ADC input pin: AIN0~AIN11.

#### Fcpu (Instruction cycle)

Fcpu = Fhosc/1, Fhosc/2, Fhosc/4, Fhosc/8, Fhosc/16, Fhosc/32, Fhosc/64, Fhosc/128

- On chip watchdog timer and clock source

- 1.8V/2.4V/3.3V 3-level LVD with trim.

#### **Powerful instructions**

Instruction's length is one word. Most of instructions are one cycle only. All ROM area JMP instruction. All ROM area lookup table function (MOVC). ♦ Four 8-bit timer. (T0, TC0, TC1, TC2).

T0: Basic timer.

TC0: Timer/counter/PWM0. TC1: Timer/counter/PWM1. TC2: Timer/counter/PWM2

- ♦ 3 channel duty/cycle programmable PWM to Generate PWM, Buzzer and IR carrier signals. (PWM0~2).

- ◆ One 16-bit timer (T1) with capture timer function.

- 12-channel 10-bit SAR ADC.

- Build in Embedded ICE function.

- ♦ Four system clocks

External high clock: RC type up to 10MHz External high clock: Crystal type up to 16MHz Internal high clock: RC type 16MHz Internal low clock: RC type 16KHz

♦ Four operating modes

Normal mode: Both high and low clock active

Slow mode: Low clock only

Sleep mode: Both high and low clock stop Green mode: Periodical wakeup by timer

♦ Package (Chip form support)

PDIP 32 pin LQFP 32 pin QFN 32 pin SDIP 32 pin SKDIP 28 pin SOP 28 pin SSOP 28 pin QFN 28 pin QFN 24 pin DIP 20 pin SOP 20 pin

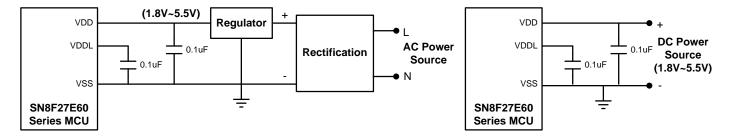

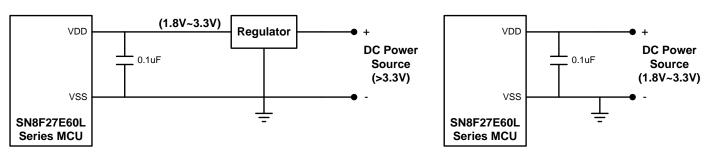

SN8F27E60 series micro-controller includes two types for different power types.

For AC power type (alternating current power source) and DC high voltage power ( $\leq$ 5.5V), the power pin has VDD and VDDL. VDD pin is connect to DC power source from DC-DC inverter or regulator and connects a 0.1uF capacitor to VSS pin (ground). VDDL is internal power terminal, not connect with power source, and only connects a 0.1uF capacitor to VSS pin (ground). This pin assignment has high power noise immunity, but the static current is larger. The application field is household, motor control...

For DC power type (battery power source), the power pin is VDD. VDD pin is connect to DC power source from battery and connects a 0.1uF capacitor to VSS pin (ground). This pin assignment has low power noise immunity, but the static current is very low. The application field is portable application...

#### Features Selection Table SN8F27E60 Series

| 0.10. 2. 200 00.100 |       |     |       |                     |     |      |       |     |      |     |         |                         |                      |                                     |

|---------------------|-------|-----|-------|---------------------|-----|------|-------|-----|------|-----|---------|-------------------------|----------------------|-------------------------------------|

| CHIP                | ROM   | RAM | Stack | Timer               | 1/0 | PWM  | ADC   | SIO | UART | MSP | Ext.INT | ISP/<br>Embedded<br>ICE | Operating<br>Voltage | Package                             |

| SN8F27E65           | 6K*16 | 512 | 8     | 8-bit*4<br>16-bit*1 | 27  | 3-ch | 12-ch | V   | V    | V   | 2       | V                       | 1.8V~5.5V            | DIP32<br>LQFP32<br>QFN32<br>SDIP32  |

| SN8F27E64           | 6K*16 | 512 | 8     | 8-bit*4<br>16-bit*1 | 25  | 3-ch | 11-ch | V   | V    | ٧   | 2       | V                       | 1.8V~5.5V            | SKDIP28<br>SOP28<br>SSOP28<br>QFN28 |

| SN8F27E62           | 6K*16 | 512 | 8     | 8-bit*4<br>16-bit*1 | 17  | 3-ch | 9-ch  | -   | V    | -   | 1       | V                       | 1.8V~5.5V            | DIP20<br>SOP20                      |

#### SN8F27E60L Series

| CHIP       | ROM   | RAM | Stack | Timer               | 1/0 | PWM  | ADC   | SIO | UART | MSP | Ext.INT | ISP/<br>Embedded<br>ICE | Operating<br>Voltage | Package                             |

|------------|-------|-----|-------|---------------------|-----|------|-------|-----|------|-----|---------|-------------------------|----------------------|-------------------------------------|

| SN8F27E65L | 6K*16 | 512 | 8     | 8-bit*4<br>16-bit*1 | 27  | 3-ch | 12-ch | V   | V    | ٧   | 2       | V                       | 1.8V~3.3V            | DIP32<br>LQFP32<br>QFN32<br>SDIP32  |

| SN8F27E64L | 6K*16 | 512 | 8     | 8-bit*4<br>16-bit*1 | 25  | 3-ch | 11-ch | V   | V    | ٧   | 2       | V                       | 1.8V~3.3V            | SKDIP28<br>SOP28<br>SSOP28<br>QFN28 |

| SN8F27E63L | 6K*16 | 512 | 8     | 8-bit*4<br>16-bit*1 | 21  | 3-ch | 8-ch  | ٧   | V    | V   | 2       | V                       | 1.8V~3.3V            | QFN24                               |

| SN8F27E62L | 6K*16 | 512 | 8     | 8-bit*4<br>16-bit*1 | 17  | 3-ch | 9-ch  | -   | V    | -   | 1       | V                       | 1.8V~3.3V            | DIP20<br>SOP20                      |

#### 1.2 SYSTEM BLOCK DIAGRAM

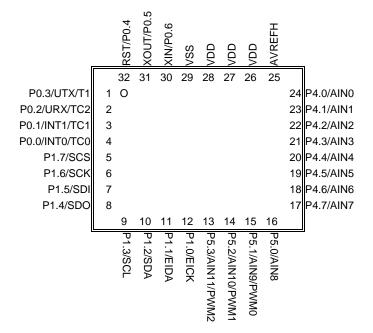

#### 1.3 PIN ASSIGNMENT

- SN8F27E65P (AC field, DIP 32 Pin):

- SN8F27E65U (AC field, SDIP 32 Pin):

|               | <u> </u> |   |    |                  |

|---------------|----------|---|----|------------------|

| VSS           | 1        | U | 32 | VDDL             |

| XIN/P0.6      | 2        |   | 31 | VDDL             |

| XOUT/P0.5     | 3        |   | 30 | VDD              |

| RST/P0.4      | 4        |   | 29 | AVREFH           |

| P0.3/UTX/T1   | 5        |   | 28 | P4.0/AIN0        |

| P0.2/URX/TC2  | 6        |   | 27 | P4.1/AIN1        |

| P0.1/INT1/TC1 | 7        |   | 26 | P4.2/AIN2        |

| P0.0/INT0/TC0 | 8        |   | 25 | P4.3/AIN3        |

| P1.7/SCS      | 9        |   | 24 | P4.4/AIN4        |

| P1.6/SCK      | 10       |   | 23 | P4.5/AIN5        |

| P1.5/SDI      | 11       |   | 22 | P4.6/AIN6        |

| P1.4/SDO      | 12       |   | 21 | P4.7/AIN7        |

| P1.3/SCL      | 13       |   | 20 | P5.0/AIN8        |

| P1.2/SDA      | 14       |   | 19 | P5.1/AIN9/PWM0   |

| P1.1/EIDA     | 15       |   | 18 | P5.2/AIN10/PWM1  |

| P1 0/FICK     | 16       |   | 17 | P5 3/AIN11/PW/M2 |

- SN8F27E65LP (DC field, DIP 32 Pin):

- SN8F27E65LU (DC field, SDIP 32 Pin):

|               | _ (= - |   | ,  |                 |

|---------------|--------|---|----|-----------------|

| VSS           | 1      | U | 32 | VDD             |

| XIN/P0.6      | 2      |   | 31 | VDD             |

| XOUT/P0.5     | 3      |   | 30 | VDD             |

| RST/P0.4      | 4      |   | 29 | AVREFH          |

| P0.3/UTX/T1   | 5      |   | 28 | P4.0/AIN0       |

| P0.2/URX/TC2  | 6      |   | 27 | P4.1/AIN1       |

| P0.1/INT1/TC1 | 7      |   | 26 | P4.2/AIN2       |

| P0.0/INT0/TC0 | 8      |   | 25 | P4.3/AIN3       |

| P1.7/SCS      | 9      |   | 24 | P4.4/AIN4       |

| P1.6/SCK      | 10     |   | 23 | P4.5/AIN5       |

| P1.5/SDI      | 11     |   | 22 | P4.6/AIN6       |

| P1.4/SDO      | 12     |   | 21 | P4.7/AIN7       |

| P1.3/SCL      | 13     |   | 20 | P5.0/AIN8       |

| P1.2/SDA      | 14     |   | 19 | P5.1/AIN9/PWM0  |

| P1.1/EIDA     | 15     |   | 18 | P5.2/AIN10/PWM1 |

| P1.0/EICK     | 16     |   | 17 | P5.3/AIN11/PWM2 |

|               |        |   |    |                 |

- SN8F27E65F (AC field, LQFP 32 Pin):

- SN8F27E65J (AC field, QFN 5x5 32 Pin):

- OUT/P0.5 RST/P0.4 IN/P0.6 AVREFH 32 31 30 29 28 27 26 25 24 P4.0/AIN0 P0.3/UTX/T1 1 0 23 P4.1/AIN1 P0.2/URX/TC2 2 P0.1/INT1/TC1 22 P4.2/AIN2 3 21 P4.3/AIN3 P0.0/INT0/TC0 4 20 P4.4/AIN4 P1.7/SCS P1.6/SCK 19 P4.5/AIN5 18 P4.6/AIN6 P1.5/SDI 7 P1.4/SDO 17 P4.7/AIN7 8 10 P1.1/EIDA P1.0/EICK P5.3/AIN11/PWM2 P5.2/AIN10/PWM1 P5.1/AIN9/PWM0 P5.0/AIN8 .2/SDA

- SN8F27E65LF (DC field, LQFP 32 Pin):

- SN8F27E65LJ (DC field, QFN 5x5 32 Pin):

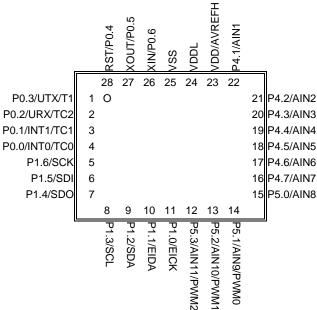

- SN8F27E64K (AC field, SKDIP 28 Pin):

- SN8F27E64S (AC field, SOP 28 Pin):

- SN8F27E64X (AC field, SSOP 28 Pin):

| 0             | 7  | , |    | · -• · ···/·    |

|---------------|----|---|----|-----------------|

| VSS           | 1  | U | 28 | VDDL            |

| XIN/P0.6      | 2  |   | 27 | VDD/AVREFH      |

| XOUT/P0.5     | 3  |   | 26 | P4.1/AIN1       |

| RST/P0.4      | 4  |   | 25 | P4.2/AIN2       |

| P0.3/UTX/T1   | 5  |   | 24 | P4.3/AIN3       |

| P0.2/URX/TC2  | 6  |   | 23 | P4.4/AIN4       |

| P0.1/INT1/TC1 | 7  |   | 22 | P4.5/AIN5       |

| P0.0/INT0/TC0 | 8  |   | 21 | P4.6/AIN6       |

| P1.6/SCK      | 9  |   | 20 | P4.7/AIN7       |

| P1.5/SDI      | 10 |   | 19 | P5.0/AIN8       |

| P1.4/SDO      | 11 |   | 18 | P5.1/AIN9/PWM0  |

| P1.3/SCL      | 12 |   | 17 | P5.2/AIN10/PWM1 |

| P1.2/SDA      | 13 |   | 16 | P5.3/AIN11/PWM2 |

| P1.1/EIDA     | 14 |   | 15 | P1.0/EICK       |

|               |    |   |    |                 |

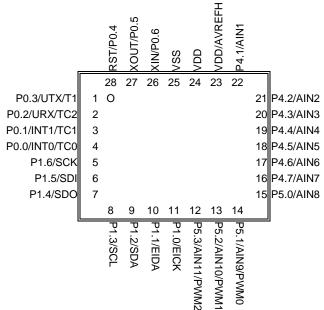

- SN8F27E64LK (DC field, SKDIP 28 Pin):

- SN8F27E64LS (DC field, SOP 28 Pin):

- SN8F27E64LX (DC field, SSOP 28 Pin):

| VSS           | 1  | U | 28 | VDD             |

|---------------|----|---|----|-----------------|

| XIN/P0.6      | 2  |   | 27 | VDD/AVREFH      |

| XOUT/P0.5     | 3  |   | 26 | P4.1/AIN1       |

| RST/P0.4      | 4  |   | 25 | P4.2/AIN2       |

| P0.3/UTX/T1   | 5  |   | 24 | P4.3/AIN3       |

| P0.2/URX/TC2  | 6  |   | 23 | P4.4/AIN4       |

| P0.1/INT1/TC1 | 7  |   | 22 | P4.5/AIN5       |

| P0.0/INT0/TC0 | 8  |   | 21 | P4.6/AIN6       |

| P1.6/SCK      | 9  |   | 20 | P4.7/AIN7       |

| P1.5/SDI      | 10 |   | 19 | P5.0/AIN8       |

| P1.4/SDO      | 11 |   | 18 | P5.1/AIN9/PWM0  |

| P1.3/SCL      | 12 |   | 17 | P5.2/AIN10/PWM1 |

| P1.2/SDA      | 13 |   | 16 | P5.3/AIN11/PWM2 |

| P1.1/EIDA     | 14 |   | 15 | P1.0/EICK       |

SN8F27E64J (AC field, QFN 4x4 28 Pin):

SN8F27E64LJ (DC field, QFN 4x4 28 Pin):

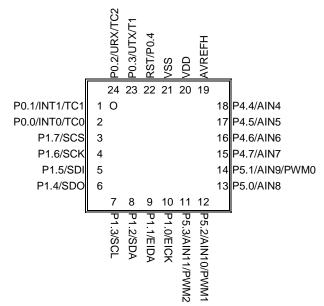

SN8F27E63LJ (DC field, QFN 4x4 24 Pin):

- SN8F27E62P (AC field, DIP 20 Pin):

- SN8F27E62S (AC field, SOP 20 Pin):

|                 |    | , - |    |                 |

|-----------------|----|-----|----|-----------------|

| VSS             | 1  | U   | 20 | VDDL            |

| XIN/P0.6        | 2  |     | 19 | VDD/AVREFH      |

| XOUT/P0.5       | 3  |     | 18 | P4.3/AIN3       |

| RST/P0.4        | 4  |     | 17 | P4.4/AIN4       |

| P0.3/UTX/T1     | 5  |     | 16 | P4.5/AIN5       |

| P0.2/URX/TC2    | 6  |     | 15 | P4.6/AIN6       |

| P0.0/INT0/TC0   | 7  |     | 14 | P4.7/AIN7       |

| P1.1/EIDA       | 8  |     | 13 | P5.0/AIN8       |

| P1.0/EICK       | 9  |     | 12 | P5.1/AIN9/PWM0  |

| P5.3/AIN11/PWM2 | 10 |     | 11 | P5.2/AIN10/PWM1 |

- SN8F27E62LP (DC field, DIP 20 Pin):

- SN8F27E62LS (DC field, SOP 20 Pin):

| VSS             | 1  | U | 20 | VDD             |

|-----------------|----|---|----|-----------------|

| XIN/P0.6        | 2  |   | 19 | VDD/AVREFH      |

| XOUT/P0.5       | 3  |   | 18 | P4.3/AIN3       |

| RST/P0.4        | 4  |   | 17 | P4.4/AIN4       |

| P0.3/UTX/T1     | 5  |   | 16 | P4.5/AIN5       |

| P0.2/URX/TC2    | 6  |   | 15 | P4.6/AIN6       |

| P0.0/INT0/TC0   | 7  |   | 14 | P4.7/AIN7       |

| P1.1/EIDA       | 8  |   | 13 | P5.0/AIN8       |

| P1.0/EICK       | 9  |   | 12 | P5.1/AIN9/PWM0  |

| P5.3/AIN11/PWM2 | 10 |   | 11 | P5.2/AIN10/PWM1 |

#### 1.4 PIN DESCRIPTIONS

| PIN NAME               | TYPE       | DESCRIPTION                                                                                                                                                                                                                |

|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD, VSS               | Р          | Power supply input pins for digital and analog circuit.                                                                                                                                                                    |

| VDDL                   | Р          | Low voltage power pin. Connect 0.1uF capacitor to Vss.                                                                                                                                                                     |

| AVREFH                 | Р          | ADC high reference voltage input pin.                                                                                                                                                                                      |

| RST/P0.4               | I/O        | RST: System external reset input pin. Schmitt trigger structure, active "low", normal stay to "high".  P0.4: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up.  |

| XIN/P0.6               | I/O        | XIN: Oscillator input pin while external oscillator enable (crystal and RC).  P0.6: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change                                    |

| XOUT/P0.5              | I/O        | wake-up.  XOUT: Oscillator output pin while external crystal enable.  P0.5: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up.                                   |

| P0.0/INT0/<br>TC0      | I/O        | P0.0: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up.  INT0: External interrupt 0 input pin.  TC0: TC0 event counter input pin.                               |

| P0.1/INT1/<br>TC1      | I/O        | P0.1: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up.  INT1: External interrupt 1 input pin.  TC1: TC1 event counter input pin.                               |

| P0.2/URX/<br>TC2       | I/O        | P0.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  TC2: TC2 event counter input pin.  URX: UART receive input pin.     |

| P0.3/UTX/T1            | I/O        | P0.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  UTX: UART transmit output pin.  T1: T1 event counter input pin.     |

| P1.0/EICK              | I/O        | P1.0: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  EICK: Embedded ICE clock pin.                                       |

| P1.1/EIDA              | I/O        | P1.1: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  EIDA: Embedded ICE data pin.                                        |

| P1.2/SDA               | I/O        | P1.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  SDA: MSP data pin.                                                  |

| P1.3/SCL               | I/O        | P1.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  SCL: MSP clock pin.                                                 |

| P1.4/SDO               | I/O        | P1.4: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  SDO: SIO data output pin.                                           |

| P1.5/SDI               | I/O        | P1.5: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  SDI: SIO data input pin.                                            |

| P1.6/SCK               | I/O        | P1.6: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  SCK: SIO clock pin.                                                 |

| P1.7/SCS               | I/O        | P1.7: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. Level change wake-up. Programmable open-drain structure.  SCS: SIO bus control pin.                                           |

| P4.0/AIN0              | I/O        | P4.0: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.  AIN0: ADC channel 0 input pin.                                                                                               |

| P4.1/AIN1              | I/O        | P4.1: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.  AIN1: ADC channel 1 input pin.                                                                                               |

| P4.2/AIN2              | I/O        | P4.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.  AIN2: ADC channel 2 input pin.  P4.3: Bi-direction pin. Schmitt trigger structure as input mode. Built in pull-up resisters. |

| P4.3/AIN3<br>P4.4/AIN4 | I/O<br>I/O | P4.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.  AIN3: ADC channel 3 input pin.  P4.4: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| F4.4/AIIN4             | 1/0        | р ч.ч. ы-чинескион рин. Эслиник trigger structure as input mode. Duilt-III pull-up resisters.                                                                                                                              |

|                     |     | AIN4: ADC channel 4 input pin.                                                               |

|---------------------|-----|----------------------------------------------------------------------------------------------|

| D4.5/AINI5          | I/O | P4.5: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| P4.5/AIN5           | 1/0 | AIN5: ADC channel 5 input pin.                                                               |

| P4.6/AIN6           | I/O | P4.6: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| P4.0/AIINO          | 2   | AIN6: ADC channel 6 input pin.                                                               |

| P4.7/AIN7           | I/O | P4.7: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| P4.7/AIIN7          | 2   | AIN7: ADC channel 7 input pin.                                                               |

| P5.0/AIN8           | 1/0 | P5.0: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| PO.U/Alino          | 1/0 | AIN8: ADC channel 8 input pin.                                                               |

| P5.1/AIN9/          |     | P5.1: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| PS. I/AIN9/<br>PWM0 | I/O | AIN9: ADC channel 9 input pin.                                                               |

| FVVIVIO             |     | PWM0: PWM 0 output pin.                                                                      |

| DE 2/AINI40/        |     | P5.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| P5.2/AIN10/<br>PWM1 | I/O | AIN10: ADC channel 10 input pin.                                                             |

| r vvivi i           |     | PWM1: PWM 1 output pin.                                                                      |

| P5.3/AIN11/         |     | P5.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |

| PS.3/AINTI/<br>PWM2 | I/O | AIN11: ADC channel 11 input pin.                                                             |

| F VVIVIZ            |     | PWM2: PWM 2 output pin.                                                                      |

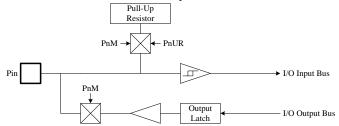

#### 1.5 PIN CIRCUIT DIAGRAMS

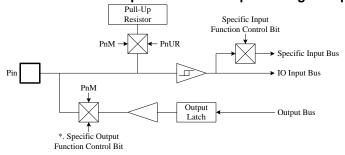

• Normal bi-direction I/O pin.

Bi-direction I/O pin shared with specific digital input function, e.g. INT0, event counter, SIO, MSP, UART...

$<sup>\</sup>ast.$  Some specific functions switch I/O direction directly, not through PnM register.

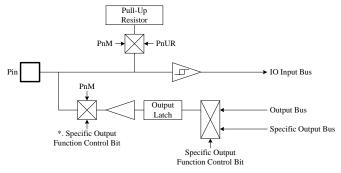

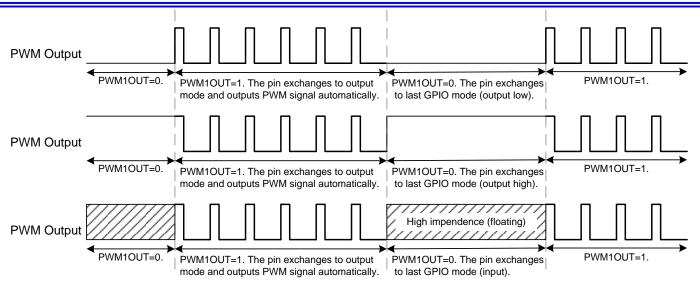

Bi-direction I/O pin shared with specific digital output function, e.g. PWM, SIO, MSP, UART...

<sup>\*.</sup> Some specific functions switch I/O direction directly, not through PnM register.

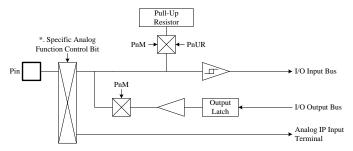

#### Bi-direction I/O pin shared with specific analog input function, e.g. XIN, ADC...

$<sup>{\</sup>bf *. \, Some \, specific \, functions \, switch \, I/O \, direction \, directly, \, not \, through \, PnM \, register.}$

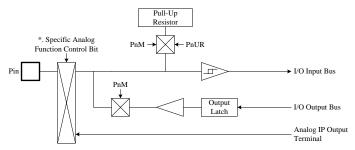

#### Bi-direction I/O pin shared with specific analog output function, e.g. XOUT...

<sup>\*.</sup> Some specific functions switch I/O direction directly, not through PnM register.

# 2 CENTRAL PROCESSOR UNIT (CPU)

#### 2.1 PROGRAM MEMORY (FLASH ROM)

**☞** 6K words FLASH ROM

| Address <u>ROM</u> Comment                |        |

|-------------------------------------------|--------|

| 0000H Reset vector Reset vector           |        |

| 0001H User program                        | n      |

| . General purpose area                    |        |

| 0007H                                     |        |

| 0008H WAKE Interrupt vector Interrupt vec | ctor   |

| 0009H INTO Interrupt vector               |        |

| 000AH INT1 Interrupt vector               |        |

| 000BH T0 Interrupt vector                 |        |

| 000CH TC0 Interrupt vector                |        |

| 000DH TC1 Interrupt vector                |        |

| 000EH TC2 Interrupt vector                |        |

| 000FH T1 Interrupt vector                 |        |

| 0010H ADC Interrupt vector                |        |

| 0011H SIO Interrupt vector                |        |

| 0012H I2C Interrupt vector                |        |

| 0013H UART RX Interrupt vector            |        |

| 0014H UART TX Interrupt vector            |        |

| 0015H User program                        | n      |

|                                           |        |

| . General purpose area                    |        |

|                                           |        |

| . End of user p                           | rogram |

| 17F8H                                     |        |

| 17F9H                                     |        |

| Reserved                                  |        |

| 17FDH Neserved                            |        |

| 17FEH                                     |        |

| 17FFH                                     |        |

The ROM includes Reset vector, Interrupt vector, General purpose area and Reserved area. The Reset vector is program beginning address. The Interrupt vector is the head of interrupt service routine when any interrupt occurring. The General purpose area is main program area including main loop, sub-routines and data table.

- 0x0000 Reset Vector: Program counter points to 0x0000 after any reset events (power on reset, reset pin reset, watchdog reset, LVD reset...).

- 0x0001~0x0007: General purpose area to process system reset operation.

- 0x0008~0x0014: Multi interrupt vector area. Each of interrupt events has a unique interrupt vector.

- 0x0015~0x177F: General purpose area for user program and ISP (EEPROM function).

- 0x1780~0x17F7: General purpose area for user program. Do not execute ISP.

- 0x17F8~0x17FF: Reserved area. Do not execute ISP.

- ROM security rule is even address ROM data protected and outputs 0x0000.

#### **2.1.1 RESET VECTOR (0000H)**

A one-word vector address area is used to execute system reset.

- Power On Reset (POR=1).

- Watchdog Reset (WDT=1).

- External Reset (RST=1).

After power on reset, external reset or watchdog timer overflow reset, then the chip will restart the program from address 0000h and all system registers will be set as default values. It is easy to know reset status from POR, WDT, and RST flags of PFLAG register. The following example shows the way to define the reset vector in the program memory.

Example: Defining Reset Vector

ORG 0 ; 0000H

JMP START ; Jump to user program address.

. . .

ORG 15H

**START:** ; 0015H, The head of user program.

.. ; User program

...

ENDP ; End of program

Note: The head of user program should skip interrupt vector area to avoid program execution error.

#### 2.1.2 INTERRUPT VECTOR (0008H~0014H)

A 13-word vector address area is used to execute interrupt request. If any interrupt service executes, the program counter (PC) value is stored in stack buffer and jump to 0008h~0014h of program memory to execute the vectored interrupt. This interrupt is multi-vector and each of interrupts points to unique vector. Users have to define the interrupt vector. The following example shows the way to define the interrupt vector in the program memory.

Note: The "PUSH" and "POP" operations aren't through instruction (PUSH, POP) and can executed save and load ACC and working registers (0x80~0x8F) by hardware automatically.

|       | ROM                      | Priority |

|-------|--------------------------|----------|

| 0008H | WAKE Interrupt vector    | 1        |

| 0009H | INTO Interrupt vector    | 2        |

| 000AH | INT1 Interrupt vector    | 3        |

| 000BH | T0 Interrupt vector      | 4        |

| 000CH | TC0 Interrupt vector     | 5        |

| 000DH | TC1 Interrupt vector     | 6        |

| 000EH | TC2 Interrupt vector     | 7        |

| 000FH | T1 Interrupt vector      | 8        |

| 0010H | ADC Interrupt vector     | 9        |

| 0011H | SIO Interrupt vector     | 10       |

| 0012H | MSP Interrupt vector     | 11       |

| 0013H | UART RX Interrupt vector | 12       |

| 0014H | UART TX Interrupt vector | 13       |

When one interrupt request occurs, and the program counter points to the correlative vector to execute interrupt service routine. If WAKE interrupt occurs, the program counter points to ORG 8. If INTO interrupt occurs, the program counter points to ORG 9. In normal condition, several interrupt requests happen at the same time. So the priority of interrupt sources is very important, or the system doesn't know which interrupt is processed first. The interrupt priority is follow vector sequence. ORG 8 is priority 1. ORG 9 is priority 2. In the case, the interrupt processing priority is as following.

If WAKE, T0, TC2, T1 and SIO interrupt requests happen at the same time, the system processing interrupt sequence is WAKE, T0, TC2, T1, and then SIO. The system processes WAKE interrupt service routine first, and then processes T0 interrupt routine...Until finishing processing all interrupt requests.

#### Example:

Interrupt Request Occurrence Sequence: (2~8 interrupt requests occur during WAKE interrupt service routine execution.)

| CACCULIOI1.) |     |     |    |     |      |    |         |

|--------------|-----|-----|----|-----|------|----|---------|

| 1            | 2   | 3   | 4  | 5   | 6    | 7  | 8       |

| WAKE         | ADC | TC1 | T0 | SIO | INT0 | T1 | UART RX |

#### Interrupt Processing Sequence:

|   | 1   | 2    | 3  | 4   | 5  | 6   | 7   | 8       |

|---|-----|------|----|-----|----|-----|-----|---------|

| W | AKE | INT0 | T0 | TC1 | T1 | ADC | SIO | UART RX |

Example: Defining Interrupt Vector. The interrupt service routine is following user program.

| .CODE        | ORG<br>JMP                                  | 0<br>START                                                                                                                | ; 0000H<br>; Jump to user program address.                                                |

|--------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|              | ORG JMP | SISR_WAKE ISR_INTO ISR_INT1 ISR_TO ISR_TC0 ISR_TC1 ISR_TC2 ISR_T1 ISR_ADC ISR_SIO ISR_SIO ISR_MSP ISR_UART_RX ISR_UART_TX | ; Interrupt vector, 0008H. ; Jump to interrupt service routine address.                   |

| START:       | ORG<br>                                     | 15H                                                                                                                       | ; 0015H, The head of user program.<br>; User program.                                     |

|              | JMP                                         | START                                                                                                                     | ; End of user program.                                                                    |

| ISR_WAKE:    |                                             |                                                                                                                           | ; The head of interrupt service routine.<br>; Save ACC and 0x80~0x8F register to buffers. |

| ISR_INT0:    | RETI                                        |                                                                                                                           | ; Load ACC and 0x80~0x8F register from buffers.<br>; End of interrupt service routine.    |

| ion_mro.     |                                             |                                                                                                                           | ; Save ACC and 0x80~0x8F register to buffers.                                             |

|              | RETI                                        |                                                                                                                           | ; Load ACC and 0x80~0x8F register from buffers. ; End of interrupt service routine.       |

|              |                                             |                                                                                                                           |                                                                                           |

| ISR_UART_TX: |                                             |                                                                                                                           | ;                                                                                         |

|              |                                             |                                                                                                                           | ; Save ACC and 0x80~0x8F register to buffers.                                             |

|              | RETI                                        |                                                                                                                           | ; Load ACC and 0x80~0x8F register from buffers. ; End of interrupt service routine.       |

|              | ENDP                                        |                                                                                                                           | ; End of program.                                                                         |

- \* Note: It is easy to understand the rules of SONIX program from demo programs given above. These points are as following:

- 1. The address 0000H is a "JMP" instruction to make the program starts from the beginning.

- 2. The address 0008H~0014H is interrupt vector.

- 3. User's program is a loop routine for main purpose application.

#### 2.1.3 LOOK-UP TABLE DESCRIPTION

In the ROM's data lookup function, Y register is pointed to middle byte address (bit 8~bit 15) and Z register is pointed to low byte address (bit 0~bit 7) of ROM. After MOVC instruction executed, the low-byte data will be stored in ACC and high-byte data stored in R register.

> Example: To look up the ROM data located "TABLE1".

$\begin{array}{lll} B0MOV & Y, \#TABLE1\$M & ; To set lookup table1's middle address \\ B0MOV & Z, \#TABLE1\$L & ; To set lookup table1's low address. \\ MOVC & ; To lookup data, R = 00H, ACC = 35H \end{array}$

; Increment the index address for next address.

INCMS Z ; Z+1 JMP @F ; Z is not overflow. INCMS Y ; Z overflow (FFH  $\rightarrow$  00),  $\rightarrow$  Y=Y+1 NOP :

@ @: MOVC ; To lookup data, R = 51H, ACC = 05H.

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H , To define a word (16 bits) da

DW 5105H

DW 2012H

Note: The Y register will not increase automatically when Z register crosses boundary from 0xFF to 0x00. Therefore, user must take care such situation to avoid look-up table errors. If Z register is overflow, Y register must be added one. The following INC\_YZ macro shows a simple method to process Y and Z registers automatically.

> Example: INC\_YZ macro.

INC\_YZ MACRO

INCMS Z : Z+1

JMP @F ; Not overflow

INCMS Y ; Y+1

NOP ; Not overflow

@@:

ENDM

Example: Modify above example by "INC\_YZ" macro.

BOMOV Y, #TABLE1\$M ; To set lookup table1's middle address BOMOV Z, #TABLE1\$L ; To set lookup table1's low address. MOVC ; To lookup data, R = 00H, ACC = 35H

INC\_YZ ; Increment the index address for next address.

@@: MOVC ; To lookup data, R = 51H, ACC = 05H.

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H DW 2012H

• • •

The other example of look-up table is to add Y or Z index register by accumulator. Please be careful if "carry" happen.

Example: Increase Y and Z register by B0ADD/ADD instruction.

B0MOV Y, #TABLE1\$M ; To set lookup table's middle address. B0MOV Z, #TABLE1\$L ; To set lookup table's low address.

B0MOV A, BUF ; Z = Z + BUF. B0ADD Z, A

B0BTS1 FC ; Check the carry flag.

JMP GETDATA ; FC = 0 INCMS Y ; FC = 1. Y+1.

NOP

**GETDATA:**

MOVC ; To lookup data. If BUF = 0, data is 0x0035

; If BUF = 1, data is 0x5105 ; If BUF = 2, data is 0x2012

• • •

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H DW 2012H

...

#### 2.1.4 JUMP TABLE DESCRIPTION

The jump table operation is one of multi-address jumping function. Add low-byte program counter (PCL) and ACC value to get one new PCL. If PCL is overflow after PCL+ACC, PCH adds one automatically. The new program counter (PC) points to a series jump instructions as a listing table. It is easy to make a multi-jump program depends on the value of the accumulator (A).

Note: PCH only support PC up counting result and doesn't support PC down counting. When PCL is carry after PCL+ACC, PCH adds one automatically. If PCL borrow after PCL-ACC, PCH keeps value and not change.

Example: Jump table.

| ORG   | 0X0100  | ; The jump table is from the head of the ROM boundary        |

|-------|---------|--------------------------------------------------------------|

| BOADD | PCL, A  | ; PCL = PCL + ACC, <b>PCH + 1 when PCL overflow occurs</b> . |

| JMP   | A0POINT | ; ACC = 0, jump to A0POINT                                   |

| JMP   | A1POINT | ; ACC = 1, jump to A1POINT                                   |

| JMP   | A2POINT | ; ACC = 2, jump to A2POINT                                   |

| JMP   | A3POINT | ; ACC = 3, jump to A3POINT                                   |

SONIX provides a macro for safe jump table function. This macro will check the ROM boundary and move the jump table to the right position automatically. The side effect of this macro maybe wastes some ROM size.

Example: If "jump table" crosses over ROM boundary will cause errors.

```

@JMP_A MACRO VAL

IF (($+1)!& 0XFF00)!!= (($+(VAL))!& 0XFF00)

JMP ($|0XFF)

ORG ($|0XFF)

ENDIF

ADD PCL, A

ENDM

```

Note: "VAL" is the number of the jump table listing number.

#### Example: "@JMP\_A" application in SONIX macro file called "MACRO3.H".

| B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|--------|---------|-------------------------------------------------|

| @JMP_A | 5       | ; The number of the jump table listing is five. |

| JMP    | A0POINT | ; ACC = 0, jump to A0POINT                      |

| JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

|        |         |                                                 |

If the jump table position is across a ROM boundary (0x00FF~0x0100), the "@JMP\_A" macro will adjust the jump table routine begin from next RAM boundary (0x0100).

#### Example: "@JMP\_A" operation.

#### ; Before compiling program.

| ROM address |        |         |                                                 |

|-------------|--------|---------|-------------------------------------------------|

|             | B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|             | @JMP_A | 5       | ; The number of the jump table listing is five. |

| 0X00FD      | JMP    | A0POINT | ; ACC = 0, jump to A0POINT                      |

| 0X00FE      | JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| 0X00FF      | JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| 0X0100      | JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| 0X0101      | JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

|             |        |         |                                                 |

#### ; After compiling program.

#### ROM address

|        | B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|--------|--------|---------|-------------------------------------------------|

|        | @JMP_A | 5       | ; The number of the jump table listing is five. |

| 0X0100 | JMP    | A0POINT | ; ACC = 0, jump to A0POINT                      |

| 0X0101 | JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| 0X0102 | JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| 0X0103 | JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| 0X0104 | JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

#### 2.1.5 CHECKSUM CALCULATION

The last ROM address are reserved area. User should avoid these addresses (last address) when calculate the Checksum value.

Example: The demo program shows how to calculated Checksum from 00H to the end of user's code.

|               | MOV<br>B0MOV<br>MOV<br>B0MOV<br>CLR<br>CLR        | A,#END_USER_CODE\$L<br>END_ADDR1, A<br>A,#END_USER_CODE\$M<br>END_ADDR2, A<br>Y<br>Z | ; Save low end address to end_addr1<br>; Save middle end address to end_addr2<br>; Set Y to 00H<br>; Set Z to 00H                                                                                  |

|---------------|---------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| @ @:<br>AAA:  | MOVC<br>BOBSET<br>ADD<br>MOV<br>ADC<br>JMP        | FC<br>DATA1, A<br>A, R<br>DATA2, A<br>END_CHECK                                      | ; Clear C flag<br>; Add A to Data1<br>; Add R to Data2<br>; Check if the YZ address = the end of code                                                                                              |

|               | INCMS<br>JMP<br>JMP                               | Z<br>@B<br>Y_ADD_1                                                                   | ; Z=Z+1<br>; If Z != 00H calculate to next address<br>; If Z = 00H increase Y                                                                                                                      |

| END_CHECK:    | MOV<br>CMPRS<br>JMP<br>MOV<br>CMPRS<br>JMP<br>JMP | A, END_ADDR1<br>A, Z<br>AAA<br>A, END_ADDR2<br>A, Y<br>AAA<br>CHECKSUM_END           | ; Check if Z = low end address<br>; If Not jump to checksum calculate<br>; If Yes, check if Y = middle end address<br>; If Not jump to checksum calculate<br>; If Yes checksum calculated is done. |

| Y_ADD_1:      | INCMS<br>NOP                                      | Υ                                                                                    | ; Increase Y                                                                                                                                                                                       |

| CHECKSUM_END: | JMP                                               | @B                                                                                   | ; Jump to checksum calculate                                                                                                                                                                       |

END\_USER\_CODE:

; Label of program end

#### 2.2 DATA MEMORY (RAM)

#### \* 512 X 8-bit RAM

| Bank   | Address  | RAM Location         | Comment       |

|--------|----------|----------------------|---------------|

| Bank 0 | 000H     |                      | RAM Bank 0    |

|        |          | General purpose area |               |

|        | <br>07FH | , ,                  |               |

|        | 080H     | Occasiona Bassissan  |               |

|        | <br>0FFH | System Register      | End of Bank 0 |

| Bank 1 | 100H     |                      | RAM Bank 1    |

|        |          | General purpose area |               |

|        | 1FFH     |                      | End of Bank 1 |

| Bank 2 | 200H     |                      | RAM Bank 2    |

|        | •••      | General purpose area |               |

|        | 27FH     |                      | End of Bank 2 |

The 512-byte general purpose RAM is separated into Bank0, Bank1 and Bank2. Accessing the three banks' RAM is controlled by "RBANK" register. When RBANK = 0, the program controls Bank 0 RAM directly. When RBANK = 1, the program controls Bank 1 RAM directly. When RBANK = 2, the program controls Bank 2 RAM directly. Under one bank condition and need to access the other bank RAM, setup the RBANK register is necessary. When interrupt occurs, RBANK register is saved, and RAM bank is still last condition. User can select RAM bank through setup RBANK register during processing interrupt service routine. When RETI is executed to leave interrupt operation, RBANK register is reloaded, and RAN bank returns to last condition. Sonix provides "Bank 0" type instructions (e.g. b0mov, b0add, b0bts1, b0bset...) to control Bank 0 RAM in non-zero RAM bank condition directly.

Example: Access Bank 0 RAM in Bank 1 condition. Move Bank 0 RAM (WK00) value to Bank 1 RAM (WK01).

; Bank 1 (RBANK = 1)

B0MOV A, WK00 ; Use Bank 0 type instruction to access Bank 0 RAM. MOV WK01,A

#### Note:

- 1. For multi-bank RAM program, it is not easy to control RAM Bank selection. Users have to take care the RBANK condition very carefully, especially for interrupt service routine. The system won't save the RBANK and switch RAM bank to Bank 0, so these controls must be through program. It is a good to use Bank 0 type instruction to process the situations.

- 2. The 190H, 191H of RAM address doesn't support directly addressing mode to access RAM but support indirectly addressing mode @HL/@YZ.

#### 2.2.1 SYSTEM REGISTER

#### 2.2.1.1SYSTEM REGISTER TABLE

|   | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7      | 8      | 9     | Α           | В      | С          | D          | Е          | F            |

|---|-------|-------|-------|-------|-------|-------|-------|--------|--------|-------|-------------|--------|------------|------------|------------|--------------|

| 8 | L     | Н     | R     | Z     | Y     | Х     | PFLAG | RBANK  | W0     | W1    | W2          | W3     | W4         | W5         | W6         | W7           |

| 9 | @HL   | @YZ   | 1     | PCL   | PCH   | OSCM  | WDTR  | INTRQ0 | INTRQ1 | ı     | INTEN0      | INTEN1 | P0OC       | P1OC       | P1W        | PEDGE        |

| Α | P0M   | P1M   | ı     | -     | P4M   | P5M   | P0    | P1     | -      | ı     | P4          | P5     | P0UR       | P1UR       | ı          | -            |

| В | P4UR  | P5UR  | TOM   | T0C   | TCOM  | TC0C  | TC0R  | TC0D   | TC1M   | TC1C  | TC1R        | TC1D   | TC2M       | TC2C       | TC2R       | TC2D         |

| С | T1M   | T1CL  | T1CH  | CPTM  | CPTCL | CPTCH | P4CON | P5CON  | ADM    | ADB   | ADR         | ADT    | İ          | ı          | 1          | -            |

| D | 1     | 1     | ı     | -     | -     | ı     | ı     | i      | -      | ı     | ī           | PECMD  | PE<br>ROML | PE<br>ROMH | PE<br>RAML | PERAM<br>CNT |

| Ε | SIOM  | SIOR  | SIOB  | SIOC  | URTX  | URRX  | URCR  | UTXD   | URXD   | ı     | MSP<br>STAT | MSPM1  | MSPM2      | MSP<br>BUF | MSP<br>ADR | STKP         |

| F | STK7L | STK7H | STK6L | STK6H | STK5L | STK5H | STK4L | STK4H  | STK3L  | STK3H | STK2L       | STK2H  | STK1L      | STK1H      | STK0L      | STK0H        |

#### 2.2.1.2SYSTEM REGISTER DESCRIPTION

H, L = Working, @HL addressing register.

R = Working register and ROM look-up data buffer.

X = Working and ROM address register

RBANK = RAM bank select register.

P1W = Port 1 wakeup register.

PEDGE = P0.0, P0.1 edge direction register.

URTX = UART transmit control register.

URRX = UART receive control register.

URCR = UART baud rate control register.

UTXD = UART transmit data buffer.

T1CH, L = T1 counting registers.

ADM = ADC mode register.

ADR = ADC resolution select register.

PEDGE = P0.0, P0.1, P0.2 edge direction register.

INTEN0,1 = Interrupt enable register.

PnM = Port n input/output mode register.

PnUR = Port n pull-up resister control register.

PCH, PCL = Program counter. T0C = T0 counting register.

TCnC = TCn counting register.

TCnD= TCn duty control register.

CPTCL,H= Capture timer counting registers MSPBUF= MSP buffer register.

MSPADR= MSP address register.

PECMD= ISP command register.

PEROM= ISP ROM address

@HL = RAM HL indirect addressing index pointer.

STKP = Stack pointer buffer.

Y, Z = Working, @YZ and ROM addressing register.

PFLAG = Special flag register.

W0~W7= Working register

P0OC,P1OC = Open-drain control register.

SIOM = SIO mode control register.

SIOR = SIO clock rate control register.

SIOB = SIO data buffer.

SIOC = SIO control register.

T1M = T1 mode register.

URXD = UART receive data buffer.

P4CON,P5CON = P4, P5 configuration register.

ADB = ADC data buffer.

ADT = ADC offset calibration register.

INTRQ0,1 = Interrupt request register.

WDTR = Watchdog timer clear register.

Pn = Port n data buffer.

OSCM = Oscillator mode register.

T0M = T0 mode register.

TCnM = TCn mode register.

TCnR = TCn auto-reload data buffer.

CPTM= Capture timer control register

MSPSTAT= MSP status register MSPM1= MSP mode register1

MSPM2= MSP mode register2

PERAM= ISP RAM mapping address

PERAMCNT= ISP RAM programming counter register.

@YZ = RAM YZ indirect addressing index pointer.

STK0~STK7 = Stack 0 ~ stack 7 buffer.

#### 2.2.1.3 BIT DEFINITION of SYSTEM REGISTER

| Address      | Bit7             | Bit6              | Bit5             | Bit4             | Bit3             | Bit2              | Bit1             | Bit0             | R/W        | Remarks       |

|--------------|------------------|-------------------|------------------|------------------|------------------|-------------------|------------------|------------------|------------|---------------|

| 080H         | LBIT7            | LBIT6             | LBIT5            | LBIT4            | LBIT3            | LBIT2             | LBIT1            | LBIT0            | R/W        | L             |

| 081H         | HBIT7            | HBIT6             | HBIT5            | HBIT4            | HBIT3            | HBIT2             | HBIT1            | HBIT0            | R/W        | H             |

| 082H         | RBIT7            | RBIT6             | RBIT5            | RBIT4            | RBIT3            | RBIT2             | RBIT1            | RBIT0            | R/W        | R             |

| 083H         | ZBIT7            | ZBIT6             | ZBIT5            | ZBIT4            | ZBIT3            | ZBIT2             | ZBIT1            | ZBIT0            | R/W        | Z             |

| 084H         | YBIT7            | YBIT6             | YBIT5            | YBIT4            | YBIT3            | YBIT2             | YBIT1            | YBIT0            | R/W        | Υ             |

| 085H         | XBIT7            | XBIT6             | XBIT5            | XBIT4            | XBIT3            | XBIT2             | XBIT1            | XBIT0            | R/W        | Х             |

| 086H         | POR              | WDT               | RST              | STKOV            |                  | С                 | DC               | Z                | R/W        | PFLAG         |

| 087H         |                  |                   |                  |                  |                  |                   | RBANKS1          | RBANKS0          | R/W        | RBANK         |

| 088H         | W0BIT7           | W0BIT6            | W0BIT5           | W0BIT4           | W0BIT3           | W0BIT2            | W0BIT1           | W0BIT0           | R/W        | W0            |

| 089H         | W1BIT7           | W1BIT6            | W1BIT5           | W1BIT4           | W1BIT3           | W1BIT2            | W1BIT1           | W1BIT0           | R/W        | W1            |

| 08AH         | W2BIT7           | W2BIT6            | W2BIT5           | W2BIT4           | W2BIT3           | W2BIT2            | W2BIT1           | W2BIT0           | R/W        | W2            |

| 08BH         | W3BIT7           | W3BIT6            | W3BIT5           | W3BIT4           | W3BIT3           | W3BIT2            | W3BIT1<br>W4BIT1 | W3BIT0           | R/W        | W3            |

| 08CH<br>08DH | W4BIT7<br>W5BIT7 | W4BIT6<br>W5BIT6  | W4BIT5<br>W5BIT5 | W4BIT4<br>W5BIT4 | W4BIT3<br>W5BIT3 | W4BIT2<br>W5BIT2  | W5BIT1           | W4BIT0<br>W5BIT0 | R/W<br>R/W | W4<br>W5      |

| 08EH         | W6BIT7           | W6BIT6            | W6BIT5           | W6BIT4           | W6BIT3           | W6BIT2            | W6BIT1           | W6BIT0           | R/W        | W6            |

| 08FH         | W7BIT7           | W7BIT6            | W7BIT5           | W7BIT4           | W7BIT3           | W7BIT2            | W7BIT1           | W7BIT0           | R/W        | W7            |

| 090H         | @HL7             | @HL6              | @HL5             | @HL4             | @HL3             | @HL2              | @HL1             | @HL0             | R/W        | @HL           |

| 091H         | @YZ7             | @YZ6              | @YZ5             | @YZ4             | @YZ3             | @YZ2              | @YZ1             | @YZ0             | R/W        | @YZ           |

| 093H         | PC7              | PC6               | PC5              | PC4              | PC3              | PC2               | PC1              | PC0              | R/W        | PCL           |

| 094H         | -                |                   |                  | PC12             | PC11             | PC10              | PC9              | PC8              | R/W        | PCH           |

| 095H         |                  |                   |                  | CPUM1            | CPUM0            | CLKMD             | STPHX            |                  | R/W        | OSCM          |

| 096H         | WDTR7            | WDTR6             | WDTR5            | WDTR4            | WDTR3            | WDTR2             | WDTR1            | WDTR0            | W          | WDTR          |

| 097H         | ADCIRQ           | T1IRQ             | TC2IRQ           | TC1IRQ           | TC0IRQ           | T0IRQ             | P01IRQ           | P00IRQ           | R/W        | INTRQ0        |

| 098H         |                  |                   |                  | MSPIRQ           | UTXIRQ           | URXIRQ            | SIOIRQ           | WAKEIRQ          | R/W        | INTRQ1        |

| 09AH         | ADCIEN           | T1IEN             | TC2IEN           | TC1IEN           | TC0IEN           | TOIEN             | P01IEN           | P00IEN           | R/W        | INTEN0        |

| 09BH         |                  |                   |                  | MSPIEN           | UTXIEN           | URXIEN            | SIOIEN           | WAKEIEN          | R/W        | INTEN1        |

| 09CH         |                  |                   |                  |                  |                  |                   | P03OC            | P02OC            | R/W        | P0OC          |

| 09DH         | P170C            | P16OC             | P15OC            | P140C            | P130C            | P120C             | P110C            | P100C            | R/W        | P10C          |

| 09EH         | P17W             | P16W              | P15W             | P14W             | P13W             | P12W              | P11W             | P10W             | R/W        | P1W           |

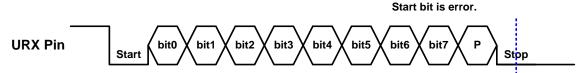

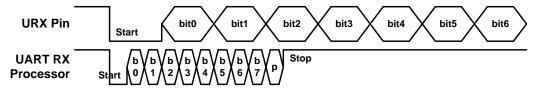

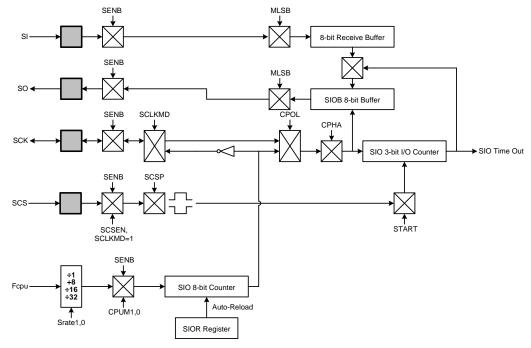

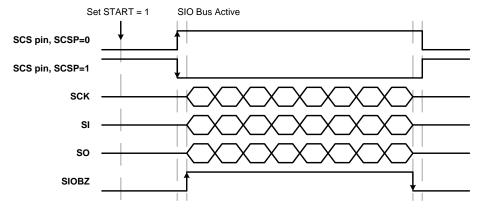

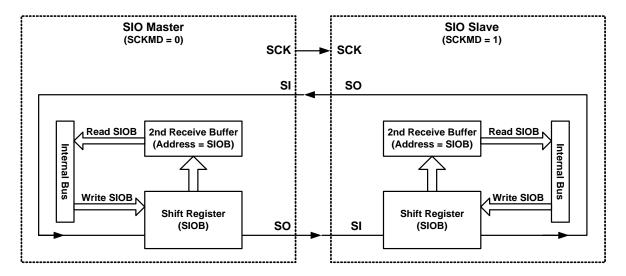

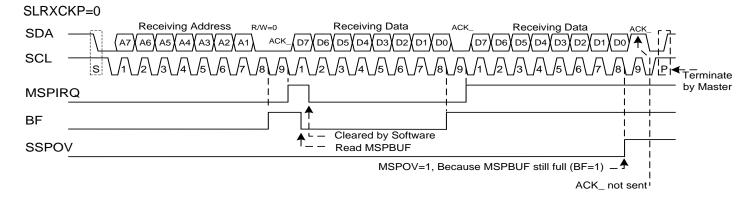

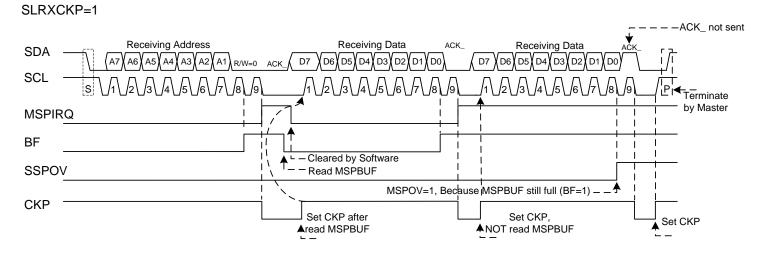

| 09FH<br>0A0H |                  | P06M              | P05M             | P04M             | P01G1<br>P03M    | P01G0<br>P02M     | P00G1<br>P01M    | P00G0<br>P00M    | R/W<br>R/W | PEDGE<br>P0M  |