## **RTL8019AS**

# Realtek Full-Duplex Ethernet Controller with Plug and Play Function (RealPNP)

**SPECIFICATION**

## REALTEK SEMI-CONDUCTOR CO., LTD. HEAD OFFICE

NO. 2, INDUSTRY E. RD. IX, SCIENCE-BASED INDUSTRIAL PARK, HSINCHU 30077, TAIWAN, R.O.C. TEL:886-3-5780211 FAX:886-3-5776598

**OFFICE**

3F, NO. 56, WU-KUNG 6 RD., TAIPEI HSIEN, TAIWAN, R.O.C. TEL: 886-2-22980098 FAX: 886-2-22980094, 22980097

## CONTENTS

| 1. FEATURES                                         | 3  |

|-----------------------------------------------------|----|

| 2. GENERAL DESCRIPTION                              | 4  |

| 3. PIN CONFIGURATION                                | 5  |

| 4. PIN DESCRIPTION                                  |    |

| 4.1. Power Pins                                     | б  |

| 4.2. ISA Bus Interface Pins                         | 6  |

| 4.3. Memory Interface Pins (including BROM, EEPROM) | 7  |

| 4.4. Medium Interface Pins                          | 8  |

| 4.5. LED Output Pins                                | 8  |

| 5. REGISTER DESCRIPTIONS                            |    |

| 5.1. Group 1: NE2000 Registers                      | 9  |

| 5.1.1. Register Table                               | 9  |

| 5.1.2. Register Functions                           | 11 |

| 5.1.2.1. NE2000 Compatible Registers                | 11 |

| 5.1.2.2. RTL8019AS Defined Registers                |    |

| 5.2. Group 2: Plug and Play (PnP) Registers         | 23 |

| 5.2.1. Card Control Registers                       | 24 |

| 5.2.2. Logical Device Control Registers             | 25 |

| 5.2.3. Logical Device Configuration Registers       | 25 |

| 6. FUNCTIONAL DESCRIPTIONS                          |    |

| 6.1. RTL8019AS Configuration Modes                  | 27 |

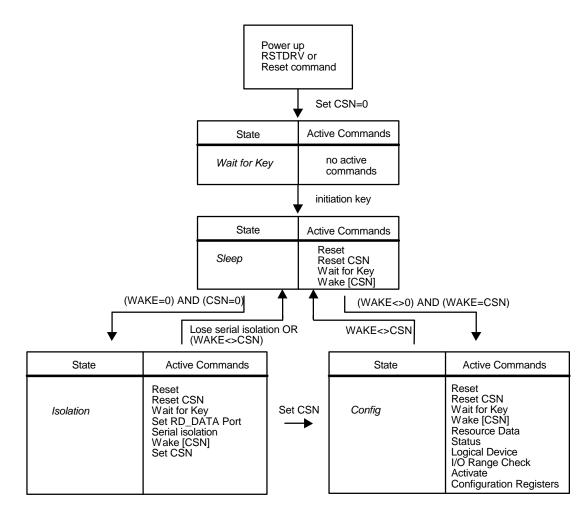

| 6.2. Plug and Play                                  | 29 |

| 6.2.1. Initiation Key                               |    |

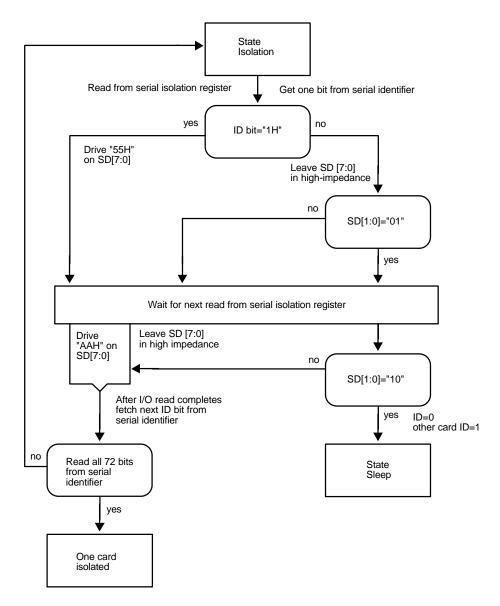

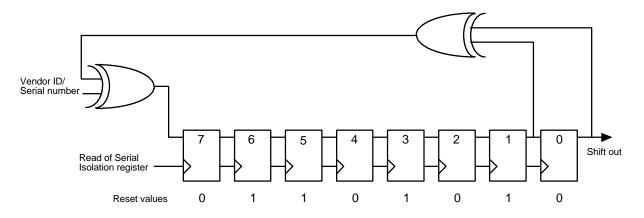

| 6.2.2. Isolation Protocol                           |    |

| 6.2.3. Plug and Play Isolation Sequence             | 34 |

| 6.2.4. Reading Resource Data                        | 35 |

| 6.2.5. PnP auto detect mode                         | 36 |

| 6.3. 9346 Contents                                  | 37 |

| 6.4. Boot ROM ·····                                 |    |

| 6.5. LED Behaviors                                  |    |

| 6.6. Loopback Diagnostic Operation                  | 42 |

| 6.6.1. Loopback Operation                           | 42 |

| 6.6.2. To implement Loopback Test                   | 43 |

| 7. Electrical Specification and Timings             |    |

| 7.1. Absolute Maximum Ratings                       | 46 |

| 7.2. D.C. Characteristics                           | 46 |

| 7.3. A.C. Timing Characteristics                    | 46 |

## **1. FEATURES**

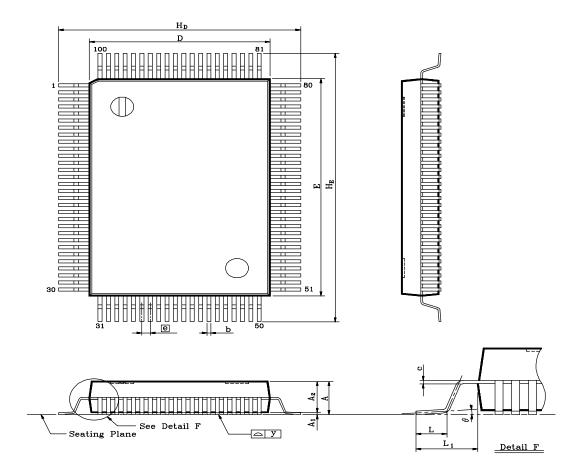

- O 100-pin PQFP

- **O** RTL8019 software compatible

- O Supports PnP auto detect mode (RTL8019AS only)

- O Compliant to Ethernet II and IEEE802.3 10Base5, 10Base2, 10BaseT

- O Software compatible with NE2000 on both 8 and 16-bit slots

- **O** Supports both jumper and jumperless modes

- O Supports Microsoft's Plug and Play configuration for jumperless mode

- **O** Supports Full-Duplex Ethernet function to double channel bandwidth

- **O** Supports three level power down modes:

- Sleep

- Power down with internal clock running

- Power down with internal clock halted

- **O** Built-in data prefetch function to improve performance

- O Supports UTP, AUI & BNC auto-detect (RTL8019AS only)

- Supports auto polarity correction for 10BaseT

- O Support 8 IRQ lines

- Supports 16 I/O base address options and extra I/O address fully decode mode (RTL8019AS only)

- Supports 16K, 32K, 64K and 16K-page mode access to BROM (up to 256 pages with 16K bytes/page)

- O Supports BROM disable command to release memory after remote boot

- Supports flash memory read/write (RTL8019AS only)

- 16k byte SRAM built in (RTL8019AS only)

- Use 9346 (64\*16-bit EEPROM) to store resource configurations and ID parameters

- **O** Capable of programming blank 9346 on board for manufacturing convenience

- Support 4 diagnostic LED pins with programmable outputs

## 2. General Description

The RTL8019AS is a highly integrated Ethernet Controller which offers a simple solution to implement a Plug and Play NE2000 compatible adapter with full-duplex and power down features. With the three level power down control features, the RTL8019AS is made to be an ideal choice of the network device for a GREEN PC system. The full-duplex function enables simultaneously transmission and reception on the twisted-pair link to a full-duplex Ethernet switching hub. This feature not only increases the channel bandwidth from 10 to 20 Mbps but also avoids the performance degrading problem due to the channel contention characteristics of the Ethernet CSMA/CD protocol. The Microsoft's Plug and Play function can relieve the users from pains of taking care the adapter's resource configurations such as IRQ, I/O, and memory address, etc. However, for special applications not to be used as a Plug and Play compatible device, the RTL8019AS also supports the jumper and proprietary jumperless options.

To offer a fully *plug and play* solution, the RTL8019AS provides the auto-detect capability between the integrated 10BaseT transceiver, BNC and AUI interface. Besides, the 10BaseT transceiver can automatically correct the polarity error on its receiving pair. Furthermore, 8 IRQ lines and 16 I/O base address options are provided for grand resource configuration flexibility.

The RTL8019AS supports 16k, 32k & 64k byte BROM and fiash memory interface. It also offers the page mode function which can support up to 4M-byte BROM within only 16k-byte system memory space. Besides, the BROM disable command is provided to release the BROM memory space for other system usage (e.g. EMM386, etc.) after the BROM program is loaded.

The RTL8019AS is built in with 16K-byte SRAM in a single chip. It is designed not only to provide more friendly functions but also to save the effort of SRAM sourcing and inventory.

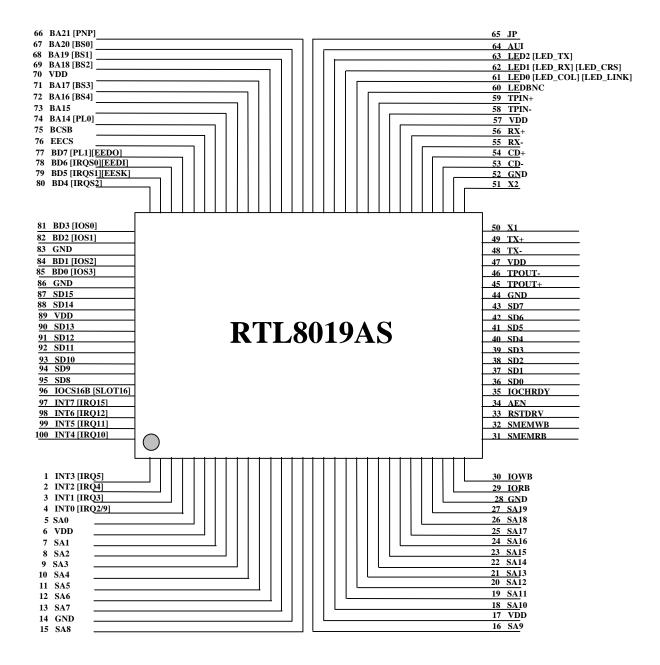

## **3. PIN CONFIGURATION**

## **4. PIN DESCRIPTIONS**

## 4.1. Power Pins

| No.                       | Name | Туре | Description  |

|---------------------------|------|------|--------------|

| 6, 17, 47, 57, 70,<br>89  | VDD  | Р    | +5V DC power |

| 14, 28, 44, 52,<br>83, 86 | GND  | Р    | Ground       |

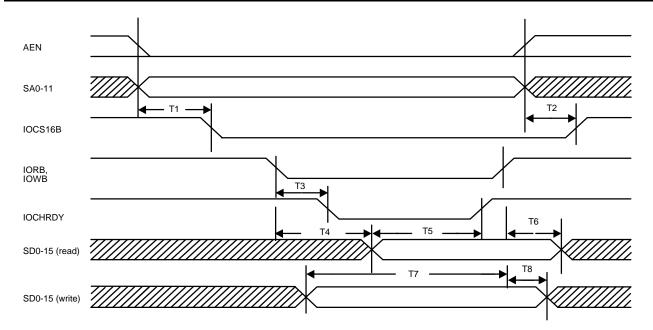

## 4.2. ISA Bus Interface Pins

| No.                       | Name                | Туре | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34                        | AEN                 | Ι    | Address Enable. This ISA signal must be low for a valid I/O command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 97-100, 1-4               | INT7-0              | 0    | Interrupt request lines which are mapped to IRQ15, IRQ12, IRQ11, IRQ10, IRQ5, IRQ4, IRQ3, IRQ2/9 respectively. Only one line is selected to reflect the interrupt requests at one time. All other lines are tri-stated. The RTL8019AS also uses these pins as inputs to monitor the actual state of the corresponding interrupt lines on ISA bus. The result is recorded in the INTR register, which may be used by software to detect interrupt conflict.                                                                                                                                                                                                                                                                                                                                                          |

| 35                        | IOCHRDY             | Ο    | This ISA signal is driven low to insert wait cycles to current host read/write command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 96                        | IOCS16B<br>[SLOT16] | 0    | Upon power-on reset, this pin acts as an input named SLOT16 to detect whether a 16-bit or 8-bit slot is in use. To do this, it is connected to a pull-down resistor (about 27KW) externally. At the falling edge of RSTDRV, the RTL8019AS senses this pin's state. If it is sensed high, the adapter is thought to be placed on a 16-bit slot where this pin is connected to the host's IOCS16B pin, which is typically pulled up by a 300W resistor on the mother board. If it is sensed low, the adapter is thought to be placed on a 8-bit slot where this pin is merely pulled low by the 27KW resistor. After having latched the input state, this pin is switched as the IOCS16B signal which is an open-drain output and is driven low during a 16-bit host data transfer. It is decoded from AEN and SA9-0. |

| 29                        | IORB                | Ι    | Host I/O read command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 30                        | IOWB                | Ι    | Host I/O write command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 33                        | RSTDRV              | Ι    | High active hardware reset signal from the ISA bus. Pulses with high level less than 800ns are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 27-18, 16-<br>15, 13-7, 5 | SA19-0              | Ι    | Host address bus. SA10 is added to implement the fully decode of PnP ports, address 279h and A79h. In RTL8019, SA10 is not decoded. In RTL8019AS, SA10 should be 0 for a valid access to PnP ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 87-88, 90-<br>95, 43-36   | SD15-0              | I/O  | Host data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

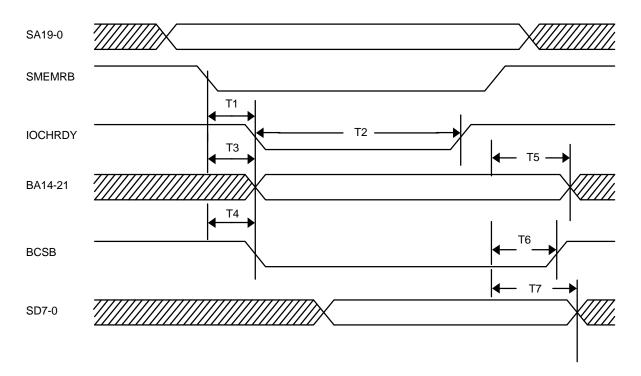

| 31 | SMEMRB | Ι | Host memory read command.                                                                   |

|----|--------|---|---------------------------------------------------------------------------------------------|

| 32 | SMEMWB | Ι | Host memory write command. This pin is added to decode the write command of a flash memory. |

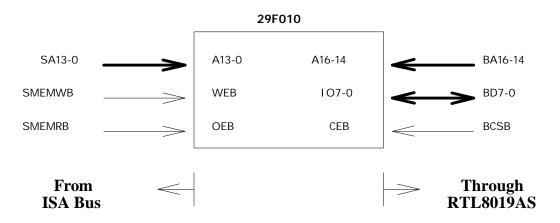

#### 4.3. Memory Interface Pins (including BROM, EEPROM)

| No.            | Name      | Туре | Description                                                                                                                                                                                                                                                                                                                             |

|----------------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 75             | BCSB      | 0    | <ul> <li>BROM chip select. Active low signal, asserted when BROM is read. RTL8019AS drives this pin low when SA19-14 matches the selected BROM memory base address and either of the 2 conditions below meets:</li> <li>(1) SMEMRB is low</li> <li>(2) SMEMWB is low and RTL8019AS's flash memory write function is enabled.</li> </ul> |

| 76             | EECS      | Ο    | 9346 chip select. Active high signal, asserted when 9346 is read/write.                                                                                                                                                                                                                                                                 |

| 66-69, 71-74   | BA21-14   | 0    | BROM address.                                                                                                                                                                                                                                                                                                                           |

| 77-82, 84-85   | BD7-0     | I/O  | BROM data bus.                                                                                                                                                                                                                                                                                                                          |

| [79]           | [EESK]    | 0    | 9346 serial data clock                                                                                                                                                                                                                                                                                                                  |

| [78]           | [EEDI]    | 0    | 9346 serial data input                                                                                                                                                                                                                                                                                                                  |

| [77]           | [EEDO]    | Ι    | 9346 serial data output                                                                                                                                                                                                                                                                                                                 |

|                |           |      | The following pins are defined for jumper options. Their states are latched at the falling edge of RSTDRV, then they are changed to serve as the SRAM bus. Each of them is internally pulled down by a 100KW resistor. Therefore, the input will be low when left open and high when pulled up by a 10K resistor externally.            |

| [66]           | [PNP]     | I    | When it is high in jumperless mode (i.e. JP=low), the RTL8019AS is forced into Plug and Play mode regardless of the contents of 9346.<br>The following pins are don't care in jumperless mode (JP=low).                                                                                                                                 |

| [72-71, 69-67] | [BS4-0]   | Ι    | Select BROM size and base address.                                                                                                                                                                                                                                                                                                      |

| [85-84, 82-81] | [IOS3-0]  | Ι    | Select I/O base address.                                                                                                                                                                                                                                                                                                                |

| [77, 74]       | [PL1-0]   | Ι    | Select network medium type.                                                                                                                                                                                                                                                                                                             |

| [80-78]        | [IRQS2-0] | Ι    | Select one interrupt line among INT7-0.                                                                                                                                                                                                                                                                                                 |

| 65             | JP        | Ι    | When high, this pin selects jumper mode. When low, it selects jumperless modes (including RT jumperless and Plug and Play).                                                                                                                                                                                                             |

After RTL8019AS latches all jumper status upon power on reset, these pins *always*\* reflect the value of BPAGE register directly in BROM page mode. In normal mode, BA16-21 are not used and BA14-15 act as:

| BROM Size | BA14 | BA15 |

|-----------|------|------|

| 16K       | high | high |

| 32K       | SA14 | high |

| 64K       | SA14 | SA15 |

\*Note: RTL8019AS doesn't drive BA14-21 until the SMEMRB goes from high to low.

#### 4.4. Medium Interface Pins

| No.   | Name              | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64    | AUI               | Ι    | This input is used to detect the usage of an external MAU on<br>the AUI interface. The input should be driven low for<br>embedded BNC and high for external MAU. When the input<br>is high, RTL8019AS sets the AUI bit (bit5) in CONFIGO<br>and drives LEDBNC low to disable the BNC. If this pin is<br>not used, it should be connected to GND such that<br>RTL8019AS acts like RTL8019. Please refer to section<br>5.1.2.2. CONFIGO for more details. |

| 54,53 | CD+,CD-           | Ι    | This AUI collision input pair carries the differential collision input signal from the MAU.                                                                                                                                                                                                                                                                                                                                                             |

| 56,55 | RX+,RX-           | Ι    | This AUI receive input pair carries the differential receive input signal from the MAU.                                                                                                                                                                                                                                                                                                                                                                 |

| 49,48 | TX+,TX-           | Ο    | This AUI transmit output pair contains differential line<br>drivers which send Manchester encoded data to the MAU.<br>These outputs are source followers and require 270 ohm<br>pull-down resistors to GND.                                                                                                                                                                                                                                             |

| 59,58 | TPIN+,<br>TPIN-   | Ι    | This TP input pair receives the 10 Mbits/s differential Manchester encoded data from the twisted-pair wire.                                                                                                                                                                                                                                                                                                                                             |

| 45,46 | TPOUT+,<br>TPOUT- | 0    | This pair carries the differential TP transmit output. The<br>output Manchester encoded signals have been pre-distorted<br>to prevent overcharge on the twisted-pair media and thus<br>reduce jitter.                                                                                                                                                                                                                                                   |

| 50    | X1                | Ι    | 20Mhz crystal or external oscillator input.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 51    | X2                | 0    | Crystal feedback output. This output is used in crystal connection only. It must be left open when X1 is driven with an external oscillator.                                                                                                                                                                                                                                                                                                            |

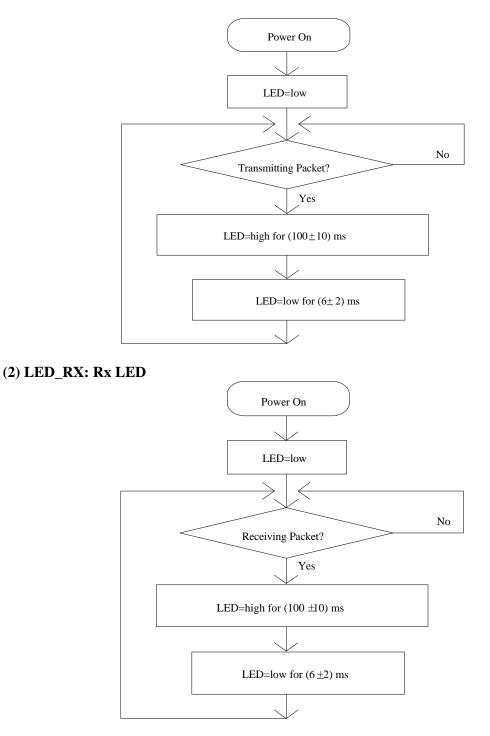

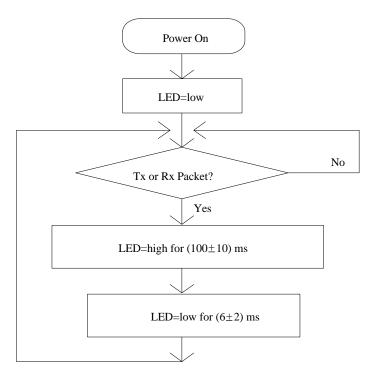

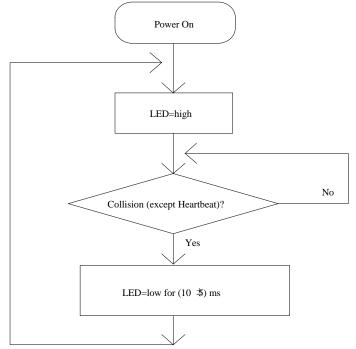

#### 4.5. LED Output Pins

| No. | Name   | Туре | Description                                                                                                                                                                                                                                                                                   |

|-----|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60  | LEDBNC | 0    | This pin goes high when RTL8019AS's medium type is set<br>to 10Base2 mode or auto-detect mode with link test failure.<br>Otherwise, this pin is low. This pin can be used to control<br>the power of the DC convertor for CX MAU and connected<br>to an LED to indicate the used medium type. |

| 61  | LED0   | 0    | When LEDS0 bit (in CONFIG3 register of RTL8019AS Page3) is 0, this pin acts as LED_COL. When LEDS0=1, it acts as LED_LINK.                                                                                                                                                                    |

| Pa<br>re<br>& | When LEDS1 bit (in CONFIG3 register of RTL8019AS<br>Page3) is 0, these 2 pins act as LED_RX & LED_TX<br>espectively. When LEDS1=1, these pins act as LED_CRS<br>& MCSB. Please refer to section 6.5 for details of the<br>ightening behavior of all LEDs. |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## **5. Register Descriptions**

The registers in RTL8019AS can be roughly divided into two groups by their address and functions -- one for NE2000, the other for Plug and Play (PnP).

#### 5.1. Group 1: NE2000 Registers

This group includes 4 pages of registers which are selected by bit PS0 & PS1 in the CR register. Each page contains 16 registers. Besides those registers compatible with NE2000, the RTL8019AS defines some registers for software configuration and feature enhancement.

| No (Hex) | Hex) Page0 |        | Page1 | Page2        |                | Page3   |

|----------|------------|--------|-------|--------------|----------------|---------|

|          | [R]        | [W]    | [R/W] | [ <b>R</b> ] | [R]            | [W]     |

| 00       | CR         | CR     | CR    | CR           | CR             | CR      |

| 01       | CLDA0      | PSTART | PAR0  | PSTART       | 9346CR         | 9346CR  |

| 02       | CLDA1      | PSTOP  | PAR1  | PSTOP        | BPAGE          | BPAGE   |

| 03       | BNRY       | BNRY   | PAR2  | -            | <b>CONFIG0</b> | -       |

| 04       | TSR        | TPSR   | PAR3  | TPSR         | CONFIG1        | CONFIG1 |

| 05       | NCR        | TBCR0  | PAR4  | -            | CONFIG2        | CONFIG2 |

| 06       | FIFO       | TBCR1  | PAR5  | -            | CONFIG3        | CONFIG3 |

| 07       | ISR        | ISR    | CURR  | -            | -              | TEST    |

| 08       | CRDA0      | RSAR0  | MAR0  | -            | CSNSAV         | -       |

| 09       | CRDA1      | RSAR1  | MAR1  | -            | -              | HLTCLK  |

| 0A       | 8019ID0    | RBCR0  | MAR2  | -            | -              | -       |

| 0B       | 8019ID1    | RBCR1  | MAR3  | -            | INTR           | -       |

| 0C       | RSR        | RCR    | MAR4  | RCR          | -              | FMWP    |

| 0D       | CNTR0      | TCR    | MAR5  | TCR          | CONFIG4        | -       |

| 0E       | CNTR1      | DCR    | MAR6  | DCR          | -              | -       |

| 0F       | CNTR2      | IMR    | MAR7  | IMR          | -              | -       |

| 10-17    | Remote DMA | Port   |       |              |                |         |

| 18-1F    | Reset Port |        |       |              |                |         |

#### 5.1.1. Register Table

Notes: "-" denotes reserved. Registers with names typed in *bold italic* format are RTL8019AS defined registers and are not supported in a standard NE2000 adapter.

## Page 0 (PS1=0, PS0=0)

| No. | Name    | Туре | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00H | CR      | R/W  | PS1   | PS0   | RD2   | RD1   | RD0   | TXP   | STA   | STP   |

| 01H | CLDA0   | R    | A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    |

|     | PSTART  | W    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 02H | CLDA1   | R    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

|     | PSTOP   | W    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 03H | BNRY    | R/W  | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 04H | TSR     | R    | OWC   | CDH   | 0     | CRS   | ABT   | COL   | -     | PTX   |

|     | TPSR    | W    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 05H | NCR     | R    | 0     | 0     | 0     | 0     | NC3   | NC2   | NC1   | NC0   |

|     | TBCR0   | W    | TBC7  | TBC6  | TBC5  | TBC4  | TBC3  | TBC2  | TBC1  | TBC0  |

| 06H | FIFO    | R    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|     | TBCR1   | W    | TBC15 | TBC14 | TBC13 | TBC12 | TBC11 | TBC10 | TBC9  | TBC8  |

| 07H | ISR     | R/W  | RST   | RDC   | CNT   | OVW   | TXE   | RXE   | PTX   | PRX   |

| 08H | CRDA0   | R    | A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    |

|     | RSAR0   | W    | A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    |

| 09H | CRDA1   | R    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

|     | RSAR1   | W    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 0AH | 8019ID0 | R    | 0     | 1     | 0     | 1     | 0     | 0     | 0     | 0     |

|     | RBCR0   | W    | RBC7  | RBC6  | RBC5  | RBC4  | RBC3  | RBC2  | RBC1  | RBC0  |

| 0BH | 8019ID1 | R    | 0     | 1     | 1     | 1     | 0     | 0     | 0     | 0     |

|     | RBCR1   | W    | RBC15 | RBC14 | RBC13 | RBC12 | RBC11 | RBC10 | RBC9  | RBC8  |

| 0CH | RSR     | R    | DFR   | DIS   | PHY   | MPA   | 0     | FAE   | CRC   | PRX   |

|     | RCR     | W    | -     | -     | MON   | PRO   | AM    | AB    | AR    | SEP   |

| 0DH | CNTR0   | R    | CNT7  | CNT6  | CNT5  | CNT4  | CNT3  | CNT2  | CNT1  | CNT0  |

|     | TCR     | W    | -     | -     | -     | OFST  | ATD   | LB1   | LB0   | CRC   |

| 0EH | CNTR1   | R    | CNT7  | CNT6  | CNT5  | CNT4  | CNT3  | CNT2  | CNT1  | CNT0  |

|     | DCR     | W    | -     | FT1   | FT0   | ARM   | LS    | LAS   | BOS   | WTS   |

| 0FH | CNTR2   | R    | CNT7  | CNT6  | CNT5  | CNT4  | CNT3  | CNT2  | CNT1  | CNT0  |

|     | IMR     | W    | -     | RDCE  | CNTE  | OVWE  | TXEE  | RXEE  | PTXE  | PRXE  |

#### Page 1 (PS1=0, PS0=1)

| No. | Name | Туре | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00H | CR   | R/W  | PS1   | PS0   | RD2   | RD1   | RD0   | TXP   | STA   | STP   |

| 01H | PAR0 | R/W  | DA7   | DA6   | DA5   | DA4   | DA3   | DA2   | DA1   | DA0   |

| 02H | PAR1 | R/W  | DA15  | DA14  | DA13  | DA12  | DA11  | DA10  | DA9   | DA8   |

| 03H | PAR2 | R/W  | DA23  | DA22  | DA21  | DA20  | DA19  | DA18  | DA17  | DA16  |

| 04H | PAR3 | R/W  | DA31  | DA30  | DA29  | DA28  | DA27  | DA26  | DA25  | DA24  |

| 05H | PAR4 | R/W  | DA39  | DA38  | DA37  | DA36  | DA35  | DA34  | DA33  | DA32  |

| 06H | PAR5 | R/W  | DA47  | DA46  | DA45  | DA44  | DA43  | DA42  | DA41  | DA40  |

| 07H | CURR | R/W  | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 08H | MAR0 | R/W  | FB7   | FB6   | FB5   | FB4   | FB3   | FB2   | FB1   | FB0   |

| 09H | MAR1 | R/W  | FB15  | FB14  | FB13  | FB12  | FB11  | FB10  | FB9   | FB8   |

| 0AH | MAR2 | R/W  | FB23  | FB22  | FB21  | FB20  | FB19  | FB18  | FB17  | FB16  |

| 0BH | MAR3 | R/W  | FB31  | FB30  | FB29  | FB28  | FB27  | FB26  | FB25  | FB24  |

| 0CH | MAR4 | R/W  | FB39  | FB38  | FB37  | FB36  | FB35  | FB34  | FB33  | FB32  |

| 0DH | MAR5 | R/W  | FB47  | FB46  | FB45  | FB44  | FB43  | FB42  | FB41  | FB40  |

| 0EH | MAR6 | R/W  | FB55  | FB54  | FB53  | FB52  | FB51  | FB50  | FB49  | FB48  |

| 0FH | MAR7 | R/W  | FB63  | FB62  | FB61  | FB60  | FB59  | FB58  | FB57  | FB56  |

## Page 2(PS1=1, PS0=0)

| No. | Name   | Туре | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|--------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00H | CR     | R/W  | PS1   | PS0   | RD2   | RD1   | RD0   | TXP   | STA   | STP   |

| 01H | PSTART | R    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 02H | PSTOP  | R    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 03H | -      |      |       |       |       |       |       |       |       |       |

| 04H | TPSR   | R    | A15   | A14   | A13   | A12   | A11   | A10   | A9    | A8    |

| 05H | -      |      |       |       |       |       |       |       |       |       |

|     |        |      |       |       |       |       |       |       |       |       |

| 0BH |        |      |       |       |       |       |       |       |       |       |

| 0CH | RCR    | R    | -     | -     | MON   | PRO   | AM    | AB    | AR    | SEP   |

| 0DH | TCR    | R    | -     | -     | -     | OFST  | ATD   | LB1   | LB0   | CRC   |

| 0EH | DCR    | R    | -     | FT1   | FT0   | ARM   | LS    | LAS   | BOS   | WTS   |

| 0FH | IMR    | R    | -     | RDCE  | CNTE  | OVWE  | TXEE  | RXEE  | PTXE  | PRXE  |

#### Page 3(PS1=1, PS0=1)

| No. | Name    | Туре  | Bit 7    | Bit 6      | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   |

|-----|---------|-------|----------|------------|-----------|-------|-------|-------|-------|---------|

| 00H | CR      | R/W   | PS1      | PS0        | RD2       | RD1   | RD0   | ТХР   | STA   | STP     |

| 01H | 9346CR  | R     | EEM1     | EEM0       | -         | -     | EECS  | EESK  | EEDI  | EEDO    |

|     |         | W     | EEM1     | EEM0       | -         | -     | EECS  | EESK  | EEDI  | -       |

| 02H | BPAGE   | R/W   | BP7      | BP6        | BP5       | BP4   | BP3   | BP2   | BP1   | BP0     |

| 03H | CONFIG0 | R     | VerID1   | VerID0     | AUI       | PNPJP | JP    | BNC   | 0     | 0       |

| 04H | CONFIG1 | R     | IRQEN    | IRQS2      | IRQS1     | IRQS0 | IOS3  | IOS2  | IOS1  | IOS0    |

|     |         | W*    | IRQEN    | -          | -         | -     | -     | -     | -     | -       |

| 05H | CONFIG2 | R     | PL1      | PL0        | BSELB     | BS4   | BS3   | BS2   | BS1   | BS0     |

|     |         | W*    | PL1      | PL0        | BSELB     | -     | -     | -     | -     | -       |

| 06H | CONFIG3 | R     | PNP      | FUDUP      | LEDS1     | LEDS0 | -     | SLEEP | PWRDN | ACTIVEB |

|     |         | W*    | -        | -          | -         | -     | -     | SLEEP | PWRDN | -       |

| 07H | TEST    | R/W   | Reserved | , Do not w | rite      |       |       |       |       |         |

| 08H | CSNSAV  | R     | CSN7     | CSN6       | CSN5      | CSN4  | CSN3  | CSN2  | CSN1  | CNS0    |

| 09H | HLTCLK  | W     | HLT7     | HLT6       | HLT5      | HLT4  | HLT3  | HLT2  | HLT1  | HLT0    |

| 0AH | -       | -     | Reserved |            |           |       |       |       |       |         |

| 0BH | INTR    | R     | INT7     | INT6       | INT5      | INT4  | INT3  | INT2  | INT1  | INT0    |

| 0CH | FMWP    | $W^*$ | Flash Me | mory Writ  | e Protect |       |       |       |       |         |

| 0DH | CONFIG4 | R     | -        | -          | -         | -     | -     | -     | -     | IOMS    |

| 0EH | -       | -     | Reserved | •          | •         | •     | •     | •     | •     |         |

|     |         |       |          |            |           |       |       |       |       |         |

| 0FH |         |       |          |            |           |       |       |       |       |         |

Note: The registers marked with type='W\*' can be written only if bits EEM1=EEM0=1.

#### **5.1.2. Register Functions**

## 5.1.2.1. NE2000 Compatible Registers

**CR:** Command Register (00H; Type=R/W)

This register is used to select register pages, enable or disable remote DMA operation and issue commands.

| Bit | Symbol   | Description |             |             |                   |                  |                     |              |  |  |

|-----|----------|-------------|-------------|-------------|-------------------|------------------|---------------------|--------------|--|--|

| 7,6 | PS1, PS0 |             |             |             |                   |                  |                     |              |  |  |

|     |          |             | PS1         | PS0         | Register Pa       | ige ]            | Remark              |              |  |  |

|     |          |             | 0           | 0           | 0                 | NE2000           | compatible          |              |  |  |

|     |          |             | 0           | 1           | 1                 | NE2000           | compatible          |              |  |  |

|     |          |             | 1           | 0           | 2                 | NE2000           | compatible          |              |  |  |

|     |          |             | 1           | 1           | 3                 | RTL801           | 9AS                 |              |  |  |

|     |          |             |             |             |                   | Configu          | ration              |              |  |  |

|     |          |             |             |             |                   |                  |                     |              |  |  |

| 5-3 | RD2-0    |             |             | _           |                   | I                |                     | 1            |  |  |

|     |          |             | RD2         | RD1         | RD0               |                  | nction              |              |  |  |

|     |          |             | 0           | 0           | 0                 | Not allowed      |                     |              |  |  |

|     |          |             | 0           | 0           | 1                 | Remote Read      |                     |              |  |  |

|     |          |             | 0           | 1           | 0                 | Remote Write     |                     |              |  |  |

|     |          |             | 0           | 1           | 1                 | Send Packet      |                     |              |  |  |

|     |          |             | 1           | *           | *                 | Abort/Comple     | te remote DMA       |              |  |  |

|     |          |             |             |             | •                 |                  |                     | 0.1          |  |  |

| 2   | TXP      |             |             |             |                   |                  | mally reset eith    | er after the |  |  |

| 1   | STA      |             |             |             |                   | ng a 0 has no ei |                     | OWED         |  |  |

| 1   | 51A      | UP=0        |             | rois notnin | g. It only reflec | is the value wr  | tten to this bit. P | OWER         |  |  |

| 0   | STP      |             | •           | STOP con    | mand When         | it is set no     | packets will be     | received or  |  |  |

| 0   | 511      |             | nitted. POW |             |                   | it is set, no    | Jackets will be     | lectived of  |  |  |

|     |          | transn      |             | LR 01-1.    |                   |                  |                     |              |  |  |

|     |          |             | STA         | STP         | F                 | inction          |                     |              |  |  |

|     |          |             | 1           | 0           | Start Comr        | nand             | =                   |              |  |  |

|     |          |             | 0           | 1           | Stop Comm         | nand             |                     |              |  |  |

|     |          |             | -           | 1           | r                 |                  |                     |              |  |  |

**ISR:** Interrupt Status Register (07H; Type=R/W in Page0)

This register reflects the NIC status. The host reads it to determine the cause of an interrupt. Individual bits are cleared by writing a "1" into the corresponding bit. It must be cleared after power up.

| Bit | Symbol | Description                                                                               |

|-----|--------|-------------------------------------------------------------------------------------------|

| 7   | RST    | This bit is set when NIC enters reset state and is cleared when a start command is        |

|     |        | issued to the CR. It is also set when receive buffer overflows and is cleared when one or |

|     |        | more packets have been read from the buffer.                                              |

| 6   | RDC    | Set when remote DMA operation has been completed.                                         |

| 5   | CNT    | Set when MSB of one or more of the network tally counters has been set.                   |

| 4   | OVW    | This bit is set when the receive buffer has been exhausted.                               |

| 3   | TXE    | Transmit error bit is set when a packet transmission is aborted due to excessive          |

|     |        | collisions.                                                                               |

| 2   | RXE    | This bit is set when a packet received with one or more of the following errors:          |

|     |        | - CRC error                                                                               |

|     |        | - Frame alignment error                                                                   |

|     |        | -Missed packet                                                                            |

| 1   | PTX    | This bit indicates packet transmitted with no errors.                                     |

| 0   | PRX    | This bit indicates packet received with no errors.                                        |

**IMR:** Interrupt Mask Register (0FH; Type=W in Page0, Type=R in Page2) All bits correspond to the bits in the ISR register. POWER UP=all 0s. Setting individual bits will enable the corresponding interrupts.

**DCR:** Data Configuration Register (0EH; Type=W in Page0, Type=R in Page2)

| Bit  | Symbol   | Description                                                           |  |  |  |  |  |  |

|------|----------|-----------------------------------------------------------------------|--|--|--|--|--|--|

| 7    | -        | Always 1                                                              |  |  |  |  |  |  |

| 6, 5 | FT1, FT0 | FIFO threshold select bit 1 and 0.                                    |  |  |  |  |  |  |

| 4    | ARM      | Auto-initialize Remote                                                |  |  |  |  |  |  |

|      |          | 0: Send Packet Command not executed.                                  |  |  |  |  |  |  |

|      |          | 1: Send Packet Command executed.                                      |  |  |  |  |  |  |

| 3    | LS       | Loopback Select                                                       |  |  |  |  |  |  |

|      |          | 0: Loopback mode selected. Bits 1 and 2 of the TCR must also be       |  |  |  |  |  |  |

|      |          | programmed for Loopback operation.                                    |  |  |  |  |  |  |

|      |          | 1: Normal Operation                                                   |  |  |  |  |  |  |

| 2    | LAS      | This bit must be set to zero. NIC only supports dual 16-bit DMA mode. |  |  |  |  |  |  |

|      |          | POWER UP =1                                                           |  |  |  |  |  |  |

| 1    | BOS      | Byte Order Select (Not implement)                                     |  |  |  |  |  |  |

|      |          | 0: MS byte placed on MD15-8 and LS byte on MD7-0. (32xxx,80x86)       |  |  |  |  |  |  |

|      |          | 1: MS byte placed on MD7-0 and LS byte on MD15-8. (680x0)             |  |  |  |  |  |  |

| 0    | WTS      | Word Transfer Select                                                  |  |  |  |  |  |  |

|      |          | 0: byte-wide DMA transfer                                             |  |  |  |  |  |  |

|      |          | 1: word-wide DMA transfer                                             |  |  |  |  |  |  |

TCR: Transmit Configuration Register (0DH; Type=W in Page0, Type=R in Page2)

| Bit  | Symbol   |        | Description                                                               |               |                         |                   |                                                    |  |  |  |  |  |  |

|------|----------|--------|---------------------------------------------------------------------------|---------------|-------------------------|-------------------|----------------------------------------------------|--|--|--|--|--|--|

| 7    | -        | Alway  | ys 1                                                                      |               |                         |                   |                                                    |  |  |  |  |  |  |

| 6    | -        | Alway  | Always 1                                                                  |               |                         |                   |                                                    |  |  |  |  |  |  |

| 5    | -        | Alway  | Always 1                                                                  |               |                         |                   |                                                    |  |  |  |  |  |  |

| 4    | OFST     | Collis | Collision Offset Enable.                                                  |               |                         |                   |                                                    |  |  |  |  |  |  |

| 3    | ATD      | Auto   | Auto Transmit Disable.                                                    |               |                         |                   |                                                    |  |  |  |  |  |  |

|      |          |        | 0: normal operation                                                       |               |                         |                   |                                                    |  |  |  |  |  |  |

|      |          |        | 1: reception of multicast address hashing to bit 62 disables transmitter, |               |                         |                   |                                                    |  |  |  |  |  |  |

|      |          | rec    | reception of multicast address hashing to bit 63 enables transmitter.     |               |                         |                   |                                                    |  |  |  |  |  |  |

| 2, 1 | LB1, LB0 |        |                                                                           |               |                         |                   |                                                    |  |  |  |  |  |  |

|      |          |        | LB1 LB0 Mode Remark                                                       |               |                         |                   |                                                    |  |  |  |  |  |  |

|      |          |        | 0                                                                         | 0             | 0                       | Normal Operation  |                                                    |  |  |  |  |  |  |

|      |          |        | 0                                                                         | 1             | 1                       | Internal Lookback |                                                    |  |  |  |  |  |  |

|      |          |        | 1                                                                         | 0             | 2                       | External Lookback |                                                    |  |  |  |  |  |  |

|      |          |        | 1                                                                         | 1             | 3                       | External          | Lookback                                           |  |  |  |  |  |  |

| 0    | CRC      | receiv |                                                                           | ontrols the a | ctivity of th           | e CRC log         | or transmitter and a gic. If this bit set, Carter. |  |  |  |  |  |  |

|      |          |        | Con                                                                       | ditions       |                         | CRC Log           | ic Activities                                      |  |  |  |  |  |  |

|      |          |        | CRC Bit                                                                   | Mode          | CRC G                   | enerator          | CRC Checker                                        |  |  |  |  |  |  |

|      |          |        | 0                                                                         | normal        | enabl                   | ed                | enabled                                            |  |  |  |  |  |  |

|      |          |        | 1                                                                         | normal        | normal disabled enabled |                   |                                                    |  |  |  |  |  |  |

|      |          |        | 0                                                                         | loopback      | enabl                   | ed                | disabled                                           |  |  |  |  |  |  |

|      |          |        | 1                                                                         | loopback      | disab                   | led               | enabled                                            |  |  |  |  |  |  |

|      |          |        |                                                                           |               |                         |                   |                                                    |  |  |  |  |  |  |

## **TSR:** Transmit Status Register (04H; Type=R in Page0)

This register indicates the status of a packet transmission.

| Bit | Symbol | Description                                                                                 |

|-----|--------|---------------------------------------------------------------------------------------------|

| 7   | OWC    | Out of Window Collision. It is set when a collision is detected after a slot time (51.2us). |

|     |        | Transmissions are rescheduled as in normal collisions.                                      |

| 6   | CDH    | CD Heartbeat. The NIC watches for a collision signal (i.e. CD Heartbeat signal) during      |

|     |        | the first 6.4us of the interframe gap following a transmission. This bit is set if the      |

|     |        | transceiver fails to send this signal.                                                      |

| 5   | -      | Always 1.                                                                                   |

| 4   | CRS    | Carrier Sense lost bit is set when the carrier is lost during transmitting a packet.        |

| 3   | ABT    | It indicates the NIC aborted the transmission because of excessive collisions.              |

| 2   | COL    | It indicates the transmission collided with some other station on the network.              |

| 1   | _      | Always 1                                                                                    |

| 0   | PTX    | This bit indicates the transmission completes with no errors.                               |

#### **RCR:** Receive Configuration Register (0CH; Type=W in Page0, Type=R in Page2)

| Bit | Symbol | Description                                                                            |

|-----|--------|----------------------------------------------------------------------------------------|

| 7   | -      | Always 1                                                                               |

| 6   | -      | Always 1                                                                               |

| 5   | MON    | When monitor mode bit is set, received packets are checked for address match, good CRC |

|     |        | and frame alignment but not buffered to memory. Otherwise, packets will be buffered to |

|     |        | memory.                                                                                |

| 4   | PRO    | If PRO=1, all packets with physical destination address accepted.                      |

|     |        | If PRO=0, physical destination address must match the node address programmed in       |

|     |        | PAR0-5.                                                                                |

| 3   | AM     | If AM=1, packets with multicast destination address are accepted.                      |

|     |        | If AM=0, packets with multicast destination address are rejected.                      |

| 2   | AB     | If AB=1, packets with broadcast destination address are accepted.                      |

|     |        | If AB=0, packets with broadcast destination address are rejected.                      |

| 1   | AR     | If AR=1, packets with length fewer than 64 bytes are accepted.                         |

|     |        | If AR=0, packets with length fewer than 64 bytes are rejected.                         |

| 0   | SEP    | If SEP=1, packets with receive errors are accepted.                                    |

|     |        | If SEP=0, packets with receive errors are rejected.                                    |

#### **RSR:** Receive Status Register (0CH; Type=R in Page0)

| Bit | Symbol | Description                                                                                  |

|-----|--------|----------------------------------------------------------------------------------------------|

| 7   | DFR    | Defferring. Set when a carrier or a collision is detected.                                   |

| 6   | DIS    | Receiver Disabled. When the NIC enters the monitor mode, this bit is set and receiver is     |

|     |        | disabled. Reset when receiver is enabled after leaving the monitor mode.                     |

| 5   | PHY    | PHY bit is set when the received packet has a multicast or broadcast destination address. It |

|     |        | is reset when the received packet has a physical destination address.                        |

| 4   | MPA    | Missed Packet bit is set when the incoming packet can not be accepted by NIC because of      |

|     |        | a lack of receive buffer or if NIC is in monitor mode. Increment CNTR2 tally counter.        |

| 3   | -      | Always 1.                                                                                    |

| 2   | FAE    | Frame Alignment Error bit reflects the incoming packet didn't end on a byte boundary         |

|     |        | and CRC did not match at last byte boundary. Increment CNTR0 tally counter.                  |

| 1   | CRC    | CRC error bit reflects packet received with CRC error. This bit will also be set for FAE     |

|     |        | errors. Increment CNTR1 tally counter.                                                       |

| 0   | PRX    | This bit indicates packet received with no errors.                                           |

**CLDA0, 1:** Current Local DMA Registers (01H & 02H; Type=R in Page0) These two registers can be read to get the current local DMA address.

| PSTART:        | Page Start Register (01H; Type=W in Page0, Type=R in Page 2)<br>The Page Start register sets the start page address of the receive buffer ring.                                                                                                                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSTOP:         | Page Stop Register (02H; Type=W in Page0, Type=R in Page2)<br>The Page Stop register sets the stop page address of the receive buffer ring. In 8 bit<br>mode the PSTOP register should not exceed to 0x60, in 16 bit mode the PSTOP<br>register should not exceed to 0x80.                                                                                 |

| BNRY:<br>TPSR: | Boundary Register (03H; Type=R/W in Page0)<br>This register is used to prevent overwrite of the receive buffer ring. It is typically<br>used as a pointer indicating the last receive buffer page the host has read.<br>Transmit Page Start Register (04H; Type=W in Page0)<br>This register sets the start page address of the packet to the transmitted. |

| TBCR0,1:       | Transmit Byte Count Registers (05H & 06H; Type=W in Page0)<br>These two registers set the byte counts of the packet to be transmitted.                                                                                                                                                                                                                     |

| NCR:           | Number of Collisions Register (05H; Type=R in Page0)<br>The register records the number of collisions a node experiences during a packet transmission.                                                                                                                                                                                                     |

| FIFO:          | First In First Out Register (06H; Type=R in Page0)<br>This register allows the host to examine the contents of the FIFO after loopback.                                                                                                                                                                                                                    |

| CRDA0, 1:      | Current Remote DMA Address registers (08H & 09H; Type=R in Page0)<br>These two registers contain the current address of remote DMA.                                                                                                                                                                                                                        |

| RSAR0,1:       | Remote Start Address Registers (08H & 09H; Type=W in Page0)<br>These two registers set the start address of remote DMA.                                                                                                                                                                                                                                    |

| RBCR0,1:       | Remote Byte Count Registers (0AH & 0BH; Type=W in Page0)<br>These two registers se the data byte counts of remote DMA.                                                                                                                                                                                                                                     |

| CNTR0:         | Frame Alignment Error Tally Counter Register (0DH; Type=R in Page0)                                                                                                                                                                                                                                                                                        |

| CNTR1:         | CRC Error Tally Counter Register (0EH; Type=R in Page0)                                                                                                                                                                                                                                                                                                    |

| CNTR2:         | Missed Packet Tally Counter Register (0FH; Type=R in Page0)                                                                                                                                                                                                                                                                                                |

| PAR0-5:        | Physical Address Registers (01H - 06H; Type=R/W in Page1)<br>These registers contain my Ethernet node address and are used to compare the destination adderss of incoming packets for acceptation or rejection.                                                                                                                                            |

| CURR:          | Current Page Register (07H; Type=R/W in Page1)<br>This register points to the page address of the first receive buffer page to be used for<br>a packet reception.                                                                                                                                                                                          |

MAR0-7: Multicast Address Register (08H - 0FH; Type=R/W in Page1) These registers provide filtering bits of multicast addresses hashed by the CRC logic.

#### 5.1.2.2. RTL8019AS Defined Registers

#### Page 0 (PS1=0, PS0=0)

Two registers are defined to contain the RTL8019AS chip ID.

| No. | Name    | Туре | Bit7-0                  |

|-----|---------|------|-------------------------|

| 0AH | 8019ID0 | R    | 50H (ASCII code of "P") |

| 0BH | 8019ID1 | R    | 70H (ASCII code of "p") |

#### Page 3(PS1=1, PS0=1)

#### Page3 Power Up Values before loading jumper states and 9346 contents

| No. | Name    | Туре | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|---------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00H | CR      | R/W  | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     |

| 01H | 9346CR  | R/W  | 0     | 0     | -     | -     | *     | *     | *     | *     |

| 02H | BPAGE   | R/W  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 03H | CONFIG0 | R/W  | 0     | 0     | *     | *     | *     | *     | 0     | 0     |

| 04H | CONFIG1 | R/W  | 1     | *     | *     | *     | *     | *     | *     | *     |

| 05H | CONFIG2 | R/W  | *     | *     | 0     | *     | *     | *     | *     | *     |

| 06H | CONFIG3 | R/W  | *     | *     | *     | *     | *     | 0     | 0     | 1     |

| 07H | TEST    | R/W  | -     | -     | -     | -     | -     | -     | -     | -     |

| 08H | CSNSAV  | R    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 09H | HLTCLK  | W    | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| 0AH | -       |      |       |       |       |       |       |       |       |       |

| 0BH | INTR    | R    | *     | *     | *     | *     | *     | *     | *     | *     |

| 0CH | FMWP    | W    |       |       |       |       |       |       |       |       |

| 0DH | CONFIG4 | R    | -     | -     | -     | -     | -     | -     | -     | *     |

| 0EH | -       |      |       |       |       |       |       |       |       |       |

|     |         |      |       |       |       |       |       |       |       |       |

| 0FH |         |      |       |       |       |       |       |       |       |       |

## **Page3** Content Descriptions

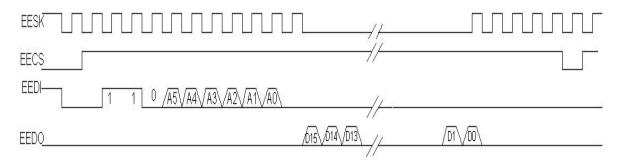

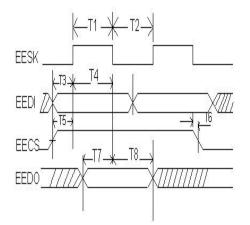

9346CR: 9346 Command Register (01H; Type=R/W except Bit0=R)

| Bit | Symbol |       | Description   |              |                                                           |  |  |

|-----|--------|-------|---------------|--------------|-----------------------------------------------------------|--|--|

| 7-6 | EEM1-0 | These | e 2 bits sele | ect the RTI  | L8019AS operating mode.                                   |  |  |

|     |        |       | EEM1          | EEM0         | Operating Mode                                            |  |  |

|     |        |       | 0             | 0            |                                                           |  |  |

|     |        |       | 0             | 1            | Normal (DP8390 compatible)<br>Auto-load:                  |  |  |

|     |        |       | 0             | 1            | Entering this mode will make the RTL8019AS                |  |  |

|     |        |       |               |              | load the contents of 9346 like when the                   |  |  |

|     |        |       |               |              | RSTDRV signal is asserted.                                |  |  |

|     |        |       |               |              | This auto-load operation will take about 2ms.             |  |  |

|     |        |       |               |              | After it is completed, the RTL8019AS goes back            |  |  |

|     |        |       |               |              | to the normal mode automatically                          |  |  |

|     |        |       |               |              | (EEM1=EEM0 =0) and the CR register is reset               |  |  |

|     |        |       |               |              | to 21H.                                                   |  |  |

|     |        |       | 1             | 0            | 9346 programming:                                         |  |  |

|     |        |       |               |              | In this mode, both the local & remote DMA                 |  |  |

|     |        |       |               |              | operation of 8390 are disabled. The 9346 can be           |  |  |

|     |        |       |               |              | directly accessed via bit3-0 which now reflect            |  |  |

|     |        |       |               |              | the states of EECS, EESK, EEDI, & EEDO pins respectively. |  |  |

|     |        |       | 1             | 1            | Config register write enable:                             |  |  |

|     |        |       | 1             | 1            | Before writing to the Page3 CONFIG1-3                     |  |  |

|     |        |       |               |              | registers, the RTL8019AS must be placed in this           |  |  |

|     |        |       |               |              | mode. This will prevent RTL8019AS's                       |  |  |

|     |        |       |               |              | configurations from accidental change.                    |  |  |

|     |        |       |               |              | ·                                                         |  |  |

| 5-4 | -      | Not u | sed.          |              |                                                           |  |  |

| 3   | EECS   | These | e bits reflec | et the state | of EECS, EESK, EEDI & EEDO pins in auto-load or           |  |  |

| 2   | EESK   | 9346  | programm      | ing mode.    |                                                           |  |  |

| 1   | EEDI   |       |               |              |                                                           |  |  |

| 0   | EEDO   |       |               |              |                                                           |  |  |

BPAGE: BROM Page Register (02H; Type=R/W)

This register selects a BROM page to be read by the host. Totally it can select 256 pages with 16k bytes per page. Thus the maximum BROM size is 256\*16k=4M bytes.

| Bit | Symbol |                                                                                      | Description |              |                                                       |  |  |  |

|-----|--------|--------------------------------------------------------------------------------------|-------------|--------------|-------------------------------------------------------|--|--|--|

| 7-6 | VERID  | Version ID: These two bits are defined as below.                                     |             |              |                                                       |  |  |  |

|     |        | Bit7                                                                                 | Bit6        | Type         | Mode                                                  |  |  |  |

|     |        | 1                                                                                    | 1           | R            | RTL8019                                               |  |  |  |

|     |        | 0                                                                                    | 0           | R            | RTL8019A                                              |  |  |  |

|     |        | 0                                                                                    | 0           | R/W          | RTL8019AS, these two bits are all "0"                 |  |  |  |

|     |        |                                                                                      |             |              | when power on, but can be written in                  |  |  |  |

|     |        |                                                                                      |             |              | RTL8019AS's config write enable                       |  |  |  |

|     |        |                                                                                      |             |              | mode (EEM0=EEM1=1). Software uses                     |  |  |  |

|     |        |                                                                                      |             |              | these differences to identify the chip.               |  |  |  |

|     |        |                                                                                      |             |              |                                                       |  |  |  |

| 5   | AUI    | This bit is set whe                                                                  | en exter    | nal MAU      | is used on AUI interface. Therefore it is set when in |  |  |  |

|     |        | 10Base5 mode or the AUI input pin is high.                                           |             |              |                                                       |  |  |  |

| 4   | PNPJP  | This bit is set when PNP jumper pin is pulled high externally.                       |             |              |                                                       |  |  |  |

| 3   | JP     | This bit reflects th                                                                 | he state    | of JP inp    | out. It, when set, indicates the RTL8019 is in jumper |  |  |  |

|     |        | mode.                                                                                |             |              |                                                       |  |  |  |

| 2   | BNC    | When set, this bit indicates that the RTL8019 is using the 10Base2 thin cable as its |             |              |                                                       |  |  |  |

|     |        | networking mediu                                                                     | ım. This    | s bit will l | be set in the following 2 cases:                      |  |  |  |

|     |        | (1) PL1=PL0=0 (a                                                                     | auto-det    | ect) and l   | ink test fails                                        |  |  |  |

|     |        | (2) PL1=PL0=1 (1                                                                     |             |              |                                                       |  |  |  |

| 1-0 | 0      | Always 0s.                                                                           |             |              |                                                       |  |  |  |

The following table describes the behavior of bits and pins for cabling media.

| Media Type               | AUI Input | Selected<br>Media | AUI Bit | BNC Bit | LEDBNC<br>Output | Original BNC bit in 8019<br>(For reference only) |

|--------------------------|-----------|-------------------|---------|---------|------------------|--------------------------------------------------|

| 10Base5                  | х         | AUI               | 1       | 0       | Ĺ                | 0                                                |

| 10Base2                  | Х         | BNC               | 0       | 1       | Н                | 1                                                |

| 10BaseT                  | Х         | UTP               | 0       | 0       | L                | 0                                                |

| Link disabled            |           |                   |         |         |                  |                                                  |

| Auto detect<br>Link OK   | х         | UTP               | 0       | 0       | L                | 0                                                |