# LOW POWER 3.3V CMOS FAST SRAM 256K (32K x 8-BIT)

**IDT71V256SA**

## **FEATURES**

- · Ideal for high-performance processor secondary cache

- Commercial (0° to 70°C) and Industrial (-40° to 85°C) temperature options

- · Fast access times:

- Commercial: 10/12/15/20ns

- Industrial: 15ns

- · Low standby current (maximum):

- 2mA full standby

- · Small packages for space-efficient layouts:

- 28-pin 300 mil SOJ

- 28-pin 300 mil plastic DIP (Commercial only)

- 28-pin TSOP Type I

- Produced with advanced high-performance CMOS technology

- · Inputs and outputs are LVTTL-compatible

- Single 3.3V(±0.3V) power supply

#### DESCRIPTION

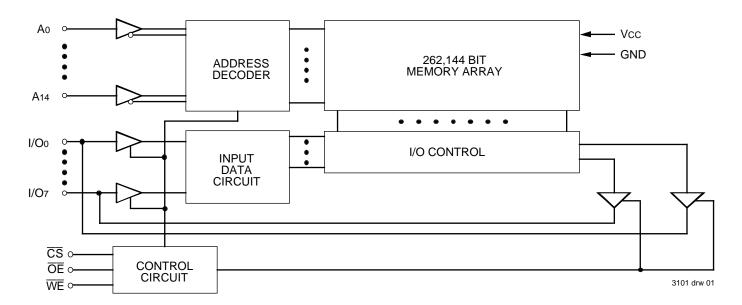

The IDT71V256SA is a 262,144-bit high-speed static RAM organized as 32K x 8. It is fabricated using IDT's high-performance, high-reliability CMOS technology.

The IDT71V256SA has outstanding low power characteristics while at the same time maintaining very high performance. Address access times of as fast as10 ns are ideal for 3.3V secondary cache in 3.3V desktop designs.

When power management logic puts the IDT71V256SA in standby mode, its very low power characteristics contribute to extended battery life. By taking  $\overline{CS}$  HIGH, the SRAM will automatically go to a low power standby mode and will remain in standby as long as  $\overline{CS}$  remains HIGH. Furthermore, under full standby mode ( $\overline{CS}$  at CMOS level, f=0), power consumption is guaranteed to always be less than 6.6mW and typically will be much smaller.

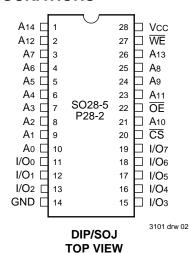

The IDT71V256SA is packaged in 28-pin 300 mil SOJ, 28-pin 300 mil plastic DIP, and 28-pin 300 mil TSOP Type I packaging.

## **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

# **PIN CONFIGURATIONS**

21 A 10 23 20 🗆 CS A11 🔲 24 19 🔲 I/O7 A 9 🔲 A 8 25 18 I/O6 A13 WE 26 17 🔲 I/O5 27 16 🔲 I/O4 Vcc □ 28 15 I/O3 SO28-8 A14 1 1 A12 2 2 A7 3 14 GND ] I/O2 12 I/O1 A 6 🔲 4 11 | I/Oo 10 A 0 9 A 1 A5 5 A4 6 5 A3 🔲 7 8 🗆 A 2

TSOP TOP VIEW

# **PIN DESCRIPTIONS**

| Name      | Description       |

|-----------|-------------------|

| A0-A14    | Addresses         |

| I/O0–I/O7 | Data Input/Output |

| CS        | Chip Select       |

| WE        | Write Enable      |

| ŌĒ        | Output Enable     |

| GND       | Ground            |

| Vcc       | Power             |

3101 tbl 01

# TRUTH TABLE(1)

| WE | CS  | ŌĒ | I/O    | Function       |

|----|-----|----|--------|----------------|

| Χ  | Н   | Χ  | High-Z | Standby (ISB)  |

| Х  | VHC | Χ  | High-Z | Standby (ISB1) |

| Н  | L   | Н  | High-Z | Output Disable |

| Н  | L   | L  | Dout   | Read           |

| L  | Ĺ   | X  | DIN    | Write          |

**NOTE:**1. H = VIH, L = VIL, X = Don't Care

3101 tbl 02

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol               | Rating                              | Value           | Unit |

|----------------------|-------------------------------------|-----------------|------|

| Vcc                  | Supply Voltage<br>Relative to GND   | -0.5 to +4.6    | V    |

| VTERM <sup>(2)</sup> | Terminal Voltage<br>Relative to GND | -0.5 to Vcc+0.5 | V    |

| TBIAS                | Temperature Under Bias              | -55 to +125     | °C   |

| Tstg                 | Storage Temperature                 | -55 to +125     | °C   |

| Рт                   | Power Dissipation                   | 1.0             | W    |

| lout                 | DC Output Current                   | 50              | mA   |

NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Input, Output, and I/O terminals; 4.6V maximum.

## **CAPACITANCE**

$(TA = +25^{\circ}C, f = 1.0MHz, SOJ package)$

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 3dV  | 6    | pF   |

| Соит   | Output Capacitance       | Vout = 3dV | 7    | pF   |

NOTE:

3101 tbl 04

3101 tbl 03

This parameter is determined by device characterization, but is not production tested.

# RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Grade Temperature |    | Vcc             |

|------------|-------------------|----|-----------------|

| Commercial | 0°C to +70°C      | 0V | $3.3V \pm 0.3V$ |

| Industrial | -40°C to +85°C    | 0V | $3.3V \pm 0.3V$ |

3101 tbl 05

# RECOMMENDED DC OPERATING CONDITIONS

| Symbol | Parameter                   | Min.                | Тур. | Max.    | Unit |

|--------|-----------------------------|---------------------|------|---------|------|

| Vcc    | Supply Voltage              | 3.0                 | 3.3  | 3.6     | V    |

| GND    | Supply Voltage              | 0                   | 0    | 0       | V    |

| VIH    | Input High Voltage - Inputs | 2.0                 | _    | 5.0     | V    |

| VIH    | Input High Voltage - I/O    | 2.0                 | _    | Vcc+0.3 | V    |

| VIL    | Input Low Voltage           | -0.3 <sup>(1)</sup> | _    | 0.8     | V    |

NOTE:

3101 tbl 06

1. VIL (min.) = -2.0V for pulse width less than 5ns, once per cycle.

# DC ELECTRICAL CHARACTERISTICS<sup>(1, 2)</sup>

$(VCC = 3.3V \pm 0.3V, VLC = 0.2V, VHC = VCC - 0.2V)$

| Symbol | Parameter                                                                                                                                                                                                              | 71V256SA10 <sup>(3)</sup> | 71V256SA12 <sup>(3)</sup> | 71V256SA15 | 71V256SA20 <sup>(3)</sup> | Unit |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|------------|---------------------------|------|

| Icc    | Dynamic Operating Current $\overline{CS} \le VIL$ , Outputs Open, $VCC = Max.$ , $f = fMAX^{(2)}$                                                                                                                      | 100                       | 90                        | 85         | 85                        | mA   |

| ISB    | Standby Power Supply Current (TTL Level) $\overline{\text{CS}}$ = ViH, Vcc = Max., Outputs Open, f = fMax <sup>(2)</sup>                                                                                               | 20                        | 20                        | 20         | 20                        | mA   |

| ISB1   | Full Standby Power Supply Current (CMOS Level) $\overline{\text{CS}} \geq \text{VHc}$ , $\text{Vcc} = \text{Max.}$ , Outputs Open, $\text{f} = 0^{(2)}$ , $\text{VIN} \leq \text{VLC}$ or $\text{VIN} \geq \text{VHc}$ | 2                         | 2                         | 2          | 2                         | mA   |

## NOTES:

3101 tbl 07

- 1. All values are maximum guaranteed values.

- 2.  $f_{MAX} = 1/t_{RC}$ , only address inputs cycling at  $f_{MAX} = 0$  means that no inputs are cycling.

- 3. Commercial temperature range only.

# DC ELECTRICAL CHARACTERISTICS

$Vcc = 3.3V \pm 0.3V$

|        |                        |                                                      | IDT71V256SA |      |      |      |

|--------|------------------------|------------------------------------------------------|-------------|------|------|------|

| Symbol | Parameter              | Test Condition                                       | Min.        | Тур. | Max. | Unit |

| LI     | Input Leakage Current  | Vcc = Max., Vin = GND to Vcc                         | _           | _    | 2    | μΑ   |

| ILO    | Output Leakage Current | Vcc = Max., $\overline{CS}$ = Viн, Vouт = GND to Vcc | _           | _    | 2    | μΑ   |

| Vol    | Output Low Voltage     | IoL = 8mA, Vcc = Min.                                | _           | _    | 0.4  | V    |

| Vон    | Output High Voltage    | IOH = -4mA, $VCC = Min$ .                            | 2.4         | _    | _    | V    |

3101 tbl 08

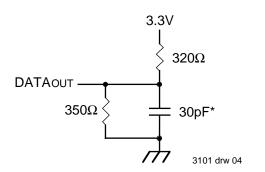

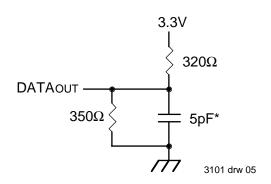

# **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise/Fall Times         | 3ns                 |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

| AC Test Load                  | See Figures 1 and 2 |

3101 tbl 09

Figure 1. AC Test Load

Figure 2. AC Test Load (for tcLz, toLz, tcHz, toHz, toW, tWHz)

\*Includes scope and jig capacitances

# AC ELECTRICAL CHARACTERISTICS (Vcc = $3.3V \pm 0.3V$ )

|                     |                                    | 71V256SA10 <sup>(2)</sup> |      | 71V256 | SA12 <sup>(2)</sup> | 71V256SA15 |      | 71V256SA20 <sup>(2)</sup> |      |      |

|---------------------|------------------------------------|---------------------------|------|--------|---------------------|------------|------|---------------------------|------|------|

| Symbol              | Parameter                          | Max.                      | Min. | Min.   | Max.                | Min.       | Max. | Min.                      | Max. | Unit |

| Read C              | Read Cycle                         |                           |      | ,      |                     | •          |      |                           |      |      |

| tRC                 | Read Cycle Time                    | 10                        | _    | 12     |                     | 15         | 1    | 20                        |      | ns   |

| tAA                 | Address Access Time                | _                         | 10   | _      | 12                  |            | 15   | _                         | 20   | ns   |

| tACS                | Chip Select Access Time            | _                         | 10   | _      | 12                  |            | 15   | _                         | 20   | ns   |

| tcLz <sup>(1)</sup> | Chip Select to Output in Low-Z     | 5                         | _    | 5      |                     | 5          |      | 5                         |      | ns   |

| tcHz <sup>(1)</sup> | Chip Select to Output in High-Z    | 0                         | 8    | 0      | 8                   | 0          | 9    | 0                         | 10   | ns   |

| tOE                 | Output Enable to Output Valid      | _                         | 6    | _      | 6                   |            | 7    | _                         | 8    | ns   |

| toLZ <sup>(1)</sup> | Output Enable to Output in Low-Z   | 3                         | _    | 3      |                     | 0          |      | 0                         |      | ns   |

| tonz <sup>(1)</sup> | Output Disable to Output in High-Z | 2                         | 6    | 2      | 6                   | 0          | 7    | 0                         | 8    | ns   |

| tон                 | Output Hold from Address Change    | 3                         | _    | 3      | _                   | 3          |      | 3                         | _    | ns   |

| Write C             | ycle                               |                           |      |        |                     |            |      |                           |      |      |

| twc                 | Write Cycle Time                   | 10                        | _    | 12     | _                   | 15         | _    | 20                        | _    | ns   |

| taw                 | Address Valid to End-of-Write      | 9                         | _    | 9      | _                   | 10         | _    | 15                        | _    | ns   |

| tcw                 | Chip Select to End-of-Write        | 9                         | _    | 9      | _                   | 10         | _    | 15                        | _    | ns   |

| tas                 | Address Set-up Time                | 0                         | —    | 0      | _                   | 0          | _    | 0                         |      | ns   |

| twp                 | Write Pulse Width                  | 9                         | _    | 9      | _                   | 10         | _    | 15                        | _    | ns   |

| twr                 | Write Recovery Time                | 0                         | _    | 0      | _                   | 0          | _    | 0                         |      | ns   |

| tow                 | Data to Write Time Overlap         | 6                         | _    | 6      | _                   | 7          | _    | 8                         | _    | ns   |

| tDH                 | Data Hold from Write Time          | 0                         | _    | 0      | _                   | 0          | _    | 0                         | _    | ns   |

| tow <sup>(1)</sup>  | Output Active from End-of-Write    | 4                         | _    | 4      | _                   | 4          | _    | 4                         | _    | ns   |

| twHz <sup>(1)</sup> | Write Enable to Output in High-Z   | 1                         | 8    | 1      | 8                   | 1          | 9    | 1                         | 10   | ns   |

## NOTE:

This parameter guaranteed with the AC test load (Figure 2) by device characterization, but is not production tested.

2. Commercial temperature range only.

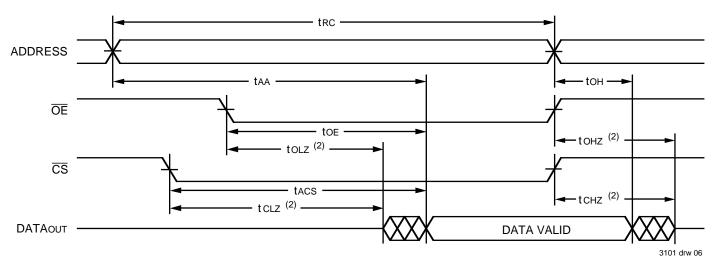

# TIMING WAVEFORM OF READ CYCLE NO. 1<sup>(1)</sup>

#### NOTES:

- 1. WE is HIGH for Read cycle.

- 2. Transition is measured ±200mV from steady state.

3101 tbl 10

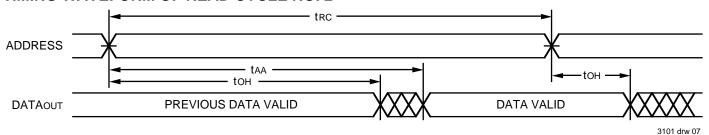

# TIMING WAVEFORM OF READ CYCLE NO. 2<sup>(1, 2, 4)</sup>

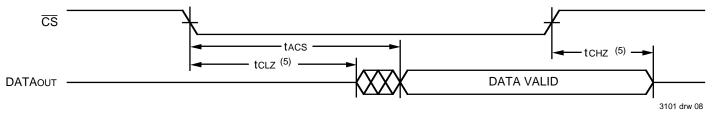

# TIMING WAVEFORM OF READ CYCLE NO. 3<sup>(1, 3, 4)</sup>

#### NOTES:

- 1. WE is HIGH for Read cycle.

- 2. Device is continuously selected,  $\overline{CS}$  is LOW.

- 3. Address valid prior to or coincident with  $\overline{\text{CS}}$  transition LOW.

- 4.  $\overline{\text{OE}}$  is LOW.

- 5. Transition is measured ±200mV from steady state.

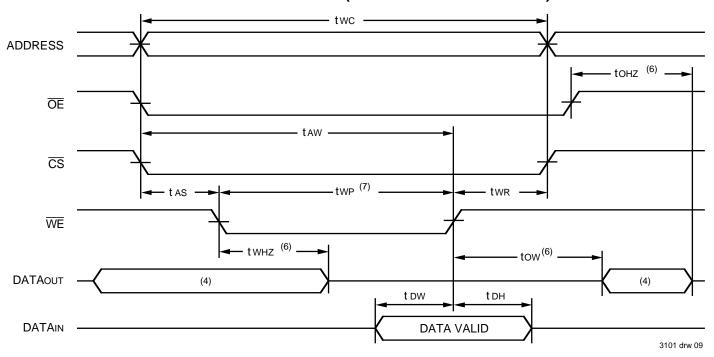

# TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED TIMING)(1, 2, 3, 5, 7)

## NOTES:

- 1. WE or CS must be HIGH during all address transitions.

- 2. A write occurs during the overlap of a LOW  $\overline{\text{CS}}$  and a LOW  $\overline{\text{WE}}$ .

- 3. twn is measured from the earlier of  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going HIGH to the end of the write cycle.

- 4. During this period, I/O pins are in the output state so that the input signals must not be applied.

- 5. If the CS LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high-impedance state.

- 6. Transition is measured ±200mV from steady state.

- 7. If  $\overline{OE}$  is LOW during a  $\overline{WE}$  controlled write cycle, the write pulse width must be the larger of twp or (twhz + tow) to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If  $\overline{OE}$  is HIGH during a  $\overline{WE}$  controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twp.

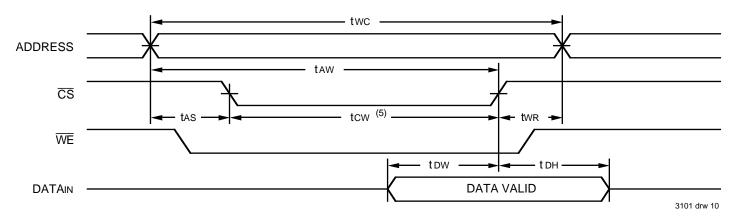

# TIMING WAVEFORM OF WRITE CYCLE NO. 2 ( $\overline{\text{CS}}$ CONTROLLED TIMING) $^{(1, 2, 3, 4)}$

#### NOTES:

- 1. WE or CS must be HIGH during all address transitions.

- 2. A write occurs during the overlap of a LOW  $\overline{\text{CS}}$  and a LOW  $\overline{\text{WE}}$ .

- 3. twn is measured from the earlier of  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going HIGH to the end of the write cycle.

- 4. If the  $\overline{\text{CS}}$  LOW transition occurs simultaneously with or after the  $\overline{\text{WE}}$  LOW transition, the outputs remain in a high-impedance state.

- 5. If  $\overline{OE}$  is LOW during a  $\overline{WE}$  controlled write cycle, the write pulse width must be the larger of twp or (twhz + tow) to allow the I/O drivers to turn off and data to be placed on the bus for the required tow. If  $\overline{OE}$  is HIGH during a  $\overline{WE}$  controlled write cycle, this requirement does not apply and the write pulse can be as short as the spectified twp.

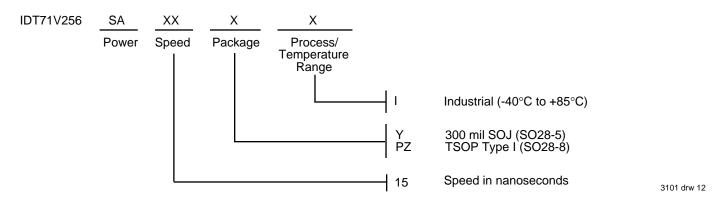

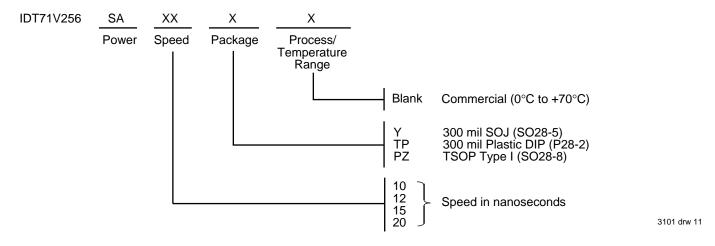

## **ORDERING INFORMATION - COMMERCIAL**

## **ORDERING INFORMATION - INDUSTRIAL**