## F2914 Datasheet

## High Reliability SP4T RF Switch

50 MHz to 8000 MHz

#### **GENERAL DESCRIPTION**

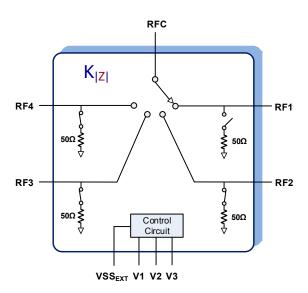

The F2914 is a high reliability, low insertion loss, 50  $\Omega$ SP4T absorptive RF switch designed for a multitude of RF applications including wireless communications. This device covers a broad frequency range from 50 MHz to 8000 MHz. In addition to providing low insertion loss, the F2914 also delivers excellent linearity and isolation performance while providing a  $50 \Omega$  termination to the unused RF input ports. The F2914 also includes a patent pending constant impedance  $(K_7)$  feature.  $K_7$  improves system hot switching ruggedness, minimizes LO pulling in VCOs, and reduces phase and amplitude variations in distribution networks. It is also ideal for dynamic switching / selection between two or more amplifiers while avoiding damage to upstream /downstream sensitive devices such as PAs and ADCs.

The F2914 uses a single positive supply voltage supporting three logic control pins using either 3.3 V or 1.8 V control logic. Connecting a negative voltage to pin 20 disables the internal negative voltage generator and becomes the negative supply.

#### **COMPETITIVE ADVANTAGE**

The F2914 provides constant impedance in all RF ports during transitions improving a system's hot-switching ruggedness. The device also supports high power handling, and high isolation; particularly important for DPD receiver use.

- ✓ Constant impedance K<sub>|Z|</sub> during switching transition

- ✓ RFX to RFC Isolation = 50 dB\*

- ✓ Insertion Loss = 1.1 dB\*

- ✓ IIP3: +60 dBm\*

- ✓ Extended temperature: -40 °C to +105 °C

- \* 4 GHz

#### **APPLICATIONS**

- Base Station 2G, 3G, 4G

- Portable Wireless

- Repeaters and E911 systems

- Digital Pre-Distortion

- Point to Point Infrastructure

- Public Safety Infrastructure

- Military Systems, JTRS radios

- Cable Infrastructure

- Test / ATE Equipment

#### **FEATURES**

- Four symmetric, absorptive RF ports

- High Isolation: 50 dB @ 4000 MHz

- Low Insertion Loss: 1.1 dB @ 4000 MHz

- · High Linearity:

- o IIP2 of 114 dBm @ 2000 MHz

- $_{\odot}$  IIP3 of 60 dBm @ 4000 MHz

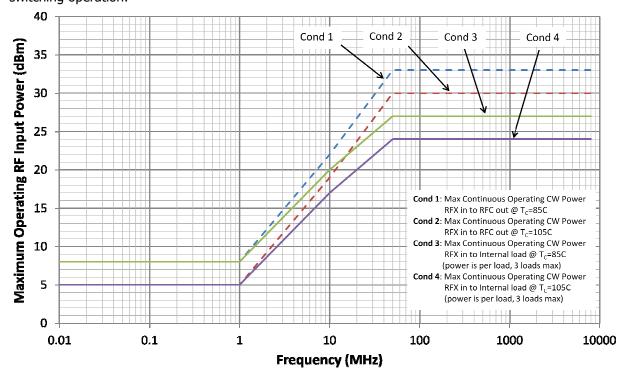

- High Operating Power Handling:

- o 33 dBm CW on selected RF port

- o 27 dBm on terminated ports

- Single 2.7 V to 5.5 V supply voltage

- External Negative Supply Option

- 3.3 V and 1.8 V compatible control logic

- Operating temperature -40 °C to +105 °C

- 4 mm x 4 mm 24 pin QFN package

- Pin compatible with competitors

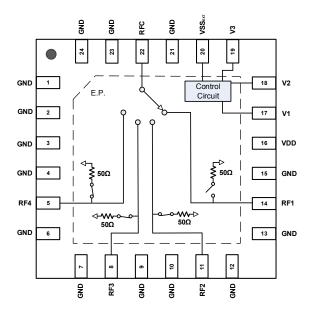

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **ORDERING INFORMATION**

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                                                                | Symbol               | Min  | Max                                      | Units |

|----------------------------------------------------------------------------------------------------------|----------------------|------|------------------------------------------|-------|

| V <sub>DD</sub> to GND                                                                                   | $V_{DD}$             | -0.3 | +6.0                                     | V     |

| V1, V2, V3 to GND                                                                                        | $V_{CNTL}$           | -0.3 | Minimum<br>( 3.6, V <sub>DD</sub> + 0.3) | V     |

| RF1, RF2, RF3, RF4, RFC to GND                                                                           | $V_{RF}$             | -0.3 | +0.3                                     | V     |

| VSS <sub>EXT</sub> to GND                                                                                | $V_{EXT}$            | -4.0 | +0.3                                     | V     |

| Input Power for any one selected RF through port. ( $V_{DD}$ applied @ 2GHz and $T_{C} = +85^{\circ}C$ ) | P <sub>MAXTHRU</sub> |      | 37                                       | dBm   |

| Input Power for any one selected RF terminated port .( $V_{DD}$ applied @ 2GHz and $T_{C} = +85$ °C)     | P <sub>MAXTERM</sub> |      | 30                                       | dBm   |

| Input Power for RFC when in the all off state. $(V_{DD}$ applied @ 2GHz and $T_{C} = +85^{\circ}C)$      | P <sub>MAXCOM</sub>  |      | 33                                       | dBm   |

| Continuous Power Dissipation (T <sub>C</sub> = 95 °C Max)                                                |                      |      | 3                                        | W     |

| Maximum Junction Temperature                                                                             | $T_{Jmax}$           |      | +140                                     | °C    |

| Storage Temperature Range                                                                                | T <sub>ST</sub>      | -65  | +150                                     | °C    |

| Lead Temperature (soldering, 10s)                                                                        | $T_LEAD$             |      | +260                                     | °C    |

| ESD Voltage— HBM (Per JESD22-A114)                                                                       | $V_{ESDHBM}$         |      | Class 1C (1000 V)                        |       |

| ESD Voltage – CDM (Per JESD22-C101)                                                                      | $V_{ESDCDM}$         |      | Class III (1000 V)                       |       |

$T_C$  = Temperature of the exposed paddle

Stresses above those listed above may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL AND MOISTURE CHARACTERISTICS**

| $\theta_{JA}$ (Junction – Ambient)                                                 | 41 °C/W  |

|------------------------------------------------------------------------------------|----------|

| $\theta_{\text{JC}}$ (Junction – Case) [The Case is defined as the exposed paddle] | 6.4 °C/W |

| Moisture Sensitivity Rating (Per J-STD-020)                                        | MSL1     |

#### F2914 RECOMMENDED OPERATING CONDITIONS

| Parameter                                           | Symbol             | Co                   | nditions                                    | Min  | Тур  | Max  | Units |

|-----------------------------------------------------|--------------------|----------------------|---------------------------------------------|------|------|------|-------|

|                                                     |                    | Pin 20 grou          | nded                                        | 2.7  |      | 5.5  |       |

| Supply Voltage (s)                                  | $V_{DD}$           | Pin 20 Drive         | en with VSS <sub>EXT</sub>                  | 2.7  |      | 5.5  | V     |

|                                                     | VSS <sub>EXT</sub> | Negative Su          | ıpply <sup>1</sup>                          | -3.6 | -3.4 | -3.2 |       |

| Operating Temp Range                                | $T_{CASE}$         | Exposed Pa           | ddle Temperature                            | -40  |      | +105 | °C    |

| RF Frequency Range                                  | $F_RF$             |                      |                                             | 50   |      | 8000 | MHz   |

| RF Continuous                                       | D                  | Selected Po          | rt                                          |      |      | 33   | dBm   |

| Input CW Power <sup>2</sup>                         | $P_{RF}$           | Terminated           | Ports <sup>3</sup>                          |      |      | 27   | ubili |

|                                                     |                    | DEC                  | Switch to RF1 thru RF4.                     |      |      | 27   |       |

| RF Continuous                                       |                    | RFC as<br>the input  | Switched into or out of all off state.      |      |      | 24   | dDm   |

| Input CW Power for<br>Hot RF Switching <sup>2</sup> | P <sub>RFSW</sub>  | RF1 thru             | Switched to RFC or into Term <sup>3</sup> . |      |      | 27   | dBm   |

|                                                     |                    | RF5 as<br>the inputs | Switch into or out of all off condition.    |      |      | 27   |       |

| RF1 - 4 Port Impedance                              | $Z_{RFx}$          |                      |                                             |      | 50   | _    | Ω     |

| RFC Port Impedance                                  | $Z_{RFC}$          |                      |                                             |      | 50   |      | 75    |

Note 1: For normal operation, connect  $VSS_{EXT} = 0 \text{ V (pin 20)}$  to GND to enable the internal negative voltage generator. By applying  $VSS_{EXT}$  to pin 20, the negative voltage generator is disabled thereby completely eliminating any generator spurious responses.

Note 2: Levels based on  $T_C \le 85$  °C. See Figure 1 power derating curve for higher case temperatures.

Note 3: In any of the insertion loss modes or switching into any insertion loss mode, the 3 remaining terminated port paths can be each exposed to the maximum stated power level during continuous or hot switching operation.

Figure 1 - MAXIMUM RF INPUT POWER VS. RF FREQUENCY

#### F2914 SPECIFICATION

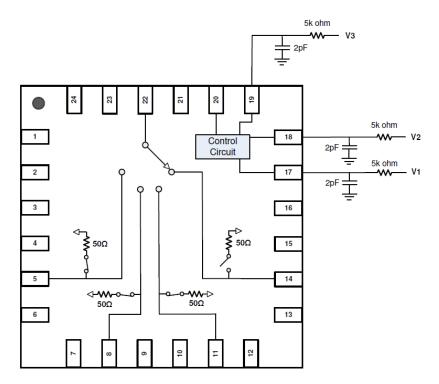

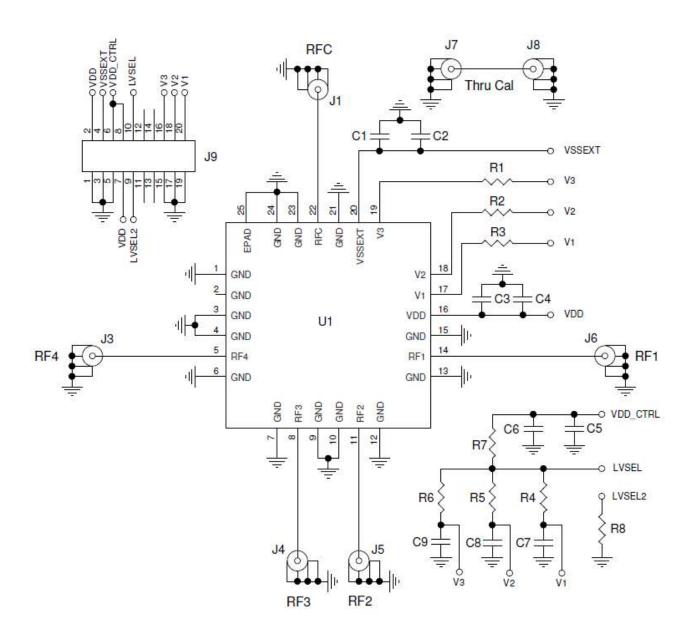

Typical Application Circuit, Normal mode ( $V_{DD}=3.3 \text{ V}$ ,  $VSS_{EXT}=0 \text{ V}$ ) or Bypass mode ( $V_{DD}=3.3 \text{ V}$ ,  $VSS_{EXT}=-3.3 \text{ V}$ ),  $T_{C}=+25$  °C,  $F_{RF}=2000$  MHz, Input power = 0 dBm,  $Z_{S}=Z_{L}=50$   $\Omega$ , RFX = one of the four input ports, PCB board trace and connector losses are de-embedded unless otherwise noted.

| Parameter                                          | Symbol               |                                        | Condi                     | itic      | ons                             | Min  | Тур        | Max                      | Units  |

|----------------------------------------------------|----------------------|----------------------------------------|---------------------------|-----------|---------------------------------|------|------------|--------------------------|--------|

| Logic Input High Threshold                         | $V_{\mathrm{IH}}$    |                                        |                           |           |                                 | 1.1  |            | Minimum $(3.6, V_{DD})$  | V      |

| Logic Input Low Threshold                          | $V_{\mathrm{IL}}$    |                                        |                           |           | -0.3                            |      | 0.6        | V                        |        |

| Logic Current                                      | $I_{IH}$ , $I_{IL}$  | For each                               | control pin               |           |                                 | -2   |            | +2                       | μΑ     |

| DC Current (V <sub>DD</sub> )                      | ${ m I}_{ m DD}$     | Normal M<br>Bypass M                   |                           |           | V or 1.8V Logic V or 1.8V Logic |      | 290<br>270 | <i>360</i><br><i>340</i> | μΑ     |

| DC Current (VSS <sub>EXT</sub> )                   | $I_{VSS}$            | VSS <sub>EXT</sub> =                   |                           |           |                                 |      | -44        | -60                      | μA     |

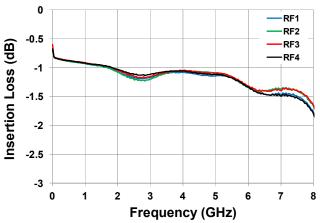

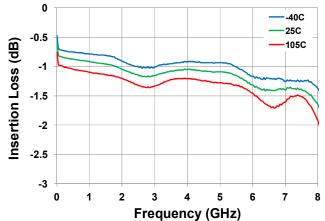

| 2 3 Santana (Tasaki)                               | - 133                | 900 MHz                                |                           |           |                                 |      | 0.90       | 1.41                     | Par. 1 |

|                                                    |                      | 2100 MHz                               | <u> </u>                  |           |                                 |      | 1.1        | 1.5                      |        |

| Insertion Loss                                     | IL                   | 2700 MHz                               | <u> </u>                  |           |                                 |      | 1.15       | 1.6                      | dB     |

| RFX to RFC                                         |                      | 2700 MHz                               | z – 4000 Mł               | Hz        |                                 |      | 1.2        | 1.65 <sup>2</sup>        |        |

|                                                    |                      |                                        | z – 8000 MH               |           |                                 |      | 1.8        |                          |        |

|                                                    |                      |                                        | – 900 MHz                 |           |                                 | 56   | 62.2       |                          |        |

|                                                    |                      |                                        | – 2100 MHz                |           |                                 | 48.5 | 55.4       |                          |        |

| Minimum Isolation                                  | ISOC                 | 2100 MHz                               | z – 2700 Mł               | Hz        |                                 | 48   | 53.5       |                          | dB     |

| RFX to RFC                                         |                      | 2700 MHz                               | z – 4000 Mł               | Hz        |                                 | 44   | 50         |                          |        |

|                                                    |                      | 4000 MHz – 8000 MHz                    |                           |           | 29.5                            | 35.7 |            |                          |        |

|                                                    |                      |                                        | – 900 MHz                 |           |                                 | 55   | 60.3       |                          |        |

| Minimum Isolation                                  | ISOX                 | 900 MHz – 2100 MHz                     |                           |           | 49.5                            | 53.6 |            | dB                       |        |

|                                                    |                      | 2100 MHz – 2700 MHz                    |                           |           | 47                              | 52   |            |                          |        |

| RFX to RFX                                         |                      | 2700 MHz – 4000 MHz                    |                           |           | 43                              | 47.6 |            |                          |        |

|                                                    |                      | 4000 MHz – 8000 MHz                    |                           |           | 29                              | 36   |            |                          |        |

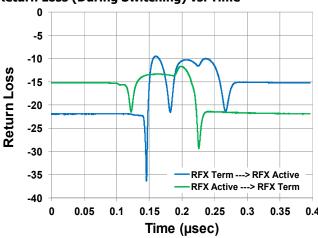

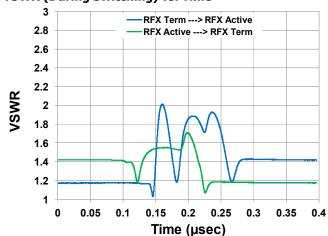

| Maximum RFX Port VSWR                              | VCMD                 | From RF                                | X Active to               | o RI      | FX Term                         |      | 1.7:1      |                          |        |

| During Switching                                   | VSWR <sub>⊤</sub>    | From RF                                | X Term to                 | RF        | X Active                        |      | 2:1        |                          | -      |

| Minimum Return Loss<br>(RFC Port )                 | $RFC_{RL}$           | 400 MHz                                | – 4000 MH                 | łz        |                                 |      | 15         |                          | dB     |

| Minimum Return Loss                                | DE1/                 | 400 1411                               | 4000 1411                 |           | Active                          |      | 13         |                          | in.    |

| (RFX Port )                                        | RFX <sub>RL</sub>    | 400 MHz                                | –4000 MHz                 | -         | Terminated                      |      | 17         |                          | dB     |

| Input 0.1dB Compression <sup>3</sup>               | ICP <sub>0.1dB</sub> |                                        |                           |           | •                               |      | 35         |                          | dBm    |

| Input IP2                                          | IIP2                 |                                        | = RFX, P <sub>IN</sub> :  |           | 2010 MHz<br>20 dBm / tone       |      | 114        |                          | dBm    |

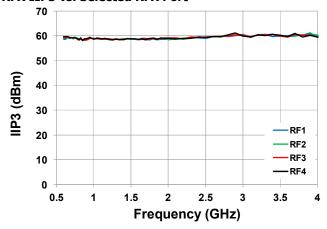

|                                                    |                      | $\Delta F = 1 M$                       | 1Hz                       |           | F <sub>RF</sub> = 2000 MHz      |      | 59.5       |                          |        |

| Input IP3                                          | IIP3                 | RF Input                               |                           | -         | $F_{RF} = 4000 \text{ MHz}$     |      | 60         |                          | dBm    |

|                                                    |                      | $P_{IN} = +20$                         | dBm / ton                 |           |                                 |      |            | 2.45                     |        |

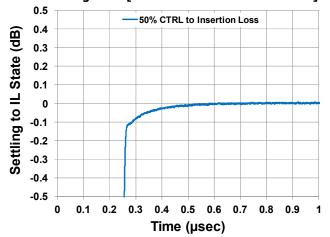

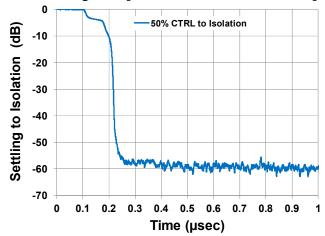

| Switching Time <sup>4</sup>                        |                      | D                                      | 50% CTRL                  |           |                                 |      | 256        | 345                      | ns     |

|                                                    | $T_SW$               | Bypass<br>Mode                         | 50% CTRL                  |           |                                 |      | 256        | 345                      |        |

|                                                    | 344                  | Mode 50% CTRL to R<br>+/- 0.1 dB of I. |                           |           |                                 | 285  |            |                          |        |

| M · C · I · D · 5                                  | CIM                  | Pin 20 =                               |                           |           |                                 |      | 25         |                          |        |

| Maximum Switching Rate⁵                            | $SW_{RATE}$          | Pin 20 = VSS <sub>EXT</sub> applied    |                           |           | 290                             |      | kHz        |                          |        |

| Maximum spurious level on any RF port <sup>6</sup> | Spur <sub>MAX</sub>  | RF ports t<br>RFX conn                 | terminated<br>ected to RF | into<br>C | 50Ω                             |      | -120       |                          | dBm    |

- Note 1 Items in min/max columns in **bold italics** are Guaranteed by Test.

- Note 2 Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

- Note 3 The input 0.1dB compression point is a linearity figure of merit. Refer to Absolute Maximum Ratings section for the maximum RF input power and Figure 1 for maximum operating RF input power.

- Note  $4 F_{RF} = 1GHz$ .

- Note 5 Minimum time required between switching of states = 1/ (Maximum Switching Rate).

- Note 6 Spurious due to on-chip negative voltage generator. Typical generator fundamental frequency is 2.2 MHz.

Table 1: 3-Pin Switch Control Truth Table

| Mode    | V3 | V2 | V1 |

|---------|----|----|----|

| RF4 on* | 0  | 0  | 0  |

| RF1 on  | 0  | 0  | 1  |

| RF2 on  | 0  | 1  | 0  |

| RF3 on  | 0  | 1  | 1  |

| RF4 on  | 1  | 0  | 0  |

| All off | 1  | 0  | 1  |

| All off | 1  | 1  | 0  |

| All off | 1  | 1  | 1  |

<sup>\*</sup> Redundant state with state "100"

**Table 2: 2-Pin Switch Control Truth Table** 1,2

| Mode   | V2 | V1 |

|--------|----|----|

| RF4 on | 0  | 0  |

| RF1 on | 0  | 1  |

| RF2 on | 1  | 0  |

| RF3 on | 1  | 1  |

Note 1 - Pin 19 (V3) must be grounded for 2-pin control.

Note 2 - 2-pin control can be used if All Off mode is not required.

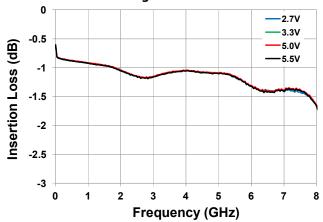

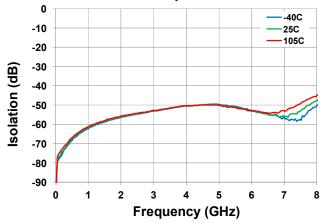

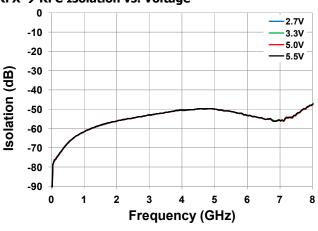

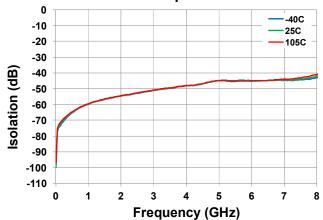

## **Typical Operating Conditions (TOC)**

Unless otherwise noted for the TOC graphs on the following pages, the following conditions apply.

- $V_{DD} = 3.3 \text{ V}.$

- T<sub>CASE</sub> = +25 °C (T<sub>CASE</sub> = Temperature of exposed paddle).

- $F_{RF} = 2000 \text{ MHz}.$

- RFX is the driven RF port and RFC is the output port.

- Pin = 10 dBm for all small signal tests.

- Pin = +15 dBm/tone applied to selected RFX port for two tone linearity tests.

- Two tone frequency spacing = 5 MHz.

- $Z_S = Z_L = 50$  ohms.

- All unused RF ports terminated into 50 ohms.

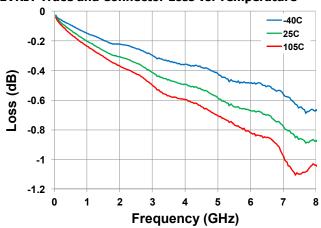

- For Insertion Loss and Isolation plots, RF trace and connector losses are de-embedded (see EVKIT Board and Connector loss plot).

- Plots for Isolation and Insertion Loss over temperature and voltage are for a typical path. For performance of a specific path, refer to the online S-Parameter file.

## Typical Operating Conditions (-1-)

#### **Insertion Loss vs. Temperature**

#### **Insertion Loss vs. Voltage**

**RFX** → **RFC** Isolation vs. Temperature

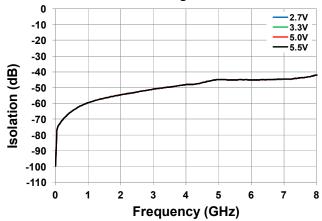

#### RFX → RFC Isolation vs. Voltage

RFX → RFX Isolation vs. Temperature

## Typical Operating Conditions (-2-)

#### RFX → RFX Isolation vs. Voltage

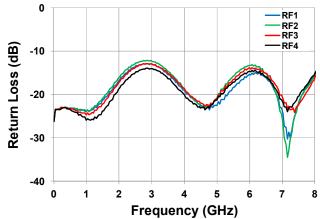

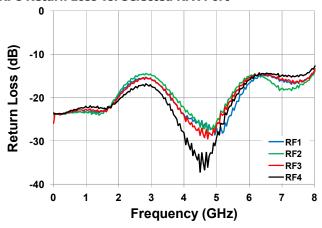

#### **RFX Return Loss vs. Selected RFX Port**

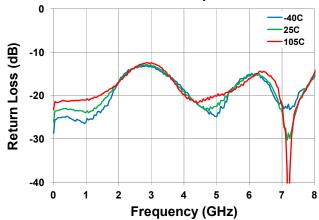

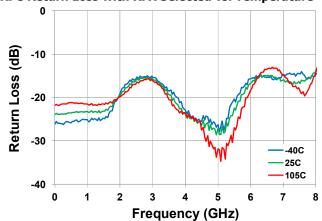

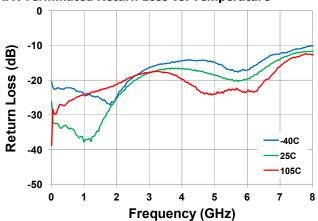

#### **RFX Selected Return Loss vs. Temperature**

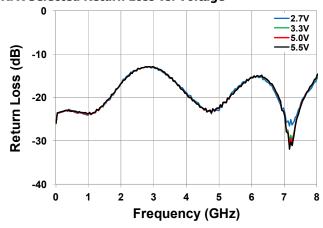

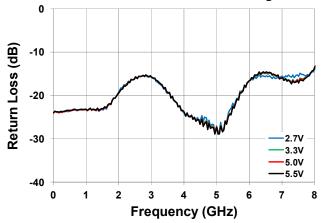

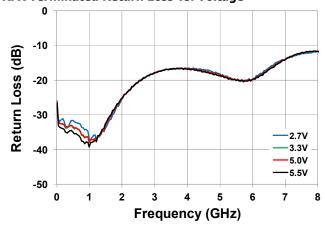

**RFX Selected Return Loss vs. Voltage**

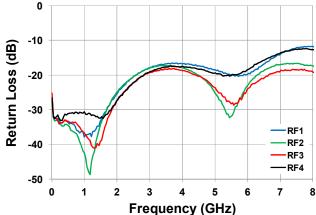

#### **RFC Return Loss vs. Selected RFX Port**

**RFC Return Loss with RFX Selected vs. Temperature**

## Typical Operating Conditions (-3-)

### **RFX Terminated Return Loss vs. RFX Port**

#### **RFX Terminated Return Loss vs. Temperature**

**RFX Terminated Return Loss vs. Voltage**

#### **Return Loss (During Switching) vs. Time**

VSWR (During Switching) vs. Time

## Typical Operating Conditions (-4-)

#### **RFX Switching Time [RFX Terminated to RFX Active]**

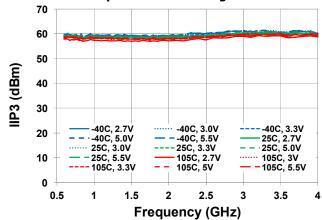

#### **RFX IIP3 vs. Selected RFX Port**

#### **EVKIT Trace and Connector Loss vs. Temperature**

#### **RFX Switching Time [RFX Active to RFX Terminated]**

#### **RFX IIP3 vs. Temperature and Voltage**

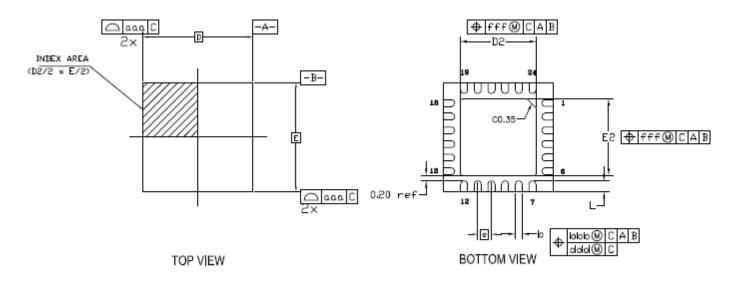

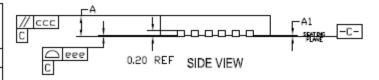

#### **PACKAGE DRAWING**

(4 mm x 4 mm 24-pin QFN), NBG24

#### NOTE: THE F2914 USES THE P3 EXPOSED PADDLE DIMENSIONS NOTED BELOW

| SYMBOL | DIMENSION |         |      |  |  |  |

|--------|-----------|---------|------|--|--|--|

|        | MIN       | NOM     | MAX  |  |  |  |

| D2     | SEE       | EPAD OP | ПОП  |  |  |  |

| E2     | SEE       | EPAD OP | ПОП  |  |  |  |

| L      | 0.30      | 0.40    | 0.50 |  |  |  |

| D      | 4.00 BSC  |         |      |  |  |  |

| E      | 4.00 BSC  |         |      |  |  |  |

| е      | 0.50 BSC  |         |      |  |  |  |

| Α      | 0.70      | 0.75    | 0.80 |  |  |  |

| A1     | 0.00      | 0.02    | 0.05 |  |  |  |

| b      | .20       | .25     | .30  |  |  |  |

| aaa    |           | 0.15    |      |  |  |  |

| bbb    | 0.10      |         |      |  |  |  |

| ccc    | 0.10      |         |      |  |  |  |

| ddd    | 0.05      |         |      |  |  |  |

| eee    |           | 0.08    |      |  |  |  |

| fff    |           | 0.10    |      |  |  |  |

## EPAD OPTIONS:

| SYMBOL |      | Р3   |      |

|--------|------|------|------|

| ~      | MIN  | NOM  | MAX  |

| D2     | 2.60 | 2.70 | 2.80 |

| E2     | 2.60 | 2.70 | 2.80 |

## NOTES:

- ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982

- 1. 2. ALL DIMENSIONS ARE IN MILLIMETERS.

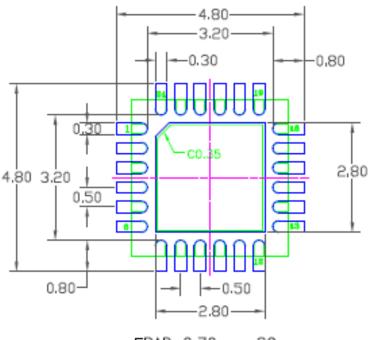

#### **LAND PATTERN DIMENSION**

EPAD 2.70mm SQ

# Land Pattern to Support 2.7 mm x 2.7 mm Exposed Paddle Version (See Version P3 of Package Drawing)

#### NOTES:

- ALL DIMENSION ARE IN mm. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW. AS VIEWED ON PCB.

- 3. COMPONENT OUTLINE SHOW FOR REFERENCE IN GREEN.

- 4. LAND PATTERN IN BLUE. NSMD PATTERN ASSUMED.

- LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

## **PIN DIAGRAM**

## **PIN DESCRIPTION**

| Pin                                             | Name               | Function                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 4, 6, 7, 9, 10, 12,<br>13, 15, 21, 23, 24 | GND                | Ground these pins as close to the device as possible.                                                                                                                                                                                                                      |

| 2                                               | GND                | This pin is internally connected to the exposed paddle. This pin can be left open or grounded. Note: The EVKIT layout has a floating RF trace connected to this pin to make the board compatible with the F2915.                                                           |

| 5                                               | RF4                | RF4 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 8                                               | RF3                | RF3 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 11                                              | RF2                | RF2 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 14                                              | RF1                | RF1 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 16                                              | VDD                | Power Supply. Bypass to GND with capacitors shown in the Typical Application Circuit as close as possible to pin.                                                                                                                                                          |

| 17                                              | V1                 | Control pin to set switch state. See Table 1 or Table 2.                                                                                                                                                                                                                   |

| 18                                              | V2                 | Control pin to set switch state. See Table 1 or Table 2.                                                                                                                                                                                                                   |

| 19                                              | V3                 | Control pin to set switch state. See Table 1 or Table 2.                                                                                                                                                                                                                   |

| 20                                              | VSS <sub>EXT</sub> | External VSS negative voltage control. Connect to ground to enable on chip negative voltage generator. To bypass and disable on chip generator connect this pin to an external VSS.                                                                                        |

| 22                                              | RFC                | RF Common Port. Matched to 50 ohms when one of the 4 RF ports is selected. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                     |

| 25 — EF                                         |                    | Exposed Pad. Internally connected to GND. Solder this exposed pad to a PCB pad that uses multiple ground vias to provide heat transfer out of the device into the PCB ground planes. These multiple ground vias are also required to achieve the specified RF performance. |

#### **APPLICATIONS INFORMATION**

#### **Default Start-up**

Control pins include no internal pull-down resistors to logic LOW or pull-up resistors to logic HIGH.

#### **Logic Control**

Three control pins V1, V2, and V3 are used to set the state of the SP4T switch (see Table 1 or Table 2).

#### **External Vss**

The F2914 is designed with an on-chip negative voltage generator. This on-chip generator is enabled by connecting pin 20 of the device to ground. To disable the on-chip generator apply a negative voltage to pin 20 (VSSEXT) of the device within the range stated in the Recommended Operating Conditions Table.

#### **Power Supplies**

A common VDD power supply should be used for all pins requiring DC power. All supply pins should be bypassed with external capacitors to minimize noise and fast transients. Supply noise can degrade noise figure and fast transients can trigger ESD clamps and cause them to fail. Supply voltage change or transients should have a slew rate smaller than 1V/20uS. In addition, all control pins should remain at 0 V (+/-0.3 V) while the supply voltage ramps or while it returns to zero.

#### **Control Pin Interface**

If control signal integrity is a concern and clean signals cannot be guaranteed due to overshoot, undershoot, ringing, etc., the following circuit at the input of each control pin is recommended. This applies to control pins 17, 18, and 19 as shown below.

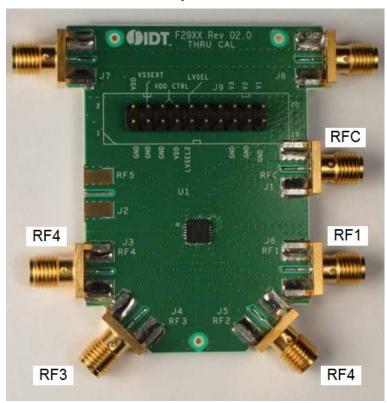

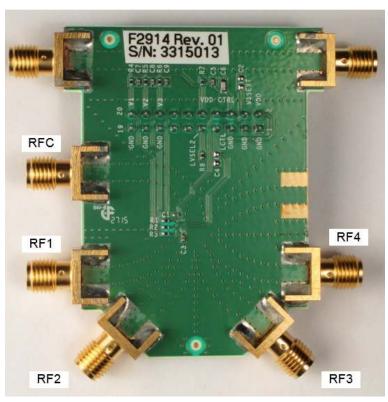

## **EVKIT PICTURE**

## **Top View**

#### **Bottom View**

## **EV**KIT / **APPLICATIONS CIRCUIT**

## **EVKIT BOM**

| Part Reference                                             | QTY | DESCRIPTION                                    | Mfr. Part #          | Mfr.      |

|------------------------------------------------------------|-----|------------------------------------------------|----------------------|-----------|

| C1, C3, C5, C7,<br>C8, C9                                  | 6   | 100 pF ±5%, 50V, C0G Ceramic Capacitor (0402)  | GRM1555C1H101J       | Murata    |

| C2                                                         | 0   | Not Installed (0603)                           |                      |           |

| C4                                                         | 0   | Not Installed (0603)                           |                      |           |

| C6                                                         | 1   | 1000 pF ±5%, 50V, C0G Ceramic Capacitor (0603) | GRM1885C1H102J       | Murata    |

| R1, R2, R3 3 0 Ω ±1%, 1/10W, Resistor (0402)               |     | 0 Ω ±1%, 1/10W, Resistor (0402)                | ERJ-2GE0R00X         | Panasonic |

| R4, R5, R6 3 100 kΩ ±1%, 1/10W, Resistor (0402)            |     | 100 kΩ ±1%, 1/10W, Resistor (0402)             | ERJ-2RKF1003X        | Panasonic |

| R7 1 15 kΩ ±1%, 1/10W, Resistor (0402)                     |     | ERJ-2RKF1502X                                  | Panasonic            |           |

| R8 1 22 k $\Omega$ ±1%, 1/10W, Resistor (0402)             |     | ERJ-2RKF2202X                                  | Panasonic            |           |

| J1, J3-J8 7 Edge Launch SMA (0.375 inch pitch ground tabs) |     | 142-0701-851                                   | Emerson Johnson      |           |

| J9 1 CONN HEADER VERT DE                                   |     | CONN HEADER VERT DBL 10 X 2 POS GOLD           | 67997-120HLF         | FCI       |

| U1 1 SP4T Switch 4 mm x 4 mm QFN24-EP                      |     | F2914NBGK                                      | IDT                  |           |

|                                                            | 1   | Printed Circuit Board                          | F29XX EVKIT Rev 02.0 | IDT       |

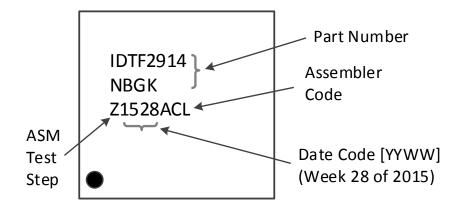

#### **TOP MARKINGS**

#### **EVKIT OPERATION**

#### **External Supply Setup**

Set up a VDD power supply in the voltage range of 2.7 V to 5.5 V and disable the power supply output.

If using the on-chip negative voltage generator install a 2-pin shunt to short out pins 3 and 4 of J9.

If an external negative voltage supply is to be used set the supply voltage within the range of -3.6 V to -3.2 V and disable the negative voltage power supply output. Also, be sure there are no jumper connections on pins 3 and 4 of J9.

#### **Logic Control Setup**

#### Using the EVKIT to manually set the control logic:

On connector J9 connect a 2-pin shunt from pin 7 (VDD) to pin 8 (VDD\_CTRL). This connection provides the VDD voltage supply to the Eval Board logic control pull up network.

On connector J9 connect a 2-pin shunt from pin 9 (LVSEL2) to pin 10 (LVSEL). This connection enables R7 (15 k $\Omega$ ) and R8 (22 k $\Omega$ ) to form a voltage divider to set the proper logic control levels to support the full voltage range of VDD. Note that when using the on-board R7 / R8 voltage divider the current draw from the VDD supply will be higher by approximately VDD / 37 k $\Omega$ .

Connector J9 has 3 logic input pins: V1 (pin 20), V2 (pin 18), and V3 (pin 16). See Table 1 or Table 2 for Logic Truth Table. With the pullup network enabled (as noted above), these pins open will provide a logic high through pull up resistors R4, R5, and R6. To set a logic low to V1, V2, and V3 connect 2-pin shunts from pin 16 to pin 15, pin 18 to pin 17 and pin 20 to pin 19 respectively.

#### **Using external control logic:**

Pins 6, 7, 8, 9, and 10 of J9 should have no connection. External logic controls would be applied to J9 pins 16 (V3), 18 (V2) and 20 (V1). See Table 1 or Table 2 for Logic Truth Table.

#### **Turn on Procedure**

Setup the supplies and Eval Board as noted in the **External Supply Setup** and **Logic Control Setup** sections above.

Connect the preset disabled VDD power supply to pin 2 (VDD) and pin 1 (GND) of J9.

If the external negative voltage source is to be used, connect the disabled supply to pin 4 (VSSEXT) and pin 3 (GND) of J9. If using on-chip negative supply be sure the 2-pin shunt is installed connecting pin 3 to pin 4.

Enable the VDD supply then enable the VSSEXT supply (if used).

Set the desired logic setting using V1, V2, and V3 to achieve the desired Table 1 or Table 2 setting. Note that external control logic should not be applied without VDD being applied first.

#### **Turn off Procedure**

If using external control logic for V1, V2, V3 then set to a logic low.

Disable any external VSSEXT supply.

Disable the VDD supply.

## **REVISION HISTORY SHEET**

|   | Rev | Date        | Page | Description of Change |

|---|-----|-------------|------|-----------------------|

| Ī | 0   | 2016-Mar-01 |      | Production Release    |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 USA Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.idt.com Tech Support http://www.idt.com/support/technical-support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners.

Copyright ©2015. Integrated Device Technology, Inc. All rights reserved.