# Dual 350 MHz Low Power Amplifier

AD8012\*

#### **FEATURES**

**Low Power**

1.7 mA/Amplifier Supply Current

Fully Specified for ±5 V and +5 V Supplies

High Output Current, 125 mA

**High Speed**

350 MHz, -3 dB Bandwidth (G = +1)

150 MHz, -3 dB Bandwidth (G = +2)

2,250 V/μs Slew Rate

20 ns Settling Time to 0.1%

**Low Distortion**

–72 dBc Worst Harmonic @ 500 kHz,  $R_L$  = 100  $\Omega$

-66 dBc Worst Harmonic @ 5 MHz,  $R_L$  = 1 k $\Omega$

Good Video Specifications ( $R_L = 1 \text{ k}\Omega$ , G = +2)

0.02% Differential Gain Error

0.06° Differential Phase Error

Gain Flatness 0.1 dB to 40 MHz

60 ns Overdrive Recovery

Low Offset Voltage, 1.5 mV

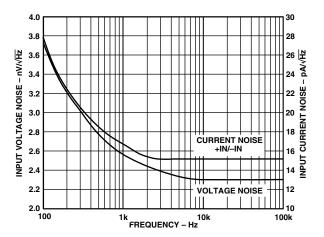

Low Voltage Noise, 2.5 nV/√Hz

Available in 8-Lead SOIC and 8-Lead MSOP

**APPLICATIONS**

**XDSL, HDSL Line Drivers**

**ADC Buffers**

**Professional Cameras**

**CCD Imaging Systems**

**Ultrasound Equipment**

**Digital Cameras**

### PRODUCT DESCRIPTION

The AD8012 is a dual, low power, current feedback amplifier capable of providing 350 MHz bandwidth while using only 1.7 mA per amplifier. It is intended for use in high frequency, wide dynamic range systems where low distortion and high speed are essential and low power is critical.

With only 1.7 mA of supply current, the AD8012 also offers exceptional ac specifications such as 20 ns settling time and 2,250 V/ $\mu$ s slew rate. The video specifications are 0.02% differential gain and 0.06 degree differential phase, excellent for such a low power amplifier. In addition, the AD8012 has a low offset of 1.5 mV.

The AD8012 is well suited for any application that requires high performance with minimal power.

The product is available in standard 8-lead SOIC or MSOP packages and operates over the industrial temperature range –40°C to +85°C.

\*Protected under U.S. Patent Number 5,537,079.

### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

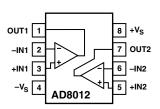

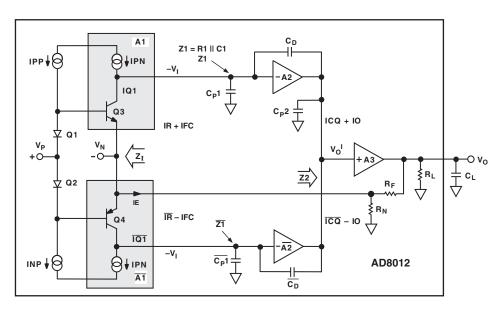

### FUNCTIONAL BLOCK DIAGRAM

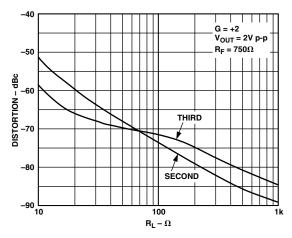

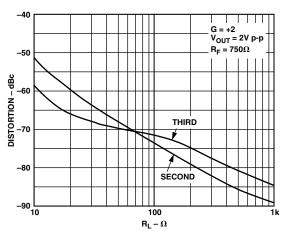

Figure 1. Distortion vs. Load Resistance,  $V_S = \pm 5 V$ , Frequency = 500 kHz

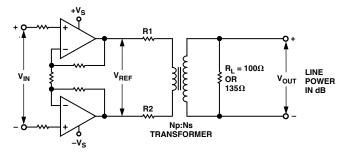

Figure 2. Differential Drive Circuit for XDSL Applications

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

# AD8012-SPECIFICATIONS

**DUAL SUPPLY** (@  $T_A = 25^{\circ}C$ ,  $V_S = \pm 5$  V, G = +2,  $R_L = 100~\Omega$ ,  $R_F = R_G = 750~\Omega$ , unless otherwise noted.)

| Parameter                                                                                                                                                                    | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min         | Тур                                                                                                       | Max                | Unit                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE  -3 dB Small Signal Bandwidth  0.1 dB Bandwidth  Large Signal Bandwidth  Slew Rate  Rise and Fall Time  Settling Time  Overdrive Recovery                | $G = +1, V_{OUT} < 0.4 \text{ V p-p, } R_L = 1 \text{ k}\Omega$ $G = +2, V_{OUT} < 0.4 \text{ V p-p, } R_L = 1 \text{ k}\Omega$ $G = +2, V_{OUT} < 0.4 \text{ V p-p, } R_L = 100 \Omega$ $V_{OUT} < 0.4 \text{ V p-p, } R_L = 1 \text{ k}\Omega/100 \Omega$ $V_{OUT} = 4 \text{ V p-p}$ $V_{OUT} = 4 \text{ V p-p}$ $V_{OUT} = 2 \text{ V p-p}$ $0.1\%, V_{OUT} = 2 \text{ V p-p}$ $0.02\%, V_{OUT} = 2 \text{ V p-p}$ $2 \times \text{ Overdrive}$                                                                                                                                                                                                                                                                                                                                                                                                       | 270<br>95   | 350<br>150<br>90<br>40/23<br>75<br>2,250<br>3<br>20<br>35<br>60                                           |                    | MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>V/µs<br>ns<br>ns                              |

| NOISE/HARMONIC PERFORMANCE Distortion Second Harmonic  Third Harmonic  Output IP3 IMD Crosstalk Input Voltage Noise Input Current Noise Differential Gain Differential Phase | $\begin{split} &V_{\rm OUT} = 2 \ V \ p\text{-p}, \ G = +2 \\ &500 \ k\text{Hz}, \ R_{\rm L} = 1 \ k\Omega/100 \ \Omega \\ &5 \ M\text{Hz}, \ R_{\rm L} = 1 \ k\Omega/100 \ \Omega \\ &500 \ k\text{Hz}, \ R_{\rm L} = 1 \ k\Omega/100 \ \Omega \\ &500 \ k\text{Hz}, \ R_{\rm L} = 1 \ k\Omega/100 \ \Omega \\ &500 \ k\text{Hz}, \ \Delta f = 10 \ k\text{Hz}, \ R_{\rm L} = 1 \ k\Omega/100 \ \Omega \\ &500 \ k\text{Hz}, \ \Delta f = 10 \ k\text{Hz}, \ R_{\rm L} = 1 \ k\Omega/100 \ \Omega \\ &500 \ k\text{Hz}, \ A_{\rm L} = 100 \ \Omega \\ &5 \ M\text{Hz}, \ R_{\rm L} = 100 \ \Omega \\ &f = 10 \ k\text{Hz} \\ &f = 10 \ k\text{Hz}, \ +\text{Input}, \ -\text{Input} \\ &f = 3.58 \ M\text{Hz}, \ R_{\rm L} = 150 \ \Omega/1 \ k\Omega, \ G = +2 \\ &f = 3.58 \ M\text{Hz}, \ R_{\rm L} = 150 \ \Omega/1 \ k\Omega, \ G = +2 \end{split}$ |             | -89/-73<br>-78/-62<br>-84/-72<br>-66/-52<br>30/40<br>-79/-77<br>-70<br>2.5<br>15<br>0.02/0.02<br>0.3/0.06 |                    | dBc<br>dBc<br>dBc<br>dBc<br>dBm<br>dBc<br>dB<br>nV/√Hz<br>pA/√Hz<br>%<br>Degrees |

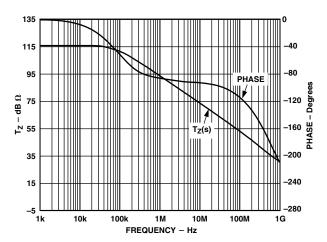

| DC PERFORMANCE Input Offset Voltage Open-Loop Transimpedance                                                                                                                 | $T_{MIN}$ - $T_{MAX}$ $V_{OUT} = \pm 2 \text{ V}, \text{ R}_{L} = 100 \Omega$ $T_{MIN}$ - $T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 240<br>200  | ±1.5                                                                                                      | ±4<br>±5           | mV<br>mV<br>kΩ<br>kΩ                                                             |

| INPUT CHARACTERISTICS Input Resistance Input Capacitance Input Bias Current  Common-Mode Rejection Ratio Input Common-Mode Voltage Range                                     | +Input<br>+Input<br>+Input, -Input<br>+Input, -Input, $T_{MIN}$ - $T_{MAX}$<br>$V_{CM} = \pm 2.5 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -56<br>±3.8 | 450<br>2.3<br>±3<br>-60<br>±4.1                                                                           | ±12<br>±15         | kΩ<br>pF<br>μΑ<br>μΑ<br>dB<br>V                                                  |

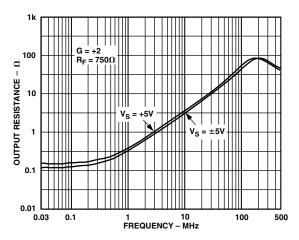

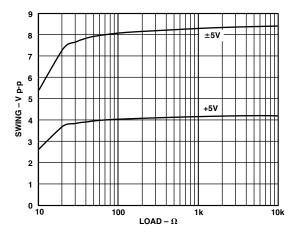

| OUTPUT CHARACTERISTICS Output Resistance Output Voltage Swing Output Current Short-Circuit Current                                                                           | $G = +2$ $T_{MIN} - T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ±3.85       | 0.1<br>±4<br>125<br>500                                                                                   |                    | Ω<br>V<br>mA<br>mA                                                               |

| POWER SUPPLY Supply Current/Amp  Operating Range Power Supply Rejection Ratio                                                                                                | T <sub>MIN</sub> -T <sub>MAX</sub><br>Dual Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ±1.5<br>-58 | 1.7<br>-60                                                                                                | 1.8<br>1.9<br>±6.0 | mA<br>mA<br>V<br>dB                                                              |

Specifications subject to change without notice.

-2- REV. B

$\textbf{SINGLE SUPPLY} \ (@\ T_A=25^{\circ}\text{C},\ V_S=+5\ \text{V},\ G=+2,\ R_L=100\ \Omega,\ R_F=R_G=750\ \Omega,\ unless\ otherwise\ noted.)$

| Parameter                            | Conditions                                                                       | Min        | Typ                  | Max     | Unit               |

|--------------------------------------|----------------------------------------------------------------------------------|------------|----------------------|---------|--------------------|

| DYNAMIC PERFORMANCE                  |                                                                                  |            |                      |         |                    |

| -3 dB Small Signal Bandwidth         | $G = +1, V_{OUT} < 0.4 \text{ V p-p}, R_L = 1 \text{ k}Ω$                        | 220        | 300                  |         | MHz                |

| · ·                                  | $G = +2$ , $V_{OUT} < 0.4 \text{ V p-p}$ , $R_L = 1 \text{ k}\Omega$             | 90         | 140                  |         | MHz                |

|                                      | $G = +2$ , $V_{OUT} < 0.4 \text{ V p-p}$ , $R_L = 100 \Omega$                    |            | 85                   |         | MHz                |

| 0.1 dB Bandwidth                     | $V_{OUT} < 0.4 \text{ V p-p}, R_L = 1 \text{ k}\Omega/100 \Omega$                |            | 43/24                |         | MHz                |

| Large Signal Bandwidth               | $V_{OUT} = 2 V p-p$                                                              |            | 60                   |         | MHz                |

| Slew Rate                            | $V_{OUT} = 3 V p-p$                                                              |            | 1,200                |         | V/µs               |

| Rise and Fall Time                   | $V_{OUT} = 2 V p-p$                                                              |            | 2                    |         | ns                 |

| Settling Time                        | $0.1\%, V_{OUT} = 2 \text{ V p-p}$                                               |            | 25                   |         | ns                 |

| 2                                    | $0.02\%, V_{OUT} = 2 V p-p$                                                      |            | 40                   |         | ns                 |

| Overdrive Recovery                   | 2× Overdrive                                                                     |            | 60                   |         | ns                 |

| NOISE/HARMONIC PERFORMANCE           |                                                                                  |            |                      |         |                    |

| Distortion                           | $V_{OUT} = 2 \text{ V p-p, } G = +2$                                             |            |                      |         |                    |

| Second Harmonic                      | 500  kHz, R <sub>L</sub> = 1 kΩ/100 Ω                                            |            | -87/-71              |         | dBc                |

| Second Harmonic                      | $\frac{1}{2}$ 5 MHz, R <sub>L</sub> = 1 kΩ/100 Ω                                 |            | -77/ <del>-</del> 61 |         | dBc                |

| Third Harmonic                       | $500 \text{ kHz}$ , $R_L = 1 \text{ k}\Omega/100 \Omega$                         |            | -89/-72              |         | dBc                |

| Time Harmonic                        | $_{2}^{500 \text{ KHz}}$ , $R_{L} = 1 \text{ kΩ}/100 \Omega$                     |            | -78/ <del>-</del> 52 |         | dBc                |

| Output IP3                           | $5$ WHz, $R_L = 1$ kΩ/100 Ω                                                      |            | 30/40                |         | dBm                |

| IMD                                  | $500 \text{ kHz}$ , $R_L = 1 \text{ kΩ}/100 \text{ Ω}$                           |            | -77/ <del>-</del> 80 |         | dBn                |

| Crosstalk                            | $5 \text{ MHz}, R_L = 1 \text{ RS2/100 S2}$<br>$5 \text{ MHz}, R_L = 100 \Omega$ |            | -777-80<br>-70       |         | dB                 |

| Input Voltage Noise                  | f = 10  kHz                                                                      |            | 2.5                  |         | nV/√ <del>Hz</del> |

|                                      |                                                                                  |            |                      |         |                    |

| Input Current Noise                  | f = 10 kHz, +Input, -Input                                                       |            | 15                   |         | pA/√ <del>Hz</del> |

| Differential Gain                    | Black Level Clamped to +2 V, f = 3.58 MHz                                        |            | 0.02/0.02            |         | %                  |

| Differential Gain Differential Phase | $R_{L} = 150 \Omega/1 k\Omega$ $R_{L} = 150 \Omega/1 k\Omega$                    |            | 0.03/0.03            |         |                    |

|                                      | K <sub>L</sub> = 130 22/1 K22                                                    |            | 0.4/0.08             |         | Degrees            |

| DC PERFORMANCE                       |                                                                                  |            |                      |         |                    |

| Input Offset Voltage                 |                                                                                  |            | ±1                   | ±3      | mV                 |

|                                      | $T_{MIN}$ - $T_{MAX}$                                                            |            |                      | $\pm 4$ | mV                 |

| Open-Loop Transimpedance             | $V_{OUT} = 2 \text{ V p-p}, R_L = 100 \Omega$                                    | 200        | 400                  |         | kΩ                 |

|                                      | $T_{MIN}$ - $T_{MAX}$                                                            | 150        |                      |         | kΩ                 |

| INPUT CHARACTERISTICS                |                                                                                  |            |                      |         |                    |

| Input Resistance                     | +Input                                                                           |            | 450                  |         | $k\Omega$          |

| Input Capacitance                    | +Input                                                                           |            | 2.3                  |         | pF                 |

| Input Bias Current                   | +Input, -Input                                                                   |            | ±3                   | ±12     | μΑ                 |

|                                      | +Input, -Input, T <sub>MIN</sub> -T <sub>MAX</sub>                               |            |                      | ±15     | μA                 |

| Common-Mode Rejection Ratio          | $V_{CM} = 1.5 \text{ V to } 3.5 \text{ V}$                                       | -56        | -60                  |         | dB                 |

| Input Common-Mode Voltage Range      |                                                                                  | 1.5 to 3.5 | 1.2 to 3.8           |         | V                  |

| OUTPUT CHARACTERISTICS               |                                                                                  |            |                      |         |                    |

| Output Resistance                    | G = +2                                                                           |            | 0.1                  |         | Ω                  |

| Output Voltage Swing                 |                                                                                  | 1 to 4     | 0.9 to 4.2           |         | V                  |

| Output Current                       | $T_{MIN}$ - $T_{MAX}$                                                            | 50         | 100                  |         | mA                 |

| Short-Circuit Current                | MIN - MAA                                                                        |            | 500                  |         | mA                 |

| POWER SUPPLY                         |                                                                                  |            |                      |         |                    |

| Supply Current/Amp                   |                                                                                  |            | 1.55                 | 1.75    | mA                 |

| Supply Sufferiorninp                 | $T_{MIN}$ $-T_{MAX}$                                                             |            | 1.22                 | 1.75    | mA                 |

| Operating Range                      | Single Supply                                                                    | 3          |                      | 1.65    | V                  |

| Power Supply Rejection Ratio         | onigic ouppry                                                                    | _58        | -60                  | 14      | dB                 |

| Tower Supply Rejection Ratio         |                                                                                  | -50        | -00                  |         | uБ                 |

Specifications subject to change without notice.

REV. B -3-

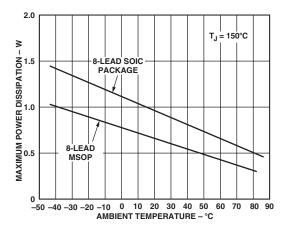

### **MAXIMUM POWER DISSIPATION**

The maximum power that can be safely dissipated by the AD8012 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately +150°C. Temporarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of +175°C for an extended period can result in device failure.

The output stage of the AD8012 is designed for maximum load current capability. As a result, shorting the output to common can cause the AD8012 to source or sink 500 mA. To ensure proper operation, it is necessary to observe the maximum power derating curves. Direct connection of the output to either power supply rail can destroy the device.

Figure 3. Plot of Maximum Power Dissipation vs. Temperature for AD8012

## **Test Circuits**

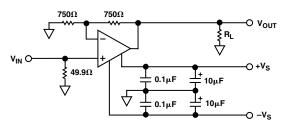

Test Circuit 1. Gain = +2

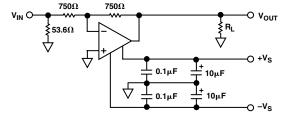

Test Circuit 2. Gain = -1

-4- REV. B

### ABSOLUTE MAXIMUM RATINGS1

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Specification is for device in free air at +25°C.

8-Lead SOIC Package:  $\theta_{JA} = 155^{\circ}\text{C/W}$ 8-Lead MSOP Package:  $\theta_{JA} = 200^{\circ}\text{C/W}$

### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8012 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **ORDERING GUIDE**

| Model             | Temperature Range | Package Description | Package Options | Branding |

|-------------------|-------------------|---------------------|-----------------|----------|

| AD8012AR          | -40°C to +85°C    | 8-Lead SOIC         | R-8             |          |

| AD8012AR-REEL     | −40°C to +85°C    | 13" Tape and Reel   | R-8             |          |

| AD8012AR-REEL7    | –40°C to +85°C    | 7" Tape and Reel    | R-8             |          |

| AD8012ARM         | –40°C to +85°C    | 8-Lead MSOP         | RM-08           | H6A      |

| AD8012ARM-REEL    | –40°C to +85°C    | 13" Tape and Reel   | RM-08           | H6A      |

| AD8012ARM-REEL7   | –40°C to +85°C    | 7" Tape and Reel    | RM-08           | H6A      |

| AD8012ARMZ*       | –40°C to +85°C    | 8-Lead MSOP         | RM-08           | H6A      |

| AD8012ARMZ-REEL*  | −40°C to +85°C    | 13" Tape and Reel   | RM-08           | H6A      |

| AD8012ARMZ-REEL7* | −40°C to +85°C    | 7" Tape and Reel    | RM-08           | H6A      |

<sup>\*</sup>Z = Pb-free product.

REV. B –5–

# **AD8012**—Typical Performance Characteristics

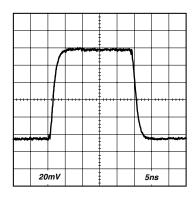

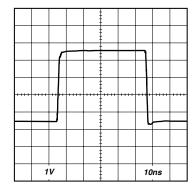

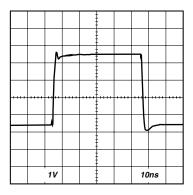

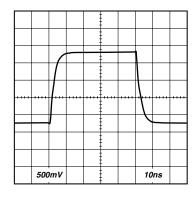

TPC 1. 100 mV Step Response; G = +2,  $V_S = \pm 2.5$  V or  $\pm 5$  V,  $R_L = 1$  k $\Omega^*$

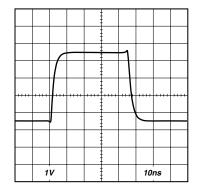

TPC 4. 4 V Step Response; G = -1,  $V_S$  =  $\pm 5$  V,  $R_L$  = 1  $k\Omega$

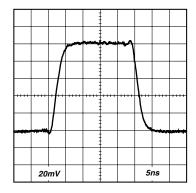

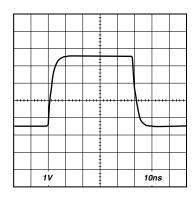

TPC 2. 4 V Step Response; G = +2,  $V_S = \pm 5$  V,  $R_L = 1$   $k\Omega$

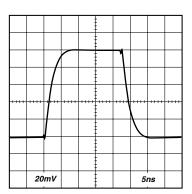

TPC 5. 100 mV Step Response; G = +2,  $V_S = \pm 2.5$  V or  $\pm 5$  V,  $R_L = 100 \,\Omega^*$

TPC 3. 100 mV Step Response; G = -1,  $V_S = \pm 2.5$  V or  $\pm 5$  V,  $R_L = 1$  k $\Omega^*$

TPC 6. 2 V Step Response;  $G=+2,~V_S=\pm 2.5~V,~R_L=100~\Omega$

$<sup>^*</sup>V_S = \pm 2.5 \text{ V}$  operation is identical to  $V_S = +5 \text{ V}$  single-supply operation.

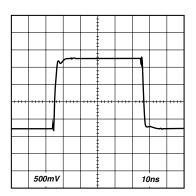

TPC 7. 4 V Step Response; G = +2,  $V_S = \pm 5$  V,  $R_L = 100~\Omega$

TPC 10. 4 V Step Response; G = -1,  $V_S = \pm 5$  V,  $R_L = 100 \Omega$

TPC 8. 100 mV Step Response; G = –1,  $V_S$  =  $\pm 2.5$  V or  $\pm 5$  V,  $R_L$  = 100  $\Omega^*$

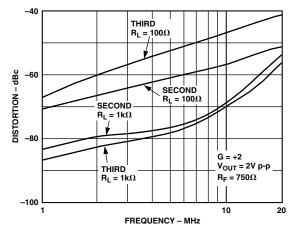

TPC 11. Distortion vs. Load Resistance;  $V_S = \pm 5 V$ , Frequency = 500 kHz

TPC 9. 2 V Step Response; G = -1,  $V_S = \pm 2.5$  V,  $R_L = 100~\Omega$

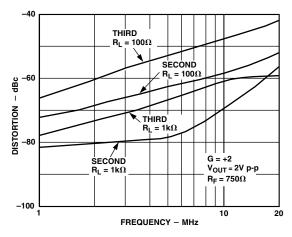

TPC 12. Distortion vs. Frequency;  $V_S = \pm 5 \text{ V}$

REV. B -7-

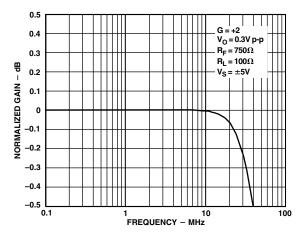

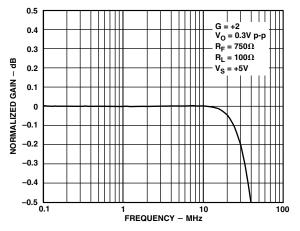

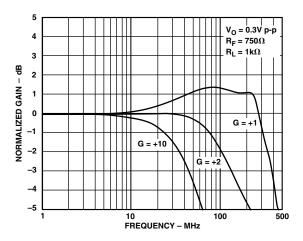

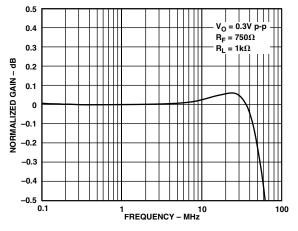

TPC 13. Gain Flatness;  $V_S = \pm 5 V$

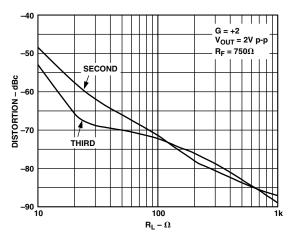

TPC 14. Distortion vs. Load Resistance;  $V_S = +5 V$ , Frequency = 500 kHz

TPC 15. Distortion vs. Frequency;  $V_S = +5 \text{ V}$

TPC 16. Gain Flatness;  $V_S = +5 \text{ V}$

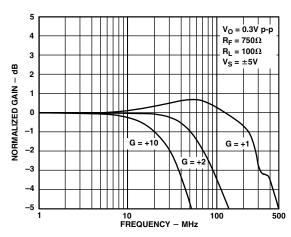

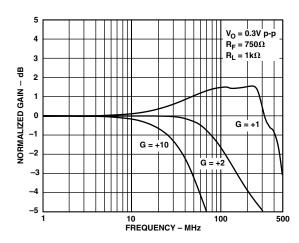

TPC 17. Frequency Response;  $V_S = \pm 5 V$

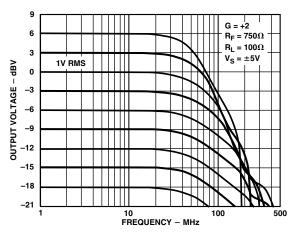

TPC 18. Output Voltage vs. Frequency;  $V_S = \pm 5~V$ , G = +2,  $R_L = 100~\Omega$

-8- REV. B

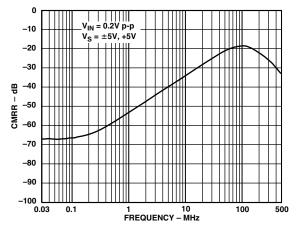

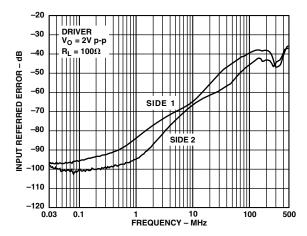

TPC 19. CMRR vs. Frequency;  $V_S = \pm 5 V$ , +5 V

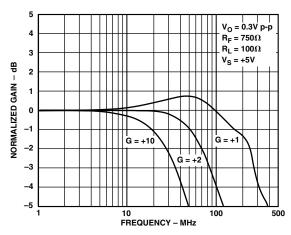

TPC 20. Frequency Response;  $V_S = +5 \text{ V}$

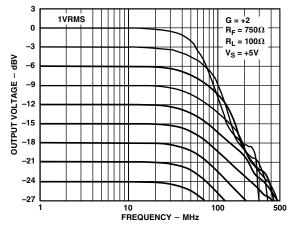

TPC 21. Output Voltage vs. Frequency;  $V_S = +5 \text{ V}$ , G = +2,  $R_L = 100 \Omega$

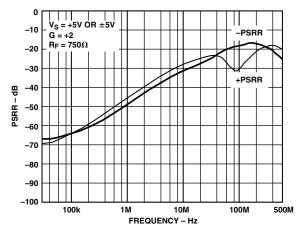

TPC 22. PSRR vs. Frequency;  $V_S = \pm 5 V$ , +5 V

TPC 23. Output Resistance vs. Frequency

TPC 24. Open-Loop Transimpedance and Phase vs. Frequency

REV. B –9–

TPC 25. Output Swing vs. Load

TPC 26. Noise vs. Frequency

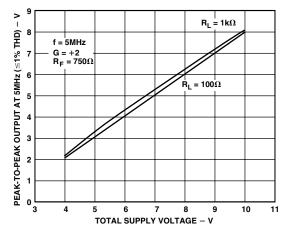

TPC 27. Output Swing vs. Supply

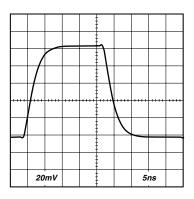

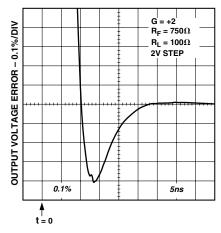

TPC 28. Settling Time,  $V_S = \pm 5 \text{ V}$

TPC 29. Frequency Response;  $V_S = \pm 5 V$

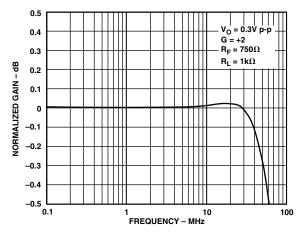

TPC 30. Gain Flatness;  $V_S = \pm 5 V$

-10- REV. B

TPC 31. Crosstalk vs. Frequency

TPC 32. Frequency Response;  $V_S = +5 \text{ V}$

TPC 33. Gain Flatness;  $V_S = +5 V$

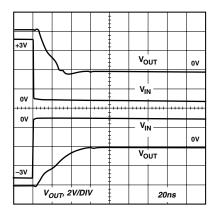

TPC 34. Overdrive Recovery;  $V_S=\pm 5~V,~G=+2,~R_F=750~\Omega,~R_L=100~\Omega,~V_{IN}=3~V~p\text{-p}~(T=1~\mu s)$

REV. B –11–

### THEORY OF OPERATION

The AD8012 is a dual, high speed CF amplifier that attains new levels of bandwidth (BW), power, distortion, and signal swing capability. Its wide dynamic performance (including noise) is the result of both a new complementary high speed bipolar process and a new and unique architectural design. The AD8012 uses a two-gain stage complementary design approach versus the traditional single-stage complementary mirror structure sometimes referred to as the Nelson amplifier. Though twin stages have been tried before, they typically consumed high power since they were of a folded cascade design, similar to that of the AD9617. This design allows for the standing or quiescent current to add to the high signal or slew current-induced stages. In the time domain, the large signal output rise/fall time and slew rate is typically controlled by the small signal BW of the amplifier and the input signal step amplitude, respectively, and not the dc quiescent current of the gain stages (with the exception of input level shift diodes Q1/Q2). Using two stages versus one also allows for a higher overall gain bandwidth product (GBWP) for the same power, resulting in lower signal distortion and the ability to drive heavier external loads. In addition, the second-gain stage also isolates (divides down) A3's input reflected load drive and the nonlinearities created, resulting in relatively lower distortion and higher open-loop gain.

Overall, when high external load drive and low ac distortion is a requirement, a twin-gain stage integrating amplifier like the AD8012 will provide excellent results for lower power over the

traditional single stage complementary devices. In addition, because the AD8012 is a CF amplifier, closed-loop BW variations versus external gain variations (varying RN) will be much lower compared to a VF op amp, where the BW varies inversely with gain. Another key attribute of this amplifier is its ability to run on a single 5 V supply partially because of its wide common-mode input and output voltage range capability. For 5 V supply operation, the device consumes half the quiescent power (vs. 10 V supply) with little degradation in its ac and dc performance characteristics. See data sheet comparisons.

### DC GAIN CHARACTERISTICS

Gain stages A1/A1B and A2/A2B combined provide negative feedforward transresistance gain as shown in Figure 4. Stage A3 is a unity-gain buffer that provides external load isolation to A2. Each stage uses a symmetrical complementary design (A3 is also complementary though not explicitly shown). This is done to reduce both second-order signal distortion and overall quiescent power as previously described. In the quasi dc to low frequency region, the closed-loop gain relationship can be approximated as:

$$G = 1 + R_F/R_N$$

noninverting operation

$G = -R_F/R_N$  inverting operation

These basic relationships are common to all traditional operational amplifiers.

Figure 4. Simplified Block Diagram

–12– REV. B

### **APPLICATIONS**

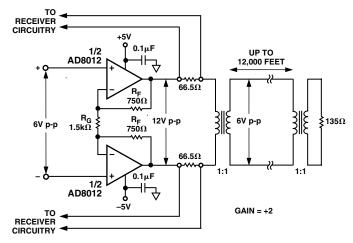

#### Line Driving for HDSL

High bitrate digital subscriber line (HDSL) is becoming popular as a means of providing full duplex data communication at rates up to 1.544 MBPS or 2.048 MBPS over moderate distances via conventional telephone twisted pair wires. Traditional T1 (E1 in Europe) requires repeaters every 3,000 feet to 6,000 feet to boost the signal strength and allow transmission over distances of up to 12,000 feet. In order to achieve repeaterless transmission over this distance, an HDSL modem requires a transmitted power level of 13.5 dBm (assuming a line impedance of 135  $\Omega$ ).

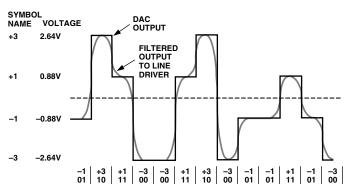

HDSL uses the two binary/one quaternary line code (2B1Q). A sample 2B1Q waveform is shown in Figure 5. The digital bit stream is broken up into groups of two bits. Four analog voltages (called quaternary symbols) are used to represent the four possible combinations of two bits. These symbols are assigned the arbitrary names +3, +1, -1, and -3. The corresponding voltage levels are produced by a DAC that is usually part of an analog front end circuit (AFEC). Before being applied to the line, the DAC output is low-pass filtered and acquires the sinusoidal form shown in Figure 5. Finally, the filtered signal is applied to the line driver. The line voltages that correspond to the quaternary symbols +3, +1, -1, and -3 are 2.64 V, 0.88 V, -0.88 V, and -2.64 V. This gives a peak-to-peak line voltage of 5.28 V.

Figure 5. Time Domain Representation of an HDSL Signal Many of the elements of a classic differential line driver are shown in the HDSL line driver in Figure 6. A 6 V peak-to-peak differential signal is applied to the input. The differential gain of the amplifier  $(1+2~R_F/R_G)$  is set to +2, so the resulting differential output signal is 12~V~p-p.

As is normal in telephony applications, a transformer galvanically isolates the differential amplifier from the line. In this case, a 1:1 turns ratio is used. In order to correctly terminate the line, it is necessary to set the output impedance of the amplifier to be equal to the impedance of the line being driven (135  $\Omega$  in this case). Because the transformer has a turns ratio of 1:1, the impedance reflected from the line is equal to the line impedance of 135  $\Omega$  ( $R_{REFL}=R_{LINE}/Turns\ Ratio^2$ ). As a result, two 66.5  $\Omega$  resistors correctly terminate the line.

Figure 6. Differential for HDSL Applications

The immediate effect of back-termination is that the signal from the amplifier is halved before being applied to the line. This doubles the power the amplifier must deliver. However, the back-termination resistors also play an important second role.

Full-duplex data transmission systems like HDSL simultaneously transmit data in both directions. As a result, the signal on the line and across the back termination resistors is the composite of the transmitted and received signal. The termination resistors are used to tap off this signal and feed it to the receive circuitry. Because the receive circuitry "knows" what is being transmitted, the transmitted data can be subtracted from the digitized composite signal to reveal the received data.

Driving a line with a differential signal offers a number of advantages compared to a single-ended drive. Because the two outputs are always 180 degrees out of phase relative to one another, the differential signal output is double the output amplitude of either of the op amps. As a result, the differential amplifier can have a peak-to-peak swing of 16 V (each op amp can swing to  $\pm 4 \text{ V}$ ), even though the power supply is  $\pm 5 \text{ V}$ .

In addition, even-order harmonics (second, fourth, sixth, and so on.) of the two single-ended outputs tend to cancel out one another, so the total harmonic distortion (quadratic sum of all harmonics) decreases compared to the single-ended case, even as the signal amplitude is doubled. This is particularly advantageous in the case of the second harmonic. Because it is very close to the fundamental, filtering becomes difficult. In this application, the THD is dominated by the third harmonic, which is 65 dB below the carrier (i.e., spurious-free dynamic range = -65 dBc).

Differential line driving also helps to preserve the integrity of the transmitted signal in the presence of electromagnetic interference (EMI). EMI tends to induce itself equally onto both the positive and negative signal lines. As a result, a receiver with good common-mode rejection will amplify the original signal while rejecting induced (common-mode) EMI.

REV. B –13–

Increasing the peak-to-peak output signal of the amplifier in the previous example and adding a variation in the turns ratio of the transformer can yield further enhancements to the circuit. The output signal swing of the AD8012 can be increased to about  $\pm 3.9 \text{ V}$  before clipping occurs. This increases the peak-to-peak output of the differential amplifier to 15.6 V. Because the signal applied to the primary winding is now bigger, the transformer turns ratio of 1:1 can be replaced with a (step-down) turns ratio

Choosing the Appropriate Turns Ratio for the Transformer

of about 1.3:1 (from amplifier to line). This steps the 7.8 V peak-to-peak primary voltage down to 6 V. This is the same secondary voltage of the earlier examples, so the resulting power delivered to the line is the same.

The received signal, which is small relative to the transmitted signal, will, however, be stepped up by a factor of 1.3. Amplifying the received signal in this manner enhances its signal-to-noise ratio and is useful when the received signal is small compared to the to-be-transmitted signal.

The impedance reflected from the 135  $\Omega$  line now becomes 228  $\Omega$  (1.3 $^2$  × 135  $\Omega$ ). With a correctly terminated line, the amplifier must now drive a total load of 456  $\Omega$  (114  $\Omega$  + 114  $\Omega$  + 228  $\Omega$ ), considerably more than the original 270  $\Omega$  load. This reduces the drive current from the op amps by about 40%.

More significant, however, is the reduction in dynamic power consumption—that is, the power the amplifier must consume in order to deliver the load power. Increasing the output signal so that it is as close as possible to the power rails minimizes the power consumed in the amplifier.

There is, however, a price to pay in terms of increased signal distortion. Increasing the output signal of each op amp from the original  $\pm 3$  V to  $\pm 3.9$  V reduces the spurious-free dynamic range (SFDR) from -65 dB to -50 dB (measured at 500 kHz), even though the overall load impedance has increased from  $270~\Omega$  to  $456~\Omega$ .

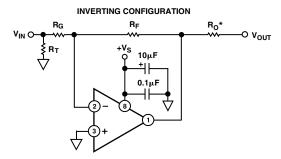

### LAYOUT CONSIDERATIONS

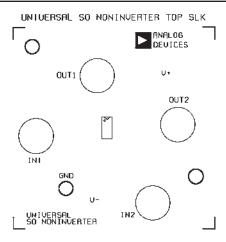

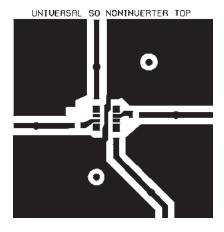

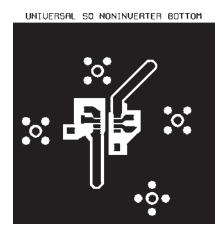

The specified high speed performance of the AD8012 requires careful attention to board layout and component selection. Table I shows recommended component values for the AD8012 and Figures 8–13 show recommended layouts for the 8-lead SOIC and MSOP packages for a positive gain. Proper RF design techniques and low parasitic component selections are mandatory.

The PCB should have a ground plane covering all unused portions of the component side of the board to provide a low impedance ground path. The ground plane should be removed from the area near the input pins to reduce stray capacitance.

Chip capacitors should be used for supply bypassing (see Figure 7). One end should be connected to the ground plane and the other within 1/8 inch of each power pin. An additional (4.7  $\mu F$  to 10  $\mu F)$  tantalum electrolytic capacitor should be connected in parallel.

The feedback resistor should be located close to the inverting input pin in order to keep the stray capacitance at this node to a minimum. Capacitance greater than 1.5 pF at the inverting input will significantly affect high speed performance when operating at low noninverting gains.

Stripline design techniques should be used for long signal traces (greater than about 1 inch). They should be designed with the proper system characteristic impedance and be properly terminated at each end.

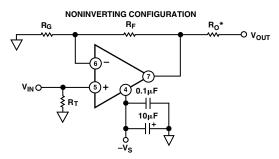

${}^*\mathrm{R}_\mathrm{O}$  CHOSEN FOR CHARACTERISTIC IMPEDANCE.

${}^{*}\mathrm{R}_{\mathrm{O}}$  chosen for characteristic impedance.

Figure 7. Inverting and Noninverting Configurations

Table I. Typical Bandwidth vs. Gain Setting Resistors

| Gain | $R_{\mathrm{F}}$ | $R_G$  | R <sub>T</sub> | Small Signal -3 dB BW (MHz),<br>$V_S = \pm 5 \text{ V}, R_L = 1 \text{ k}\Omega$ |

|------|------------------|--------|----------------|----------------------------------------------------------------------------------|

| -1   | 750 Ω            | 750 Ω  | 53.6 Ω         | 110                                                                              |

| +1   | 750 Ω            |        | $49.9~\Omega$  | 350                                                                              |

| +2   | 750 Ω            | 750 Ω  | 49.9 Ω         | 150                                                                              |

| +10  | 750 Ω            | 82.5 Ω | 49.9 Ω         | 40                                                                               |

$R_T$  chosen for 50  $\Omega$  characteristic input impedance.

–14– REV. B

Figure 8. Universal SOIC Noninverter Top Silkscreen

Figure 9. Universal SOIC Noninverter Top

Figure 10. Universal SOIC Noninverter Bottom

Figure 11. Universal MSOP Noninverter Top Silkscreen

Figure 12. Universal MSOP Noninverter Top

Figure 13. Universal MSOP Noninverter Bottom

REV. B –15–

### **OUTLINE DIMENSIONS**

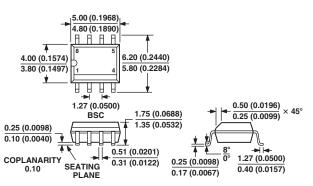

### 8-Lead Standard Small Outline Package [SOIC] Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

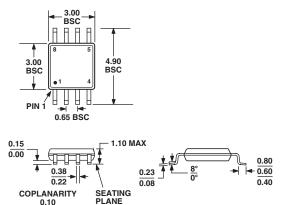

# 8-Lead Mini Small Outline Package [MSOP] (RM-8)

Dimensions shown in millimeters

**COMPLIANT TO JEDEC STANDARDS MO-187AA**

## **Revision History**

| Location                                        | Page      |

|-------------------------------------------------|-----------|

| 12/03—Data Sheet changed from REV. A to REV. B. |           |

| Renumbered figures and TPCs                     | Universal |

| Updated ORDERING GUIDE                          | 5         |

| Updated OUTLINE DIMENSIONS                      | 16        |

-16- REV. B