## Features

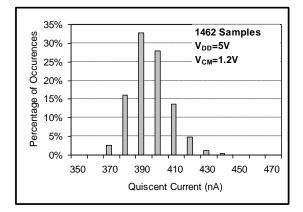

- Ultra-Low Supply Current: 390 nA Comparator with Reference

- Internal 1.248V ± 1.4% Reference

- Fast Response Time: 13 µs Propagation Delay, with 100 mV Overdrive

- Internal Hysteresis for Clean Switching

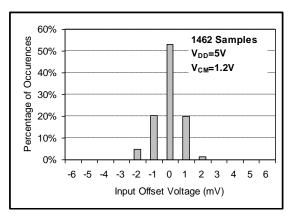

- Offset Voltage: ± 2.0 mV Maximum

- Offset Voltage Temperature Drift: 0.3 µV/°C

- Input Bias Current: 6 pA Typical

- Input Common-Mode Range Extends 200 mV

- Push-Pull Output with ±25 mA Drive Capability

- Open-Drain Output Version Available: TP2025

- No Phase Reversal for Overdriven Inputs

- Low Supply Voltage: 1.8V to 5.5V

- Green, Space-Saving SC70/SOT23 Package

# **Applications**

- Battery Monitoring / Management

- Alarm and Monitoring Circuits

- Threshold Detectors/Discriminators

- Sensing at Ground or Supply Line

- Oscillators and RC Timers

- Mobile Communications and Notebooks

- Ultra-Low-Power Systems

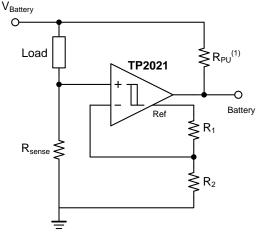

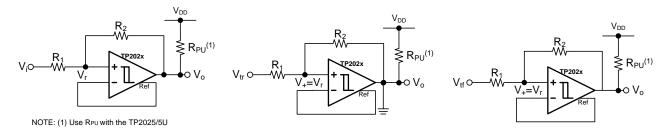

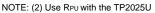

NOTE: (1) Use  $R_{\text{PU}}$  with the TP2025

## **TP2021 in Low-Side Current Sensing**

## Description

The TP2021 has a push-pull output stage with loads up to 25mA. The TP2025 has an open-drain output stage that makes it suitable for mixed-voltage system design. Both feature an on-chip 1.248V ±1.4% reference and draw an ultra-low supply current of only 440nA (max). The TP202x incorporate 3PEAK's proprietary and patented design techniques to achieve the best world-class performance among all nano-power comparators. Both have 13µs fast response time under 1.8V to 5.5V supply. The internal input hysteresis eliminates output switching due to internal input noise voltage, current draw. They have reducing input common-mode range 200mV beyond the supply rails, and operate down to +1.8V. The integrated 1.248V voltage reference offers low 120ppm/°C drift, is stable with up to 10nF capacitive load, and can provide up to 25mA of output current. These features make the TP202x ideal for all 2-Cell Battery Monitoring/Management.

The TP202x is available in the tiny SC70/SOT23 package for space-conservative designs. Both versions are specified for the temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

3PEAK and the 3PEAK logo are registered trademarks of 3PEAK INCORPORATED. All other trademarks are the property of their respective owners.

# **Related Products**

| DEVICE                           | DESCRIPTION                                                                                                                                                                      |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP1941/TP1941N<br>/TP1942/TP1944 | Fast 68ns, 1.8V Low Power (46 $\mu$ A), Internal Hysteresis,<br>±3mV Maximum V <sub>OS</sub> , – 0.2V to V <sub>DD</sub> + 0.2V RRI, Push-<br>Pull (CMOS/TTL) Output Comparators |

| TP1945/TP1945N<br>/TP1946/TP1948 | Fast 68ns, 1.8V Low Power (46 $\mu$ A), Internal Hysteresis, ±3mV Maximum V <sub>OS</sub> , – 0.2V to V <sub>DD</sub> + 0.2V RRI, Open-Drain Output Comparators                  |

| TP1931<br>/TP1932/TP1934         | 950ns, 3µA, 1.8V, $\pm 2.5mV$ $V_{OS-MAX}$ – 0.2V to $V_{DD}$ + 0.2V RRI, Internal Hysteresis, Push-Pull Output Comparators                                                      |

| TP1935<br>/TP1936/TP1938         | 950ns, 3µA, 1.8V, $\pm 2.5$ mV V <sub>OS-MAX</sub> , – 0.2V to V <sub>DD</sub> + 0.2V RRI, Internal Hysteresis, Open-Drain Comparators                                           |

| TP2011<br>/TP2012/TP2014         | Ultra-low 200nA, $13\mu$ s, 1.6V, ±2mV Maximum V <sub>OS</sub> ,<br>Internal Hysteresis, – 0.2V to V <sub>DD</sub> + 0.2V RRI, Push-Pull<br>(CMOS/TTL) Output Comparators        |

| TP2015<br>/TP2016/TP2018         | Ultra-low 200nA, 13 $\mu$ s, 1.6V, ±2mV Maximum V <sub>OS</sub> ,<br>Internal Hysteresis, – 0.2V to V <sub>DD</sub> + 0.2V RRI, Open-<br>Drain Output Comparators                |

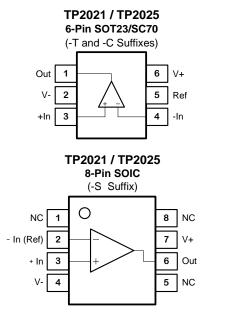

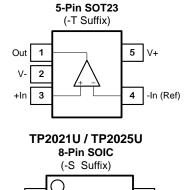

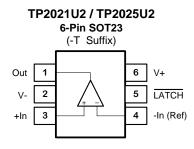

# Pin Configuration (Top View)

8

7

6 Out

5 NC

LATCH

V+

1

2

3

4

Ref

- In

+ In

V-

TP2021U / TP2025U

# **Order Information**

| Model Name | Order Number | Package     | Transport Media, Quantity | Marking<br>Information |

|------------|--------------|-------------|---------------------------|------------------------|

| TP2021     | TP2021-TR    | 6-Pin SOT23 | Tape and Reel, 3000       | C2TYW <sup>(1)</sup>   |

|            | TP2021-CR    | 6-Pin SC70  | Tape and Reel, 3000       | C2CYW <sup>(1)</sup>   |

|            | TP2021-SR    | 8-Pin SOIC  | Tape and Reel, 4000       | 2021S                  |

| TP2021U    | TP2021U-TR   | 5-Pin SOT23 | Tape and Reel, 3000       | C2UYW <sup>(1)</sup>   |

|            | TP2021U-SR   | 8-Pin SOIC  | Tape and Reel, 4000       | 2021US                 |

| TP2021U2   | TP2021U2-TR  | 6-Pin SOT23 | Tape and Reel, 3000       | C2VYW <sup>(1)</sup>   |

|            | TP2025-TR    | 6-Pin SOT23 | Tape and Reel, 3000       | CT2YW <sup>(1)</sup>   |

| TP2025     | TP2025-CR    | 6-Pin SOT23 | Tape and Reel, 3000       | CC2YW <sup>(1)</sup>   |

|            | TP2025-SR    | 8-Pin SOIC  | Tape and Reel, 4000       | 2025S                  |

| TP2025U    | TP2025U-TR   | 5-Pin SOT23 | Tape and Reel, 3000       | CU2YW <sup>(1)</sup>   |

|            | TP2025U-SR   | 8-Pin SOIC  | Tape and Reel, 4000       | 2025US                 |

| TP2025U2   | TP2025U2-TR  | 6-Pin SOT23 | Tape and Reel, 3000       | CV2YW <sup>(1)</sup>   |

Note (1): 'YW' is date coding scheme. 'Y' stands for calendar year, and 'W' stands for single workweek coding scheme.

# Absolute Maximum Ratings Note 1

| Supply Voltage: V <sup>+</sup> – V <sup>-</sup> | 6.0V                         |

|-------------------------------------------------|------------------------------|

| Input Voltage V                                 | -0.3 to V <sup>+</sup> + 0.3 |

| Input Current: +IN, -IN, Note 2                 | ±10mA                        |

| Output Current: OUT                             | ±25mA                        |

| Output Short-Circuit Duration Note 3.           | Indefinite                   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The inputs are protected by ESD protection diodes to each power supply. If the input extends more than 500mV beyond the power supply, the input current should be limited to less than 10mA.

**Note 3**: A heat sink may be required to keep the junction temperature below the absolute maximum. This depends on the power supply voltage and how many amplifiers are shorted. Thermal resistance varies with the amount of PC board metal connected to the package. The specified values are for short traces connected to the leads.

# ESD, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| HBM    | Human Body Model ESD     | MIL-STD-883H Method 3015.8 | 8             | kV   |

| CDM    | Charged Device Model ESD | JEDEC-EIA/JESD22-C101E     | 2             | kV   |

# **Electrical Characteristics**

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 27^{\circ}C$ .  $V_{DD} = +1.8V$  to +5.5V,  $V_{IN+} = V_{DD}$ ,  $V_{IN-} = 1.2V$ ,  $R_{PU}=10k\Omega$ ,  $C_L=15pF$ .

| SYMBOL               | PARAMETER                             | CONDITIONS                                           |   | MIN                  | ТҮР    | MAX     | UNITS |

|----------------------|---------------------------------------|------------------------------------------------------|---|----------------------|--------|---------|-------|

| V <sub>DD</sub>      | Supply Voltage                        |                                                      | • | 1.8                  |        | 5.5     | V     |

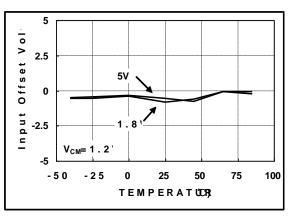

| Vos                  | Input Offset Voltage Note 1           | V <sub>CM</sub> = 1.2V                               | • | -2.0                 | 0.5    | +2.0    | mV    |

| Vos TC               | Input Offset Voltage Drift Note 1     | V <sub>CM</sub> = 1.2V                               |   |                      | 0.3    |         | μV/°C |

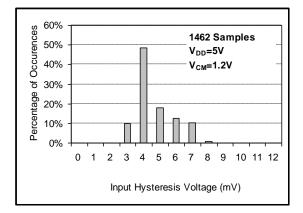

| VHYST                | Input Hysteresis Voltage Note 1       | V <sub>CM</sub> = 1.2V                               | • | 3                    | 4      | 7       | mV    |

| V <sub>HYST</sub> TC | Input Hysteresis Voltage Drift Note 1 | V <sub>CM</sub> = 1.2V                               |   | 20                   |        |         | µV/°C |

| l <sub>B</sub>       | Input Bias Current                    | V <sub>CM</sub> = 1.2V                               |   |                      | 6      |         | pА    |

| los                  | Input Offset Current                  | V <sub>CM</sub> = 1.2V                               |   | 4                    |        |         | pА    |

| R <sub>IN</sub>      | Input Resistance                      |                                                      |   | > 100                |        |         | GΩ    |

| CIN                  | Input Capacitance                     | Differential<br>Common Mode                          |   |                      | 2<br>4 |         | pF    |

| CMRR                 | Common Mode Rejection Ratio           | V <sub>CM</sub> = V <sub>SS</sub> to V <sub>DD</sub> | • | 50                   | 82     |         | dB    |

| V <sub>CM</sub>      | Common-mode Input Voltage<br>Range    |                                                      | • | V-                   |        | V+      | V     |

| PSRR                 | Power Supply Rejection Ratio          |                                                      | • | 60                   | 90     |         | dB    |

| Vон                  | High-Level Output Voltage             | Iout=-1mA                                            | • | V <sub>DD</sub> -0.3 |        |         | V     |

| Vol                  | Low-Level Output Voltage              | Iout=1mA                                             | • |                      |        | Vss+0.3 | V     |

| lsc                  | Output Short-Circuit Current          | Sink or source current                               |   |                      | 25     |         | mA    |

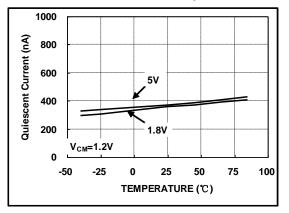

| la                   | Quiescent Current per Comparator      |                                                      | • |                      | 390    | 440     | nA    |

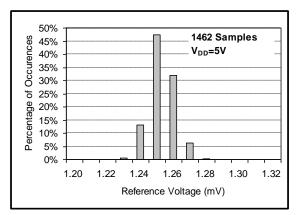

| Vout                 | Reference Voltage                     |                                                      |   | 1.230                | 1.248  | 1.265   | V     |

| VOUT TC              | Reference Voltage Drift               |                                                      |   | 150                  |        |         | μV/°C |

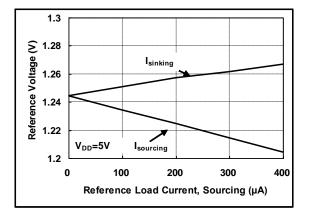

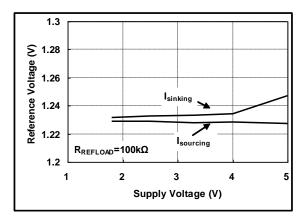

| Vout LC              | Reference Voltage Load                | 0µA≤I <sub>source</sub> ≤400µA                       |   |                      | 1.45   |         | μV/μA |

| VOULC                | Regulation                            | 0µA≤I <sub>sink</sub> ≤400µA                         |   |                      | 0.13   |         | μV/μA |

| t <sub>R</sub>       | Rising Time Note 2                    |                                                      |   |                      | 5      |         | ns    |

| tF                   | Falling Time                          |                                                      |   |                      | 5      |         | ns    |

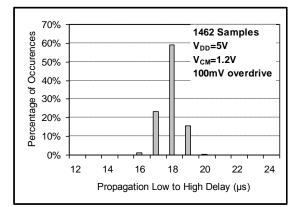

| t <sub>PD+</sub>     | Propagation Delay (Low-to-High)       | Overdrive=100mV, V <sub>IN-</sub> =1.2V              | • |                      | 13     | 19      | μs    |

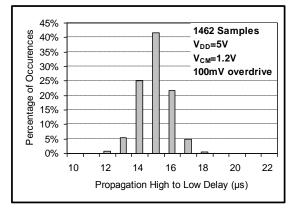

| t <sub>PD-</sub>     | Propagation Delay (High-to-Low)       | Overdrive=100mV, V <sub>IN-</sub> =1.2V              | • |                      | 14     | 18      | μs    |

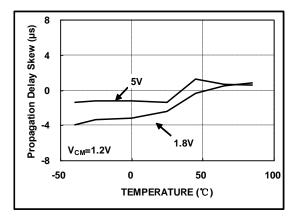

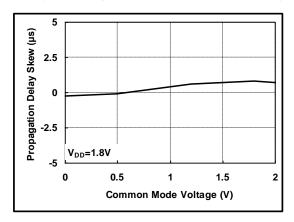

| T <sub>PD-SKEW</sub> | Propagation Delay Skew Note 3         | Overdrive=100mV, V <sub>IN-</sub> =1.2V              | • |                      | 1      | 5       | μs    |

**Note 1:** The input offset voltage is the average of the input-referred trip points. The input hysteresis is the difference between the input-referred trip points.

Note 2: For TP2025/TP2025U,  $t_R$  dependent on  $R_{PU}$  and  $C_{L-}$ .

Note 3: Propagation Delay Skew is defined as: tPD-SKEW = tPD+ - tPD-.

4

5V

M=1.2V

-25

4

2

0

-50

# **Typical Performance Characteristics**

# Input Offset Voltage vs. Temperature

Input Hysteresis Voltage vs. Temperature 10 Input Hysteresis Voltage (mV) 8 6

1.8V

25

TEMPERATURE (℃)

50

75

100

0

**Quiescent Current vs. Temperature**

Propagation Delay Skew vs. Temperature

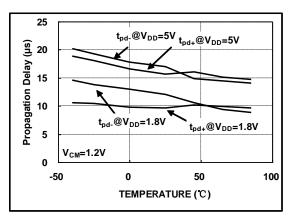

**Propagation Delay vs. Temperature**

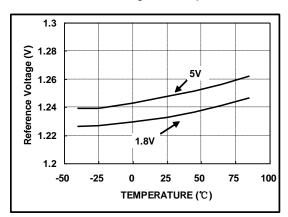

**Reference Voltage vs. Temperature**

# SC70, 1.8V, Nano-power Comparators with Voltage Reference

# **Typical Performance Characteristics**

Propagation Delay vs. Overdrive Voltage

## Propagation Delay vs. Overdrive Voltage

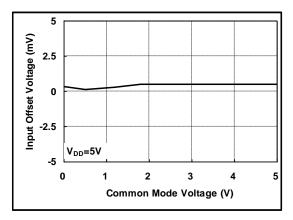

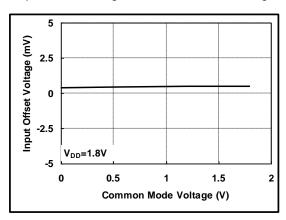

### Input Offset Voltage vs. Common Mode Voltage

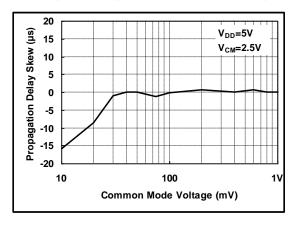

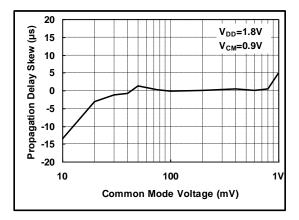

Propagation Delay Skew vs. Overdrive Voltage

#### Propagation Delay Skew vs. Overdrive Voltage

#### Input Offset Voltage vs. Common Mode Voltage

# **Typical Performance Characteristics**

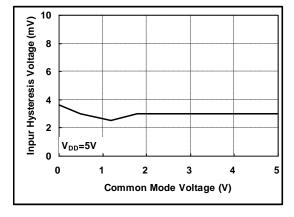

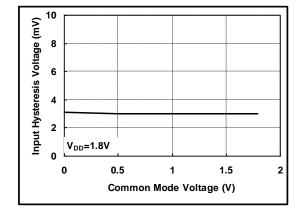

## Input Hysteresis Voltage vs. Common Mode Voltage

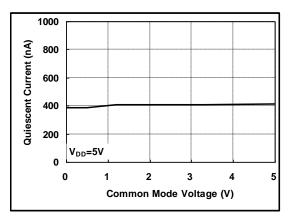

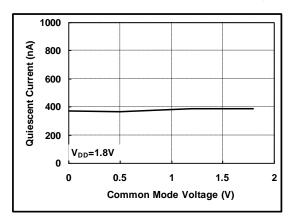

## Quiescent Current vs. Common Mode Voltage

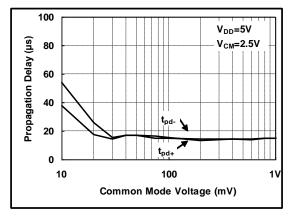

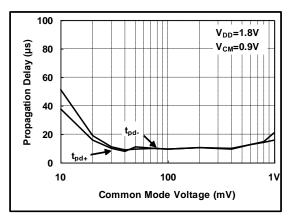

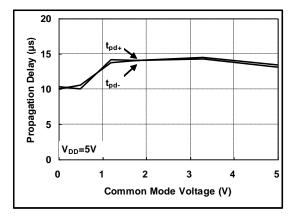

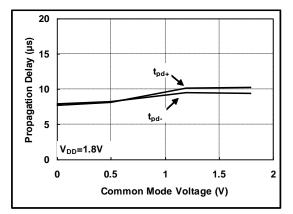

#### Propagation Delay vs. Common Mode Voltage

## Input Hysteresis Voltage vs. Common Mode Voltage

#### Quiescent Current vs. Common Mode Voltage

#### Propagation Delay vs. Common Mode Voltage

# SC70, 1.8V, Nano-power Comparators with Voltage Reference

# **Typical Performance Characteristics**

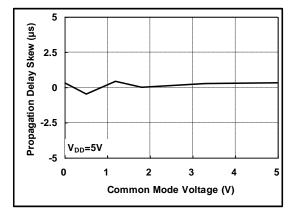

## Propagation Delay Skew vs. Common Mode Voltage

## Input Offset Voltage Distribution

## **Quiescent Current Distribution**

#### Propagation Delay Skew vs. Common Mode Voltage

#### Input Hysteresis Voltage Distribution

#### Low to High Propagation Delay Distribution

# SC70, 1.8V, Nano-power Comparators with Voltage Reference

# **Typical Performance Characteristics**

## High to Low Propagation Delay Distribution

**Reference Voltage Distribution**

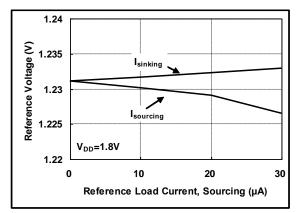

## Reference Voltage vs. Reference Load Current

50% 1462 Samples Percentage of Occurences 45% V<sub>DD</sub>=5V 40% V<sub>CM</sub>=1.2V 35% 100mV overdrive 30% 25% 20% 15% 10% 5% 0% -2 0 2 4 6 8 10 Propagation Delay Skew (µs)

#### **Propagation Delay Skew Distribution**

#### Reference Voltage vs. Supply Voltage

## Reference Voltage vs. Reference Load Current

# SC70, 1.8V, Nano-power Comparators with Voltage Reference

# **Typical Performance Characteristics**

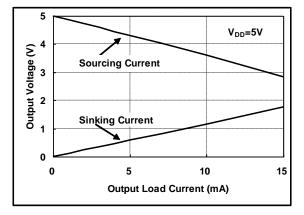

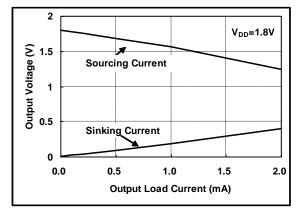

## Output Voltage Headroom vs. Output Load Current

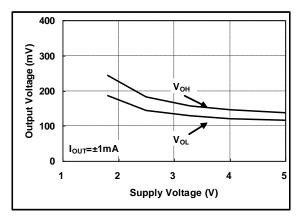

## Output Voltage Headroom vs. Supply Voltage

# Output Voltage Headroom vs. Output Load Current

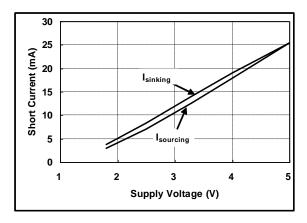

#### **Output Short Current vs. Supply Voltage**

## **Pin Functions**

**–IN:** Inverting Input of the Comparator. Voltage range of this pin can go from  $V^- - 0.3V$  to  $V^+ + 0.3V$ .

**+IN:** Non-Inverting Input of Comparator. This pin has the same voltage range as –IN.

**V+:** Positive Power Supply. Typically the voltage is from 1.8V to 5.5V. Split supplies are possible as long as the voltage between V+ and V– is between 1.8V and 5.5V. A bypass capacitor of  $0.1\mu$ F as close to the part as possible should be used between power supply pins or between supply pins and ground.

**V**<sup>-</sup>: Negative Power Supply. It is normally tied to ground. It can also be tied to a voltage other than ground as long as the voltage between V<sup>+</sup> and V<sup>-</sup> is from 1.8V to 5.5V. If it is not connected to ground, bypass it with a capacitor of  $0.1\mu$ F as close to the part as possible.

**OUT:** Comparator Output. The voltage range extends to within millivolts of each supply rail.

Ref: Reference voltage output.

**LATCH:** Active Low Latch enable. Latch enable threshold is 1/2 V+ above negative supply rail.

NC: No Connection.

## Operation

The TP202x family single-supply comparators feature internal hysteresis, internal reference, high speed, and ultra-low power. Input signal range extends beyond the negative and positive power supplies. The output can even extend all the way to the negative supply. The input stage is comprised of two CMOS differential amplifiers, a PMOS stage and NMOS stage that are active over different ranges of common mode input voltage. Rail-to-rail input voltage range and low-voltage single-supply operation make these devices ideal for portable equipment.

## **Applications Information**

## Inputs

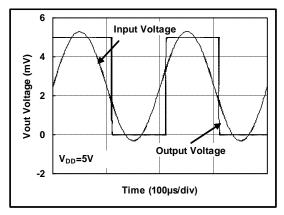

The TP202x comparator family uses CMOS transistors at the input which prevent phase inversion when the input pins exceed the supply voltages. Figure 1 shows an input voltage exceeding both supplies with no resulting phase inversion.

Figure 1. Response time to Input Voltage

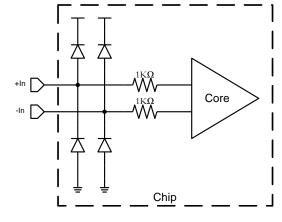

The electrostatic discharge (ESD) protection input structure of two back-to-back diodes and  $1k\Omega$  series resistors are used to limit the differential input voltage applied to the precision input of the comparator by clamping input voltages that exceed supply voltages, as shown in Figure 2.

Large differential voltages exceeding the supply voltage should be avoided to prevent damage to the input stage.

# **Internal Hysteresis**

Most high-speed comparators oscillate in the linear region because of noise or undesired parasitic feedback. This tends to occur when the voltage on one input is at or equal to the voltage on the other input. To counter the parasitic effects and noise, the TP202x implements internal hysteresis.

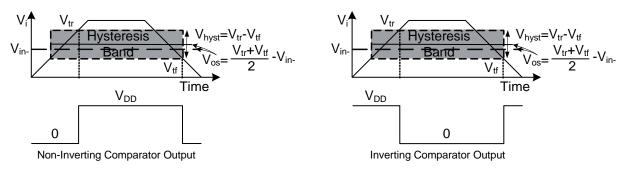

The hysteresis in a comparator creates two trip points: one for the rising input voltage and one for the falling input voltage. The difference between the trip points is the hysteresis. When the comparator's input voltages are equal, the hysteresis effectively causes one comparator input voltage to move quickly past the other, thus taking the input out of the region where oscillation occurs. Figure 3 illustrates the case where IN- is fixed and IN+ is varied. If the inputs were reversed, the figure would look the same, except the output would be inverted.

Figure 3. Comparator's hysteresis and offset

# **External Hysteresis**

Greater flexibility in selecting hysteresis is achieved by using external resistors. Hysteresis reduces output chattering when one input is slowly moving past the other. It also helps in systems where it is best not to cycle between high and low states too frequently (e.g., air conditioner thermostatic control). Output chatter also increases the dynamic supply current.

## Non-Inverting Comparator with Hysteresis

A non-inverting comparator with hysteresis requires a two-resistor network, as shown in Figure 4 and a voltage reference ( $V_r$ ) at the inverting input.

## Figure 4. Non-Inverting Configuration with Hysteresis

Consider the comparator of TP2021/TP2021U, when  $V_i$  is low, the output is also low. For the output to switch from low to high,  $V_i$  must rise up to  $V_{tr}$ . When  $V_i$  is high, the output is also high. In order for the comparator to switch back to a low state,  $V_i$  must equal  $V_{tf}$  before the non-inverting input V+ is again equal to  $V_r$ .

$$V_{r} = \frac{R_2}{R_1 + R_2} V_{tr}$$

$$V_{r} = (V_{DD} - V_{tf}) \frac{R_1}{R_1 + R_2} + V_{tf}$$

## SC70, 1.8V, Nano-power Comparators with Voltage Reference

$$V_{tr} = \frac{R_1 + R_2}{R_2} V_r$$

$$V_{tf} = \frac{R_1 + R_2}{R_2} V_r - \frac{R_1}{R_2} V_{DD}$$

$$V_{hy\,st} = V_{tr} - V_{tf} = \frac{R_1}{R_2} V_{DD}$$

As for the TP2025/TP2025U, a pull-up resistor should be placed between output and the supply. The formula for calculating  $V_{tf}$  is slight difference with TP2021/TP2021U, so does the hysteresis voltage  $V_{hyst}$ .

$$V_{r} = (V_{DD} - V_{tf}) \frac{R_{1}}{R_{1} + R_{2} + R_{PU}} + V_{tf}$$

$$V_{tf} = \frac{R_{1} + R_{2} + R_{PU}}{R_{2} + R_{PU}} V_{r} - \frac{R_{1}}{R_{2} + R_{PU}} V_{DD}$$

$$v_{hyst} \approx \frac{R_1}{R_2 + R_{PU}} v_{DD}$$

if  $R_{PU} << R_2$

## Inverting Comparator with Hysteresis

The inverting comparator with hysteresis requires a two-resistor network that is referenced to the comparator supply voltage ( $V_{DD}$ ), as shown in Figure 5.

#### Figure 5. Inverting Configuration with Hysteresis

Consider the comparator of TP2021/TP2021U, when  $V_i$  is greater than  $V_+$ , the output voltage is low. In this case, the three network resistors can be presented as paralleled resistor  $R_2 \parallel R_3$  in series with  $R_1$ . When  $V_i$  at the inverting input is less than  $V_+$ , the output voltage is high. The three network resistors can be represented as  $R_1 \parallel R_3$  in series with  $R_2$ .

$$V_{tr} = \frac{R_1}{R_2 + R_1} (V_{DD} - V_{ref}) + V_{ref}$$

$$V_{tf} = \frac{R_2}{R_1 + R_2} V_{ref}$$

www.3peakic.com

$$V_{hyst} = V_{tr} - V_{tf} = \frac{R_1}{R_1 + R_2} V_{DD}$$

As for the TP2025/TP2025U, a pull-up resistor should be placed between output and the supply. The formula for calculating  $V_{tr}$  is slight difference with TP2021/TP2021U, so does the hysteresis voltage  $V_{hyst}$ .

$$V_{tr} = \frac{R_1}{R_{PU} + R_2 + R_1} (V_{DD} - V_{ref}) + V_{ref}$$

$$V_{hyst} = \frac{R_1}{R_1 + R_2} V_{DD}$$

if  $R_{PU} << R_2$

# Low Input Bias Current

The TP202x family is a CMOS comparator family and features very low input bias current in pA range. The low input bias current allows the comparators to be used in applications with high resistance sources. Care must be taken to minimize PCB Surface Leakage. See below section on "PCB Surface Leakage" for more details.

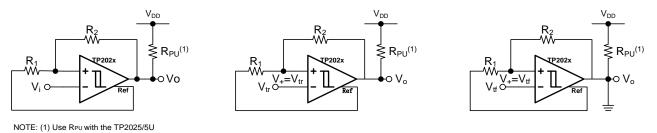

## PCB Surface Leakage

In applications where low input bias current is critical, Printed Circuit Board (PCB) surface leakage effects need to be considered. Surface leakage is caused by humidity, dust or other contamination on the board. Under low humidity conditions, a typical resistance between nearby traces is  $10^{12}\Omega$ . A 5V difference would cause 5pA of current to flow, which is greater than the TP202x's input bias current at +27°C (±6pA, typical). It is recommended to use multi-layer PCB layout and route the comparator's -IN and +IN signal under the PCB surface.

The effective way to reduce surface leakage is to use a guard ring around sensitive pins (or traces). The guard ring is biased at the same voltage as the sensitive pin. An example of this type of layout is shown in Figure 6. for Inverting configuration application.

- 1. For Non-Inverting Configuration:

- a) Connect the non-inverting pin ( $V_{IN}$ +) to the input with a wire that does not touch the PCB surface.

- b) Connect the guard ring to the inverting input pin ( $V_{IN}$ -). This biases the guard ring to the same reference as the comparator.

- 2. For Inverting Configuration:

- a) Connect the guard ring to the non-inverting input pin (V<sub>IN</sub>+). This biases the guard ring to the same reference voltage as the comparator (e.g., V<sub>DD</sub>/2 or ground).

- b) Connect the inverting pin (V\_{IN-}) to the input with a wire that does not touch the PCB surface.

## Figure 6. Example Guard Ring Layout for Inverting Comparator

# Ground Sensing and Rail to Rail Output

The TP202x family implements a rail-to-rail topology that is capable of swinging to within 10mV of either rail. Since the inputs can go 300mV beyond either rail, the comparator can easily perform 'true ground' sensing.

The maximum output current is a function of total supply voltage. As the supply voltage of the comparator increases, the output current capability also increases. Attention must be paid to keep the junction temperature of the IC below 150°C when the output is in continuous short-circuit condition. The output of the amplifier has reverse-biased ESD diodes connected to each supply. The output should not be forced more than 0.5V beyond either supply, otherwise current will flow through these diodes.

# ESD

The TP202x family has reverse-biased ESD protection diodes on all inputs and output. Input and output pins can not be biased more than 300mV beyond either supply rail.

# **Power Supply Layout and Bypass**

The TP202x family's power supply pin should have a local bypass capacitor (i.e.,  $0.01\mu$ F to  $0.1\mu$ F) within 2mm for good high frequency performance. It can also use a bulk capacitor (i.e.,  $1\mu$ F or larger) within 100mm to provide large, slow currents. This bulk capacitor can be shared with other analog parts.

Good ground layout improves performance by decreasing the amount of stray capacitance and noise at the comparator's inputs and outputs. To decrease stray capacitance, minimize PCB lengths and resistor leads, and place external components as close to the comparator' pins as possible.

# **Proper Board Layout**

The TP202x family is a series of fast-switching, high-speed comparator and requires high-speed layout considerations. For best results, the following layout guidelines should be followed:

1. Use a printed circuit board (PCB) with a good, unbroken low-inductance ground plane.

2. Place a decoupling capacitor (0.1µF ceramic, surface-mount capacitor) as close as possible to supply.

3. On the inputs and the output, keep lead lengths as short as possible to avoid unwanted parasitic feedback around the comparator. Keep inputs away from the output.

4. Solder the device directly to the PCB rather than using a socket.

5. For slow-moving input signals, take care to prevent parasitic feedback. A small capacitor (1000 pF or less) placed between the inputs can help eliminate oscillations in the transition region. This capacitor causes some degradation to propagation delay when the impedance is low. The topside ground plane should be placed between the output and inputs.

6. The ground pin ground trace should run under the device up to the bypass capacitor, thus shielding the inputs from the outputs.

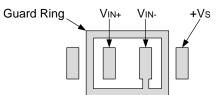

# Typical Applications

## **IR Receiver**

The TP202x is an ideal candidate to be used as an infrared receiver shown in Figure 7. The infrared photo diode creates a current relative to the amount of infrared light present. The current creates a voltage across  $R_D$ . When this voltage level cross the voltage applied by the voltage divider to the inverting input, the output transitions. Optional  $R_o$  provides additional hysteresis for noise immunity.

NOTE: (1) Use RPU with the TP2025

## Figure 7. IR Receiver

## **Relaxation Oscillator**

A relaxation oscillator using TP2021 is shown in Figure 8. Resistors  $R_1$  and  $R_2$  set the bias point at the comparator's inverting input. The period of oscillator is set by the time constant of  $R_4$  and  $C_1$ . The maximum frequency is limited by the large signal propagation delay of the comparator. TP2021's low propagation delay guarantees the high frequency oscillation.

If the inverted input ( $V_{C1}$ ) is lower than the non-inverting input ( $V_A$ ), the output is high which charges  $C_1$  through  $R_4$  until  $V_{C1}$  is equal to  $V_A$ . The value of  $V_A$  at this point is

$$v_{A1} = \frac{v_{DD} \bullet R_2}{R_1 \parallel R_3 + R_2}$$

At this point the comparator switches pulling down the output to the negative rail. The value of V<sub>A</sub> at this point is

$$\mathbf{V}_{A2} = \frac{\mathbf{V}_{DD} \bullet \mathbf{R}_2 \parallel \mathbf{R}_3}{\mathbf{R}_1 + \mathbf{R}_2 \parallel \mathbf{R}_3}$$

If  $R_1{=}R_2{=}R_3$ , then  $V_{A1}{=}2V_{DD}$  /3, and  $V_{A2}{=}$   $V_{DD}/3$

The capacitor  $C_1$  now discharges through  $R_4$ , and the voltage  $V_C$  decreases till it is equal to  $V_{A2}$ , at which point the comparator switches again, bringing it back to the initial stage. The time period is equal to twice the time it takes to discharge  $C_1$  from  $2V_{DD}/3$  to  $V_{DD}/3$ . Hence the frequency is:

$$Freq = \frac{1}{2 \bullet \ln 2 \bullet R_4 \bullet C_1}$$

Figure 8. Relaxation Oscillator

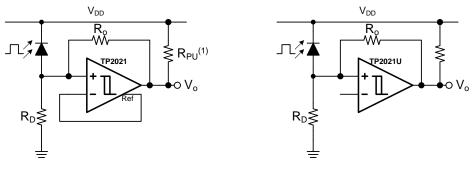

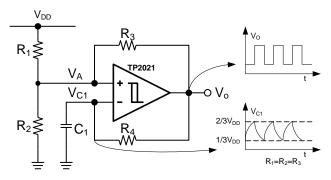

## **Battery Level Detect**

The low power consumption and 1.8V supply voltage of the TP202x make it an excellent candidate for battery-powered applications. Figure 9 shows the TP202x configured as a low battery level detector for a 3V battery.

BatteryGood =  $V_r \bullet (R_1 + R_2)/R_2$

NOTE: (1) Use RPU with the TP2025/5U

## Figure 9. Battery Level Detect

SC70, 1.8V, Nano-power Comparators with Voltage Reference

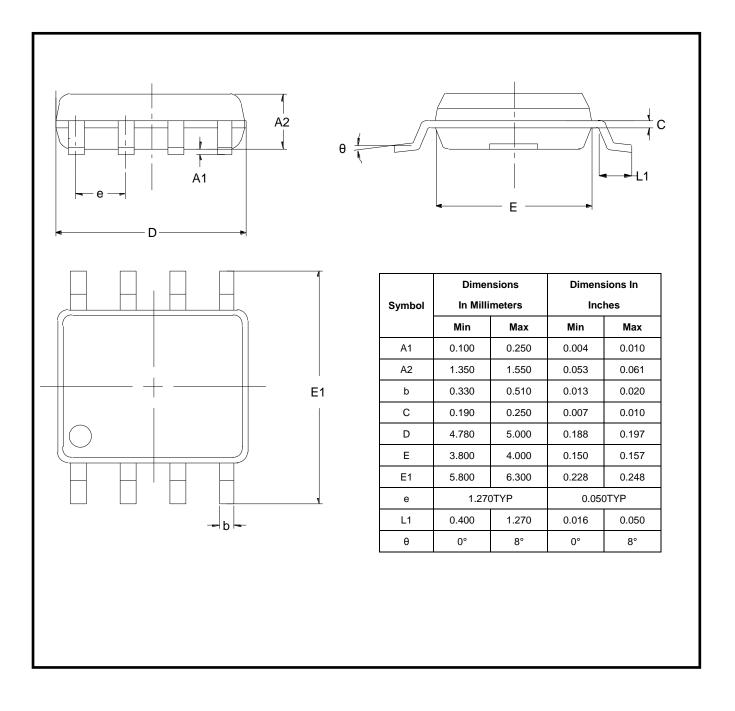

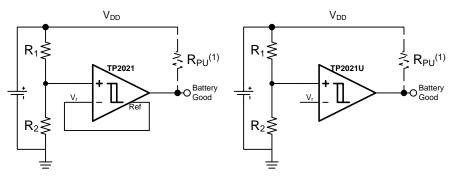

# **Package Outline Dimensions**

SC-70-5 / SC-70-6 (SOT353 / SOT363)

# **Package Outline Dimensions**

SOT23-5 / SOT23-6

SC70, 1.8V, Nano-power Comparators with Voltage Reference

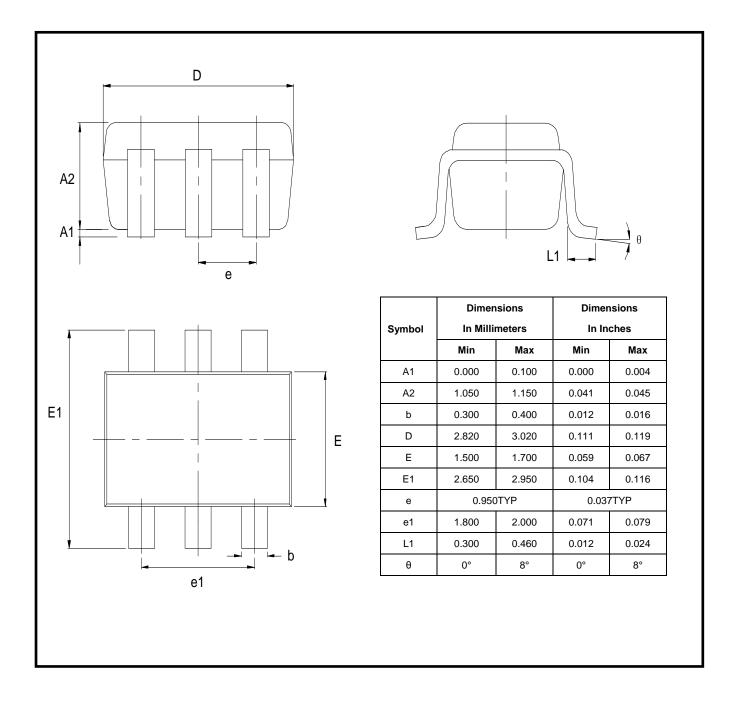

# **Package Outline Dimensions**

SO-8 (SOIC-8)