# **Brushed DC Motor Full-Bridge Gate Driver**

### **FEATURES**

- Single Channel H-bridge Gate Driver

Drive 2 external P+N MOSFETs

- . Wide 5V to 40V Operating Voltage

- Supports 1.8V, 3.3V, 5V Logic Inputs

- . PWM Control Interface

- . VM Undervoltage Lockout (UVLO)

- . Overcurrent Protection (OCP)

- . Thermal Shutdown (TSD)

- Small Package and Footprint

-DFN3x3-10 package

## **APPLICATIONS**

- . Brushed DC Motors

- Mopping machine

- . Massager

- Robots

### **GENERAL DESCRIPTION**

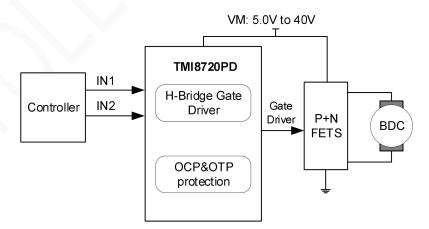

TMI8720PD is an H-bridge gate driver that uses 2 external P+N channel MOSFETs. It is mainly used to drive 5.5V to 40V brushed DC motors, and other small machines. There are two logic input terminals, used to control the motor forward, reverse and brake, PWM mode control mode.

The maximum current capacity is up to 10A, support for ultra-low power sleep mode; built-in UVLO, Thermal Shutdown, OCP protection circuit.

The package form of TMI8720PD is DFN3x3-10 package, which complies with ROHS specifications, and the lead frame is 100% lead-free.

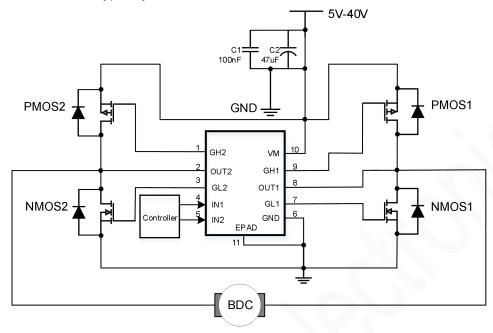

## TYPICAL APPILCATION

**Figure 1. Basic Application Circuit**

www.toll-semi.com

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| Parameter                                      | Min  | Max    | Unit |

|------------------------------------------------|------|--------|------|

| Power supply voltage (VM)                      | -0.3 | 45     | V    |

| Logic input voltage (IN1, IN2)                 | -0.3 | 7      | V    |

| High-side gate pin voltage (GH1, GH2)          | -0.3 | VM-7   | ٧    |

| Low-side gate pin voltage (GL1, GL2)           | -0.3 | 7      | V    |

| Continuous phase node pin voltage (OUT1, OUT2) | -0.3 | VM+0.3 | V    |

| T <sub>a</sub> , Operating ambient temperature | -30  | 85     | °C   |

| Operating junction temperature (Note 2)        | -40  | 150    | °C   |

| Storage temperature                            | -65  | 150    | °C   |

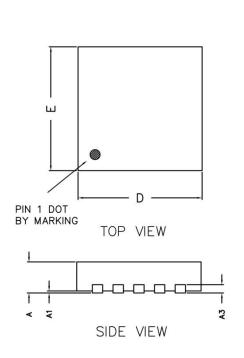

## **PACKAGE/ORDER INFORMATION**

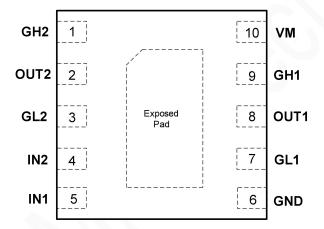

DFN3x3-10(Top view)

| Part Number | Package   | Top mark | Quantity/ Reel |

|-------------|-----------|----------|----------------|

|             |           | TMI      |                |

| TMI8720PD   | DFN3x3-10 | 8720PD   | 5000           |

|             |           | xxxxOH   |                |

TMI8720PD device is Pb-free and RoHS compliant.

## **PIN FUNCTIONS**

| Pin | Name | Function                                                                  |

|-----|------|---------------------------------------------------------------------------|

| 1   | GH2  | High-side gate, Connect to high-side FET gate.                            |

| 2   | OUT2 | Connect to high-side FET source and low-side FET drain.                   |

| 3   | GL2  | Low-side gate, Connect to low-side FET gate.                              |

| 4   | IN2  | Logic inputs. Controls the output. Has internal pulldowns.                |

| 5   | IN1  | Logic inputs. Controls the output. Has internal pulldowns.                |

| 6   | GND  | Logic ground. Connect to board ground.                                    |

| 7   | GL1  | Connect to high-side FET source and low-side FET drain.                   |

| 8   | OUT1 | Low-side gate, Connect to low-side FET gate.                              |

| 9   | GH1  | High-side gate, Connect to high-side FET gate.                            |

| 10  | VM   | 5V to 40V power supply input. Connect a 0.1µF bypass capacitor to ground, |

| 10  | VIVI | as well as a sufficient bulk capacitance rated for VM.                    |

| 11  | GND  | Ground Pin (Exposed Pad).                                                 |

## **ESD RATING**

| Items     | Description                   | Value | Unit |

|-----------|-------------------------------|-------|------|

| $V_{ESD}$ | Human Body Model for all pins | ±2000 | V    |

## **JEDEC specification JS-001**

## **RECOMMENDED OPERATING CONDITIONS**

| Items       | Description                | Min  | Max | Unit |  |  |  |  |

|-------------|----------------------------|------|-----|------|--|--|--|--|

| VM          | Power supply voltage range | 5    | 40  | V    |  |  |  |  |

| Logic input | V <sub>IN_</sub> X         | -0.3 | 6   | V    |  |  |  |  |

| Logic input | F <sub>IN_X</sub>          | 0    | 50  | kHz  |  |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

## $T_A = 25$ °C, over recommended operating conditions unless otherwise noted.)

| Parameter                                        | rameter Symbol Conditions |                                                 | Min  | Тур. | Max  | Unit |

|--------------------------------------------------|---------------------------|-------------------------------------------------|------|------|------|------|

| Power supply (VM)                                |                           |                                                 |      |      |      |      |

| Operation voltage                                | $V_{VM}$                  |                                                 | 5    |      | 40   | V    |

| Shutdown current                                 | I <sub>VMQ</sub>          | VM=24V, IN1=IN2=0V, no load                     |      |      | 20   | nA   |

|                                                  |                           | VM=24V, IN1=IN2=5V or IN1=5V                    |      |      |      |      |

| Standby current                                  | $I_{VM}$                  | l <sub>VM</sub> & IN2=0V or IN1=0V & IN2=5V, no |      | 0.5  | 0.6  | mA   |

|                                                  |                           | load                                            |      |      |      |      |

| PWM current   VM=24V, IN1=5V, IN2=50kHz, no load |                           | 1                                               | 1.8  | 3    | mA   |      |

| VM undervoltage                                  | V <sub>UVLO_fall</sub>    | VM falls until UVLO triggers                    | 4.2  | 4.4  | 4.5  | V    |

| lockout                                          | V <sub>UVLO_rise</sub>    | VM rises until operation recovers               | 4.5  | 4.7  | 4.8  | V    |

| Logic inputs                                     |                           |                                                 |      |      |      |      |

| Input logic high voltage                         | V <sub>INH</sub>          |                                                 | 1.4  |      | 5.5  | V    |

| Input logic low voltage                          | V <sub>INL</sub>          |                                                 |      |      | 0.7  | V    |

| Input logic high current                         | I <sub>INH</sub>          | VM=24V, IN <sub>X</sub> =5V                     |      | 50   | 75   | μA   |

| Input logic low current                          | I <sub>INL</sub>          | VM=24V, IN <sub>X</sub> =0V                     |      |      | 1    | μA   |

| FET GATE DRIVERS (                               | GH1, GH2,                 | GL1, GL2, OUT1, OUT2)                           |      |      |      |      |

|                                                  | V <sub>GHS</sub>          | VM>24V                                          | -5.6 | -5.8 | -6.0 | V    |

| High-side VGS gate drive (gate-to- source)       |                           | VM=12V                                          | -5.5 | -5.7 | -5.8 |      |

| anve (gate to beares)                            |                           | VM=8V                                           | -5.1 | -5.2 | -5.3 |      |

|                                                  |                           | VM>24V                                          | 5.6  | 5.8  | 6.0  |      |

| Low-side VGS gate drive (gate-to- source)        | $V_{\text{GLS}}$          | VM=12V                                          | 5.5  | 5.7  | 5.8  | V    |

| drive (gate-to- source)                          |                           | VM=8V                                           | 5.4  | 5.5  | 5.6  |      |

| High-side Gate                                   |                           | Peak Sink current                               |      | 50   |      | _    |

| Drive current                                    | $I_{GHX}$                 | Peak Source current                             |      | 200  |      | mA   |

| Low-side Gate                                    |                           | Peak Sink current                               |      | 200  |      |      |

| Drive current                                    | $I_{GLX}$                 | Peak Source current                             |      | 50   |      |      |

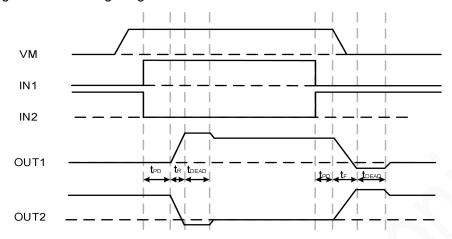

| Output dead time                                 | t <sub>DEAD</sub>         | Body diode conducting                           |      | 300  |      | ns   |

| Output rise time                                 | t <sub>RISE</sub>         | VM=24V, OUTx rising 10% to 90%                  |      | 165  |      | ns   |

| Output fall time                                 | t <sub>FALL</sub>         | VM=24V, OUTx falling 90% to 10%                 |      | 150  |      | ns   |

| Input to output propagation delay                | t <sub>PD</sub>           |                                                 |      | 150  |      | ns   |

## **ELECTRICAL CHARACTERISTICS** (Continued)

$T_A = 25$ °C, over recommended operating conditions unless otherwise noted)

| Over temperature pro    | tection                   |                               |      |      |   |      |

|-------------------------|---------------------------|-------------------------------|------|------|---|------|

| Thermal shutdown        | T <sub>SD (Note 3)</sub>  |                               |      | 160  |   | °C   |

| Thermal shutdown        | T <sub>HYS (Note 3)</sub> |                               |      | 35   |   |      |

| hysteresis              | 11110 (14010 0)           |                               |      |      |   |      |

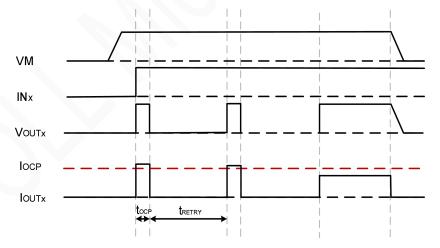

| Over current protection | on                        |                               |      |      |   |      |

|                         | VDS H-side                | VM=24V, High side FETs: VM –  |      | 0.38 |   | V    |

| N/                      |                           | OUTx                          |      | 0.50 |   | V    |

| V <sub>DS(OCP)</sub>    | V                         | VM=24V, Low side FETs: OUTx – | 0.26 |      | V |      |

|                         | V <sub>DS_L-side</sub>    | GND                           |      | 0.20 |   | V    |

| Overcurrent deglitch    | 4                         |                               |      | 2.5  |   |      |

| time                    | tocp                      |                               |      | 3.5  |   | μs   |

| Overcurrent retry time  | t <sub>RETRY</sub>        |                               |      | 2.5  |   | ms   |

|                         | •NEIRY                    |                               |      | 2.5  |   | 1113 |

Note 1: Absolute Maximum Ratings are values beyond which the life of devices may be impaired.

**Note 2:**  $T_J$  is calculated from the amIN2ent temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:  $T_J = T_A + P_D \times \theta_{JA}$ . The maximum allowable continuous power dissipation at any amIN2ent temperature is calculated by  $P_{D \text{ (MAX)}} = (T_{J \text{(MAX)}} - T_A)/\theta_{JA}$ .

Note 3: Thermal shutdown threshold and hysteresis are guaranteed by design.

### **OPERATION**

#### Overview

The TMI8720PD is an H-bridge gate driver. The device integrates FET gate drivers in order to control 2 external P+N channel MOSFETs.. The device can be powered with a supply voltage between 5V to 40 V.

### **Bridge Control**

The TMI8720PD output consists of 2 external P+N channel MOSFETs. TMI8720PD that are designed to drive high current. These outputs are controlled by the two logic inputs IN1and IN2 as listed in Table 1.

Table 1. H-Bridge Control

| IN1 | IN2 | OUT1   | OUT2   | DESCRIPTION                        |  |  |

|-----|-----|--------|--------|------------------------------------|--|--|

| L   | L   | High-Z | High-Z | Coast; H-bridge disabled to High-Z |  |  |

| L   | Н   | L      | Н      | Reverse (Current OUT2 → OUT1)      |  |  |

| Н   | L   | Н      | L      | Forward (Current OUT1 → OUT2)      |  |  |

| Н   | Н   | L      | L      | Brake; low-side slow decay         |  |  |

The inputs can be set to static voltages for 100% duty cycle drive, or they can be pulse-width modulated (PWM) for variable motor speed. When the VM voltage is set above the UVLO point and the logic input pins is left floating or connected to logic low voltage, the OUTx is at high

www.toll-semi.com

resistance state. The OUTx is connected to GND via the internal N-channel MOSFET once the corresponding Inx is turned logic high.

Figure 2. Propagation Delay Time

### VM Undervoltage Lockout (UVLO)

If at any time the voltage on the VM pin falls below the undervoltage-lockout threshold voltage, all FETs in the device will be disabled. Operation resumes when VM rises above the UVLO threshold.

### **Overcurrent Protection (OCP)**

If the output current exceeds the OCP threshold, IOCP, for longer than  $t_{\text{OCP}}$ , all FETs in the device are disabled. After a duration of  $t_{\text{RETRY}}$ , the MOSFET is re-enabled according to the state of the INx pins. If the overcurrent fault is still present, the cycle repeats; otherwise normal device operation resumes.

Figure 3. Over current protection Time Periods

### Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all FETs in the device are disabled. After the die temperature has fallen to a safe level, operation automatically resumes.

## **APPLICATION INFORMATION**

The TMI8720PD devices are typically used to drive two directional motors as below:

Figure 4. TMI8720PD Typical Application

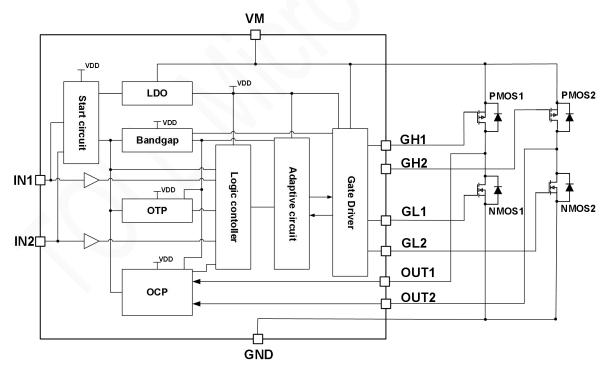

## **Block Diagram**

Figure 5. TMI8720PD Block Diagram

TMÍ SUNTO

www.toll-semi.com

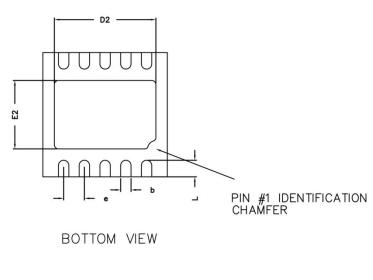

# **Package Information**

## DFN3x3-10

Unit: mm

| Symbol | Dimensions In Millimeters |      |      | Cumbal | Dimensions In Millimeters |      |      |

|--------|---------------------------|------|------|--------|---------------------------|------|------|

|        | Min                       | Nom  | Max  | Symbol | Min                       | Nom  | Max  |

| Α      | 0.70                      | 0.75 | 0.80 | b      | 0.18                      | 0.23 | 0.28 |

| A1     | 0.00                      | -    | 0.05 | L      | 0.30                      | 0.40 | 0.50 |

| А3     | 0.2 REF                   |      |      | D2     | 2.30                      | 2.45 | 2.55 |

| D      | 2.95                      | 3.00 | 3.05 | E2     | 1.50                      | 1.65 | 1.75 |

| E      | 2.95                      | 3.00 | 3.05 | е      | 0.50 BSC                  |      |      |

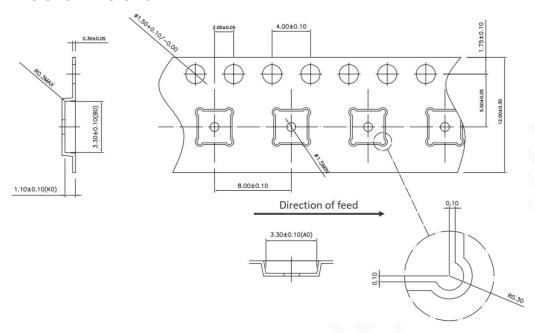

### **TAPE AND REEL INFORMATION**

### **TAPE DIMENSIONS: DFN3x3-10**

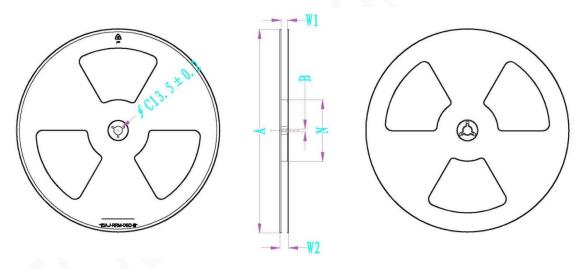

### **REEL DIMENSIONS: DFN3x3-10**

Unit: mm

| Ø A     | ØС       | В       | W1       | W2       | N       |

|---------|----------|---------|----------|----------|---------|

| 330±1.0 | 13.5±0.2 | 4.7±0.5 | 13.4±0.5 | 17.4±0.5 | 100±0.5 |

### Note:

- 1) All Dimensions are in Millimeter

- 2) Quantity of Units per Reel is 5000

- 3) MSL level is level 3.

## **Important Notification**

This document only provides product information. Xi'an TOLL Microelectronic Inc. (TMI) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

Xi'an TOLL Microelectronic Inc. (TMI) cannot assume responsilN2lity for use of any circuitry other than circuitry entirely embodied in a TMI product. No circuit patent licenses are implied.

All rights are reserved by Xi'an TOLL Microelectronic Inc. http://www.toll-semi.com