**TMP1826** SBOSA45C - FEBRUARY 2022 - REVISED MAY 2023

# TMP1826 1-Wire®, ±0.2°C Accurate Temperature Sensor With 2Kb EEPROM

## 1 Features

- 1-Wire® interface with multi-drop shared bus and cyclic redundancy check (CRC)

- Bus powered with operating voltage: 1.7 V to 5.5 V

- IEC 61000-4-2 ESD for 8-kV contact discharge

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- High-accuracy digital temperature sensor (WSON package)

- ±0.2°C (maximum) from +10°C to +45°C

- ±0.3°C (maximum) from –40°C to +105°C

- ±0.4°C (maximum) from –55°C to +150°C

- High-accuracy digital temperature sensor (VSSOP package)

- ±0.3°C (maximum) from –20°C to +85°C

- ±0.5°C (maximum) from -55°C to +150°C

- Temperature measurement current: 94 µA

- Shutdown current: 1.3 µA

- 16-bit temperature resolution: 7.8125 m°C (1 LSB)

- Fast data rates of 90 kbps in overdrive speed

- Flexible user programmable short address modes for faster device address

- 2Kb EEPROM features:

- Write operation in 64-bit block size

- Continuous read mode

- Read with write protection with 256-bit page size

- Programming current: 178 μA

- NIST traceable factory-programmed non erasable 64-bit identification number for device addressing

- Four configurable open-drain digital input-output and temperature alert

# 2 Applications

- Factory automation and control

- **Appliances**

- Medical accessories

- **CPAP** machines

- Battery charger ICs

- EV charging infrastructure

- LED lighting

- Temperature transmitters

- Cold chain

# 3 Description

The TMP1826 is a high-accuracy, 1-Wire compatible digital output temperature sensor with integrated 2Kb EEPROM and a wide operating temperature range from -55°C to +150°C. The TMP1826 provides a high accuracy of ±0.1°C (typical)/±0.2°C (maximum) across the temperature range of +10°C to +45°C. Each device comes with a factory programmed 64-bit unique identification number for addressing and NIST traceability. The TMP1826 supports both standard speed for legacy application and overdrive mode with 90-kbps data rate for low latency communication across a wide voltage range of 1.7 V to 5.5 V.

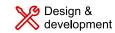

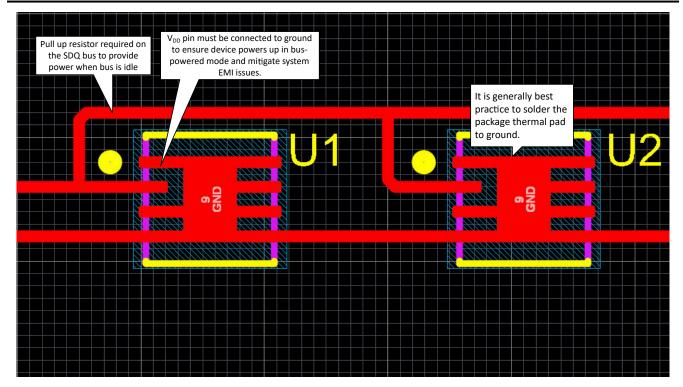

In the simplest mode of operation, the TMP1826 1-Wire interface, with an integrated 8-kV IEC-61000-4-2 ESD protection on the data pin, requires only a single connection and a ground return in bus powered mode, which simplifies and reduces cost by reducing the number of wires and external protection components. Additionally, there is the V<sub>DD</sub> power pin also available for applications that may want to have a dedicated power supply.

# **Package Information**

| PART NUMBER | PACKAGE <sup>(1)(2)</sup> | PACKAGE SIZE<br>(NOM) |

|-------------|---------------------------|-----------------------|

| TMP1826     | WSON (8)                  | 2.50 mm × 2.50 mm     |

| TMP 1820    | VSSOP (8)                 | 3.00 mm × 4.90 mm     |

- For all available packages, see the orderable addendum at the end of the data sheet.

- These package options are compatible with 1-Wire® devices. 1-Wire is a registered trademark of Maxim Integrated Products Inc.

Simplified Schematic

# **Table of Contents**

| 1 Features                           | 1 | 9.2 Functional Block Diagram                          | . 15 |

|--------------------------------------|---|-------------------------------------------------------|------|

| 2 Applications                       |   | 9.3 Feature Description                               |      |

| 3 Description                        |   | 9.4 Device Functional Modes                           |      |

| 4 Revision History                   |   | 9.5 Programming                                       |      |

| 5 Description (cont.)                |   | 9.6 Register Map                                      |      |

| 6 Device Comparison                  | 4 | 10 Application and Implementation                     |      |

| 7 Pin Configuration and Functions    | 5 | 10.1 Application Information                          |      |

| 8 Specifications                     |   | 10.2 Typical Applications                             |      |

| 8.1 Absolute Maximum Ratings         |   | 10.3 Power Supply Recommendations                     |      |

| 8.2 ESD Ratings                      |   | 10.4 Layout                                           |      |

| 8.3 Recommended Operating Conditions |   | 11 Device and Documentation Support                   |      |

| 8.4 Thermal Information              | 6 | 11.1 Documentation Support                            |      |

| 8.5 Electrical Characteristics       |   | 11.2 Receiving Notification of Documentation Updates. |      |

| 8.6 1-Wire Interface Timing          |   | 11.3 Support Resources                                |      |

| 8.7 EEPROM Characteristics           | 8 | 11.4 Trademarks                                       |      |

| 8.8 Timing Diagrams                  |   | 11.5 Electrostatic Discharge Caution                  |      |

| 8.9 Typical Characteristics          |   | 11.6 Glossary                                         |      |

| 9 Detailed Description               |   | 12 Mechanical, Packaging, and Orderable               |      |

| 9.1 Overview                         |   | Information                                           | . 61 |

|                                      |   |                                                       |      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision B (December 2022) to Revision C (May 2023)                                       | Page |

|---|-------------------------------------------------------------------------------------------------------|------|

| • | Removed preview note from WSON package option                                                         | 1    |

| • | Added device comparison table                                                                         |      |

| • | Changed maximum operating temperature range for standard speed mode in footnote 2                     |      |

| • | Changed NGR package maximum accuracy for +10°C to +45°C from ±0.3°C to ±0.2°C and full range          |      |

|   | from ±1.0°C to ±0.4°C                                                                                 |      |

| • | Changed V <sub>IL</sub> of IO from 0.2×V <sub>S</sub> to 0.3×V <sub>S</sub>                           | 6    |

| • | Changed V <sub>IH</sub> of IO from 0.8×V <sub>S</sub> to 0.7×V <sub>S</sub>                           | 6    |

| • | Added standby current specification for continuous conversion mode                                    | 6    |

| • | Changed t <sub>SLOT</sub> minimum in standard mode from 60 µs to t <sub>WR0L</sub> + t <sub>RC</sub>  |      |

| • | Removed t <sub>SLOT</sub> maximum in standard mode                                                    |      |

| • | Changed t <sub>SLOT</sub> minimum in overdrive mode from 11 µs to t <sub>WR0L</sub> + t <sub>RC</sub> |      |

| • | Changed t <sub>REC</sub> in overdrive speed from 10 µs to 2 µs                                        |      |

| • | Changed t <sub>RL</sub> minimum from 2 µs to 2.5 µs                                                   | 8    |

| • | Changed t <sub>READIDLE</sub> from 400 µs to 560 µs                                                   |      |

| • | Changed I <sub>DD PROG</sub> from 214 µA to 230 µA                                                    |      |

| • | Added continuous conversion mode for V <sub>DD</sub> powered mode                                     |      |

| _ | hanges from Povision A (Sentember 2022) to Povision B (December 2022)                                 | Paga |

| _ | hanges from Revision A (September 2022) to Revision B (December 2022)                                 |      |

| • | Changed the DGK (VSSOP) package status from Advanced Information to Production Data                   |      |

| • | Added Functional Safety information to the <i>Features</i> section                                    |      |

| • | Changed DGK package maximum accuracy for full range from ±1.0°C to ±0.5°C                             |      |

| • | Changed t <sub>REC</sub> in overdrive speed from 2 µs to 10 µs                                        | 8    |

| • | Added minimum EEPROM Endurance specification for 125 °C                                               |      |

| • | Removed GPIO read and CRC byte from the GPIO WRITE section                                            | 37   |

**Page**

Added WSON package option.....1

Changes from Revision \* (February 2022) to Revision A (September 2022)

# www.ti.com

| • | Added pinout for WSON package                                                              | <mark>5</mark> |

|---|--------------------------------------------------------------------------------------------|----------------|

| • | Updated operating ambient temperature as –55°C to 150 °C                                   |                |

| • | Added long-term stability and drift specification                                          |                |

| • | Added temperature cycling and hysteresis specification                                     |                |

| • | Added response time specification                                                          |                |

| • | Changed standby current as 1.6 µA                                                          |                |

| • | Changed power-on reset threshold on rising supply from typical 1.25 V to minimum of 1.5 V  |                |

| • | Changed power-on reset threshold on falling supply from typical 1.15 V to maximum of 1.3 V |                |

| • | Added typical Endurance spec for EEPROM                                                    |                |

| • | Added the Flexible Device Address section                                                  |                |

| • | Added section on standard and overdrive bus speeds                                         |                |

| • | Added FLEXADDR address command                                                             |                |

| • | Added description of FLEXADDR address command                                              |                |

| • | Updated reset value for TEMP_RESULT_L and TEMP_RESULT_H registers                          |                |

| • | Added DATA_READY flag in STATUS_REG                                                        |                |

| • | Added FLEX_ADDR_MODE bits in CONFIG_REG2 register                                          |                |

| • | Updated STACKMODE_ADDR as SHORT_ADDR register                                              |                |

|   |                                                                                            |                |

# 5 Description (cont.)

The 2Kb EEPROM on the TMP1826 allows the host to store application data in increments of 64 bits. With user programmable 256-bit page size write protection to avoid accidental overwrite, the EEPROM can be used as non-volatile, read-only memory. The four digital I/O pins are configurable for general purpose functions, temperature alert, or provide host to identify the position of the device on a shared bus.

# **6 Device Comparison**

**Table 6-1. Device Comparison**

| FEATURE                     | TMP1826                      | TMP1827                     | TMP1827N <sup>(1)</sup>     |

|-----------------------------|------------------------------|-----------------------------|-----------------------------|

| Best Accuracy               | 0.2°C                        | 0.2°C                       | 0.9°C                       |

| Temperature Range           | −55°C to +150°C              | –55°C to +150°C             | –55°C to +150°C             |

| Memory Size                 | 2Kb                          | 2Kb                         | 2Kb                         |

| Memory Write protection     | Yes                          | Yes                         | Yes                         |

| Authenticated Memory Write  | -                            | Yes                         | Yes                         |

| Authentication type         | -                            | SHA-256-HMAC                | SHA-256-HMAC                |

| Bus speeds                  | Standard and Overdrive       | Standard and Overdrive      | Standard and Overdrive      |

| Drop in replacement package | NGR (2.5 mm × 2.5 mm, WSON)  | NGR (2.5 mm × 2.5 mm, WSON) | NGR (2.5 mm × 2.5 mm, WSON) |

| Alternate package           | DGK (3.0 mm × 4.9 mm, VSSOP) | -                           | -                           |

<sup>(1)</sup> TMP1827N is an orderable option for the TMP1827. See the orderable addendum at the end of the data sheet.

Product Folder Links: TMP1826

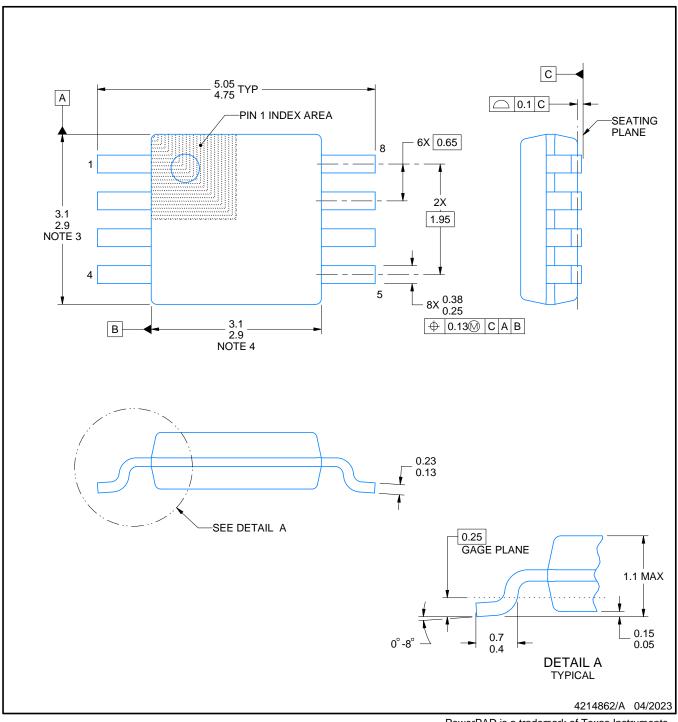

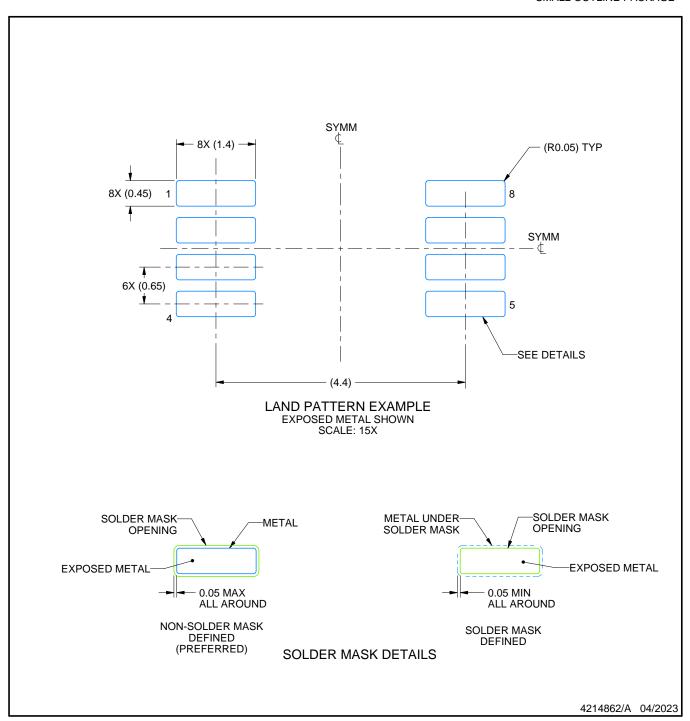

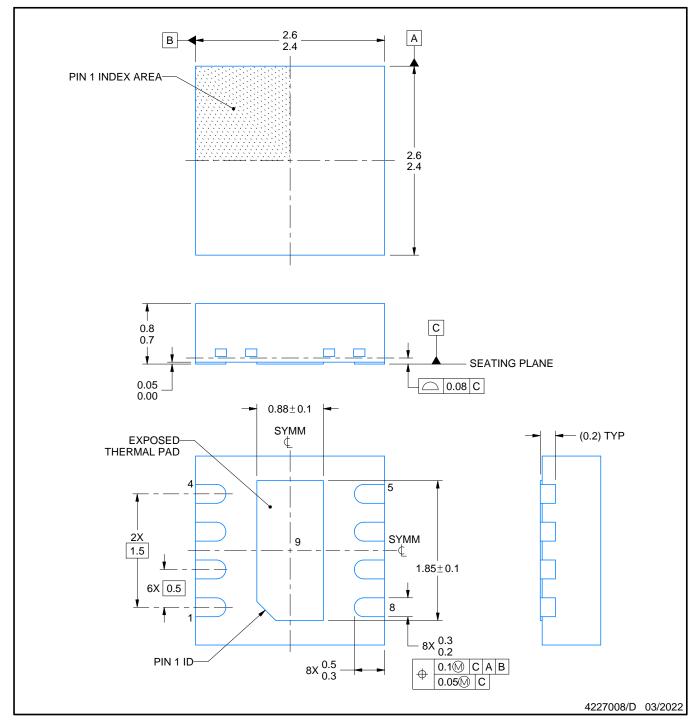

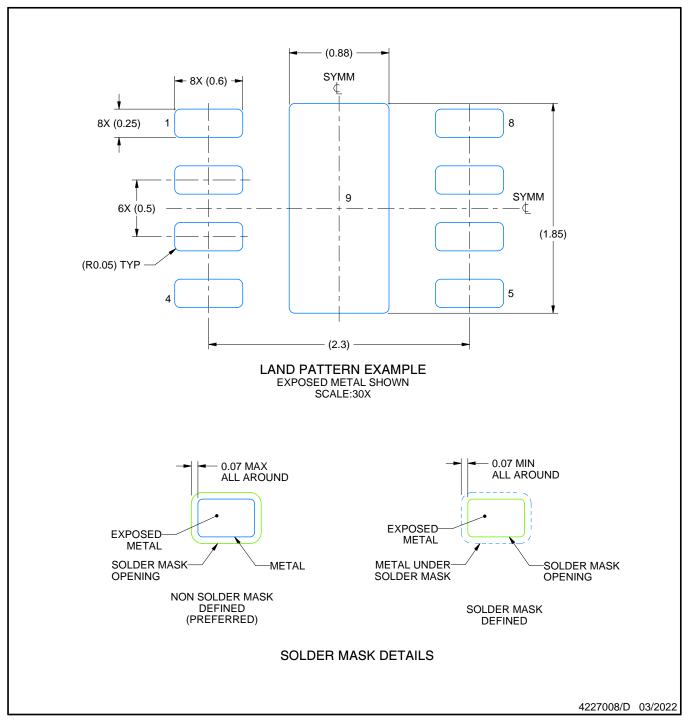

# 7 Pin Configuration and Functions

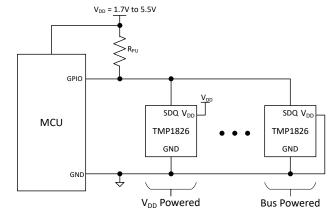

Figure 7-1. NGR 8-Pin WSON Top View

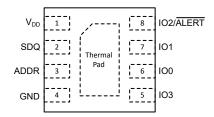

Figure 7-2. DGK 8-Pin VSSOP Top View

Table 7-1. Pin Functions

|                 | PIN  | PIN   |     | DECORPORTION                                                                                                                  |  |

|-----------------|------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | WSON | VSSOP | I/O | DESCRIPTION                                                                                                                   |  |

| ADDR            | 3    | 3     | I   | Resistor address select. If unused, TI recommends to connect pin to ground                                                    |  |

| GND             | 4    | 4     | _   | Ground                                                                                                                        |  |

| 100             | 6    | 6     | I/O | General-purpose digital open-drain IO. If unused, TI recommends to connect pin to ground                                      |  |

| IO1             | 7    | 7     | I/O | General-purpose digital open-drain IO. If unused, TI recommends to connect pin to ground                                      |  |

| IO2/ALERT       | 8    | 8     | I/O | General-purpose digital open-drain IO or configurable as temperature alert. If unused, TI recommends to connect pin to ground |  |

| IO3             | 5    | 5     | I/O | General-purpose digital open-drain IO. If unused, TI recommends to connect pin to ground                                      |  |

| SDQ             | 2    | 2     | I/O | Serial bidirectional data. In bus power mode, the pin is used to power the internal capacitor                                 |  |

| V <sub>DD</sub> | 1    | 1     | I   | Supply voltage in $V_{\text{DD}}$ powered mode. In bus powered mode, must be connected to ground                              |  |

# 8 Specifications

# 8.1 Absolute Maximum Ratings

Over free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                               |                                     | MIN  | MAX                   | UNIT |

|-----------------------------------------------|-------------------------------------|------|-----------------------|------|

| Supply voltage                                | $V_{DD}$                            |      | 6.5                   | V    |

| I/O valtage                                   | SDQ, Bus powered mode               | -0.3 | 6.5                   | V    |

| I/O voltage                                   | SDQ, Supply powered mode            | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| I/O voltage                                   | 100, 101, 102, 103                  | -0.3 | 6.5                   | V    |

| Input voltage                                 | ADDR                                | -0.3 | 1.65                  | V    |

| perating junction temperature, T <sub>J</sub> |                                     | -55  | 155                   | °C   |

| Storage temperature                           | orage temperature, T <sub>stg</sub> |      | 155                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions.

If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 8.2 ESD Ratings

|                                            |                                                                       |                                                                   |          | VALUE | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|----------|-------|------|

|                                            |                                                                       | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | All pins | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | All pins                                                          | ±500     | V     |      |

|                                            | 3                                                                     | IEC 61000-4-2 Contact Discharge                                   | SDQ pin  | ±8000 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 8.3 Recommended Operating Conditions

|                  |                                                                                   | MIN | NOM MAX               | UNIT |

|------------------|-----------------------------------------------------------------------------------|-----|-----------------------|------|

| $V_{DD}$         | Supply voltage V <sub>DD</sub> powered mode                                       | 1.7 | 5.5                   | V    |

| V <sub>PUR</sub> | Supply voltage on SDQ in bus powered mode (V <sub>DD</sub> = GND)                 | 1.7 | 5.5                   | V    |

| V                | All IO pins in V <sub>DD</sub> powered mode (except SDQ and ADDR <sup>(1)</sup> ) | 0   | 5.5                   | V    |

| V <sub>I/O</sub> | SDQ pin in V <sub>DD</sub> powered mode                                           | 0   | V <sub>DD</sub> + 0.3 | V    |

| T <sub>A</sub>   | Operating ambient temperature <sup>(2)</sup>                                      | -55 | 150                   | °C   |

- (1) If ADDR pin is not used, it is recommended to be connected to GND

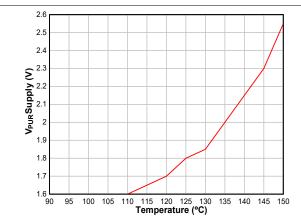

- (2) In bus powered mode, overdrive speed supports the max operating temperature up to 150°C, while standard speed supports up to 105°C for full V<sub>PUR</sub> range and up to 125°C for V<sub>PUR</sub> > 2.5V (See Figure 8-18)

# 8.4 Thermal Information

|                        |                                              | TMP        |             |      |

|------------------------|----------------------------------------------|------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | NGR (WSON) | DGK (VSSOP) | UNIT |

|                        |                                              | 8 PINS     | 8 PINS      |      |

| R <sub>θJA</sub>       | Junction-to-ambient thermal resistance       | 66.1       | 158.2       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 55.7       | 52.6        | °C/W |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 20.2       | NA          | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 26.3       | 79.0        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 1.0        | 4.9         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 26.1       | 77.5        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 8.5 Electrical Characteristics

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                     | PARAMETER                    | TEST CONDITIONS                                                                                       | MIN | TYP    | MAX   | UNIT |

|---------------------|------------------------------|-------------------------------------------------------------------------------------------------------|-----|--------|-------|------|

| TEMPERA             | ATURE SENSOR                 |                                                                                                       |     |        |       |      |

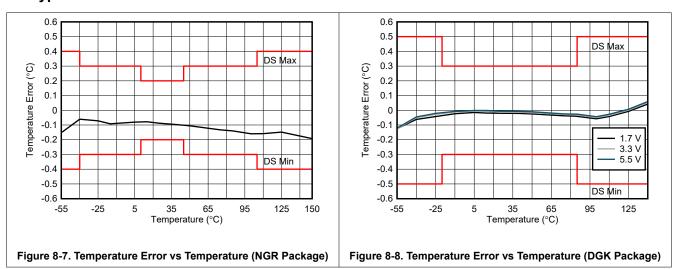

| T <sub>ERR</sub>    |                              | 10°C to 45°C                                                                                          |     | ±0.1   | ±0.2  |      |

|                     | Temperature accuracy (NGR)   | -40°C to 105°C                                                                                        |     |        | ±0.3  |      |

|                     |                              | –55°C to 150°C                                                                                        |     |        | ±0.4  |      |

|                     | Temperature accuracy (DGK)   | –20°C to 85°C                                                                                         |     | ±0.1   | ±0.3  | °C   |

|                     |                              | –55°C to 150°C                                                                                        |     |        | ±0.5  | C    |

| PSR                 | DC power supply sensitivity  |                                                                                                       |     |        | ±0.03 | °C/V |

| _                   | Temperature resolution (High | Including sign bit                                                                                    |     | 16     |       | Bits |

| T <sub>RES</sub>    | Precision Format)            | LSB                                                                                                   |     | 7.8125 |       | m°C  |

| T <sub>REPEAT</sub> | Repeatability <sup>(1)</sup> | Averaging enabled, Conversion Time = 5.5 ms,<br>16-bit mode,<br>1-Hz conversion rate, 300 acquisition |     | ±2     |       | LSB  |

Product Folder Links: TMP1826

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                        | PARAMETER                                                      | TEST CO                                                                         | NDITIONS                        | MIN                  | TYP                                                                                                                      | MAX                  | UNIT   |

|------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|--------|

| T <sub>LTD</sub>       | Long-term stability and drift                                  | 1000 hours at 150°C <sup>(2)</sup>                                              |                                 |                      | 0.0625                                                                                                                   |                      | °C     |

| T <sub>HYST</sub>      | Temperature cycling and hysteresis                             | $T_{START} = -40$ °C<br>$T_{FINISH} = 150$ °C<br>$T_{TEST} = 25$ °C<br>3 cycles |                                 |                      | 4                                                                                                                        |                      | LSB    |

|                        | Response time (Stirred                                         | Single layer Flex PCB                                                           | т = 63 %                        |                      | 0.77                                                                                                                     |                      | s      |

| t <sub>RESP_L</sub>    | Liquid)<br>NGR Package                                         | 2-layer 62-mil Rigid<br>PCB                                                     | 25°C to 75°C                    |                      | 1.91                                                                                                                     |                      | s      |

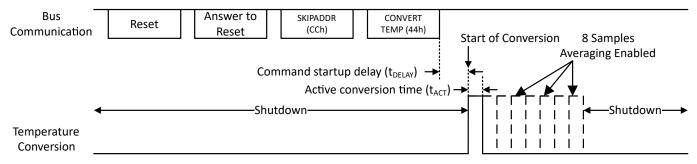

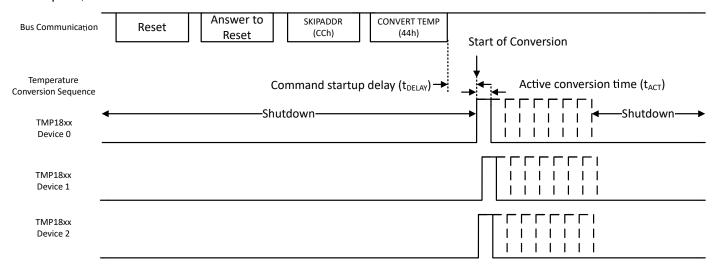

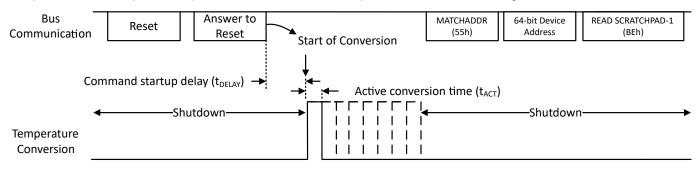

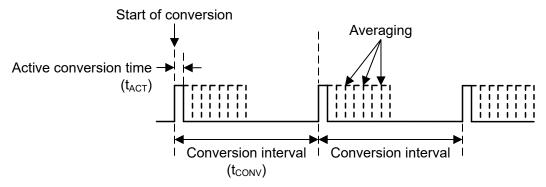

| t                      | Active Conversion time (No                                     | CONV_TIME_SEL = 0                                                               | (Figure 9-12)                   | 2.54                 | 3                                                                                                                        | 3.37                 | ms     |

| t <sub>ACT</sub>       | Averaging)                                                     | CONV_TIME_SEL = 1                                                               | (Figure 9-12)                   | 4.69                 | 5.5                                                                                                                      | 6.12                 | ms     |

| t <sub>DELAY</sub>     | Start-up delay for temperature conversion                      | )                                                                               |                                 | 100                  |                                                                                                                          | 300                  | μs     |

| SDQ DIGIT              | TAL INPUT/OUTPUT                                               |                                                                                 |                                 |                      |                                                                                                                          |                      |        |

| C <sub>IN</sub>        | SDQ pin capacitance                                            |                                                                                 |                                 |                      | 40                                                                                                                       |                      | pF     |

| V <sub>IL</sub>        | Input logic low level <sup>(3)</sup>                           |                                                                                 |                                 | -0.3                 |                                                                                                                          | 0.2 × V <sub>S</sub> | V      |

| $V_{IH}$               | Input logic high level <sup>(3)</sup>                          |                                                                                 |                                 | 0.8 × V <sub>S</sub> |                                                                                                                          | $V_{S} + 0.3$        | V      |

| $V_{HYST}$             | Hysteresis                                                     |                                                                                 |                                 |                      | 0.3                                                                                                                      |                      | V      |

| $V_{OL}$               | Output low level                                               | $I_{OL} = -4 \text{ mA}$                                                        |                                 |                      |                                                                                                                          | 0.4                  | V      |

| IO CHARA               | CTERISTICS                                                     |                                                                                 |                                 |                      |                                                                                                                          |                      |        |

| C <sub>IN</sub>        | Input capacitance                                              |                                                                                 |                                 |                      | 10                                                                                                                       |                      | pF     |

| V <sub>IL</sub>        | Input logic low level <sup>(3)</sup>                           |                                                                                 |                                 | -0.3                 |                                                                                                                          | 0.3 × V <sub>S</sub> | V      |

| $V_{IH}$               | Input logic high level <sup>(3)</sup>                          |                                                                                 |                                 | 0.7 × V <sub>S</sub> |                                                                                                                          | $V_{S} + 0.3$        | V      |

| I <sub>IN</sub>        | Input leakage current                                          |                                                                                 |                                 |                      | 0                                                                                                                        | ±0.12                | μA     |

| $V_{OL}$               | Output low level                                               | $I_{OL} = -3 \text{ mA}$                                                        |                                 |                      |                                                                                                                          | 0.4                  | V      |

| RESISTOR               | ADDRESS DECODER CHAR                                           | ACTERISTICS                                                                     |                                 |                      |                                                                                                                          |                      |        |

| $C_{LOAD}$             | Load capacitance as seen on ADDR pin (includes PCB parasitics) |                                                                                 |                                 |                      |                                                                                                                          | 100                  | pF     |

|                        | R <sub>ADDR</sub> resistor range                               |                                                                                 |                                 | 6.49                 |                                                                                                                          | 54.9                 | kΩ     |

|                        | R <sub>ADDR</sub> resistor tolerance                           | T <sub>A</sub> = 25°C                                                           |                                 | -1.0                 |                                                                                                                          | 1.0                  | %      |

|                        | R <sub>ADDR</sub> resistor temperature coefficient             |                                                                                 |                                 | -100                 |                                                                                                                          | 100                  | ppm/°C |

|                        | R <sub>ADDR</sub> resistor lifetime drift                      |                                                                                 |                                 | -0.2                 |                                                                                                                          | 0.2                  | %      |

| t <sub>RESDET</sub>    | Resistor decoding time                                         |                                                                                 |                                 |                      | 2.8                                                                                                                      |                      | ms     |

| POWER S                | UPPLY                                                          |                                                                                 |                                 |                      |                                                                                                                          |                      |        |

| $I_{PU}$               | Pullup current <sup>(5)</sup>                                  | Bus powered mode, seria                                                         | al bus idle                     | 300                  |                                                                                                                          |                      | μA     |

| I <sub>DD_ACTIVE</sub> | Supply current during temperature conversion                   | Temperature Conversion                                                          | , serial bus idle               |                      | 94                                                                                                                       | 154                  | μΑ     |

| I <sub>DD_SB</sub>     | Standby current <sup>(4)</sup>                                 | V <sub>DD</sub> powered, serial bus inactive, continuous                        | T <sub>A</sub> = -55°C to 85°C  |                      | 1.6                                                                                                                      | 4.2                  | μA     |

|                        |                                                                | conversion mode                                                                 | T <sub>A</sub> = -55°C to 150°C |                      |                                                                                                                          | 24                   | -      |

| I <sub>DD_SD</sub>     | Shutdown current                                               | Serial bus inactive, one                                                        | T <sub>A</sub> = -55°C to 85°C  |                      | 1.3                                                                                                                      | 3.3                  | μA     |

| 55_65                  |                                                                | shot conversion mode                                                            | T <sub>A</sub> = -55°C to 150°C |                      | 10 -0.3 0.3 × V <sub>S</sub> v <sub>S</sub> + 0.3 0 ±0.12 0.4  100 3.49 -1.0 100 100 100 -0.2 2.8  300 94 154 1.6 4.2 24 | 1                    |        |

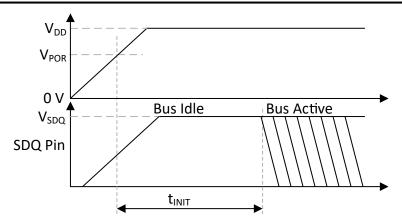

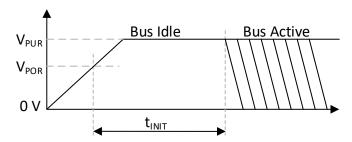

| $V_{POR}$              | Power-on reset threshold voltage                               | Supply rising (Figure 8-4                                                       | , Figure 8-5)                   | 1.5                  |                                                                                                                          |                      | V      |

|                        | Brownout detect                                                | Supply falling                                                                  |                                 |                      |                                                                                                                          | 1.3                  | V      |

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                 |     | PARAMETER               | TEST CONDITIONS                                                          | MIN | TYP | MAX | UNIT |

|-----------------|-----|-------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>IN</sub> | NIT | POR Initialization Time | Time required by device to reset after power up (Figure 8-4, Figure 8-5) |     |     | 2.0 | ms   |

- (1) Repeatability is the ability to reproduce a reading when the measured temperature is applied consecutively, under the same conditions. See Figure 8-12

- (2) Long term stability is determined using accelerated operational life testing at a junction temperature of 150°C.

- (3) In bus powered mode  $V_S = V_{PUR}$ . In supply powered mode  $V_S = V_{DD}$ .

- (4) Quiescent current between conversions.

- (5) The pullup current parameter is required to size the bus pullup resistor (See Section 9.3.3) for active temperature conversion or EEPROM read and program operations.

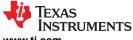

# 8.6 1-Wire Interface Timing

Over free-air temperature range and  $V_{DD}$  = 1.70 V to 5.5 V (unless otherwise noted)

|                    |                                                                             | STANDARD                            | MODE                             | OVERDRIVE                           | MODE                             | LINUT |

|--------------------|-----------------------------------------------------------------------------|-------------------------------------|----------------------------------|-------------------------------------|----------------------------------|-------|

|                    |                                                                             | MIN MAX                             |                                  | MIN                                 | MAX                              | UNIT  |

| BUS RESET          | AND BIT SLOT TIMING                                                         |                                     |                                  |                                     |                                  |       |

| t <sub>RSTL</sub>  | Host to device bus reset pulse width (Figure 8-1)                           | 480                                 | 560                              | 48                                  | 80                               | μs    |

| t <sub>RSTH</sub>  | Device to host response time (Figure 8-1) <sup>(2)</sup>                    | 480                                 |                                  | 48                                  |                                  | μs    |

| t <sub>PDH</sub>   | Device turnaround time for bus reset response (Figure 8-1)                  | 15                                  | 60                               | 2                                   | 8                                | μs    |

| t <sub>PDL</sub>   | Device to host response pulse width (Figure 8-1)                            | 60                                  | 240                              | 8                                   | 24                               | μs    |

| t <sub>SLOT</sub>  | Bit slot time (Figure 8-2, Figure 8-3) <sup>(5)</sup>                       | t <sub>WR0L</sub> + t <sub>RC</sub> |                                  | t <sub>WR0L</sub> + t <sub>RC</sub> |                                  | μs    |

| t <sub>REC</sub>   | Recovery time (Figure 8-2, Figure 8-3)                                      | 2                                   |                                  | 2                                   |                                  | μs    |

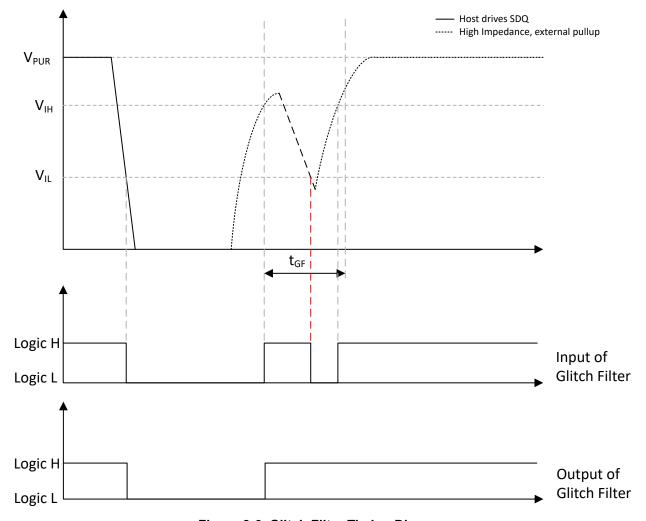

| t <sub>GF</sub>    | Glitch filter width (Figure 8-6) <sup>(3)</sup>                             | 0.48                                |                                  | 0.025                               |                                  | μs    |

| t <sub>F</sub>     | Fall time                                                                   |                                     | 100                              |                                     | 100                              | ns    |

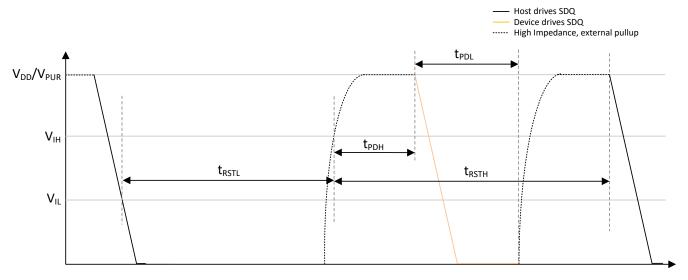

| BIT WRITE          | TIMING                                                                      |                                     |                                  |                                     |                                  |       |

| t <sub>WR0L</sub>  | Host write 0 width (Figure 8-2)                                             | 60                                  | 120                              | 9                                   | 10                               | μs    |

| t <sub>WR1L</sub>  | Host write 1 width (Figure 8-2)                                             | 2                                   | 15                               | 1                                   | 2                                | μs    |

| t <sub>RDV</sub>   | Device read data valid time (Figure 8-2)                                    | 15                                  |                                  | 2                                   |                                  | μs    |

| t <sub>DSW</sub>   | Device read data window (Figure 8-2)                                        | 15                                  | 45                               | 2                                   | 7                                | μs    |

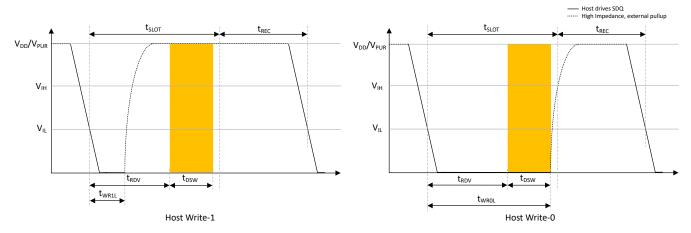

| BIT READ T         | IMING                                                                       |                                     |                                  |                                     |                                  |       |

| t <sub>RL</sub>    | Host drive read bit slot time (Figure 8-3) <sup>(4)</sup>                   | 2.5                                 | 5                                | 2                                   | 3                                | μs    |

| t <sub>RWAIT</sub> | Host wait time before read data sampling window (Figure 8-3) <sup>(5)</sup> |                                     | t <sub>RL</sub> +t <sub>RC</sub> |                                     | t <sub>RL</sub> +t <sub>RC</sub> | μs    |

| t <sub>MSW</sub>   | Host read data sampling window (Figure 8-3) <sup>(5)</sup>                  | t <sub>RL</sub> +t <sub>RC</sub>    | 30                               | t <sub>RL</sub> +t <sub>RC</sub>    | 3                                | μs    |

- (1) In bus powered mode, extending the  $t_{\mbox{\scriptsize RSTL}}$  above 600  $\mu \mbox{\scriptsize s}$  may cause the device to power on reset

- (2) The t<sub>RSTH</sub> is the maximum time the host must wait to receive a response from the furthest device, taking into account the propagation delay and recovery time for all the devices.

- (3) The glitch filter timing applies only on the rising edge of the SDQ signal

- (4) t<sub>RL</sub> minimum time includes the glitch filter timing

- (5) The t<sub>RC</sub> time is defined as the time taken for the bus voltage to rise from 0V to minimum V<sub>IH</sub> of the device. This is a function of the bus pullup resistor, devices and parasitic capacitance of the trace or cable. The parameters must be characterized for the application.

#### 8.7 EEPROM Characteristics

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                       |                                                      | MIN | TYP  | MAX | UNIT |

|-----------------------|------------------------------------------------------|-----|------|-----|------|

|                       | Programming time for 8-byte data word in user EEPROM |     | 13.2 | 21  | ms   |

| TPROG                 | Programming time for register copy to EEPROM         |     | 26.4 | 42  | ms   |

| t <sub>READIDLE</sub> | Idle bus time for EEPROM 8-byte data read            |     |      | 560 | μs   |

Product Folder Links: TMP1826

www.ti.com

Over free-air temperature range and  $V_{DD}$  = 1.7 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                      |                           | MIN   | TYP    | MAX | UNIT   |

|----------------------|---------------------------|-------|--------|-----|--------|

| I <sub>DD_PROG</sub> | Programming current       |       | 178    | 230 | μΑ     |

| Data Retention       | at T <sub>A</sub> = 125°C | 25    |        |     | years  |

| Data Retention       | at T <sub>A</sub> = 150°C | 10    |        |     | years  |

| Drogram Endurance    | at T <sub>A</sub> = 125°C | 20000 | 200000 |     | cycles |

| Program Endurance    | at T <sub>A</sub> = 150°C | 1000  | 10000  |     | cycles |

# 8.8 Timing Diagrams

Figure 8-1. Bus Reset Timing Diagram

Figure 8-2. Write Timing Diagram

Figure 8-3. Read Timing Diagram

Figure 8-4. V<sub>DD</sub> Powered Initialization Timing Diagram

Figure 8-5. Bus Powered Initialization Timing Diagram

Figure 8-6. Glitch Filter Timing Diagram

# 8.9 Typical Characteristics

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

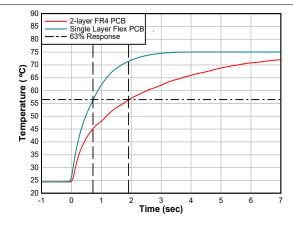

# 8.9 Typical Characteristics (continued)

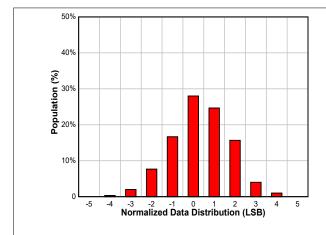

# 8.9 Typical Characteristics (continued)

Averaging Off in 16-Bit Format

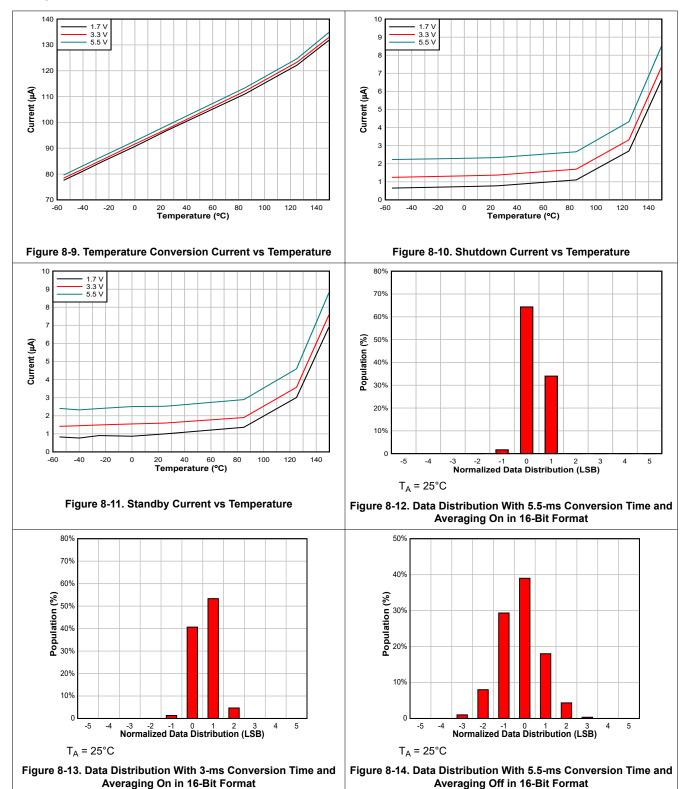

T<sub>A</sub> = 25°C, 5.5-ms conversion time, Averaging On, 16-bit

Figure 8-16. Data Distribution for Power Mode and Bus Speed Figure 8-15. Data Distribution With 3-ms Conversion Time and

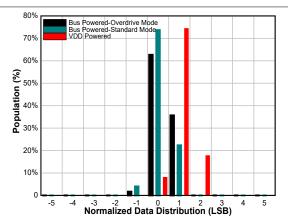

Figure 8-17. Thermal Response Time (NGR)

Figure 8-18. V<sub>PUR</sub> Typical Standard Speed Mode Supply Voltage vs Temperature

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 9 Detailed Description

### 9.1 Overview

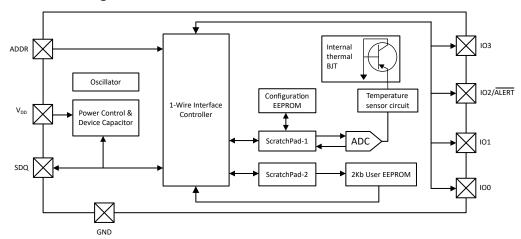

The TMP1826 is a digital output temperature sensor designed for thermal-management and thermal-protection applications. The TMP1826 is a 1-Wire device which can operate in either supply powered or bus powered (parasitic powered) mode. The device features a 2Kb EEPROM. Figure 9-1 shows the TMP1826 block diagram.

# 9.2 Functional Block Diagram

Figure 9-1. Functional Block Diagram

# 9.3 Feature Description

## 9.3.1 Power Up

The device operates in both supply powered and bus powered mode. In both modes, when the supply voltage reaches within the operating range, the device requires  $t_{\text{INIT}}$  to initialize itself. After  $t_{\text{INIT}}$ , the host MCU can begin accessing the device.

During initialization, the device may not respond to any bus activity. When initialization is complete, the device shall wait for the bus reset from the host. During the initialization for the device, the following events take place:

- The EEPROM content for short address, temperature alert low, temperature alert high and temperature offset registers are restored.

- The EEPROM for the IO configuration register is read and contents of the IO configuration register is restored.

- The EEPROM content for device configuration-1 and device configuration-2 registers are restored to the respective registers.

- If the ARB\_MODE bits is restored as '10b' or '11b', then the device will respond to the SEARCHADDR in arbitration mode.

- If OD\_EN bit is set to '1b', then the device shall communicate in overdrive speed, unless the first bus reset pulse from the host is sent in standard speed.

- The user memory protection bits are restored and appropriate protection to the user EEPROM block applied.

#### 9.3.2 Power Mode Switch

The device is designed to operate in supply powered or bus powered mode. The dual mode implementation provides a unique method of redundancy that, even in cases where the power supply pin  $V_{DD}$  becomes 0V, the device can draw power from data pin, as long as the pullup resistor value used is as per the specification limit.

When the device switches from supply powered to bus powered mode, the device shall operate with the same settings until the internal capacitor is able to provide the current draw required by the device for communication and the external pullup resistor can keep SDQ voltage above 1.7V during ADC and EEPROM programming. If the internal voltage on the capacitor drops below the brown-out threshold, the device shall switch itself off and enter bus powered mode of communication on subsequent power up. When the device completes the power-up

initialization sequence, as described earlier, the device shall respond to first bus communication starting with the bus reset sequence.

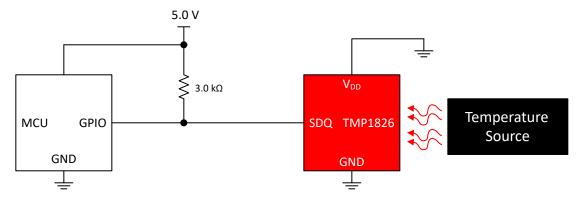

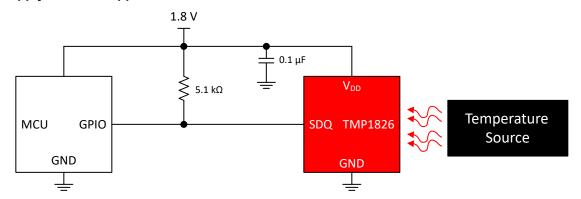

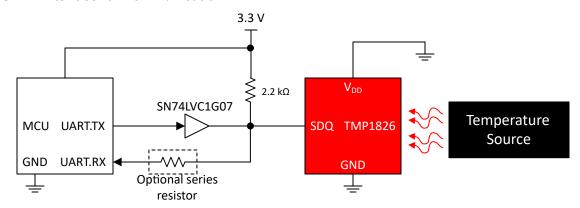

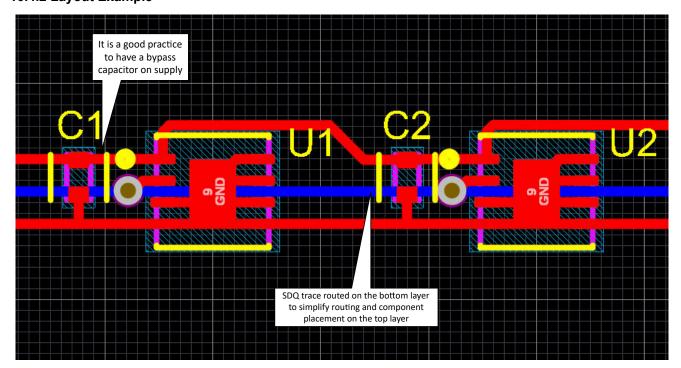

#### 9.3.3 Bus Pullup Resistor

The bus pullup resistance value selected is important for communication as per the speed mode and ensuring that minimal possible energy is consumed in the application. If the resistor value is too small, the design may violate the  $V_{OL}$  limits on the SDQ pin.

Consider the total SDQ pins and bus capacitance along with the bus leakage current when selecting the pullup resistor. The pullup resistance value selected must also ensure that the signal level reaches  $V_{IH}$  as per the timing requirements for standard and overdrive mode.

In bus powered mode of operation, the device charges the internal capacitor through the SDQ pin and the pullup resistor. This charge on the capacitor is used during bus communication, when the SDQ pin low. For other high current functions like thermal conversion and EEPROM access, the bus is held idle to ensure that the device can draw current through the pullup resistor. The SDQ pin voltage during the high current operation must be maintained to ensure sufficient operating margins. For  $V_{PUR} \le 2.0 \text{ V}$ , use Equation 1. For  $V_{PUR} > 2.0 \text{ V}$ , use Equation 2 to calculate the pullup resistor value.

$$\frac{\left(V_{PUR} - V_{OL(MAX)}\right)}{4 \times 10^{-3}} < R_{PUR} < \frac{\left(V_{PUR} - 1.6\right)}{I_{PU(MIN)}} \tag{1}$$

$$\frac{\left(V_{PUR} - V_{OL(MAX)}\right)}{4 \times 10^{-3}} < R_{PUR} < \frac{\left(V_{PUR} - V_{IH(MIN)}\right)}{I_{PU(MIN)}}$$

(2)

When the device is used in  $V_{DD}$  or supply powered mode, a larger pullup resistor value may be used, as the SDQ pin is used only for communication. The user must ensure that the pullup resistor value selected must be able to support the timing for the required bus speed of operation.

For low current consumption devices like the TMP1826, selecting the correct pullup resistor value allows the application to avoid low impedance current path components for bus powered mode of operation while maintaining communication speeds and device parameters as per its electrical specification. For multiple devices on the bus, a low impedance current path is recommended.

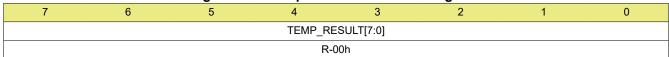

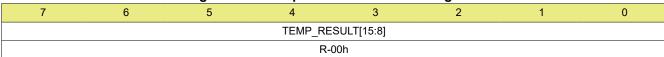

# 9.3.4 Temperature Results

The conversion is initiated by the host MCU by sending the temperature conversion command if the automatic conversion is disabled, immediately after the presence detect is completed when the automatic conversion is enabled, or in continuous conversion mode if the device is V<sub>DD</sub> powered. At the end of every conversion, the device updates the temperature registers temperature result and the status register bits. Figure 9-2 shows that the device supports a high precision and legacy format, which can be configured through the TEMP\_FMT bit in the device configuration-1 register. The default setting for the temperature result is legacy format for software compatibility.

|          |                | Ten            | nperature Res  | sult MSB Regi  | ster           |                |                |                |                 | Ter             | mperature Re    | sult LSB Regi   | ster            |                 |                 |

|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| High Pre | cision Fo      | rmat           |                |                |                |                |                |                |                 |                 |                 |                 |                 |                 |                 |

| S        | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> |

| Legacy F | ormat          |                |                |                |                |                |                |                |                 |                 |                 |                 |                 |                 |                 |

| S        | S              | S              | S              | S              | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup>  | 2 <sup>1</sup>  | 2 <sup>0</sup>  | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> |

Figure 9-2. Temperature Format

If the format selected is the high precision 16-bit format, the data in the result registers is stored in two's complement form and has a resolution of 7.8125m°C and a range of ±256°C. If the format selected is the legacy 12-bit format, the data in the result register is stored in sign extended form and has a resolution of 62.5m°C and a range of ±128°C. The temperature register reads as 0°C before the first conversion. Table 9-1 and Table

9-2 show examples of possible binary data that can be read from the temperature result registers and the corresponding hexadecimal and temperature equivalents for both formats.

Table 9-1. Precision (16-Bit) Temperature Data Format

| TEMPERATURE | DIGITAL OUTPUT (PRECISION FORMAT) |             |  |  |  |

|-------------|-----------------------------------|-------------|--|--|--|

| (°C)        | BINARY                            | HEXADECIMAL |  |  |  |

| 150         | 0100 1011 0000 0000               | 4B00        |  |  |  |

| 127         | 0011 1111 1000 0000               | 3F80        |  |  |  |

| 100         | 0011 0010 0000 0000               | 3200        |  |  |  |

| 25          | 0000 1100 1000 0000               | 0C80        |  |  |  |

| 1           | 0000 0000 1000 0000               | 0080        |  |  |  |

| 0.125       | 0000 0000 0001 0000               | 0010        |  |  |  |

| 0.03125     | 0000 0000 0000 0100               | 0004        |  |  |  |

| 0.0078125   | 0000 0000 0000 0001               | 0001        |  |  |  |

| 0           | 0000 0000 0000 0000               | 0000        |  |  |  |

| -0.0078125  | 1111 1111 1111                    | FFFF        |  |  |  |

| -0.03125    | 1111 1111 1110                    | FFFC        |  |  |  |

| -0.125      | 1111 1111 1111 0000               | FFF0        |  |  |  |

| -1          | 1111 1111 1000 0000               | FF80        |  |  |  |

| -25         | 1111 0011 1000 0000               | F380        |  |  |  |

| -40         | 1110 1100 0000 0000               | FC00        |  |  |  |

| <b>–</b> 55 | 1110 0100 1000 0000               | F480        |  |  |  |

Table 9-2. Legacy (12-Bit) Temperature Data Format

| TEMPERATURE | DIGITAL OUTPUT      |             |  |  |  |

|-------------|---------------------|-------------|--|--|--|

| (°C)        | BINARY              | HEXADECIMAL |  |  |  |

| 140         | 0000 0111 1111 1111 | 07FF        |  |  |  |

| 128         | 0000 0111 1111 1111 | 07FF        |  |  |  |

| 127.9375    | 0000 0111 1111 1111 | 07FF        |  |  |  |

| 100         | 0000 0110 0100 0000 | 0640        |  |  |  |

| 25          | 0000 0001 1001 0000 | 0190        |  |  |  |

| 1           | 0000 0000 0001 0000 | 0010        |  |  |  |

| 0.125       | 0000 0000 0000 0010 | 0002        |  |  |  |

| 0           | 0000 0000 0000 0000 | 0000        |  |  |  |

| -0.125      | 1111 1111 1111 1110 | FFFE        |  |  |  |

| -1          | 1111 1111 1111 0000 | FFF0        |  |  |  |

| -25         | 1111 1110 0111 0000 | FE70        |  |  |  |

| -40         | 1111 1101 1000 0000 | FD80        |  |  |  |

| -55         | 1111 1100 1001 0000 | FC90        |  |  |  |

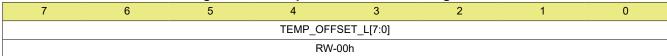

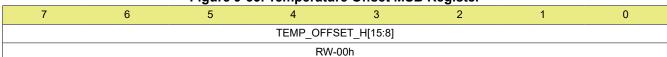

### 9.3.5 Temperature Offset

The temperature offset has the same format as the temperature result and is stored in the temperature offset registers.

The device, after every temperature conversion, applies the offset value before the temperature is stored in the temperature result register. The host write to the offset register can be stored in the configuration EEPROM of the device, which removes the overhead for the host to reprogram the value or reapply in software at every power up. The offset features allow the device to achieve better accuracy at the temperature range for the application by performing a single point calibration.

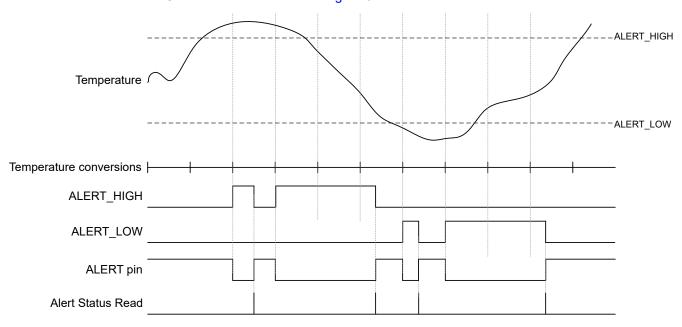

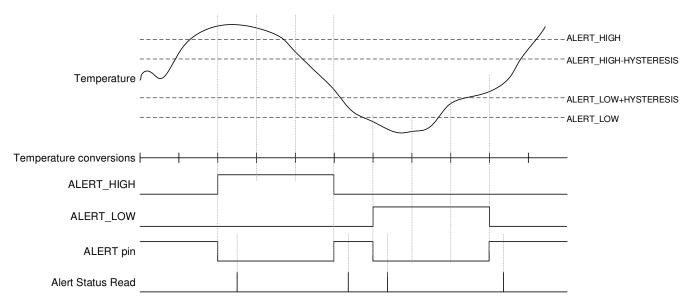

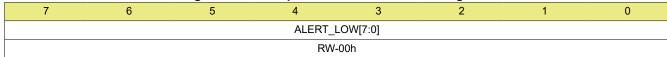

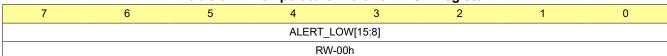

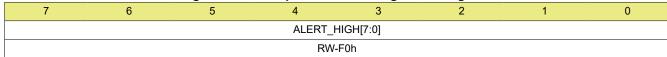

## 9.3.6 Temperature Alert

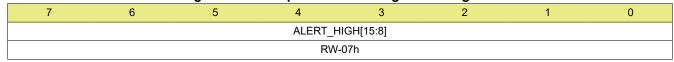

The temperature alert feature uses the temperature alert low registers for low threshold comparison and temperature alert high registers for high threshold comparison. The format of the register is the same as the temperature results.

The device shall compare the result of the last conversion with the alert thresholds. If the temperature result is less than the low limit, or more than the high limits, then the device shall set the appropriate alert status flag, in the status register. The alert status flags are cleared based on the ALERT\_MODE setting in the device configuration-1 register.

Additionally, if the IO2/ALERT pin is configured as an alert pin, the alert status is reflected on the pin in supply powered mode.

## 9.3.7 Standard Device Address

Every device comes with a unique 64-bit address that is factory programmed. This is described below.

## 9.3.7.1 Unique 64-Bit Device Address and ID

The device has a hard-coded, 64-bit address which is factory programmed and cannot be altered by the customer application. The unique 64-bit device address is used for device addressing in the end application and for NIST traceability. Figure 9-3 shows the format of the 64-bit address. When the host accesses the device or when the device sends its address, the 64-bit unique address is sent least significant bit first. The unique 64-bit address consists of 3 fields. The lower 8 bits consists of the device family code, followed by a 48-bit unique number and 8-bit CRC checksum on the 56 bits preceding it.

The device family code for TMP1826 shall read as 26h.

Figure 9-3. 64-Bit Device Address

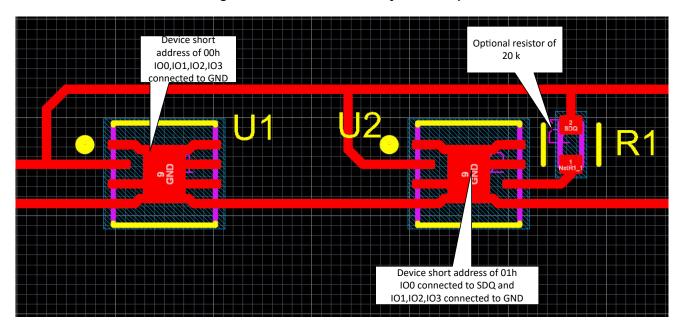

#### 9.3.8 Flexible Device Address

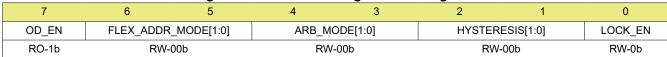

Depending on the user application case, the TMP1826 provides for some user and application configurable address modes, called flexible address mode. These modes exist alongside the standard device address, and is extremely useful for applications that require a combination of faster access and device position identification.

When the flexible device address is used, the short address register is updated. The short address register shall be updated by the host write when the FLEX\_ADDR\_MODE bits are '00b'. When these bits are changed from the value '00b', the device decodes the address resistor connected on ADDR pin or IOs or both of them and overlay on the short address register. This is helpful as the same set of 16 resistors or 16 IO combinations can be used for up to 256 unique flexible address.

The FLEX\_ADDR\_MODE is not stored in the configuration EEPROM, therefore the host must copy the short address register content into EEPROM configuration memory to make the short address values permanent without the need to decode at every power up.

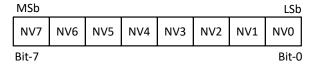

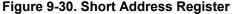

## 9.3.8.1 Non-Volatile Short Address

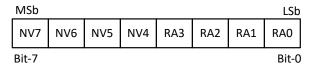

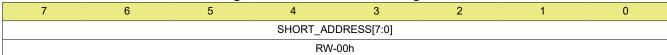

Figure 9-4 shows the user-programmable, 8-bit short address mode of the device. The host must copy the 8-bit short address to the configuration EEPROM, so that at subsequent power up, the device loads the updated short address and respond to the host.

Figure 9-4. Non-Volatile Short Address

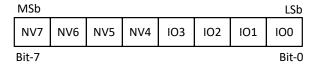

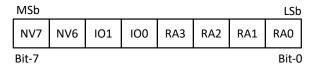

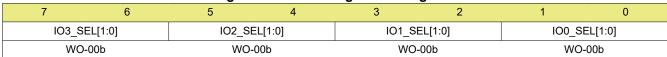

#### 9.3.8.2 IO Hardware Address

Figure 9-5 shows the 8-bit IO hardware address mode of the device. This feature is available on packages which have general-purpose pins (IO0-IO3) available. The 8-bit value consists of the lower 4 bits as read values of the pins (IO3 to IO0) that is overlaid on the contents of the short address register to form a 8-bit address. The application may connect the general-purpose pins to either  $V_{DD}/SDQ$  for logic '1' or GND for logic '0'. TI recommends to use a 20 K $\Omega$  resistor to be placed between the IO and  $V_{DD}/SDQ$  to prevent a supply shot in case the IO pin is accidentally set to zero in output mode.

After having FLEX\_ADDR\_MODE as '00b', the host must set the bits as '01b' in the device configuration-2 register for the device to latch the state of the general-purpose pins.

Figure 9-5. IO Hardware Address

#### Note

IO pins must be configured as input before using IO hardware address mode. If any of the IO0 to IO3 pins are used in output mode, then the respective value shall be latched as '0'.

#### 9.3.8.3 Resistor Address

The resistor address modes uses E96-series (1% tolerance) standard resistor connected between the ADDR pin and ground. Figure 9-6 shows the 8-bit address with the lower 4 bits decoded from the resistor connected, which is overlaid on the contents of the short address register.

Figure 9-6. Resistor Address

After having FLEX\_ADDR\_MODE as '00b', the host controller must set the bits as '10b' in the device configuration-2 register which enables the device to decode the resistor connected. After writing the device configuration-2 register, the host must place the device in shut down mode and idle the bus for  $t_{RESDET}$ , for the device to decode the resistor address. Table 9-3 shows the set value of the device address based on the decoded resistor value. If the ADDR pin connected to GND or lower than 6.49 k $\Omega$ , then the address decoder shall always decode as '0000b'. Similarly, if the ADDR pin is connected to a resistor higher than 54.9 k $\Omega$ , the address decoder shall always decode as '1111b'.

Table 9-3. Resistor Address Decode

| RESISTOR VALUE (kΩ) | ADDRESS DECODE |

|---------------------|----------------|

| < 6.49              | 0h             |

| 7.87                | 1h             |

| 9.31                | 2h             |

| 11.0                | 3h             |

| 13.3                | 4h             |

| 15.4                | 5h             |

| 17.8                | 6h             |

| 20.5                | 7h             |

| 23.7                | 8h             |

| 26.7                | 9h             |

| 30.1                | Ah             |

Copyright © 2023 Texas Instruments Incorporated

| RESISTOR VALUE (kΩ) | ADDRESS DECODE |

|---------------------|----------------|

| 33.2                | Bh             |

| 37.4                | Ch             |

| 42.2                | Dh             |

| 47.5                | Eh             |

| > 54.9 or floating  | Fh             |

This mode is useful when the application requires placing the TMP1826 on multiple printed circuit boards (PCBs). The Bill of Materials (BOM) component can be changed easily instead of having multiple PCBs fabricated for individual pin connections, thereby reducing the cost of the system.

#### Note

If unused, the ADDR pin is recommended be connected to GND. The  $C_{LOAD}$  for ADDR pin is due to parasitic capacitance depending on the board layout.

#### 9.3.8.4 Combined IO and Resistor Address

In the combined IO and resistor address mode, the IO0 and IO1 pins are used along with the resistor connected between ADDR pin and ground. Figure 9-7 shows the 8-bit address with the lower 4 bits decoded from the resistor connected, followed by 2 bits decoded from the IO0 and IO1 pins which may be connected to either VDD/SDQ for logic '1' or GND for logic '0', which is overlaid on the contents of the short address register. TI recommends to use a 20 K $\Omega$  resistor to be placed between the IO and V<sub>DD</sub>/SDQ to prevent a supply shot in case the IO pin is accidentally set to zero in output mode.

After having FLEX\_ADDR\_MODE as '00b', the host must set the bits as '11b' in the device configuration-2 register which enables the device to sample the ADDR pin to identify the resistor connected, followed by sampling of the IO0 and IO1 to configure the short address. If the bit field value has already been updated in the non-volatile storage, then the device shall automatically latch the pins, run the resistor decoder, and update the value in the short address register on power up.

The host controller must place the device in shut down mode and idle the bus for  $t_{RESDET}$ , for the device to decode the resistor address.

Figure 9-7. Combined IO and Resistor Address

This mode is useful when the application requires placing up to 64 devices on a single PCB, as it allows for easy expansion using a combined approach of IO and resistor decoding while enabling IO2 and IO3 to function as general-purpose input and output pins. This mode may also be used for position identification as no two devices may have the same short address.

#### Note

IO pins must be configured as input before using IO hardware address mode. If the IO0 or IO1 pins are used in output mode, then the respective value shall be latched as '0'.

## 9.3.9 CRC Generation

The TMP1826 implements a cyclic redundancy check (CRC) mechanism for data integrity check and communication robustness. Table 9-4 lists the properties of a 8-bit CRC.

Table 9-4. CRC-8 Rule

| CRC-8 RULE | ATTRIBUTES |

|------------|------------|

| CRC width  | 8 bits     |

# Table 9-4. CRC-8 Rule (continued)

| CRC-8 RULE            | ATTRIBUTES                                                  |

|-----------------------|-------------------------------------------------------------|

| CRC polynomial        | x <sup>8</sup> + x <sup>5</sup> + x <sup>4</sup> + 1 (0x31) |

| Initial seed value    | 00h                                                         |

| Input data reflected  | Yes                                                         |

| Output data reflected | Yes                                                         |

| XOR value             | 00h                                                         |

When a new transaction is done, the shift register is initialized with the seed value of 00h and the data is shifted in LSB first. The CRC result is always part of the 64-bit unique address and is computed on the 56-bits that precede it. Additionally, when the host writes to the scratchpad-1 for the registers and scratchpad-2 for the memory, the device sends the CRC computed on the data bytes to provide a data integrity check for the host on the transaction. When the host reads the scratchpad-1 for reading the temperature register, the device shall append the CRC after the 8 bytes of scratchpad are sent.

The host must recalculate the CRC and compare it against the received CRC from the device. This is done by shifting the read data from the device along with CRC bits. If there is no bus error, then the shift register at the end of the bit shift will result in 00h. When writing the data to the device, the host must check the CRC received by processing the write data to ensure that there were no transmission errors and take appropriate corrective action before performing the next function.

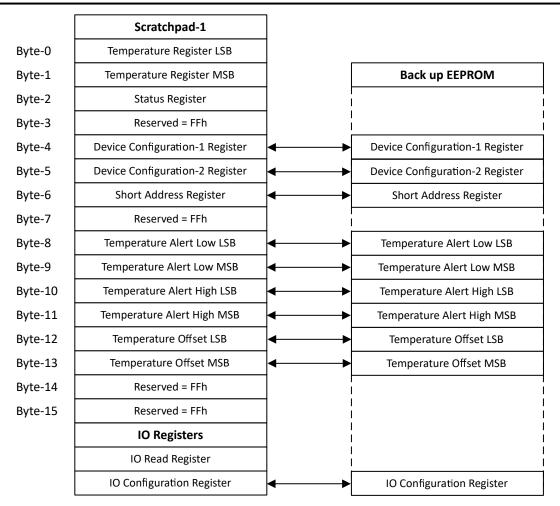

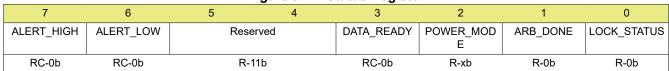

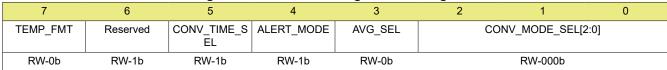

# 9.3.10 Functional Register Map

The scratchpad-1 region and the IO register region together are referred to as the functional register map (see Figure 9-8). The scratchpad-1 region is 16 bytes deep, and has temperature result, device status, device configuration, short address, temperature alert limits and temperature offset registers. The IO register region has the IO read and IO configuration registers. Some of the registers can be committed to the configuration EEPROM to ensure that the device settings are restored on power up without the host rewriting the configuration.

Figure 9-8. Functional Register Map (Scratchpad-1)

### 9.3.11 User Memory Map

The EEPROM memory is organized as 8 pages of 4 blocks each. Figure 9-9 shows that each block is 8 bytes or 64 bits. This results in a total user memory of 2048 bits. All memory access to the device shall be increments of a block size of 8 bytes. Access to the memory for programming is done through the scratchpad-2 register. The host writes to the scratchpad-2 register, which allows the device to perform a read before committing the content to the memory.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

| <b></b>                                                  | 00FFh  |            | Block 3 | 00F8h – 00FFh |

|----------------------------------------------------------|--------|------------|---------|---------------|

| <b>◆</b> ——256 bytes———————————————————————————————————— | 00E0h  | Page 7     | Block 2 | 00F0h – 00F7h |

|                                                          |        |            | Block 1 | 00E8h – 00EFh |

|                                                          |        |            | Block 0 | 00E0h – 00E7h |

|                                                          | 00DFh  | Page 6     | Block 3 | 00D8h – 00DFh |

|                                                          | 005111 |            | Block 2 | 00D0h - 00D7h |

|                                                          |        |            | Block 1 | 00C8h - 00CFh |

|                                                          | 00C0h  |            | Block 0 | 00C0h - 00C7h |

|                                                          | 00BFh  | Page 5     | Block 3 | 00B8h – 00CFh |

|                                                          | OODIII |            | Block 2 | 00B0h – 00B7h |

|                                                          |        |            | Block 1 | 00A8h – 00AFh |

|                                                          | 00A0h  |            | Block 0 | 00A0h – 00A7h |

|                                                          | 009Fh  |            | Block 3 | 0098h – 009Fh |

|                                                          | 003111 | Page 4     | Block 2 | 0090h – 0097h |

|                                                          |        |            | Block 1 | 0088h – 008Fh |

|                                                          | 0080h  |            | Block 0 | 0080h – 0087h |

|                                                          | 007Fh  |            | Block 3 | 0078h – 007Fh |

|                                                          | 007111 |            | Block 2 | 0070h – 0077h |

|                                                          |        | Page 3     | Block 1 | 0068h – 006Fh |

|                                                          | 0060h  |            | Block 0 | 0060h – 0067h |

|                                                          | 005Fh  | Page 2     | Block 3 | 0058h – 005Fh |

|                                                          |        |            | Block 2 | 0050h – 0057h |

|                                                          |        |            | Block 1 | 0048h – 004Fh |

|                                                          | 0040h  |            | Block 0 | 0040h – 0047h |

|                                                          | 003Fh  |            | Block 3 | 0038h – 003Fh |

|                                                          |        | Page 1     | Block 2 | 0030h – 0037h |

|                                                          |        |            | Block 1 | 0028h – 002Fh |

|                                                          | 0020h  |            | Block 0 | 0020h – 0027h |

|                                                          | 001Fh  | -32 bytes- | Block 3 | 0018h – 001Fh |

|                                                          |        |            | Block 2 | 0010h - 0017h |

|                                                          |        |            | Block 1 | 0008h – 000Fh |

|                                                          |        |            | Block 0 | 0000h – 0007h |

|                                                          |        |            | 1       | _ =====       |

Figure 9-9. Address to EEPROM Page and Block Map

#### **Note**

The device shall return "1" for any device read if the address is outside the user memory map.

### 9.3.12 Bit Communication

The 1-Wire interface communication does not have a reference clock, therefore all communication is performed asynchronously with fixed time slot ( $t_{SLOT}$ ) and variable pulse width to indicate logic '0' and '1'. In idle state, the external pullup resistor holds the line high. All bit communication, whether it is a write or a read, are initiated by the host by driving the data line low to generate a falling edge and the bit value is decoded as the time for which the data line is held low or high after the falling edge.

Even though the communication is one bit at a time, the data exchanged between the host and device is performed at byte boundary. Every byte is sent least significant bit first. The device behavior is not ensured when incomplete bytes are sent.

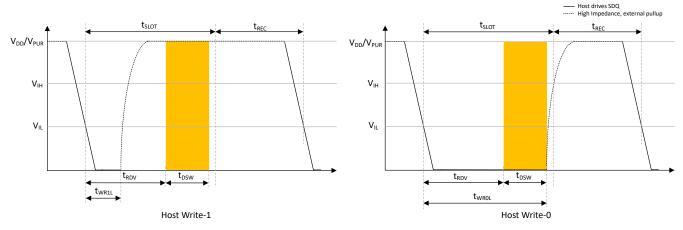

### 9.3.12.1 Host Write, Device Read

A host write is the means by which the host sends the command, function, and data to the devices. A host write starts by the host driving the data line low as shown in Figure 9-10. If the host intends to transmit a logic '1', the line is released after  $t_{WR1L}$  time. If the host intends to transmit a logic '0', the line is released after  $t_{WR0L}$ . After releasing the data, the pullup resistor causes the line to become high till the beginning of the next time slot. The device samples the line after  $t_{RDV}$  has elapsed from the falling edge, for a time frame indicated by  $t_{DSW}$ . The host must factor the rise time due to the pullup resistor and bus capacitance to determine the release of the data line before the line is sampled by the device and the host drives the next write bit time slot.

Figure 9-10. Host Write, Device Read

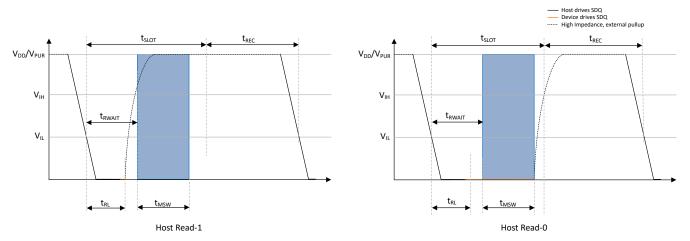

#### 9.3.12.2 Host Read. Device Write

A host read is the means by which the hosts gets the data from the device or the CRC for data integrity check. A host read starts by the host driving the data line low as shown in Figure 9-11. When the device detects the falling edge, the device can drive the line low before the time  $t_{RL}$ . The host can release the bus from the side after the time  $t_{RL(MIN)}$  elapses. If the device intends to transmit a logic '1', then the bus is released before  $t_{RL(MAX)}$  elapses. If the device intends to transmit a logic '0', then the bus is released after  $t_{SLOT(MIN)}$ . The host must sample the line after the time  $t_{RWAIT}$ , for a time frame indicated by  $t_{MSW}$ . The host must factor the rise time due to the pullup resistor and bus capacitance to determine the sampling window for the host to sample the bit level sent by the device or to drive the next read bit time slot.

Figure 9-11. Host Read, Device Write

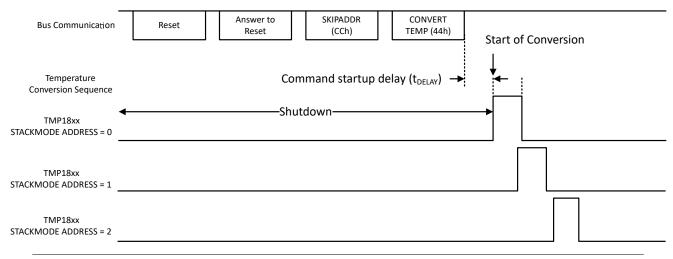

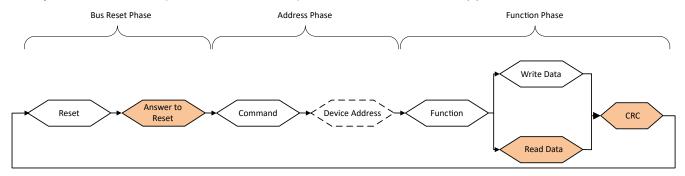

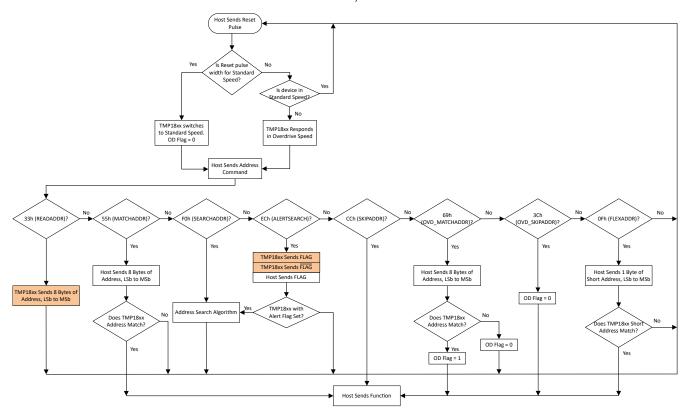

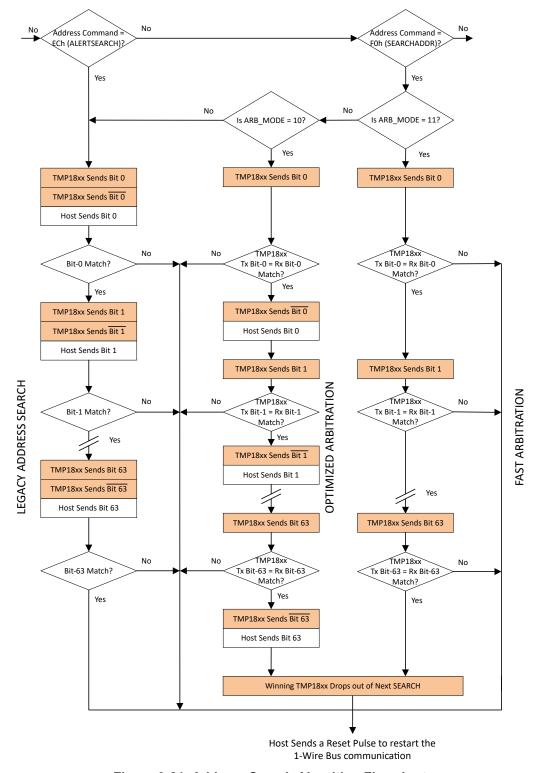

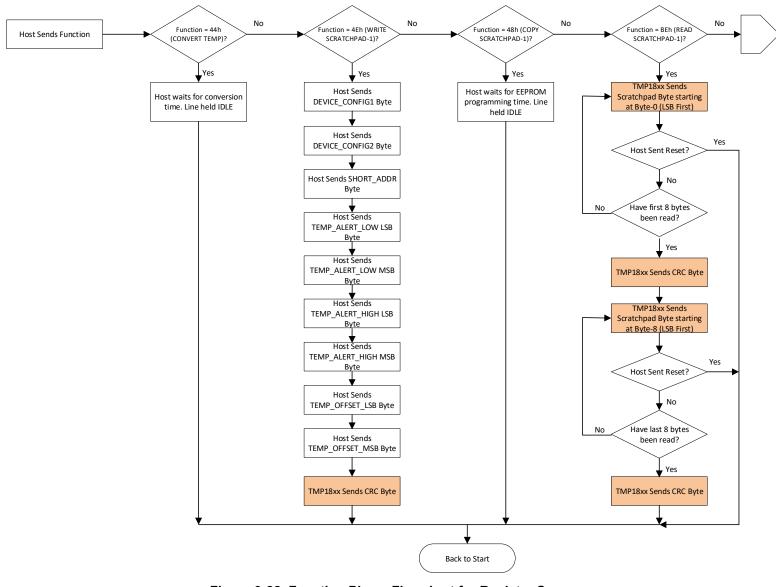

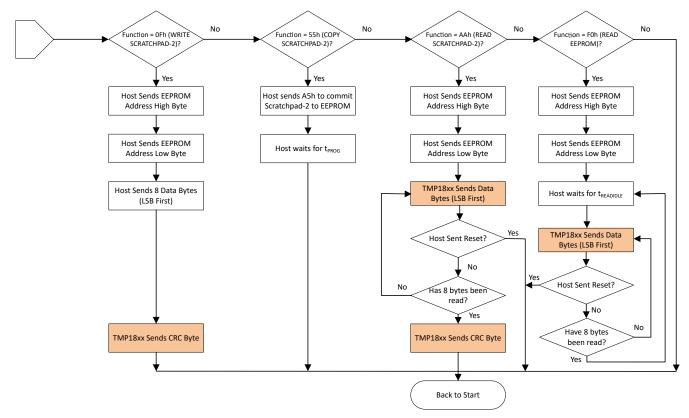

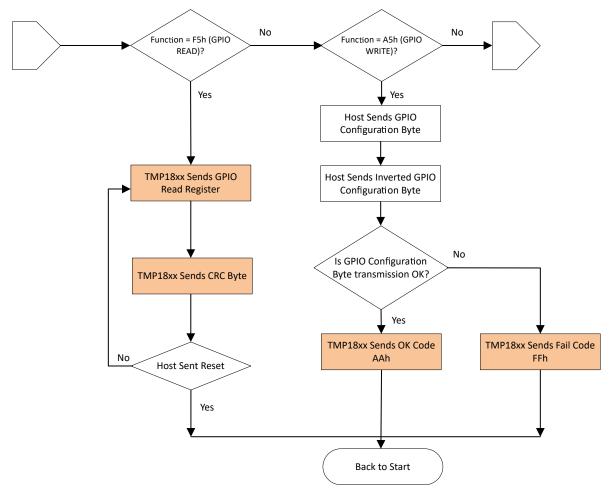

### **9.3.13 Bus Speed**