#### DESCRIPTION

The HSN75176ADR used for RS-485/RS-422 communication is a 10Mbps high-speed transceiver for half duplex communication, which includes one driver Device and a receiver.

Equippedwith ± 8kV human mode ESD protection and failure protection circuit, ensuring that when the receiver input is open or short circuited Receiver output logic high level.

If all transmitters attached to the terminal matching bus are disabled (high resistance), the receiver will output logic high Level.

The HSN75176ADR driver does not limit the swing rate and can ensure a communication rate of up to 10Mbps.

HSN75176ADR has a receiver with 1 Unit load input impedance, up to 32 transceivers can be connected to the bus.

In addition, HSN75176ADR also has an built-in overtemperature protection circuit to ensure the chip is not damaged under high temperature conditions.

#### **FEATURES**

- · Provide low current shutdown mode

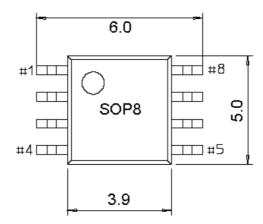

- · Provide industry standard 8-pin SOP packaging

- Up to 32 transceivers are allowed to be mounted on the bus

- · True fail safe receiver compatible with EIA/TIA-485

- Built in over temperature protection circuit ensures that the chip is not damaged due to High temperatures

- Provide enhanced ESD protection for RS-485/ RS-422 A/B pins

#### **APPLICATIONS**

- SCSI "Fast 40" Drivers and Receivers.

- · Motor Controller/Position Encoder Systems

- · Factory Automation

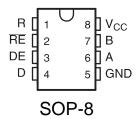

#### PIN CONFIGURATION

#### **Pin Functions**

| Р               | IN  | 1/0                 | DESCRIPTION                                          |

|-----------------|-----|---------------------|------------------------------------------------------|

| NAME            | NO. | I/O                 | DESCRIPTION                                          |

| Α               | 6   | Bus input/output    | Driver output or receiver input (complementary to B) |

| В               | 7   | Bus input/output    | Driver output or receiver input (complementary to A) |

| D               | 4   | Digital input       | Driver data input                                    |

| DE              | 3   | Digital input       | Active-HIGH driver enable                            |

| GND             | 5   | Reference potential | Local device ground                                  |

| R               | 1   | Digital output      | Receiver data output                                 |

| RE              | 2   | Digital input       | Active-LOW receiver enable                           |

| V <sub>CC</sub> | 8   | Supply              | 4.75-V to 5.25-V supply                              |

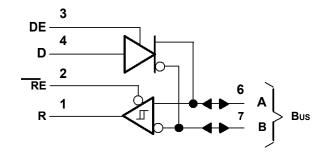

## **LOGIC DIAGRAM**

## **FEATUER DESCRIPTION**

#### **DRIVER FUNCTION TABLE**

| INPUT | ENABLE | OUT | PUTS |

|-------|--------|-----|------|

| D     | DE     | Α   | В    |

| Н     | Н      | Н   | L    |

| L     | Н      | L   | Н    |

| Х     | L      | Z   | Z    |

H = high level,

L = low level,

X = irrelevant,

Z = high impedance (off)

#### **RECEIVER FUNCTION TABLE**

| DIFFERENTIAL<br>INPUTS<br>A-B    | EN <u>AB</u> LE<br>RE | OUTPUT<br>R |

|----------------------------------|-----------------------|-------------|

| V <sub>ID</sub> ≥ 0.2 V          | L                     | Н           |

| -0.2 V < V <sub>ID</sub> < 0.2 V | L                     | ?           |

| V <sub>ID</sub> ≤ -0.2 V         | L                     | L           |

| X                                | Н                     | Z           |

| Open                             | L                     | ?           |

H = high level,

L = low level,

? = indeterminate,

X = irrelevant, Z = high impedance (off)

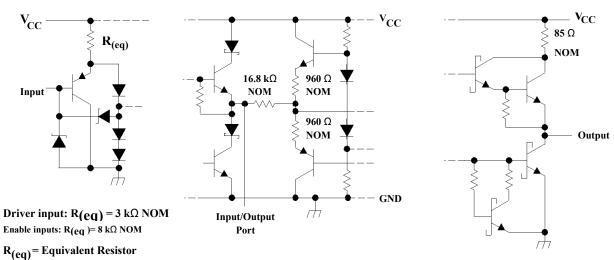

#### **EQUIVALENT OF EACH INPUT**

#### ABSOLUTE MAXIMUM RATINGS

( $V_{CC} = 5V \pm 5\%$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) over operating free-air temperature range (unless otherwise noted)1)

| SYMBOL                           | PARAMETER                                                    | MIN | MAX | UNIT |

|----------------------------------|--------------------------------------------------------------|-----|-----|------|

| V                                | Supply voltage (2)                                           |     | 7   | V    |

|                                  | Voltage range at any bus terminal                            | -10 | 15  | V    |

| VI                               | Enable input voltage                                         |     | 5.5 | V    |

| $\theta_{\scriptscriptstyle JA}$ | Package thermal impedance <sup>(3)(4)</sup>                  |     | 85  | °C/W |

| TJ                               | Operating virtual junction temperature                       |     | 150 | C    |

|                                  | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |     | 260 | C    |

| Tstg                             | Storage temperature range                                    | -65 | 150 | C    |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- All voltage values, except differential input/output bus voltage, are with respect to network ground terminal.

- (3) Maximum power dissipation is a function of T<sub>J(max)</sub>, θ<sub>JA</sub>, and T<sub>A</sub>. The maximum allowable power dissipation at any allowable ambient temperature is PD =  $(T_J(max) - T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of 150°C can affect reliability. The package thermal impedance is calculated in accordance with JESD 51-7.

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL          | PARAMETER                                               |                                |   | TYP | MAX        | UNIT |

|-----------------|---------------------------------------------------------|--------------------------------|---|-----|------------|------|

| $V_{CC}$        | Supply voltage                                          |                                |   | 5   | 5.25       | V    |

| VI or VIC       | Voltage et any hye terminal (constr                     |                                |   |     | 12         | \/   |

| ALOI AIC        | Voltage at any bus terminal (separately or common mode) |                                |   |     | <b>–</b> 7 | V    |

| Vih             | High-level input voltage                                | D, DE, and RE                  | 2 |     |            | V    |

| Vıl             | Low-level input voltage                                 | D, DE, and RE                  |   |     | 0.8        | V    |

| V <sub>ID</sub> | Differential input voltage                              | Differential input voltage (1) |   |     | ±12        | V    |

|                 |                                                         | Driver                         |   |     | -60        | mA   |

| I <sub>OH</sub> | High-level output current                               | Receiver                       |   |     | -400       | μA   |

|                 |                                                         | Driver                         |   |     | 60         |      |

| loL             | Low-level output current                                | Receiver                       |   |     | 8          | mA   |

| T <sub>A</sub>  | Operating free-air temperature                          |                                | 0 |     | 70         | C    |

<sup>(1)</sup> Differential input/output bus voltage is measured at the noninverting terminal A, with respect to the inverting terminal B.

## **DRVER SECTION Electrical Characteristics**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| SYMBOL            | PARAMETER                                                         | TEST CON                                     | DITIONS <sup>(1)</sup>       | MIN                           | TYP <sup>(2)</sup> | MAX       | UNIT |

|-------------------|-------------------------------------------------------------------|----------------------------------------------|------------------------------|-------------------------------|--------------------|-----------|------|

| $V_{IK}$          | Input clamp voltage                                               | I <sub>I</sub> = -18 mA                      |                              |                               |                    | -1.5      | V    |

| VO                | Output voltage                                                    | I <sub>O</sub> = 0                           |                              | 0                             |                    | 6         | V    |

| VOD1              | Differential output voltage                                       | IO = 0                                       |                              | 1.5                           | 3.6                | 6         | V    |

|                   |                                                                   | R <sub>L</sub> = 100 Ω                       |                              | 1/2 V <sub>OD1</sub> or 2 (3) |                    |           |      |

| VOD2              | Differential output voltage                                       | R <sub>L</sub> = 54 Ω                        |                              | 1.5                           | 2.5                | 5         | V    |

| V <sub>OD3</sub>  | Differential output voltage                                       | See (4)                                      |                              | 1.5                           |                    | 5         | V    |

| Δ V <sub>OD</sub> | Change in magnitude of differential output voltage <sup>(5)</sup> | R <sub>L</sub> = 54 Ω or 100 Ω               |                              |                               |                    | ±0.2      | V    |

| Voc               | Common-mode output voltage                                        | R <sub>L</sub> = 54 $\Omega$ or 100 $\Omega$ |                              |                               |                    | +3<br>–1  | V    |

| ΔIVOCI            | Change in magnitude of common-mode output voltage <sup>(3)</sup>  | $R_L$ = 54 $\Omega$ or 100 $\Omega$          |                              |                               |                    | ±0.2      | V    |

| lo                | Output current                                                    | Output disabled <sup>(6)</sup>               | $V_O = 12 V$<br>$V_O = -7 V$ |                               |                    | 1<br>-0.8 | mA   |

| Іш                | High-level input current                                          | V <sub>I</sub> = 2.4 V                       |                              |                               |                    | 20        | μA   |

| I⊩                | Low-level input current                                           | V <sub>I</sub> = 0.4 V                       |                              |                               |                    | -400      | μA   |

|                   |                                                                   | V <sub>O</sub> = -7 V                        |                              |                               |                    | -250      |      |

|                   |                                                                   | VO = 0                                       |                              |                               |                    | -150      |      |

| los               | Short-circuit output current                                      | V - V<br>O CC                                |                              |                               |                    | 250       | mA   |

|                   |                                                                   | V <sub>O</sub> = 12 V                        |                              |                               |                    | 250       |      |

|                   |                                                                   |                                              | Outputs enabled              |                               | 42                 | 70        |      |

| Icc               | Supply current (total package)                                    | No load                                      | Outputs disabled             |                               | 26                 | 35        | mA   |

- (1) The power-off measurement in ANSI Standard TIA/EIA-422-B applies to disabled outputs only and is not applied to combined inputs and outputs.

- All typical values are at  $V_{CC}$  = 5 V and  $T_A$  = 25°C.

- (3) The minimum V<sub>OD2</sub> with a 100-Ω load is either 1/2 V<sub>OD1</sub> or 2 V, whichever is greater.

(4) See ANSI Standard TIA/EIA-485-A, Figure 3.5, Test Termination Measurement 2.

- (5) |VOD| and |VOC| are the changes in magnitude of VOD and VOC, respectively, that occur when the input is changed from a high level

- This applies for both power on and off; refer to ANSI Standard TIA/EIA-485-A for exact conditions. The TIA/EIA-422-B limit does not apply for a combined driver and receiver terminal.

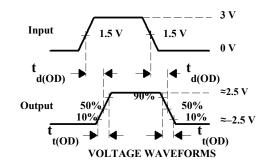

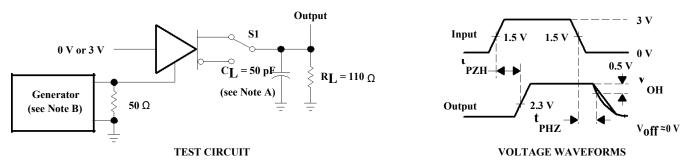

## **Switching Characteristics**

$V_{CC}$  = 5 V,  $R_L$  = 110  $\Omega$ ,  $T_A$  = 25°C (unless otherwise noted)

| SYMBOL                    | PARAMETER                           | TEST CONDITIONS       | MIN | TYP | MAX | UNIT |

|---------------------------|-------------------------------------|-----------------------|-----|-----|-----|------|

| $t_{\text{d}(\text{OD})}$ | Differential-output delay time      | R <sub>L</sub> = 54 Ω |     | 15  | 22  | ns   |

| $t_{t(OD)}$               | Differential-output transition time | R <sub>L</sub> = 54 Ω |     | 20  | 30  | ns   |

| t <sub>PZH</sub>          | Output enable time to high level    |                       |     | 85  | 120 | ns   |

| t <sub>PZL</sub>          | Output enable time to low level     |                       |     | 40  | 60  | ns   |

| t <sub>PHZ</sub>          | Output disable time from high level |                       |     | 150 | 250 | ns   |

| t <sub>PLZ</sub>          | Output disable time from low level  |                       |     | 20  | 30  | ns   |

## Symbol Equivalents

| DATA SHEET PARAMETER | TIA/EIA-422-B                           | TIA/EIA-485-A                                   |

|----------------------|-----------------------------------------|-------------------------------------------------|

| VO                   | Voa, Vob                                | Voa, Vob                                        |

| VOD1                 | Vo                                      | Vo                                              |

| V <sub>OD2</sub>     | V <sub>t</sub> (R <sub>L</sub> = 100 Ω) | V <sub>t</sub> (R <sub>L</sub> = 54 Ω)          |

| V <sub>OD3</sub>     |                                         | V <sub>t</sub> (test termination measurement 2) |

| Δ VOD                | $   V_t  -  \overline{V_t}   $          | V <sub>t</sub> -   <del>-</del>                 |

| Voc                  | V <sub>os</sub>                         | V <sub>os</sub>                                 |

| Δ VOC                | $ V_{OS} - \overline{V}_{OS} $          | V <sub>OS</sub> - \( \overline{V} \) os         |

| los                  | I <sub>sa</sub>  ,  I <sub>sb</sub>     |                                                 |

| lo                   | I <sub>xa</sub>  ,  I <sub>xb</sub>     | lia, lib                                        |

# RECEIVER SECTION Electrical Characteristics

over recommended ranges of common-mode input voltage, supply voltage, and operating free-air temperature (unless otherwise noted)

| SYMBOL           | PARAMETER                                                       | TEST CONDITIONS                              |                       | MIN                 | TYP <sup>(1)</sup> | MAX  | UNIT |

|------------------|-----------------------------------------------------------------|----------------------------------------------|-----------------------|---------------------|--------------------|------|------|

| V <sub>IT+</sub> | Positive-going input threshold voltage                          | $V_0 = 2.7 \text{ V}, I_0 = -0.4$            | 1 mA                  |                     |                    | 0.2  | V    |

| V <sub>II-</sub> | Negative-going input threshold voltage                          | VO= 0.5 V, IO = 8 mA                         | 4                     | -0.2 <sup>(2)</sup> |                    |      | V    |

| V <sub>hys</sub> | Input hysteresis voltage (V <sub>IT+</sub> – V <sub>IT-</sub> ) |                                              |                       |                     | 50                 |      | mV   |

| Vıĸ              | Enable Input clamp voltage                                      | I <sub>I</sub> = -18 mA                      |                       |                     |                    | -1.5 | V    |

| V <sub>OH</sub>  | High-level output voltage                                       | V <sub>ID</sub> = 200 mV, I <sub>OH</sub> =  | : –400 uA             | 2.7                 |                    |      | V    |

| Vol              | Low-level output voltage                                        | V <sub>ID</sub> = -200 mV, l <sub>OL</sub> : | = 8 mA                |                     |                    | 0.45 | V    |

| loz              | High-impedance-state output current                             | V <sub>O</sub> = 0.4 V to 2.4 V              |                       |                     |                    | ±20  | μA   |

|                  | Line input current                                              | Other input = 0 V <sup>(3)</sup>             | V <sub>I</sub> = 12 V |                     |                    | 1    | mA   |

| 1                | Zine input current                                              |                                              | V <sub>I</sub> = -7 V |                     |                    | -0.8 |      |

| Iн               | High-level enable input current                                 | V <sub>IH</sub> = 2.7 V                      |                       |                     |                    | 20   | μA   |

| <b>I</b> IL      | Low-level enable input current                                  | V <sub>IL</sub> = 0.4 V                      |                       |                     |                    | -100 | μA   |

| rı               | Input resistance                                                | V <sub>I</sub> = 12 V                        |                       | 12                  |                    |      | kΩ   |

| los              | Short-circuit output current                                    |                                              |                       | -15                 |                    | -85  | mA   |

|                  |                                                                 |                                              | Outputs enabled       |                     | 42                 | 55   |      |

| Icc              | Supply current (total package)                                  | No load                                      | Outputs disabled      |                     | 26                 | 35   | mA   |

<sup>(1)</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ .

## **Switching Characteristics**

V<sub>CC</sub> = 5 V, C<sub>L</sub> = 15 pF, T<sub>A</sub> = 25°C

| SYMBOL           | PARAMETER                                         | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------------------------|----------------------------|-----|-----|-----|------|

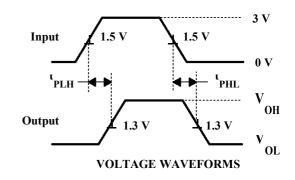

| t <sub>PLH</sub> | Propagation delay time, low- to high-level output | \\- = 0 to 2 \\            |     | 21  | 35  | ns   |

| t <sub>PHL</sub> | Propagation delay time, high- to low-level output | V <sub>ID</sub> = 0 to 3 V |     | 23  | 35  | 115  |

| <b>t</b> PZH     | Output enable time to high level                  |                            |     | 10  | 20  | ns   |

| tpzL             | Output enable time to low level                   |                            |     | 12  | 20  | 115  |

| <b>t</b> PHZ     | Output disable time from high level               |                            |     | 20  | 35  | ns   |

| <b>t</b> PLZ     | Output disable time from low level                | ]                          |     | 17  | 25  | 110  |

<sup>(2)</sup> The algebraic convention, in which the less positive (more negative) limit is designated minimum, is used in this data sheet for common-mode input voltage and threshold voltage levels only.

<sup>(3)</sup> This applies for both power on and power off. Refer to EIA Standard TIA/EIA-485-A for exact conditions.

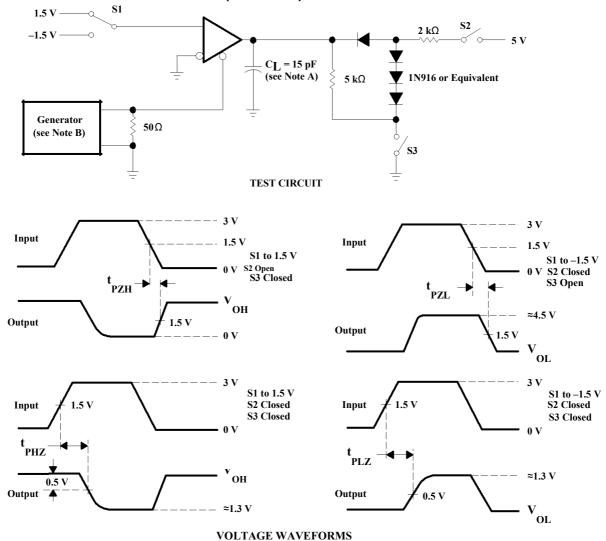

#### **Parameter Measurement Information**

OL TOPHONION

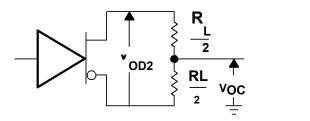

Figure 1. Driver  $V_{\mbox{\scriptsize OD}}$  and  $V_{\mbox{\scriptsize OC}}$

Figure 2. Receiver VOH and VOL

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_\Gamma \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50 \ \Omega$ .

Figure 3. Driver Test Circuit and Voltage Waveforms

- A. CL includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_\Gamma \leq$  6 ns,  $t_f \leq$  6 ns,  $t_T \leq$  7 ns,  $t_T \leq$  8 ns,  $t_T \leq$  8 ns,  $t_T \leq$  9 ns,

Figure 4. Driver Test Circuit and Voltage Waveforms

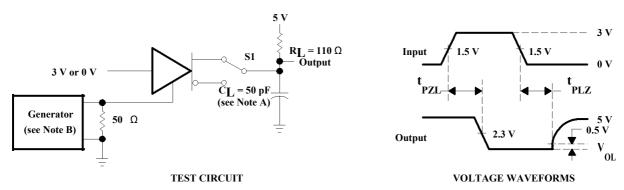

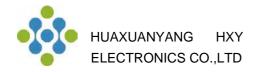

## Parameter Measurement Information (continued)

- A. CL includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_{\Gamma} \leq$  6 ns,  $t_{\Gamma} \leq$  7 ns,  $t_{\Gamma} \leq$  8 ns,  $t_{\Gamma} \leq$  8 ns,  $t_{\Gamma} \leq$  9 ns,  $t_{\Gamma} \leq$  9

Figure 5. Receiver Test Circuit and Voltage Waveforms

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  7 ns,  $t_f \leq$  8 ns,  $t_f \leq$  9 ns,

Figure 6. Driver Test Circuit and Voltage Waveforms

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50 \Omega$ .

Figure 7. Receiver Test Circuit and Voltage Waveforms

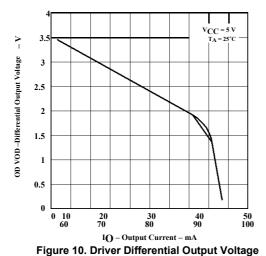

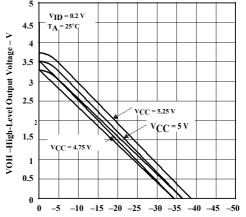

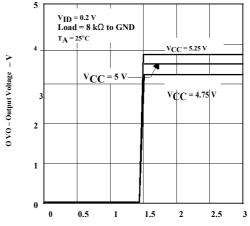

#### TYPOCAL CHARACTERISTICS

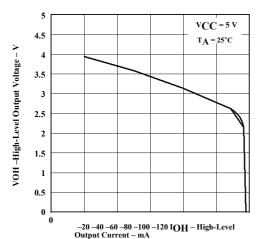

Figure 8. Driver High-Level Output Voltage vs

High-Level Output Current

**Output Current**

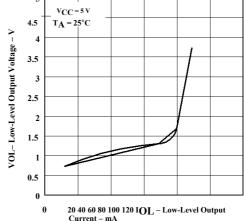

Figure 9. Driver Low-Level Output Voltage vs

Low-Level Output Current

IOH – High-Level Output Current – mA

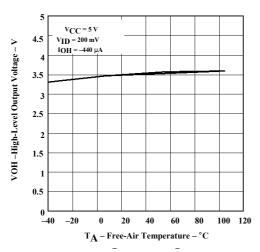

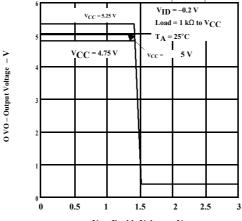

Figure 11. Receiver High-Level Output Voltage

vs

High-Level Output Current

Figure 12. VOH-High-Level Output Voltage vs Free-Air Temperature

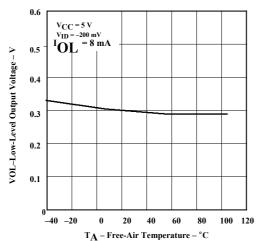

Figure 14. Receiver Low-Level Output Voltage vs

Free-Air Temperature

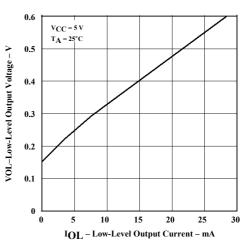

Figure 13. VOL-Low-Level Output Voltage vs

Low -Level Output Current

VI – Enable Voltage – V Figure 15. Receiver Output Voltage vs Enable Voltage

VI – Enable Voltage – V Figure 16. Receiver Output Voltage vs Enable Voltage

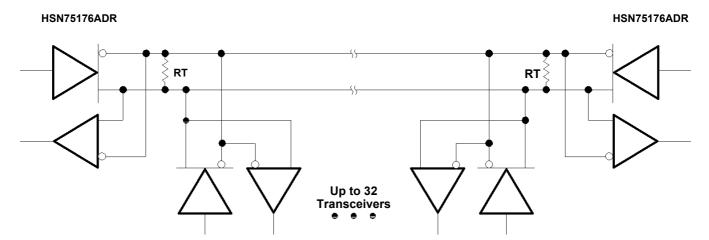

## **APPLICATION INFORMATION**

The line should be terminated at both ends in its characteristic impedance ( $R_T = Z_O$ ). Stub lengths off the main line should be kept as short as possible.

Figure 17. Typical Application Circuit

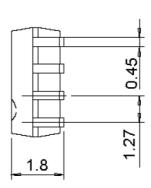

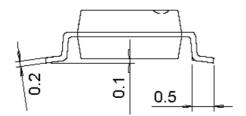

## **PACKAGE OUTLINE DIMENSIONS**

SOP-8

#### **Attention**

- Any and all HUA XUAN YANG ELECTRONICS products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your HUA XUAN YANG ELECTRONICS representative nearest you before using any HUA XUAN YANG ELECTRONICS products described or contained herein in such applications.

- HUA XUAN YANG ELECTRONICS assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein.

- Specifications of any and all HUA XUAN YANG ELECTRONICS products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- HUA XUAN YANG ELECTRONICS CO.,LTD. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all HUA XUAN YANG ELECTRONICS products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of HUA XUAN YANG ELECTRONICS CO.,LTD.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

HUA XUAN YANG ELECTRONICS believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the HUA XUAN YANG ELECTRONICS product that you intend to use.