# KENESAS

# RAA270005KFP

General Purpose Power Management IC

R02DS0017EJ0100 Rev.1.00 Apr. 9, 2018

## Description

The RAA270005KFP is a general-purpose Power Management IC (PMIC), and suitable for RENESAS RH850/P1x series microcontroller (MCU). The features and the details of the PMIC are described in this document.

The PMIC contains two types of DCDCs converters: buck and boost, two low dropout linear regulators (LDO) and two linear trackers.

The switching frequency of boost/buck DCDCs are typical 420 kHz, 2.1 MHz respectively.

Monitor functions for the internal status are implemented. Input voltage, output of all regulators, and internal analog voltage corresponding to temperature can be monitored through ADC of MCU. And reference voltage can be monitored for testing the ADC of MCU as well.

The PMIC has sequencer circuits for controlling power-up/down, therefore any external sequencer circuits are unnecessary. And the PMIC can control an external backup-power for MCU.

## Features

- Supply the power to Renesas RH850/P1x (eVR)

- Load dump robustness

- Input voltage range: 6.6~18.5V to perform specified characteristics.

5.4V $\sim$ : continued operation without low voltage detection 3.8V $\sim$ : continued operation declined the output voltage

\* If not use the boost DCDC converter

- DCDC converter: Boost: 6.0V/250mA (Input voltage: 2.2V~) Buck: 6.1V/600mA

- Linear regulators:

1. Output voltage : 3.3V/10mA

2. Output voltage : 5.0V/350mA with reverse protection

- Two linear trackers

Output voltage: VOUT1/100mA with reverse protection

- Automatic power sequence

- An external backup-power control

- Watchdog timer

- Analog multiplexer

- Interrupt request

- Thermal shut down

- Reset generator

- External devices control

- Monitoring to a core voltage in MCU.

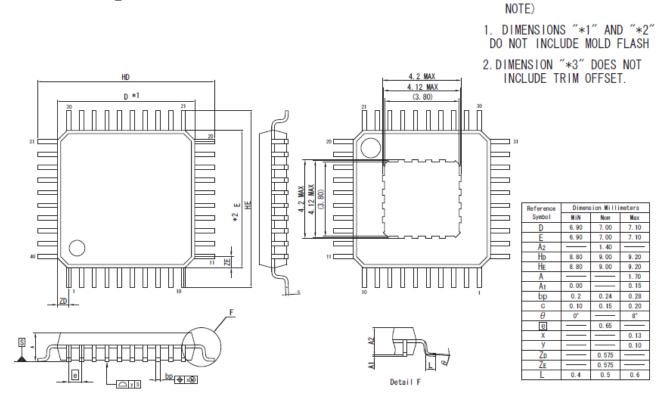

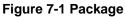

- Exposed die pad, HLQFP package, 40pin 9mm x 9mm

## Application

- Automotive applications

- Industrial applications

# **Table of Contents**

| 1. | Abusolute maximum ratings            | 4  |

|----|--------------------------------------|----|

| 2. | Pin Configuration                    | 5  |

|    | 2.1. Pin Configuration               | 5  |

|    | 2.2. Pin list                        | 6  |

| 3. | Internal Block Diagram               | 8  |

| 4. | PMIC Function                        | 10 |

|    | 4.1. Abstract of the PMIC            | 10 |

|    | 4.1.1. PMIC Operation                |    |

|    | 4.1.2. Pin setting                   |    |

|    | 4.1.3. Configuration register        |    |

|    | 4.1.4. Product code                  |    |

|    | 4.2. Serial Interface                |    |

|    | 4.2.1. Signal format                 |    |

|    | 4.2.2. Ensuring communication        |    |

|    | 4.2.3. Secured request               |    |

|    | 4.2.4. Register                      |    |

|    | 4.2.5. Register map                  |    |

|    | 4.2.6. Electrical characteristics    |    |

|    |                                      |    |

|    | 4.3. Reference Voltage               |    |

|    | 4.3.1. Electrical characteristics    |    |

|    | 4.4. LDO.                            |    |

|    | 4.4.1. Output protection function    |    |

|    | 4.4.2. Electrical characteristics    |    |

|    | 4.5. Tracker                         |    |

|    | 4.5.1. Register                      |    |

|    | 4.5.2. Electrical characteristics    |    |

|    | 4.6. DCDC converter (DCDC)           |    |

|    | 4.6.1. Buck DCDC                     |    |

|    | 4.6.2. Boost DCDC                    |    |

|    | 4.6.3. Register                      |    |

|    | 4.6.4. Electrical characteristics    |    |

|    | 4.7. Power Rail Sequence             |    |

|    | 4.7.1. Power up sequence             |    |

|    | 4.7.2. Power down sequence           | 29 |

|    | 4.7.3. Working with a backup-power   | 31 |

|    | 4.8. Watchdog Timer (WDT)            | 33 |

|    | 4.8.1. Window WDT                    | 33 |

|    | 4.8.2. WDT operation                 | 33 |

|    | 4.8.3. Advanced mode                 |    |

|    | 4.8.4. Register                      |    |

|    | 4.8.5. Electrical characteristic     |    |

|    | 4.9. Reset                           |    |

|    | 4.9.1. Reset factor                  |    |

|    | 4.9.2. Reset factor register         |    |

|    | 4.9.3. Software reset                |    |

|    | 4.9.4. External reset                |    |

|    | 4.9.5. Electrical characteristics    |    |

|    | 4.10. Specified output pins          |    |

|    | 4.10.1. Low voltage indicator (SUSP) |    |

|    | 4.10.2. Error input (ERROR)          |    |

|    | 4.10.2. Entor input (ERROR)          |    |

|    |                                      |    |

|    |                                      |    |

|    | 4.10.5. Register                     |    |

|    | 4.10.6. Electrical characteristics   |    |

|    | 4.11. Interrupt Signal               |    |

|    | 4.11.1. Interrupt control            |    |

|    | 4.11.2. Interrupt factors            | DI |

|    | 4.11.3.       | Register                              | 52 |

|----|---------------|---------------------------------------|----|

|    | 4.12. Func    | tional Safety                         |    |

|    | 4.12.1.       | Voltage detection                     | 59 |

|    | 4.12.2.       | PMIC behavior after unusual detection | 60 |

|    | 4.12.3.       | Self-diagnosis                        | 61 |

|    |               | Electrical characteristics            |    |

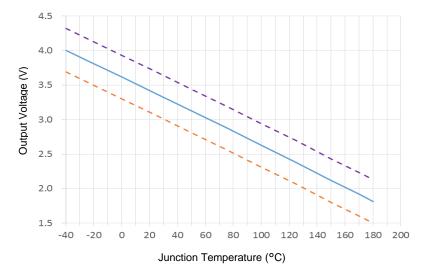

|    | 4.13. Temp    | perature sensor                       | 65 |

|    |               | Thermal shutdown                      |    |

|    | 4.13.2.       | Register                              | 65 |

|    | 4.14. Monit   | toring Function                       | 67 |

|    | 4.14.1.       | Internal analog voltage monitoring    | 67 |

|    | 4.14.2.       | Digital output monitoring             | 67 |

|    | 4.14.3.       | Register                              | 68 |

|    | 4.14.4.       | Electrical characteristics            | 68 |

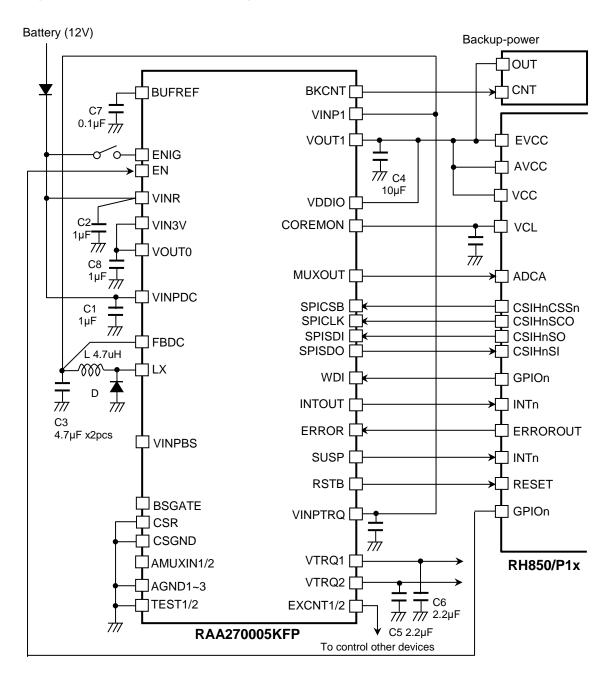

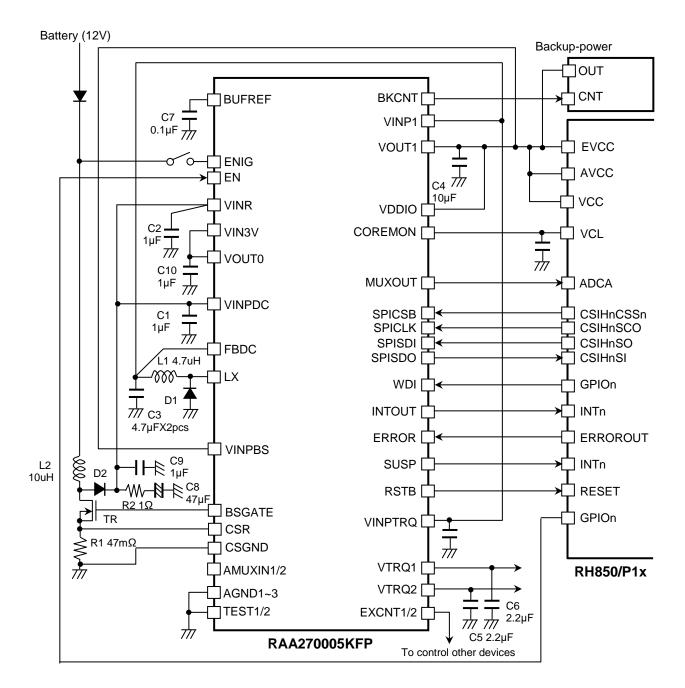

| 5. | Application   | Example                               | 71 |

|    | 5.1. Layout   | guide lines                           | 73 |

| 6. | Electrical C  | haracteristics                        | 74 |

|    | 6.1. Recom    | mended operating condition            | 74 |

|    | 6.2. Electric | cal characteristics                   | 74 |

|    | 6.2.1. D      | C characteristics                     | 74 |

| 7. | Package In    | formation                             | 75 |

# 1. Abusolute maximum ratings

| Item                                    | Comment                            | Min                   | Max              | unit |

|-----------------------------------------|------------------------------------|-----------------------|------------------|------|

| VINR, VINPDC                            | Battery                            | -0.3                  | 28 Note3         | V    |

| VIN3V                                   | Supply power for internal circuits | -0.3                  | 19               | V    |

| VDDIO, VINPBS                           | Supply power for PMIC, I/O         | -0.3                  | 6.5              | V    |

| VINP1, VINPTRQ                          | Regulator input                    | -0.3                  | 19               | V    |

| AGND1~3                                 | Ground                             | -0.3                  | 0.3              | V    |

| LX                                      |                                    | -1.0 <sup>Note2</sup> | VINPDC+0.3 Note6 | V    |

| FBDC                                    | Feedback pin for DCDC              | -0.3                  | 19               | V    |

| BSGATE                                  |                                    | -0.3                  | VINPBS+0.3 Note5 | V    |

| ENIG                                    |                                    | -0.3                  | VINR+0.3 Note6   | V    |

| AMUXIN1/2                               |                                    | -0.3                  | VINR+0.3 Note4   | V    |

| VOUT0                                   | LDO0 output                        | -0.3                  | VINR+0.3 Note4   | V    |

| VTRQ1/2                                 | TRACK1/2 output                    | -0.3                  | 19               | V    |

| VOUT1                                   | LDO1 output                        | -0.3                  | 6.5              | V    |

| MUXOUT, BUFREF                          |                                    | -0.3                  | VOUT1+0.3 Note5  | V    |

| COREMON                                 |                                    | -0.3                  | 6.5              | V    |

| BKCNT, CSGND, CSR                       |                                    | -0.3                  | VIN3V+0.3 Note5  | V    |

| ERROR, WDI                              | Digital input pins                 | -0.3                  | 6.5              | V    |

| EN, SPICSB, SPICLK,<br>SPISDI           | Digital input pins                 | -0.3                  | VDDIO+0.3 Note5  | V    |

| EXCNT1/2, SPISDO, SUSP,<br>INTOUT, RSTB | Digital output pins                | -0.3                  | VDDIO+0.3 Note5  | V    |

| TEST1/2                                 |                                    | -0.3                  | VIN3V+0.3 Note5  | V    |

|                                         | Junction to ambient                |                       | 0.2 Note7        |      |

| Thermal resistance (Typical)            | Junction to case (Top)             | 3:                    | 3.3 Note7        | °C/W |

|                                         | Junction to case (Bottom)          | 1.                    | 03 Note7         |      |

| Junction Temperature Note8              |                                    | -40                   | 150              | °C   |

| Storage Temperature Range               |                                    | -55                   | 150              | °C   |

**Notes 1.** Stress beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device liability and lifetime.

- 2. Not allowed to apply continuous voltage.

- 3. Maximum voltage is 40V under load dump condition. (Duration time is 400ms.)

- **4.** Must be 19V or lower.

- **5.** Must be 6.5V or lower.

- 6. Must be 28V or lower.

- 7. Simulation value based on JEDEC-2S2P condition.

- 8. The PMIC includes over temperature protection that is intended to protect the device during momentary over load condition. Junction temperature will exceed the maximum operating junction temperature when over temperature is achieved. Continuous operating above specified maximum operating junction temperature may impair device reliability.

# 2. Pin Configuration

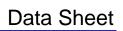

# 2.1. Pin Configuration

Pin configuration is shown in the below figure. The package is 40pin exposed die pad HLQFP.

Figure 2-1 Pin configuration (Top view)

# 2.2. Pin list

The pin list table is shown below.

|       |          |                                              | /201000 |         | lotorfo.co | Protec   | Protect circuit |                             |

|-------|----------|----------------------------------------------|---------|---------|------------|----------|-----------------|-----------------------------|

| Pin # | Pin name | Pin function                                 | Digital | I/O/P/G | level      | VDD name | GND name        | Remarks                     |

| 1     | BKCNT    | Backup-power control                         | Digital | Output  | CMOS       | VIN3V    | AGND1           |                             |

| 2     | AMUXIN1  | Analog multiplexer input1                    | Analog  | Input   | -          | ·        | <b>AGND3</b>    |                             |

| 3     | TEST2    | For test                                     | -       |         | -          | VIN3V    | 10ND1           | Connect to Ground           |

| 4     | ENIG     | Power enable of the PMIC                     | Digital | Input   | SOMN       | VINR     | AGND1           | Included pull-down resistor |

| 5     | VINR     | Power supply for LDO0                        | -       | Power   | -          | ı        | 10ND1           | Connect to battery          |

| 9     | VINPDC   | Buck DCDC input                              |         | Power   | I          | I        | AGND1           | Connect to battery          |

| 7     | ГХ       | Driver output for an external inductor       | Analog  | Output  | I          | I        | AGND1           |                             |

| 8     | AGND1    | Ground                                       | -       | ı       | I          | ı        | -               |                             |

| 6     | FBDC     | Buck DCDC feed-back input                    | Analog  | Input   | I          | I        | AGND1           |                             |

| 10    | ERROR    | Monitoring input from MCU                    | Digital | Input   | I          | I        | AGND1           | Included pull-down resistor |

| 11    | EN       | Power enable of the PMIC                     | Digital | Input   | CMOS       | VDDIO    | AGND1           | Included pull-down resistor |

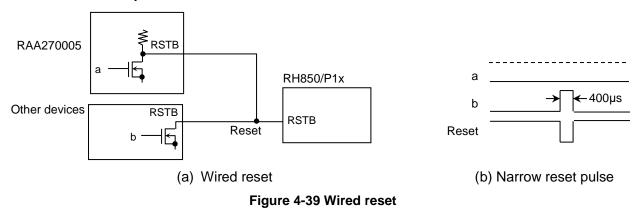

| 12    | RSTB     | Reset output                                 | Digital | Output  | Open drain | VDDIO    | AGND1           | Included pull-up resistor   |

| 13    | SPISDI   | Serial interface, data input                 | Digital | Input   | CMOS       | VDDIO    | AGND2           | Included pull-down resistor |

| 14    | SPICSB   | Serial interface, chip select                | Digital | Input   | CMOS       | VDDIO    | AGND2           | Included pull-up resistor   |

| 15    | SPICLK   | Serial interface, clock input                | Digital | Input   | CMOS       | VDDIO    | AGND2           | Included pull-down resistor |

| 16    | SPISDO   | Serial interface, data output                | Digital | Output  | CMOS       | VDDIO    | AGND2           |                             |

| 17    | VDDIO    | Power supply for digital IO part of the PMIC | T       | Power   | I          | ı        | <b>AGND2</b>    |                             |

| 18    | INTOUT   | Interrupt signal output                      | Digital | Output  | CMOS       | VDDIO    | AGND2           |                             |

| 19    | AGND2    | Ground                                       | T       | ı       | I          | ı        |                 |                             |

| 20    | COREMON  | Monitoring to a core voltage in MCU          | Analog  | Input   | ı          | I        | AGND2           |                             |

## Pin list (Continued)

| Dio<br># | Din name | Din function                          | Analog/ | 5/0/0/1 | Interface | Protect circuit | circuit  |                                       |

|----------|----------|---------------------------------------|---------|---------|-----------|-----------------|----------|---------------------------------------|

|          |          |                                       | Digital |         | level     | VDD name        | GND name |                                       |

| 21       | VINP1    | Power supply for LDO1                 | ·       | Power   | -         | I               | AGND2    | onur                                  |

| 22       | MDI      | Clear watch dog timer                 | Digital | Input   | CMOS      | I               | AGND2    | Included pull-down resistor           |

| 23       | SUSP     | Low voltage indicator of LDO1         | Digital | Output  | CMOS      | VDDIO           | AGND2    | /                                     |

| 24       | VOUT1    | LDO1 output                           | Analog  | Output  | -         | I               | AGND2    |                                       |

| 25       | MUXOUT   | Analog multiplexer output             | Analog  | Output  | -         | VOUT1           | AGND2    |                                       |

| 26       | VTRQ1    | TRACK1 output                         | Analog  | Output  | -         | I               | AGND2    |                                       |

| 27       | VINPTRQ  | Power supply for TRACK2               | I       | Power   | -         | I               | AGND2    |                                       |

| 28       | AMUXIN2  | Analog multiplexer input2             | Analog  | Input   | -         | I               | AGND3    |                                       |

| 29       | VTRQ2    | TRACK2 output                         | Analog  | Output  | -         | I               | AGND2    |                                       |

| 30       | BUFREF   | Reference voltage output              | Analog  | Output  | -         | I               | AGND2    | Connect to 0.1µF                      |

| 31       | EXCNT1   | Specified digital output1             | Digital | Output  | CMOS      | VDDIO           | AGND3    |                                       |

| 32       | EXCNT2   | Specified digital output2             | Digital | Output  | CMOS      | VDDIO           | AGND3    |                                       |

| 33       | VINPBS   | Power supply for boost DCDC           | I       | Power   | -         | I               | AGND3    |                                       |

| 34       | CSGND    | Current detection1 for boost DCDC     | Analog  | Input   | -         | I               | AGND3    | Detection resistor, low voltage side  |

| 35       | CSR      | Current detection2 for boost DCDC     | Analog  | Input   | -         | I               | AGND3    | Detection resistor, high voltage side |

| 36       | AGND3    | Ground                                | I       | I       | -         | I               | L        |                                       |

| 37       | BSGATE   | Boost switching control               | Analog  | Output  | -         | VINPBS          | AGND3    | External transistor control           |

| 38       | TEST1    | For test                              | I       | I       | -         | VIN3V           | AGND1    | Connect to ground                     |

| 39       | VIN3V    | Power supply for the internal circuit | I       | Power   | -         | I               | AGND3    |                                       |

| 40       | VOUT0    | LDO0 output                           | Analog  | Output  | ·         | VINR            | AGND3    |                                       |

|          |          |                                       |         |         |           |                 |          |                                       |

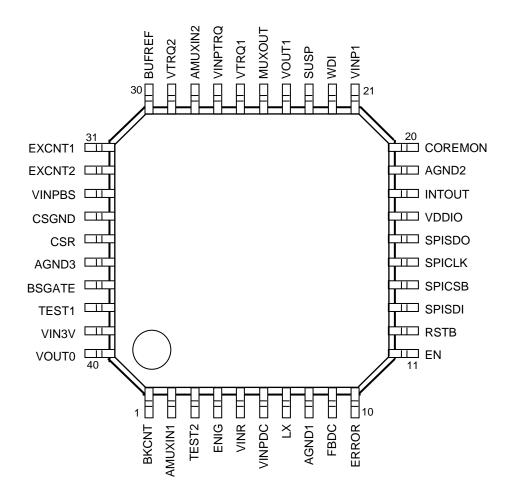

# 3. Internal Block Diagram

The PMIC block diagram is shown in the below figure.

Figure 3-1 The PMIC block diagram

The abstractive descriptions are here. Refer to each section for more details.

Boost DCDC

Boost DCDC is a switching regulator which boost up to 6.0V, and the frequency is 420 kHz.

- LD00

- LDO0 is a low drop output regulator which generates 3.3V power. The output current ability is 10mA. **LDO1**

- LDO1 is a low drop output regulator which generates 5.0V power. The output current ability is 350mA.

TRACK1 is a voltage tracker. The output tracks a voltage applied on VOUT1. The current ability is 100mA.

TRACK2

TRACK1 is a voltage tracker. The output tracks a voltage applied on VOUT1. The current ability is 100mA.

Buck DCDC

Buck DCDC is a switching regulator which generates 6.1V, and the frequency is 2.1 MHz. The output current ability is 600mA.

Band gap reference (BGR)

BGRs generate reference voltages for each regulator.

VREF

VREF generates reference voltages for regulators. An external capacitor is necessary to reduce noise of LDO1.

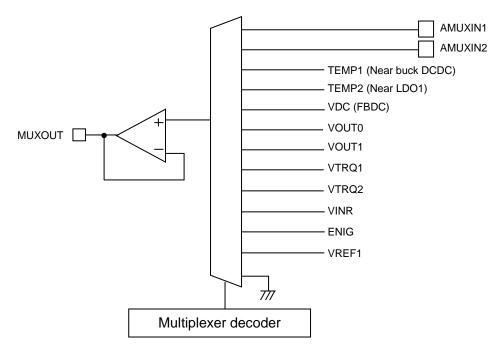

Analog multiplexer

An analog multiplexer outputs internal analog voltage of the PMIC or external pins (AMUXIN1/2).

SPI interface

SPI receives requests

SPI receives requests from MCU, or sends register setting.

Watch dog timer (WDT)

WDT monitors system operating, can be controlled by WDI pin or via SPI.

Sequencer

Sequencer controls power up/down of the regulators.

- Operation control

Operation control for the PMIC and external pins.

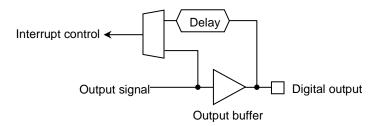

- Interrupt control Interrupt operation control.

- Interrupt operation of Oscillator

Oscillator for sequencer, buck DCDC and boost DCDC.

Thermal shutdown

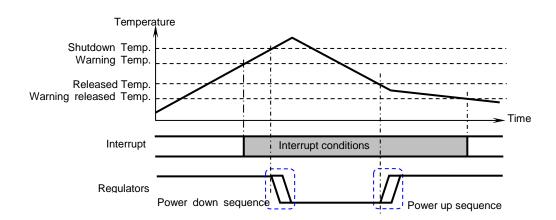

Thermal shutdown monitors the temperature in the PMIC. If the internal temperature exceeds the shutdown temperature, the PMIC goes to P/D sequence2.

Core voltage monitor

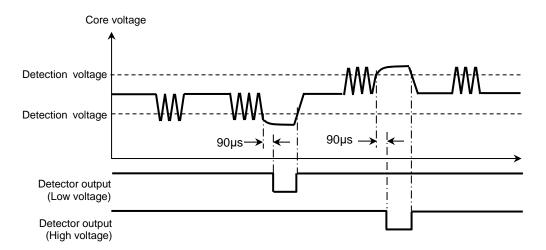

Core voltage monitor detects the under or over voltage of MCU's core voltage.

# 4. PMIC Function

# 4.1. Abstract of the PMIC

In order to supply power to MCU or ASIC, the PMIC contains current mode DCDC converters (DCDC) and two LDOs. The buck DCDC's output is used for LDO1's or trackers power source. When a battery voltage is applied to the PMIC, the regulators rise up automatically in accordance with designated sequence. And after all outputs of the regulators power up successfully, the "INTOUT" signal is released. The PMIC also has a watchdog timer (WDT). When timer in the WDT expires, a reset signal is occurred. The WDT is refreshed by a request via WDI pin or SPI.

When the junction temperature reaches over Tsd, a reset occurs and the all regulators except for LDO0 is forced to power down immediately

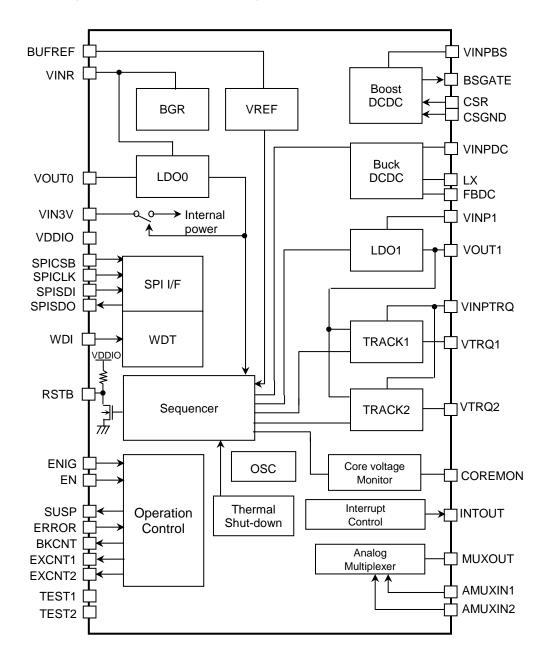

## 4.1.1. PMIC Operation

The principal operate transitions and conditions are illustrated in the below state diagram. ENIG or EN is enables operation of the PMIC.

Figure 4-1 State diagram

## Power down

In this state, no blocks in the PMIC operate.

Stand-by In this state, the PMIC executes initial reset of internal registers and RSTB pin is asserted low. Only LDO0 is activated by ENIG=1 operates in this state.

#### Self-diagnosis

Self-diagnostic automatically is started after stand-by state. In this state, over/low voltage detector in the regulators, the temperature sensor and the internal logic circuit are checked.

### P/U sequence

After executing self-diagnostic, this state is automatically entered. Even if one of regulators doesn't rise up, the PMIC stays in this state. After LDO1 rise up, INTOUT is high and passed 14.5ms, a reset is released.

### Normal

After the reset is released, this state is automatically entered. The system monitor is started with using the WD function. And also, the PMIC monitors the junction temperature and the output voltage of VOUT1.

### Reset1b

RSTB asserts low by setting low both ENIG and EN, or low voltage detection of VOUT1 immediately. **P/D sequence1**

This state is automatically entered after "Reset 1" state. Buck DCDC and LDO1 start to fall down in designated order. The junction temperature is checked. If the junction temperature is higher than Tsd, then the PMIC enters "Cool down" state. If lower than Trls, the PMIC enters back "Stand-by" state.

### Reset2

When the junction temperature comes over Tsd or the low voltage of core voltage is detected, the reset is released.

#### P/D sequence2

This state is automatically entered after "Reset2" state. Buck DCDC and LDO1 start to fall down in designated order. When ENIG or EN is set to high, the PMIC goes to "Cool down" state. When ENIG and EN are set to low, the PMIC goes to "Stand-by" state.

#### Cool down

The PMIC checks if the junction temperature is lower than Trls. If the junction temperature is higher than Tsd, the PMIC waits until the junction temperature cools down. After the junction temperature comes below Trls, the PMIC enters "Stand-by" state. When ENIG and EN are set to low, the PMIC also goes to "Stand-by" state.

## 4.1.2. Pin setting

The PMIC has ENIG and EN pin to define PMIC operation. For proper operation, these pins should be set to the appropriate level. The appropriate setting voltages are described in "6. Electrical Characteristics"

#### • PMIC enabling

The PMIC enabling is set by ENIG or EN pin. And in the initial phase, the PMIC should be enabled on by ENIG. ENIG pin can be connected to a battery voltage.

| Ia   |    | o operation setting |

|------|----|---------------------|

| ENIG | EN | PMIC operation      |

| 0    | 0  | PMIC disable        |

| 0    | 1  | PMIC enable         |

| 1    | 0  | PMIC enable         |

| 1    | 1  | PMIC enable         |

## Table 4-1 PMIC operation setting

## 4.1.3. Configuration register

In order to configure function of the PMIC, need to set in this register. Refer to each described section for more setting information.

Configuration register

The below registers are secured registers. Enter "key" code, before entering this request. (Refer to section 4.2.3.)

Address (CONF): 10H

|    |        | <i>J</i> OINI <i>J</i> . | 1011 |     |    |    |    |      | _      |       |

|----|--------|--------------------------|------|-----|----|----|----|------|--------|-------|

|    | A5     | A                        | 4    | A3  | A2 | 2  | A1 | A0   |        |       |

|    | 0      | 1                        |      | 0   | 0  |    | 0  | 0    |        |       |

| Re | gister |                          |      |     |    |    |    |      |        |       |

|    | D7     | D6                       | D5   | D   | )4 | D3 | D2 |      | D1     | D0    |

|    | -      | -                        | -    | RST | MD | -  | RS | TERR | SPIWDT | ADVWD |

Setting contents

| Pogiator po |     | Control contents               | Set | ting    |

|-------------|-----|--------------------------------|-----|---------|

| Register na | ame | Control contents               | 1   | 0       |

| RSTMD       | D4  | Reset mode                     | L   | Pulse * |

| RSTERR      | D2  | Reset assertion by ERROR       | On  | Off *   |

| SPIWDT      | D1  | Select WDT clear input channel | SPI | WDI *   |

| ADVWD       | D0  | Advanced mode for WD operating | On  | Off *   |

\* Default setting

**Note:** Advanced mode for WD is effective when SPI is selected to refresh WDT.

RSTMD: Reset mode select when a reset is occurred.

RSTERR: Reset control register by ERROR. After setting "On", RSTB asserts low when ERROR indicates error.

SPIWDT: select WDT clear input

ADVWD: This register can set to operate WDT in advanced mode. After setting "Enable", WD operates in advanced mode. Refer to section 4.8.3.

## 4.1.4. Product code

These bits identify the PMIC product code.

- Product code

- Address(CHIPID): 00H

|      | A5         | A4        | A3 | A2 | A1 | A0 |          |

|------|------------|-----------|----|----|----|----|----------|

|      | 0          | 0         | 0  | 0  | 0  | 0  |          |

| ■ Re | gister (Re | ead only) |    |    |    |    |          |

|      |            |           |    |    | DO | 50 | <b>_</b> |

| - | <u> </u> | <u> </u> |    |    |    |    |    |    |  |

|---|----------|----------|----|----|----|----|----|----|--|

|   | D7       | D6       | D5 | D4 | D3 | D2 | D1 | D0 |  |

|   | 1        | 0        | 0  | 0  | 0  | 0  | 1  | 0  |  |

## 4.2. Serial Interface

The PMIC includes serial to peripheral interface (SPI). Refer to each section for more detail contents,

- > WDT operation (If SPI control is selected)

- > Control the monitor function

- Reset control, read reset factor, write reset clear/mask

- > Interrupt control, read interrupt factor, write interrupt clear/mask

- Tracker control

- Change thermal detection

## 4.2.1. Signal format

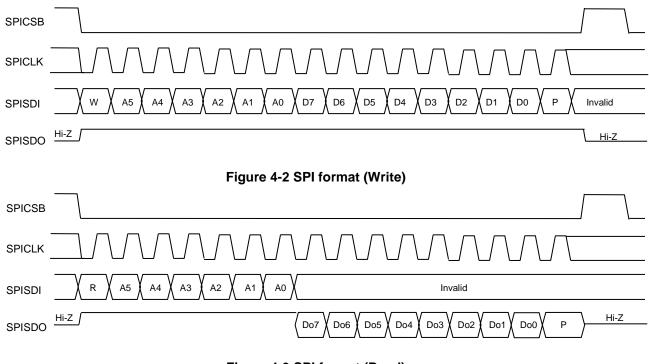

The bit length of the communication is 16bits, and the signal format is illustrated in below figures. The data should be transmitted as MSB first. For this SPI, one SPICSB active is for one request. Therefore, SPICSB should be high after transmitted data.

Figure 4-3 SPI format (Read)

Caution: The entered data is latched by rising edge of SPICSB.

## ♦ W/R

This bit indicates write or read register. To write register, bit W/R should be set 0. To read register, bit W/R should be set 1. When read register, Do7-Do0 bits indicate contents. (D7-D0 bits are ignored in the PMIC.)

A5-A0

The PMIC contains several registers. The addresses are described in these bits. Every register can be read to confirm its content.

♦ D7-D0

These bits describe control bits of the PMIC to write into the PMIC.

◆ Do7-Do0

These bits describe content bits or flag bits to read from the PMIC. SPISDO pin keeps Hi-z during transmitting "W/R" bit and address bits, A5-A0. The parity bit of read data is calculated with "W/R" bit and all address bits as 1.

**♦** P

This bit indicates a parity bit calculated based on the number of logic contained in bits excepting parity bit itself.

Bit P has to be set 0 if the number of 1 is odd. Bit P has to be set 1 if the number of 1 is even.

Note: If interrupt factors of the target address occurs during the interrupt factor reading, the parity bit might not be set correctly.

#### 4.2.2. Ensuring communication

To ensure the communication between the PMIC and MCU, the PMIC observes the SPI signal of following accesses. If any violation, The PMIC ignores this command or request.

Number of SPICLK

The PMIC counts SPICLK clocks while SPICSB is low. If the number of clock is not 16, that communication is considered as an error. The PMIC ignores this command or request.

Undefined address

When undefined address is transmitted, the PMIC ignores this address' contents.

Parity bit

The SPI format includes a parity bit. The PMIC monitors the parity bit and if transmitted bits are not based on the parity bit, this communication is considered as an error. The PMIC ignores this command or request.

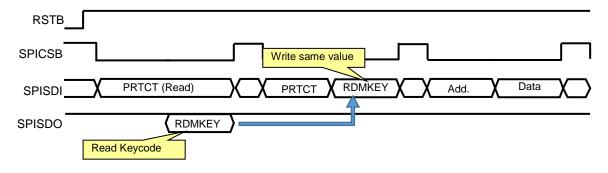

## 4.2.3. Secured request

A MCU read PRTCT register to get key and write it back to PRTCT register before modifying those secured registers, instead of writing the key to those secured registers. Without the key code, the request is ignored.

- ➢ Pin setting (Address: 02H)

- Interrupt mask register (Address: 0CH~0FH)

- Configuration register (Address: 10H)

- Reset mask register (Address: 14H)

- > Window time setting for WDT (Address: 17H)

- Tracker register (Address: 1AH)

- Buck DCDC protection setting (Address: 1BH)

- Software reset (Address: 1DH)

- > Temperature setting for the thermal shut down (Address: 1EH)

- Boost DCDC protection setting (Address: 1FH)

#### Figure 4-4 Key code unlock

## 4.2.4. Register

The contents of SPI setting are described in this section.

- Protect deactivate key code

- Address (PRTCT): 11H

| A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|

| 0  | 1  | 0  | 0  | 0  | 1  |

Register

Before the access secured registers, need to obtain the below random code by read mode.

|   | Do7       | Do6         | Do5       | Do4        | Do3      | Do2        | Do1   | Do0 |

|---|-----------|-------------|-----------|------------|----------|------------|-------|-----|

|   |           |             | F         | DMKEY      | (Do7:Do0 | ))         |       |     |

| N | eed to er | nter the ob | otained d | ata before | e MCU er | nters requ | iest. |     |

|   | D7        | D6          | D5        | D4         | D3       | D2         | D1    | D0  |

|   |           |             |           | RDMKEY     | (D7·D0)  |            |       |     |

- Setting contents

- RDMO (Do7:Do0): Random code from the PMIC

- RDMI (D7:D0): Copy and sent RDMO (Do7:Do0)

## 4.2.5. Register map

The registers which can be set in the PMIC are summarized in below table with its address and data. The detail contents are described in each section. Hexadecimal number is written as xxH.

|             |                  | ä         | ž            | 2                 | 2                     | 2               | δ               | ٤           | Initial | Controd | Reset | Eurofion                               |

|-------------|------------------|-----------|--------------|-------------------|-----------------------|-----------------|-----------------|-------------|---------|---------|-------|----------------------------------------|

|             | 2                | 5         | S            |                   | S                     | 77              | 5               | 3           | ווווומו | oecnied | by    | runcuon                                |

| r           |                  |           |              | CHIPIC            | CHIPID<7:0>           |                 |                 |             | 82H     |         |       | Chip ID                                |

| R/W         | 1                | I         | 1            |                   | SETEXCNT2             | SETEXCNT1       | SETSUSP         | SETBKCNT    | 02H     | 0       | RSTB  | Set / Read for digital output pins     |

| ۲           | 1                | I         | INTRSFG      | INTSD             | INTR4                 | INTR3           | INTR2           | INTR1       | HOO     |         | DET00 | Interrupt factor                       |

| ĸ           | DETTRQ2OC        | DETTRQ1OC | DETBSOC      | DETCOL            | DETTRO2L              | DETTRQ1L        | DET1L           | DETDCL      | HOO     |         | DET00 | Interrupt request 1                    |

| Я           | -                | 1         | DETCOU2      | DETCOU1           | DETTRQ2U              | DETTRQ1 U       | DET1U           | DETDCU      | H00     |         | DET00 | Interrupt request 2                    |

| ۲           | BKMODE           | SDBKUP    | SDSTA        | SDOSC             | BATBK                 | DETREF          | WRTMP           | DETDCOC     | HOO     |         | DET00 | Interrupt request 3                    |

| ۲           | DUMMY            | I         | 1            | PEXCNT2           | PEXCNT1               | PSUSP           | PBKCNT          | PRSTB       | HOO     |         | DET00 | Interrupt request 4                    |

| M           | CLTRQ2OC         | CLTRQ1OC  | CLBSOC       | CLCOL             | <b>CLTRQ2L</b>        | <b>CLTRQ1L</b>  | CL1L            | CLDCL       | •       |         | RSTB  | Interrupt clear 1                      |

| ×           | 1                | I         | CLCOU2       | CLCOU1            | <b>CLTRQ2U</b>        | CLTRQ1U         | CL1U            | CLDCU       | •       |         | RSTB  | Interrupt clear 2                      |

| N           | CLBKMODE         | CLBKUP    | CLSDSTA      | CLSDOSC           | CLBATBK               | CLREF           | CLWRTMP         | CLDCOC      | •       |         | RSTB  | Interrupt clear 3                      |

| M           | 1                | I         | 1            | <b>CLPEXCNT2</b>  | CLPEXCNT1             | CLPSUSP         | CLPBKCNT        | CLPRSTB     | •       |         | RSTB  | Interrupt clear 4                      |

| R/W N       | <b>MSKTRQ2OC</b> | MSKTRQ10C | MSKBSOC      | I                 | <b>MSKTRO2L</b>       | <b>MSKTRQ1L</b> | MSK1L           | MSKDCL      | H00     | 0       | RSTB  | Interrupt mask 1                       |

| INTMSK2 R/W | I                | 1         | MSKCOU2      | MSKCOU1           | <b>MSKTRQ2U</b>       | <b>MSKTRQ1U</b> | MSK1U           | MSKDCU      | HOO     | 0       | RSTB  | Interrupt mask 2                       |

| R/W         | 1                | 1         | MSKSDSTA     | MSKSDOSC          | 1                     | MSKREF          | MSKWRTMP        | MSKDCOC     | HOO     | 0       | RSTB  | Interrupt mask 3                       |

| R/W         | -                | 1         | -            | <b>MSKPEXCNT2</b> | MSKPEXCNT2 MSKPEXCNT1 | MSKPSUSP        | MSKPBKCNT       | MSKPRSTB    | H00     | 0       | RSTB  | Interrupt mask 4                       |

| R/W         | -                | 1         | 1            | RSTMD             | -                     | RSTERR          | LDWIdS          | ADVWD       | H00     | 0       | DET00 | Configuration register                 |

| R/W         |                  |           |              | RDMKE             | RDMKEY<7:0>           |                 |                 |             | H**     |         | RSTB  | Protect remove code                    |

| Я           |                  | STPERR    | OVADV        | LVCORE            | TSDTMP                | WDEXP           | SNSQM           | LVLD01      | H00     |         | DET00 | Reset factor                           |

| M           |                  | CLSTPERR  | CLOVADV      | CLLVCORE          | CLTSDTMP              | CLWDEXP         | CLWDSUS         | CLLVLD01    | •       |         | RSTB  | Reset factor clear                     |

| RSTFMSK R/W | 1                | I         | MSKOVADV     | I                 | MSKTSDTMP             | MSKWDEXP        | SUSDWASM        | 1           | H00     | 0       | RSTB  | Reset factor mask                      |

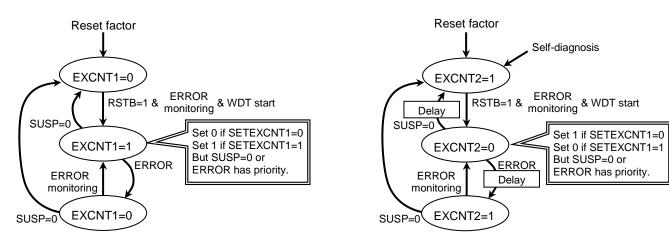

| R/W         | -                | 1         | DEXCNT2<1:0> | F2<1:0>           | -                     |                 | SELDT           | ERMODE      | HOO     |         | RSTB  | EXCNT and error monitor setting        |

| R/W         | OPE              | OPE<1:0>  |              |                   | SUBJ                  | SUBJ<5:0>       |                 |             | H**     |         | RSTB  | WD advanced mode                       |

| WDTIME R/W  | 1                | I         | I            | I                 | CWSE                  | CWSET<1:0>      | NILOM           | WDTIME<1:0> | 01H     | 0       | RSTB  | WD window time setting                 |

| R/W         | -                | MUXCNT    | 1            | I                 |                       | MUXSE           | MUXSEL<3:0>     |             | HOO     |         | RSTB  | Muxamp control                         |

| R           |                  |           |              | ACCVI             | ACCVA<7:0>            |                 |                 |             | HOO     |         | RSTB  | Accumulated value for WD advanced mode |

| TROCNT R/W  |                  | -         |              | TRQLVSEL          | -                     |                 | <b>VTRQ2CNT</b> | VTRQ1CNT    | 00H     | 0       | RSTB  | TRACK1/2 on/off control                |

| R/W         |                  | 1         | 1            | 1                 | INTIME                | INTIME<1:0>     | DTIME           | DTIME<1:0>  | 04H     | 0       | DET00 | Limit control for DCDC                 |

| R/W         |                  |           |              | SETV/             | SETVA<7:0>            |                 |                 |             | FFH     |         | RSTB  | Number of reset for WD advanced mode   |

| Μ.          |                  |           |              | RDMKEY<7:0>       | EY<7:0>               |                 |                 |             |         | 0       | RSTB  | Software reset                         |

| SENTMP R/W  | WARREL<1:0>      | :L<1:0>   | THREL<1:0>   | -<1:0>            | WARDE                 | WARDET<1:0>     |                 | -           | 94H     | 0       | DET00 | Thermal shutdown temperature           |

| R/W         | INTIMEBS<1:0>    | 3S<1:0>   | DTIMEBS<1:0> | S<1:0>            |                       |                 | -               | BSCNT       | 41H     | 0       | RSTB  | BOOST DCDC control                     |

Note: The initial value of PRTCT, WDTRG are undefined value.

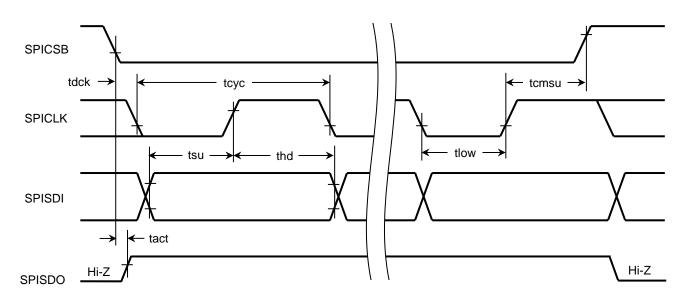

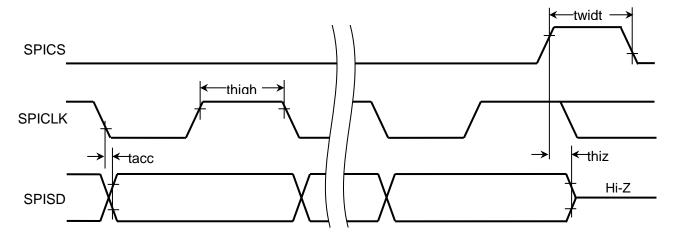

## 4.2.6. Electrical characteristics

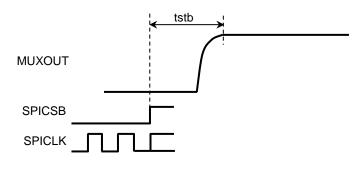

| Parameter           | Symbol | Conditions         | MIN  | TYP | MAX | Unit |

|---------------------|--------|--------------------|------|-----|-----|------|

| SPICLK delay        | tdck   | From SPICSB↓       | 400  | -   | -   | ns   |

| SPICLK period       | tcyc   |                    | 800  | -   | -   | ns   |

| H period of SPICLK  | thigh  |                    | 320  | -   | -   | ns   |

| L period of SPICLK  | tlow   |                    | 320  | -   | -   | ns   |

| Command set-up      | tcmsu  | From last SPICLK ↑ | 400  | -   | -   | ns   |

| Data set-up         | tsu    | Before SPICLK ↑    | 100  | -   | -   | ns   |

| Data hold           | thd    | After SPICLK ↑     | 100  | -   | -   | ns   |

| Data access time    | tacc   | From SPICLK ↓      | -    | -   | 50  | ns   |

| Read data Hi-Z time | thiz   |                    | -    | -   | 50  | ns   |

| Data active delay   | tact   | After SPICSB ↓     | -    | -   | 50  | ns   |

| H width of SPICSB   | twidth |                    | 2800 | -   | -   | ns   |

Figure 4-5 SPI write timing

Figure 4-6 SPI read timing

## 4.3. Reference Voltage

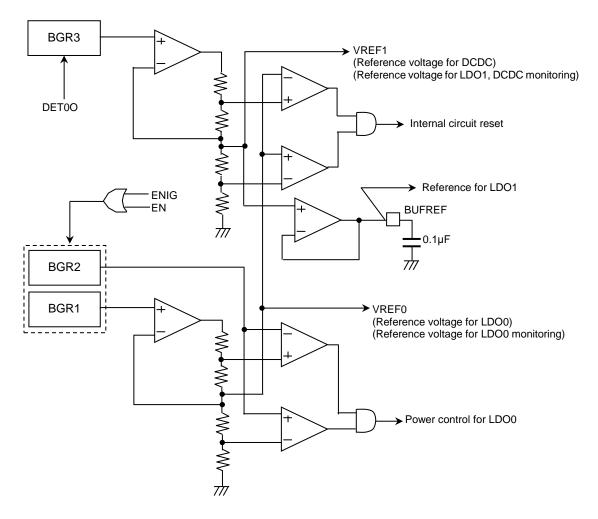

Below figure shows simplified reference voltage generator block.

Figure 4-7 REF block diagram

There are three Band Gap Reference (BGR) circuits in the PMIC. In Figure 4-7, if BGR1 or BGR2 has damage, the PMIC does not power up. If BGR3 suffers damage, LDO0 powers up and Buck DCDC and LDO1 does not power up.

BUFREF is the reference voltage for LDO1. In order to apply "clear" supply for ADC in MCU, 0.1µF capacitor is recommended to connect to ground.

## 4.3.1. Electrical characteristics

| Parameter             | Symbol | Conditions | MIN   | TYP   | MAX   | Unit |

|-----------------------|--------|------------|-------|-------|-------|------|

| BUFREF output voltage | VBUF   | BUREF      | 1.176 | 1.200 | 1.224 | V    |

## 4.4. LDO

The PMIC includes two LDOs. Each LDO requires a ceramic capacitor on its output. The gain stage of LDO1 is operated with 3.3V generated by LDO0. And LDO1 input of power stage has to be connected to the buck DCDC's output. These LDOs have a protection circuit with fold back characteristics (Refer to section 4.4.1).

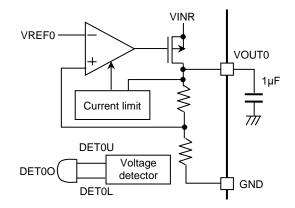

## ♦ LDO0

The LDO0 output should be used as power supply for internal circuit of the PMIC. The typical output voltage is 3.3V. The LDO0 output contains an output voltage detector.

When the over voltage is detected, the power line switch for internal circuit of the PMIC cut off supply power. Or when the low voltage is detected, The PMIC makes reset and initializes internal register. The detect voltages are described in section 4.12.4.

Figure 4-8 LDO0 block diagram

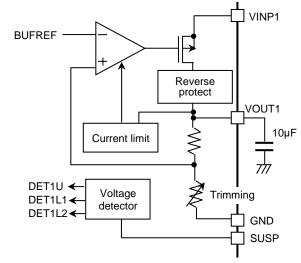

## ♦ LDO1

The LDO1 output should be used as power supply for MCU. The typical output voltage is 5.0V.

The LDO1 includes an output voltage detector. If the output voltage comes across the over voltage, a flag is set into register and INTOUT asserts low. When DET1L1 is detected, SUSP is asserted as the warning. And when DET1L2 is detected, RSTB is asserted. The detect voltages are described in section 4.12.4.

Figure 4-9 LDO1 block diagram

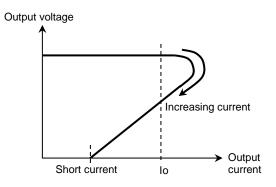

## 4.4.1. Output protection function

All LDOs have a current limit function. Fold-back characteristic is illustrated in Figure 4-10. In this figure, "lo" is a guaranteed current which maintains the specified output voltage. For more than "lo" current, the more output current flows, the lower output voltage goes down with decreasing output current

Figure 4-10 Fold-back characteristic

## 4.4.2. Electrical characteristics

Characteristics noted under conditions GND=0V, unless otherwise noted. The TYP condition is Ta=25°C.

### ♦ LDO0

C0=1.0µF (ESR=0~0.1Ω)

| Parameter      | Symbol | Conditions     | MIN  | TYP  | MAX  | Unit |

|----------------|--------|----------------|------|------|------|------|

| Output voltage | Vo0    | lo=0~10mA (DC) | 3.20 | 3.30 | 3.40 | V    |

| Short current  | ls0    | Vo=0V          | -    | -    | 20   | mA   |

**Note:** "(DC)" means not to include AC factor like transient response.

## ♦ LDO1

C1=10µF (ESR=0~0.1Ω), VDC~VINP1 connected

|                | <i>[!</i> |                                  |      |      |      |      |

|----------------|-----------|----------------------------------|------|------|------|------|

| Parameter      | Symbol    | Conditions                       | MIN  | TYP  | MAX  | Unit |

|                | Vo11      | VINPDC>5.75V,<br>Io=0~350mA (DC) | 4.90 | 5.00 | 5.10 | V    |

| Output voltage | Vo12 *    | VINPDC=5.4V, Io=300mA (DC)       | 4.75 | -    | -    | V    |

|                | Vo13 *    | VINPDC=3.8V, Io=300mA (DC)       | 3.20 | -    | -    | V    |

| Short current  | ls1       | Vo=0V                            | -    | -    | 100  | mA   |

**Note:** "(DC)" means not to include AC factor like transient response.

\*: Guaranteed by Design Engineering

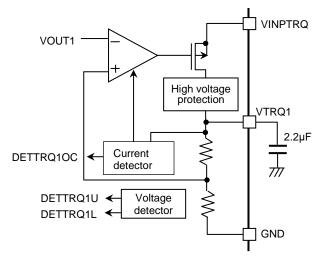

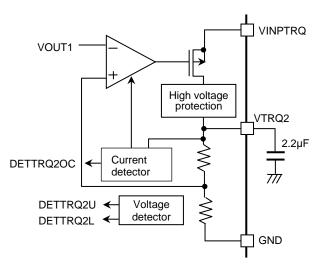

## 4.5. Tracker

The PMIC includes two trackers. Each tracker needs a ceramic capacitor on its output. The buffer on the tracker is operated by 3.3V generated at the LDO0. And each input of power stage has to be connected to buck DCDC's output. Set VTRQ1CNT1 or VTRQ2CNT to 1 to activate the trackers.

## ♦ TRACK1

TRACK1 is an auxiliary power rail. This output voltage follows to VOUT1. The power up control is set via SPI. This tracker has high voltage protect function to prevent reverse current from the output. When the output touch high voltage like battery, this circuit stops reverse current toward the PMIC. TRACK1 has a voltage/current detector which assert INTOUT to low, if the over/low voltage or over current is detected. The detect voltages are described in section 4.12.4.

Figure 4-11 TRACK1 block diagram

Figure 4-12 TRACK2 block diagram

## ♦ TRACK2

TRACK2 is an auxiliary power rail. This output voltage follows to VOUT1. The power up control is set via SPI. This tracker has high voltage protect function to prevent reverse current from the output. When the output touch high voltage like battery, this circuit stops reverse current toward the PMIC. TRACK2 has a voltage/current detector which assert INTOUT to low, if the over/low voltage or over current is detected. The detect voltages are described in section 4.12.4.

## Caution:

If over current or low voltage is detected, the tracker is suspended for the protection. The VTRQ1CNT or VTRQ2CNT register set 0 once, and then set 1 to reboot the tracker.

Not allow to add over  $20\mu$ F in addition to  $2.2\mu$ F in Figure 4-11 and Figure 4-12.

## 4.5.1. Register

The content of TRACK1/2 setting controls output and changes low voltage detection.

## TRACK1/2 setting

The below registers are secured registers. Enter "key" code, before entering this request. (Refer to section 4.2.3.)

Address (TRQCNT): 1AH

| - /  |        |    | ., |    |    |    |

|------|--------|----|----|----|----|----|

|      | A5     | A4 | A3 | A2 | A1 | A0 |

|      | 0      | 1  | 1  | 0  | 1  | 0  |

| ■ Re | gister |    |    |    |    |    |

|      |        |    |    |    |    |    |

| D7 | D6 | D5 | D4       | D3 | D2 | D1       | D0       |

|----|----|----|----------|----|----|----------|----------|

| -  | -  | -  | TRQLVSEL | -  | -  | VTRQ2CNT | VTRQ1CNT |

Setting contents

| Pogietor po | ma | Control contents                  | Set   | ting    |

|-------------|----|-----------------------------------|-------|---------|

| Register na | me | Control contents                  | 1     | 0       |

| TRQLVSEL    | D4 | Low voltage detection on TRACK1/2 | 92.5% | 48.6% * |

| VTRQ2CNT    | D1 | TRACK2 On/Off                     | On    | Off *   |

| VTRQ1CNT    | D0 | TRACK1 On/Off                     | On    | Off *   |

\* Default setting

**Note:** Set TRQLSEL before start-up. TRQLVSEL changes both TRACK1 and TRACK2 low voltage detection.

## 4.5.2. Electrical characteristics

Characteristics noted under conditions GND=0V, unless otherwise noted. The TYP condition is Ta=25°C.

## ♦ TRACK1

CTRQ1=2.2μF (ESR=0~0.1Ω)

| Parameter             | Symbol   | Conditions  | MIN | TYP | MAX | Unit |

|-----------------------|----------|-------------|-----|-----|-----|------|

| Matching output error | dVTR1    | VTRQ1-VOUT1 | -20 | -   | 20  | mV   |

| Output current        | lotr11   |             | 100 | -   | -   | mA   |

| Power on time         | Trtrq1 * | 90% output  | -   | 1.8 | 2.4 | ms   |

\*: Guaranteed by Design Engineering

## ♦ TRACK2

CTRQ2=2.2μF (ESR=0~0.1Ω)

| Parameter             | Symbol   | Conditions  | MIN | TYP | MAX | Unit |

|-----------------------|----------|-------------|-----|-----|-----|------|

| Matching output error | dVTR2    | VTRQ2-VOUT1 | -10 | -   | 10  | mV   |

| Output current        | lotr2    |             | 100 | -   | -   | mA   |

| Power on time         | Trtrq2 * | 90% output  | -   | 1.8 | 2.4 | ms   |

\*: Guaranteed by Design Engineering

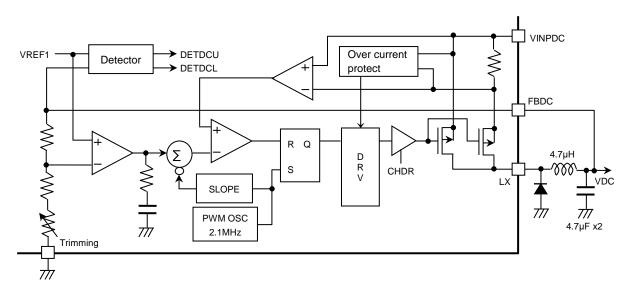

## 4.6. DCDC converter (DCDC)

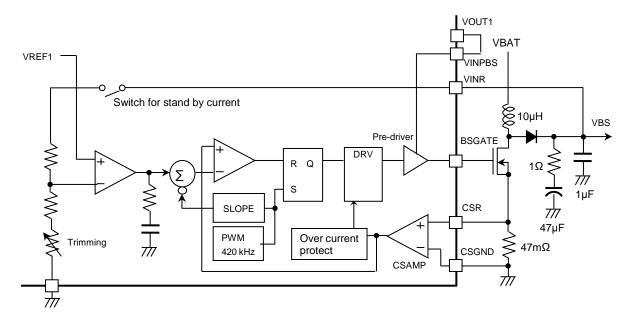

The PMIC includes two types of DCDCs: buck and boost. The internal high-side PMOS power stage is implemented in the buck DCDC. The buck DCDC requires some external device in Figure 4-13. The boost DCDC operates down to 2.2V battery voltage (VBAT) by configuration in Figure 4-16 and that output connects to the input of the buck DCDC. The buck DCDC has output monitoring which protect the DCDC output and the over-current by a detector monitoring the over and low voltage.

## 4.6.1. Buck DCDC

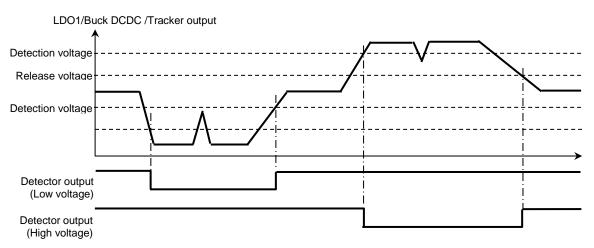

The buck DCDC operates with current mode control and is supposed to supply power as intermediate power supply. LDO1 and trackers input should be connected to the buck DCDC's output. The buck DCDC includes an output voltage detector. If the output voltage comes across over or low voltage, the flag is set into register and INTOUT signal is occurred. The detect voltage is described in section 4.12.4.

Figure 4-13 Buck DCDC block diagram

## Buck DCDC output protect function

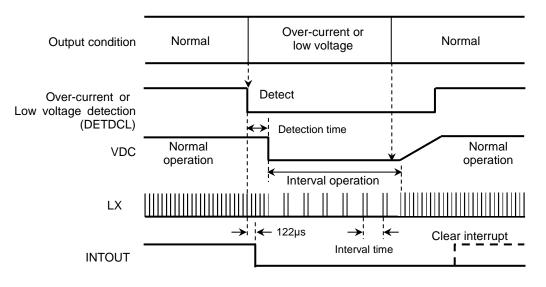

The buck DCDC monitors the output current and output voltage. In the case that over voltage is detected on the buck DCDC, the PMIC stops the buck DCDC's switching. When over current or low voltage are detected with taking over detection time, then the buck DCDC enters the interval operation. The detection time of over current and the interval time of resuming can be set via SPI.

Before the buck DCDC's operation comes into the protect mode, INTOUT is asserted low. The operation timing is shown in Figure 4-14 and Figure 4-15.

Figure 4-14 Buck DCDC protect function behavior 1

Figure 4-15 Buck DCDC protect function behavior 2

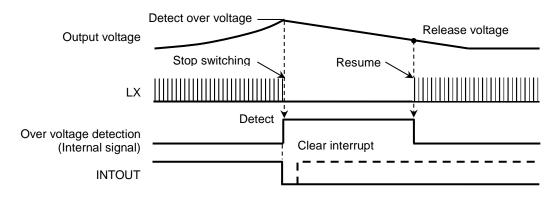

### 4.6.2. Boost DCDC

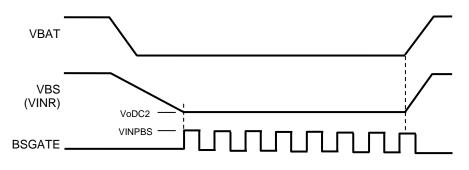

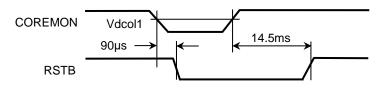

The PMIC operates without a reset signal until the input voltage (VBAT) is down to Vdbu. The boost DCDC should be operated in the lower VBAT voltage to maintain the PMIC function. Some external devices shown in Figure 4-16 is required for the boost operation. The output of the boost DCDC (VBS) is connected to the input of the buck DCDC (VINPDC) or LDO0 (VINR) and BSCNT is set to 1. the boost DCDC is activated when the VBAT is lower after starting up the PMIC.

The timing chart in the boost operation is shown in Figure 4-17.

The VBAT is same voltage to the VINR in the normal. The boost DCDC is enabled when the VINR voltage is lower than VoDC2. The VBAT returns to the normal, then the boost DCDC is suspended.

Figure 4-17 Timing chart (boost DCDC)

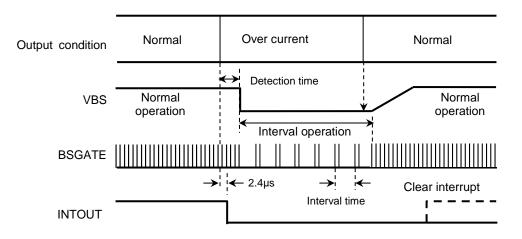

## Boost DCDC output protect function

The boost DCDC stops the switching when over current is detected though a resister both CSR and CSGND, moves the interval operation. The PMIC goes to the power down state and stops the buck DCDC and LDO1 if VBS(VINR) is under Vdbu after over current detecting.

The detection time of over current and the interval time of resuming can be set via SPI.

Before the boost DCDC's operation comes into the protect mode, INTOUT is asserted low. The operation timing is shown in Figure 4-18.

Figure 4-18 boost DCDC protect function behavior

## 4.6.3. Register

The contents of protect function setting are described here.

Buck DCDC protection mode setting

The below registers are secured registers. Enter "key" code, before entering this request. (Refer to section 4.2.3.)

■ Address(DCLIM): 1BH

| - //0 |        | <u>Envij. i Di</u> |    |    |       |         |      |         |

|-------|--------|--------------------|----|----|-------|---------|------|---------|

|       | A5     | A4                 | A3 | A2 | A1    | A0      |      |         |

|       | 0      | 1                  | 1  | 0  | 1     | 1       |      |         |

| ■ Re  | gister |                    |    |    |       |         |      |         |

|       | D7     | D6                 | D5 | D4 | D3    | D2      | D1   | D0      |

|       | -      | -                  | -  | -  | INTIM | E (1:0) | DTIM | E (1:0) |

Setting contents

Interval time and over current detection time for the buck DCDC

| INTIN | 1E (1:0) | Interval time |

|-------|----------|---------------|

| D3    | D2       | intervar time |

| 0     | 0        | 15.6ms        |

| 0     | 1        | 31.2ms *      |

| 1     | 0        | 124.9ms       |

| 1     | 1        | 249.9ms       |

| DTIM | E (1:0) | Detection time |

|------|---------|----------------|

| D1   | D0      | Detection time |

| 0    | 0       | 122µs *        |

| 0    | 1       | 122µs          |

| 1    | 0       | 610µs          |

| 1    | 1       | 1098µs         |

\* Default setting

\* Default setting

Note: INTOUT is low in 122µs regardless of DTIME.

### Boost DCDC protection mode setting

The below registers are secured registers. Enter "key" code, before entering this request. (Refer to section 4.2.3.)

■ Address(BSSET): 1FH

| Au | ness(DO | <u>oli i). II i</u> |       |          |    |    |    |       |

|----|---------|---------------------|-------|----------|----|----|----|-------|

|    | A5      | A4                  | A3    | A2       | A1 | A0 |    |       |

|    | 0       | 1                   | 1     | 1        | 1  | 1  |    |       |

| Re | gister  |                     |       |          |    |    |    | _     |

|    | D7      | D6                  | D5    | D4       | D3 | D2 | D1 | D0    |

|    | INTIME  | BS (1:0)            | DTIME | BS (1:0) | -  | -  | -  | BSCNT |

## Setting contents

Interval time and over current detection time for the boost DCDC

| INTIME | BS (1:0) | Interval time     |

|--------|----------|-------------------|

| D7     | D6       | Interval time     |

| 0      | 0        | 4.8µs             |

| 0      | 1        | 11.9µs *          |

| 1      | 0        | 312.1ms           |

| 1      | 1        | 624.2ms           |

|        |          | * Default cotting |

| DTIN | /IEE | 3S (1:0) | Detection time |  |  |  |  |

|------|------|----------|----------------|--|--|--|--|

| D5   |      | D4       | Detection time |  |  |  |  |

| 0    |      | 0        | 2.4µs *        |  |  |  |  |

| 0    |      | 1        | 2.4µs          |  |  |  |  |

| 1    |      | 0        | 11.9µs         |  |  |  |  |

| 1    |      | 1        | 2440µs         |  |  |  |  |

Default setting

\* Default setting

| Degister   |      | Control contents  | Setting  |                  |    |  |

|------------|------|-------------------|----------|------------------|----|--|

| Register n | lame | Control contents  | 1        | 0                |    |  |

| BSCNT      | D0   | Boost DCDC enable | Enable * | Disable          |    |  |

|            |      |                   |          | * Default settin | ١g |  |

**Note:** INTOUT is low in 2.4µs regardless of DTIMEBS.

## 4.6.4. Electrical characteristics

Characteristics noted under conditions GND=0V, unless otherwise noted. The TYP condition is Ta=25°C.

#### Buck DCDC

Co=4.7μF x2 (ESR=0.0~0.1Ω), L=4.7μH

| Parameter      | Symbol | Conditions      | MIN  | TYP  | MAX  | Unit |

|----------------|--------|-----------------|------|------|------|------|

| Output voltage | VoDC1  | lo=0~600mA (DC) | 5.90 | 6.10 | 6.30 | V    |

| OSC frequency  | Fosc1  |                 | 1890 | 2100 | 2310 | kHz  |

|                |        |                 |      |      | -    |      |

**Note:** "(DC)" means not to include AC factor like transient response.

#### Boost DCDC

Co=47 $\mu$ F (electrolytic capacitor, ESR=0.01~6 $\Omega$ ) + 1.0 $\mu$ F (ESR=0.0~0.1 $\Omega$ ), L=10 $\mu$ H

| Г | Parameter      | Symbol | Conditions                   | MIN  | TYP  | MAX  | Unit |

|---|----------------|--------|------------------------------|------|------|------|------|

|   | Output voltage | VoDC2  | VBAT=2.2V,<br>lo=0~250mA(DC) | 5.70 | 6.00 | 6.40 | V    |

|   | OSC frequency  | Fosc2  |                              | 378  | 420  | 462  | kHz  |

**Note:** "(DC)" means not to include AC factor like transient response.

## 4.7. Power Rail Sequence

When the battery voltage is applied to the PMIC, the LDO0 rises up first. After the LDO0 rises up, the buck DCDC and LDO1 are powered up in the sequence automatically. After LDO1 rises up, reset signal is released.

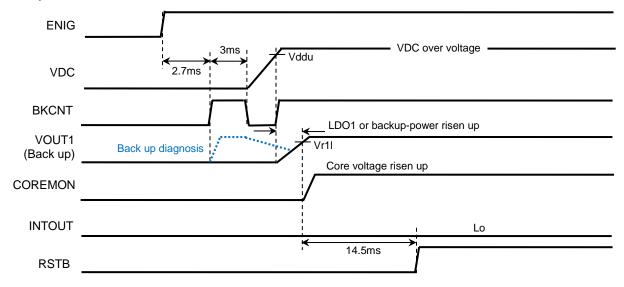

## 4.7.1. Power up sequence

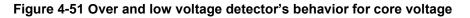

After the PMIC is applied supply voltage, the buck DCDC(VDC) and VOUT1 rise up automatically. If a back-up supply is connected, the PMIC powers up the back-up supply once to detect it after self-diagnosis. The rise up timing of VOUT1, INTOUT and RSTB are suitable for RENESAS RH850/P1x.

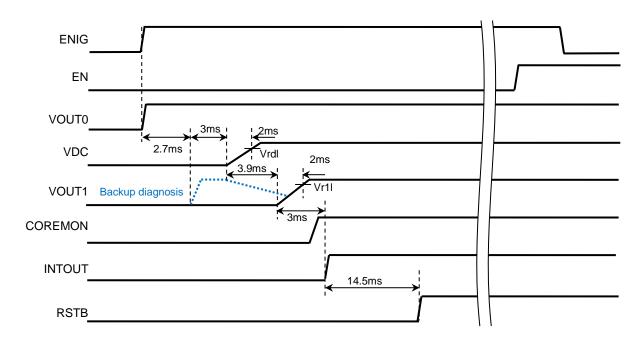

### • Power up with ENIG

While the supply voltage is applied, the PMIC can be controlled by ENIG pin. After ENIG is entered, the self-diagnosis is executed. The buck DCDC and LDO1 are controlled by the internal sequencer. After VOUT1 rises up, the interrupt signal is released. Further 14.5ms passes, the reset signal is released as well. INTOUT is asserted high even if a core voltage (VCL) in MCU is not activated. The PMIC keep the operation by asserted EN high from MCU, if ENIG is low.

Figure 4-19 Power up timing (with ENIG setting)

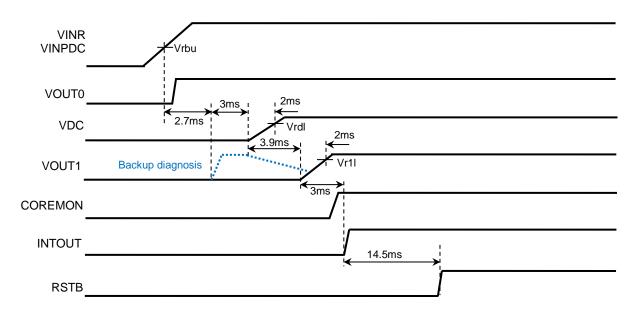

### Power up without ENIG

When ENIG are connected to the supply voltage and the supply voltage comes up, the power up sequence starts automatically. The power up sequence behavior is same as using ENIG. INTOUT is asserted high even if a core voltage (VCL) in MCU is not activated.

Figure 4-20 Power up timing (Supply power coming up)

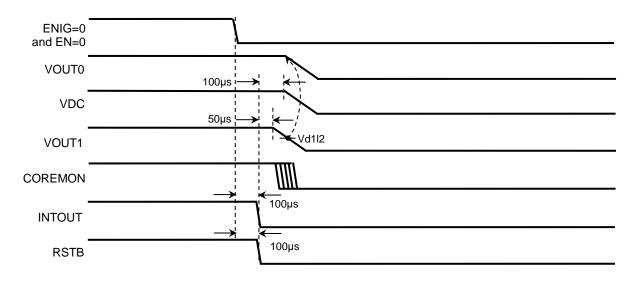

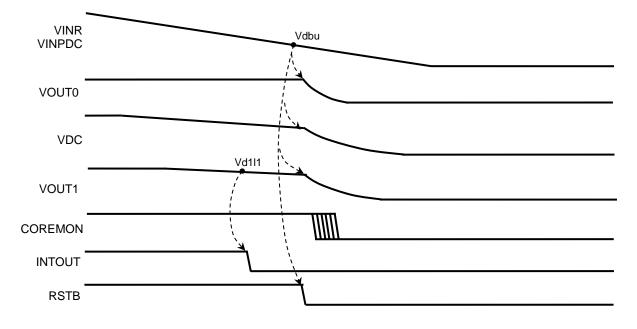

### 4.7.2. Power down sequence

When the PMIC powers down, all regulators fall down automatically. The difference of fall down time between each regulator is suitable for RENESAS RH850/P1x.

The PMIC is not re-activated without the low voltage detection (Vd1I2) in the LDO1 after the power down sequence.

#### • Power down with ENIG

When the PMIC is stopped operating by ENIG, the power down sequence is started by asserted ENIG and EN low. After INTOUT and RSTB is low, the LDO1 or the buck DCDC is powered down. The LDO0 is powered down after VOUT1 detects Vd1l2.

### ♦ Power down without ENIG, EN

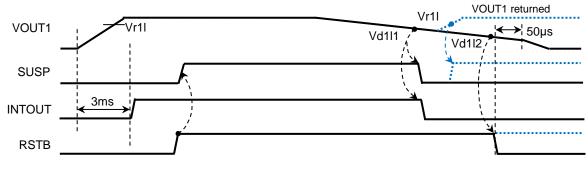

The output behavior in low supply voltage is shown in the below figure. Even though the supply voltage of the PMIC goes down lower than the output voltage of the buck DCDC, regulators can generate the output voltage. But the output voltage becomes to be almost same as the supply voltage.

When the supply voltage falls down and VOUT1 goes across Vd1I1, the PMIC asserts that INTOUT is low. Further the supply voltage goes across Vdbu or VOUT1 goes across Vd1I2, the PMIC asserts that RSTB is low.

Figure 4-22 Power down timing (Supply voltage falling down)

## Power down by low voltage of VOUT1

When VOUT1 goes across Vd1l2, the PMIC asserts that RSTB is low and moves to the power down sequence. The PMIC turns off the LDO1 and the buck DCDC.

Figure 4-23 Power down timing (VOUT1 low voltage detection)

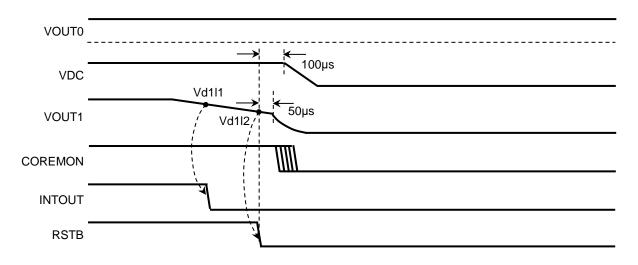

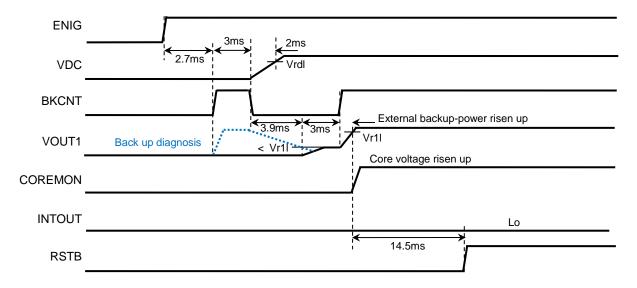

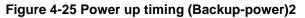

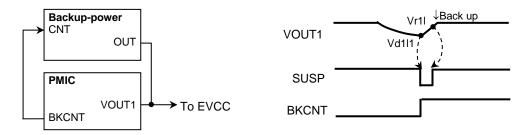

## 4.7.3. Working with a backup-power

If the buck DCDC or LDO1 is in unusual operation, the backup is powered up.

#### Buck DCDC unusual operation

When the buck DCDC detects over, low voltage or over current, the backup-power is risen up instead of the LDO1 if the PMIC is connected with the backup-power. If no back up, the LDO1 is risen up. Even DCDC goes back to the normal operation, the backup-power is operated until the operation mode is the stand-by.

Figure 4-24 Power up timing (Backup-power)1

#### ♦ LDO1 low voltage

If the low voltage is detected on LDO1 during the PMIC starting up, the backup-power is risen up and LDO1 is suspended. The backup-power is operated until the operation mode is the stand-by.

## ♦ Backup-power power down

The backup-power executes power down sequence.

Figure 4-26 Power down timing (Back up suppy)

# 4.8. Watchdog Timer (WDT)

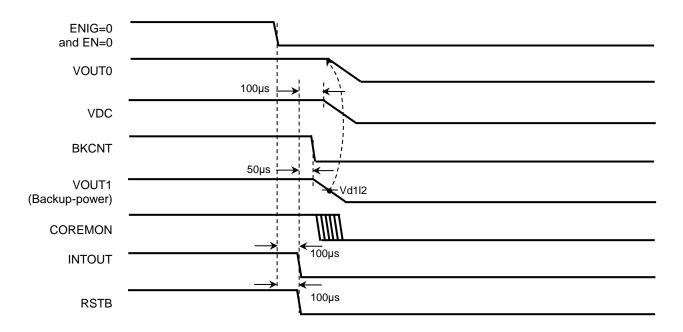

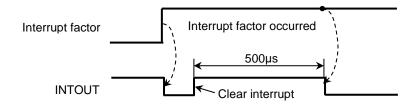

The watchdog (WD) timer can be used for monitoring the system health to prevent a runaway operation. In order to refresh WD timer (WDT), a trigger via SPI or on WDI pin is required.

## 4.8.1. Window WDT

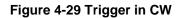

The window WDT is implemented in the PMIC. A trigger is required to start the WD operation during first window (FW) in "Normal" state. If the trigger is not executed, a reset pulse is occurred and the PMIC waits for a FW trigger again. After WD starts operating in "System monitor" state, a trigger should not be executed during Close Window (CW). A trigger should be executed to refresh the timer during Open window (OW). If the refreshing is not executed within designated time in OW, a reset pulse occurs. While the WDT is operating and when SUSP is asserted, the WDT stops its operating. And when SUSP is released, then the WDT resumes FW in "Normal" state.

The CW time and the OW time are programmed via SPI.

## 4.8.2. WDT operation

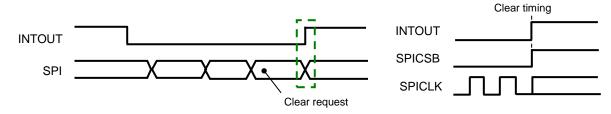

The detail WD operation is described in this section. In order to clear the timer, toggling on WDI or SPI is required.

### Operation in normal

The below figure shows the normal operation of WDT when the trigger from WDI pin or SPI is entered within designated time. The certified point as a trigger is the both edge of WDI or rising edge of SPICSB. In SPI mode, the parity bit should be set to the correct data to be checked by the PMIC even though any data can be written into WD trigger address(WDTRG).

Figure 4-27 WDT normal operation

## • Behaviors in unusual operation

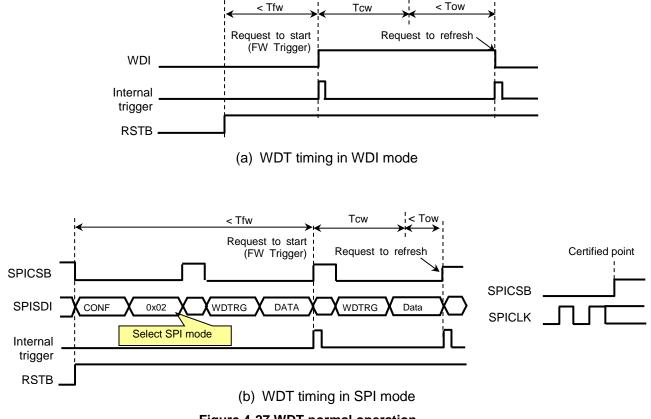

A reset is occurred when the trigger in CW or when the OW timer expires.

(1) No trigger in FW

When the trigger is not entered in FW, a reset is occurred. After that, if no triggers are entered, a reset is occurred frequently on the periodic interval. If RSTMD register is set to 1, RSTB maintains low (the reset is low after the PMIC's restart through stand-by state in the PMIC.).

Figure 4-28 No trigger in FW

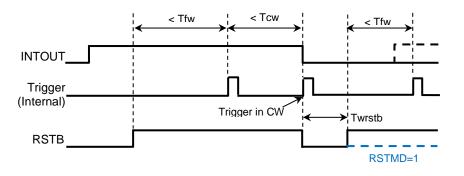

(2) A trigger in CW

When the trigger is entered in CW, a reset is occurred. RSTMD is set to 0, INTOUT asserts low. WDSUS in the reset factor register is set to 1. RSTMD is set to 1, RSTB maintains low (the reset is low after the PMIC's restart through stand-by state in the PMIC.).

(3) No trigger in OW

When the trigger is not entered in OW, the timer is expired and a reset is asserted. RSTMD is set 0, WD is restarted from FW after the reset is released. INTOUT asserts low. WDEXP in the reset factor register is set to 1. RSTMD is set to 1, RSTB maintains low (the reset is low after the PMIC's restart through stand-by state in the PMIC.).

Figure 4-30 No trigger in OW

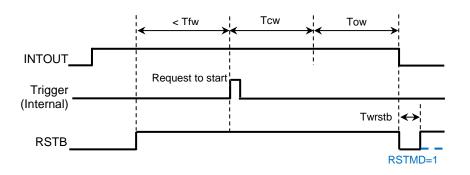

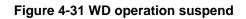

## WD operation suspend

When the output voltage on VOUT1 comes down and SUSP asserts low, then WD stops its operation. And SUSP is changed to high, WD resumes the operation form FW.

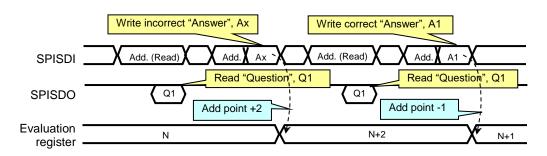

## 4.8.3. Advanced mode

Advanced mode WDT is MCU and the PMIC are monitoring each other operation. Set the configuration register (CONF) to "Advanced mode". The "Advanced mode" is enable in the case of setting to SPI in SPIWDT.

After WD operation starts, MCU should obtain a "Question" to send an "Answer" to the PMIC. (QA monitoring) The "Question" contains operand and objective data. The MCU should send a request to refresh WD timer with data of the "Answer". The "Answer" is in accordance with the operand in the previous "question". The PMIC refreshes the WD timer, gives a point for the "Answer", and accumulates the points to evaluation register. When the accumulated point reaches the designated value, a reset is occurred. The PMIC accepts the other SPI communication form the MCU between "Question" and "Answer".

If "Advanced mode" is not selected, only refreshing the WD timer is executed. It is possible to change to "Advanced mode" in CW, a reset is occurred if the changing the mode is executed in OW.

### Figure 4-32 QA monitoring operation

### Procedure

Below figure illustrates the procedure in accordance with Figure 4-32.

| elow figure illustrates                               | uie p         | noce              |                   | Addr              |                   | orac         |                   | ,                          |                          | 90.10             | Dat                     |                   |                   |                   |              |                  |               |

|-------------------------------------------------------|---------------|-------------------|-------------------|-------------------|-------------------|--------------|-------------------|----------------------------|--------------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|--------------|------------------|---------------|

|                                                       |               |                   |                   | )                 |                   |              |                   |                            |                          |                   |                         | $\square$         |                   |                   |              |                  |               |

|                                                       | R/W           | A5                | A4                | A3                | A2                | A1           | A0                | D7                         | D6                       | D5                | D4                      | D3                | D2                | D1                | D0           | Р                |               |

| Set "SPI mode", <b>—</b><br>"Advanced mode"           | 0             | 0                 | 1                 | 0                 | 0                 | 0            | 0                 | 0                          | 0                        | 0                 | 0                       | 0                 | 0                 | 1                 | 1            | 0                |               |

|                                                       | R/W           | A5                | A4                | A3                | A2                | A1           | A0                | D7                         | D6                       | D5                | D4                      | D3                | D2                | D1                | D0           | Ρ                |               |

| Request to start →                                    | 0             | 0                 | 1                 | 0                 | 1                 | 1            | 0                 | 0                          | 0                        | 0                 | 0                       | 0                 | 0                 | 0                 | 0            | 0                | WD start      |

|                                                       |               |                   |                   |                   |                   |              |                   |                            |                          |                   |                         |                   |                   |                   |              |                  | •             |

|                                                       | R/W           | A5                | A4                | A3                | A2                | A1           | A0                | D7                         | D6                       | D5                | D4                      | D3                | D2                | D1                | D0           | Ρ                |               |

| Read "Question" 🔶                                     | 1             | 0                 | 1                 | 0                 | 1                 | 1            | 0                 | 0                          | 0                        | 0                 | 0                       | 0                 | 0                 | 0                 | 0            | 1                |               |

| "Question" data 🗲                                     | 1             | 1                 | 1                 | 1                 | 1                 | 1            | 1                 | 1                          | 1                        | 0                 | 0                       | 1                 | 0                 | 0                 | 1            | 0                |               |

|                                                       |               |                   |                   |                   |                   |              |                   | Opera                      | and                      |                   | Ra                      | Indon             | n data            | a                 |              |                  |               |

|                                                       |               |                   |                   | A3                | A 0               | ~ 4          |                   |                            | DC                       | D5                | D4                      | D3                | D2                | D1                | D0           | 1                |               |

|                                                       | R/W           | A5                | A4                | AS                | A2                | A1           | A0                | D7                         | D6                       | Do                | 04                      | 00                | 02                |                   | 00           | Р                |               |

| Write "Answer"                                        | R/W<br>0      | A5<br>0           | A4<br>1           | A3<br>0           | A2<br>1           | A1<br>1      | AU<br>0           | D7<br>1                    | D6<br>1                  | 1                 | 1                       | 0                 | 1                 | 1                 | 0            | Р<br>0           | Refresh timer |

| Write "Answer" <del></del>                            |               |                   |                   |                   |                   |              |                   |                            |                          | -                 | _                       | -                 |                   |                   |              |                  | Refresh timer |

| Write "Answer"                                        |               |                   |                   |                   |                   |              |                   |                            |                          | -                 | _                       | -                 |                   |                   |              |                  | Refresh timer |

| Write "Answer" <b>→→</b><br>Read "Question" <b>→→</b> | 0             | 0                 | 1                 | 0                 | 1                 | 1            | 0                 | 1                          | 1                        | 1                 | 1                       | 0                 | 1                 | 1                 | 0            | 0                | Refresh timer |

|                                                       | 0<br>R/W      | 0<br>A5           | 1<br>A4           | 0<br>A3           | 1<br>A2           | 1<br>A1      | 0<br>A0           | 1<br>D7                    | 1<br>D6                  | 1<br>D5           | 1<br>D4                 | 0<br>D3           | 1<br>D2           | 1<br>D1           | 0<br>D0      | 0<br>P           | Refresh timer |

| Read "Question"                                       | 0<br>R/W<br>1 | 0<br>A5<br>0      | 1<br>A4<br>1      | 0<br>A3<br>0      | 1<br>A2<br>1      | 1<br>A1<br>1 | 0<br>A0<br>0<br>1 | 1<br>D7<br>0               | 1<br>D6<br>0<br>0        | 1<br>D5<br>0      | 1<br>D4<br>0<br>1       | 0<br>D3<br>0<br>0 | 1<br>D2<br>0      | 1<br>D1<br>0<br>1 | 0<br>D0<br>0 | 0<br>P<br>1      | Refresh timer |

| Read "Question"                                       | 0<br>R/W<br>1 | 0<br>A5<br>0      | 1<br>A4<br>1      | 0<br>A3<br>0      | 1<br>A2<br>1      | 1<br>A1<br>1 | 0<br>A0<br>0<br>1 | 1<br>D7<br>0<br>1          | 1<br>D6<br>0<br>0        | 1<br>D5<br>0      | 1<br>D4<br>0<br>1       | 0<br>D3<br>0<br>0 | 1<br>D2<br>0      | 1<br>D1<br>0<br>1 | 0<br>D0<br>0 | 0<br>P<br>1      | Refresh timer |

| Read "Question"                                       | 0<br>R/W<br>1 | 0<br>A5<br>0<br>1 | 1<br>A4<br>1<br>1 | 0<br>A3<br>0<br>1 | 1<br>A2<br>1<br>1 | 1<br>A1<br>1 | 0<br>A0<br>0<br>1 | 1<br>D7<br>0<br>1<br>Opera | 1<br>D6<br>0<br>0<br>and | 1<br>D5<br>0<br>1 | 1<br>D4<br>0<br>1<br>Ra | 0<br>D3<br>0<br>0 | 1<br>D2<br>0<br>0 | 1<br>D1<br>0<br>1 | 0<br>D0<br>0 | 0<br>P<br>1<br>0 | Refresh timer |

#### Figure 4-33 Refresh procedure in advanced mode

- Select "SPI mode" and "Advance mode" Set the configuration register (CONF) to control WD via SPI and use advance mode. In Figure 4-33, D0 bit and D1 bit are set 1.

- Request to WD start Enter WD trigger address (WDTRG) to start WD function. The data of WDTRG is ignored in WD start, but the parity bit is checked.

- Read "Question"

The PMIC generates a random data as a question containing 2bit operand and 6bit objective data. A MCU has to read the question to respond with an answer.

• Write "Answer"

A MCU enters an answer to the obtained data. The address data to enter an answer is same as a WD trigger address (WDTRG) and refresh the WD timer simultaneously. The data contains 2bit operand and 6bit data operated along with the operand. If the consecutive "Question" reading, the "Question" is the first reading data.

#### Evaluation register

The PMIC gives a point to the entered answer and has the register (ACCVA) to accumulate the points. The accumulated value is read via SPI. When the WD starts, accumulated point is 0. The evaluation is executed in OW.

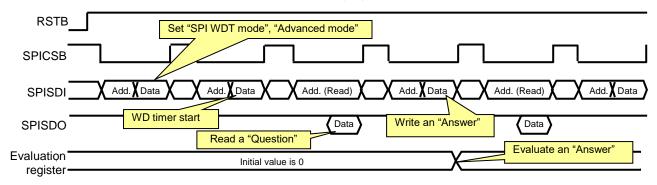

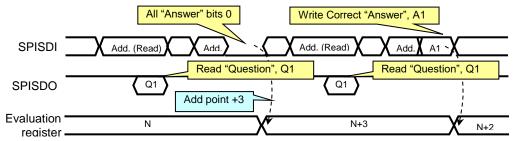

• Correct "Answer" sending in OW

The PMIC gives "-1" point to the evaluation register when a correct answer is entered. If the accumulated value in the evaluation register is 0, the evaluation register is "0".

In below example, a correct answer A1 is entered as a response of Q1. And then, "-1" is added to current value of evaluation register.

Figure 4-34 Evaluation for enterd answer (Correct answer)

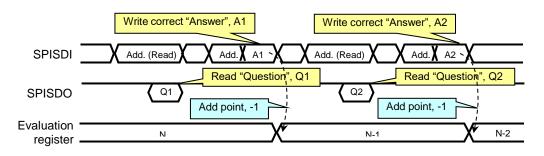

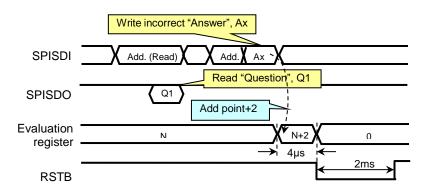

• Incorrect "Answer" sending in OW

The PMIC gives "+2" point to the evaluation register when an incorrect answer is entered. And the next question is same as previous one.

In below example, an incorrect answer Ax is entered as a response of Q1. And then, "+2" is added to current value of evaluation register. In spite of incorrect answer, the PMIC refreshes the WD timer.

Figure 4-35 Evaluation for enterd answer (Incorrect answer)

• "Answer" bits all "0"

The PMIC gives "+3" point to evaluation register when the entered bits of the answer are all "0". The PMIC never create a "Question" which leads the answer's bits are all 0.

Figure 4-36 Evaluation for enterd answer (No answer)

• Reset by accumulated value

Through QA monitoring, when accumulated value (ACCVA) is more than designated value (SETVA), a reset is occurred.

In below example, the reset value of evaluation register (RSTVA) is more than "N+1" and the current value of the evaluation register is "N". When an incorrect answer is entered, the value comes up to "N+2". Eventually, the reset is occurred after 4us passes. The pulse width of the reset is 2ms.

Figure 4-37 Evaluation for enterd answer (In appropriate term)

#### 4.8.4. Register

The contents of WDT setting are described in this section.

> WD trigger

Only entering address refresh the timer in SPI mode ((D7-D0) data is ignored but the parity bit is checked)

■ Address(WDTRG): 16H

| A5    | A4 | 4 A3 | A2 | A1 | A0 |

|-------|----|------|----|----|----|

| <br>0 | 1  | 0    | 1  | 1  | 0  |

Register

To evaluate "answer", MCU should enter below data in accordance with the question.

|    | D7                                    | D6    | D5         | D5 D4 D3 D2 D1 D0 |      |       |  |     |  |  |  |

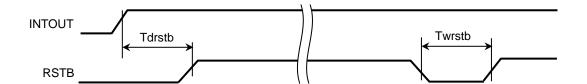

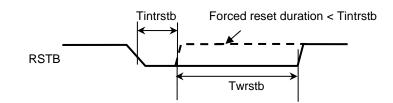

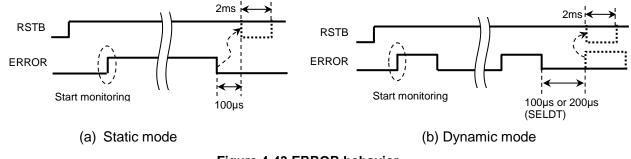

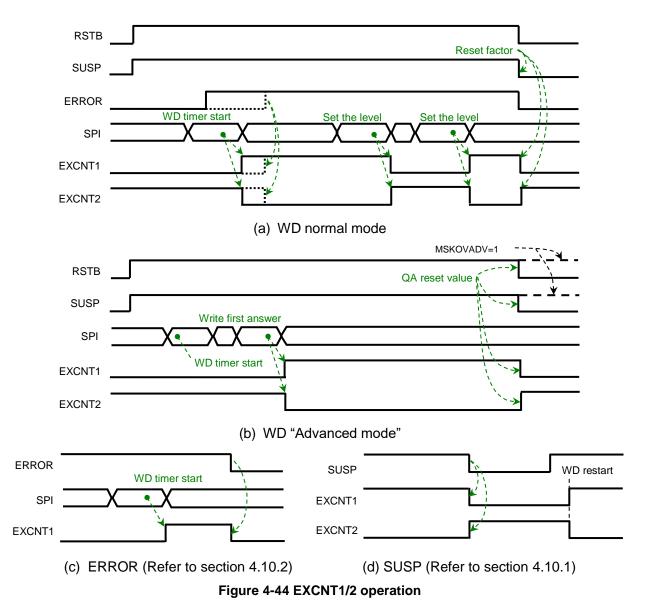

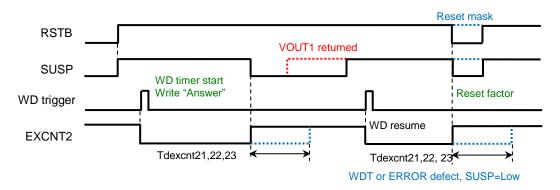

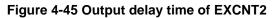

|----|---------------------------------------|-------|------------|-------------------|------|-------|--|-----|--|--|--|