Document Number: MC33186

Rev. 7.0, 10/2011

# **H-Bridge Driver**

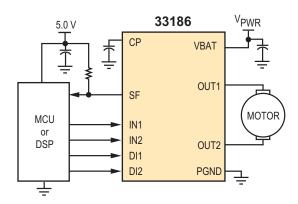

The 33186 is a monolithic H-Bridge ideal for fractional horsepower DC-motor and bi-directional thrust solenoid control. The IC incorporates internal control logic, charge pump, gate drive, and low  $R_{DS(ON)}$  MOSFET output circuitry. The 33186 is able to control continuous inductive DC load currents up to 5.0 A. Output loads can be pulse width modulated (PWM-ed) at frequencies up to 10 kHz.

The 33186 is parametrically specified over a temperature range of -40°C  $\leq$   $T_A \leq$  125°C, 5.0 V  $\leq$  V+  $\leq$  28 V. The IC can also be operated up to 40 V with de-rating of the specifications. The IC is available in a surface mount power package with exposed pad for heat sinking.

#### **Features**

- Overtemperature, Short-Circuit Protection, and Overvoltage Protection against Transients up to 40 V at VBAT Typical

- RDSon = 150 mΩ for each output Transistor at 25°C

- Continuous DC Load Current 5 A (TC < 100°C)</li>

- Output Current Limitation at typ 6,5 A +/- 20%

- · Short-Circuit Shutdown for Output Currents over 8 A

- Logic Inputs TTL/CMOS Compatible

- Operating Frequency up to 20 kHz

- · Undervoltage Disable Function

- · Diagnostic Output, 2 Disable Input

- Coding Input for Alternative Functions

- Stable Operation with an External Capacitance of Maximum 47  $\mu\text{F}$  at VBAT

- Pb-Free Packaging Designated by Suffix Code VW

33186

### H-BRIDGE MOTOR DRIVER

DH SUFFIX VW SUFFIX (PB-FREE) PLASTIC PACKAGE 98ASH70702A 20-PIN HSOP

| ORDERING INFORMATION                       |                |         |  |  |

|--------------------------------------------|----------------|---------|--|--|

| Device Temperature Range (T <sub>A</sub> ) |                |         |  |  |

| MC33186DH1/R2                              | -40°C to 125°C | 20 HSOP |  |  |

| MC33186VW1/R2                              | -40 C to 125 C | 20113OF |  |  |

Figure 1. 33186 Simplified Block Diagram

<sup>\*</sup>This document contains certain information on a product under development. Freescale reserves the right to change or discontinue this product without notice

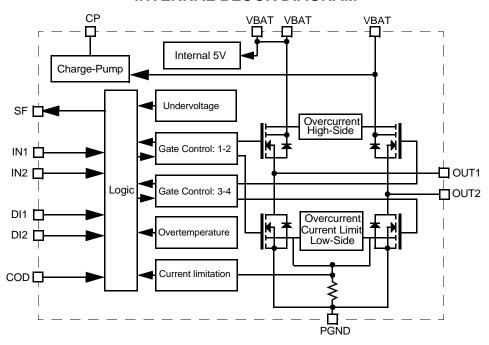

## INTERNAL BLOCK DIAGRAM

Figure 2. 33186 Simplified Internal Block Diagram

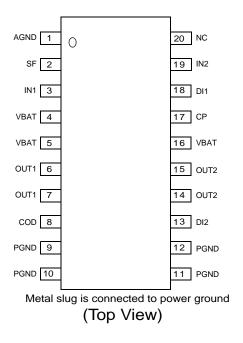

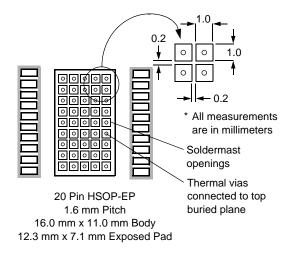

## **PIN CONNECTIONS**

## **PIN CONNECTIONS**

Figure 3. 33186 Pin Locations

Table 1. 33186 Pin Description

| Pin                         | Name                              | Description                                                                                                                                                                                                                                                         |

|-----------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 10, 11, 12<br>Metal slug | PGND                              | Power Ground. All the ground are connected together, they should be connected as short as possible on the PCB.                                                                                                                                                      |

| 1                           | AGND                              | Analog ground. All the ground are connected together, they should be connected as short as possible on the PCB.                                                                                                                                                     |

| 2                           | Output<br>Status flag (SF)        | Open drain output, active low. Is set according to the truth table. When a fault appears, SF changes typically in less than 100 ms.                                                                                                                                 |

| 3,13<br>18, 19              | Inputs IN1, IN2,<br>DI1, DI2, COD | Voltage controlled inputs with hysteresis                                                                                                                                                                                                                           |

| 8                           | COD                               | When not connected or connected to GND, a stored failure will be reset by change of the voltage-level on DI1 or DI2.  When connected to VCC, the disable Pin DI1 and DI2 are inactive. A stored failure will be reset by change of the voltage-level on IN1 or IN2. |

| 6, 7, 14, 15                | OUT1, OUT2                        | H-Bridge outputs with integrated free-wheeling diodes.                                                                                                                                                                                                              |

Table 1. 33186 Pin Description(continued)

| Pin      | Name | Description                                                                                                                                                                                                                                                                                                                    |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 5, 16 | VBAT | The Pins 4 and 5 are internally connected. These Pins supply the left high side and the analog/logic part of the device.                                                                                                                                                                                                       |

|          |      | The Pin 16 supplies the right high side and the charge pump.                                                                                                                                                                                                                                                                   |

|          |      | The Pins 4, 5 and 16 should be connected together on the printed circuit board with connections as short as possible.                                                                                                                                                                                                          |

|          |      | Supervision and protection functions                                                                                                                                                                                                                                                                                           |

|          |      | a) Supply voltage supervision                                                                                                                                                                                                                                                                                                  |

|          |      | The supply voltage is supervised. If it is below its specific threshold, the power stages are switched in tristate and the status flag is switched low.                                                                                                                                                                        |

|          |      | If the supply voltage is over the specific threshold again, the power stage switches independently into normal operation, according to the input Pins and the status flag is reset.                                                                                                                                            |

|          |      | b) Thermal supervision                                                                                                                                                                                                                                                                                                         |

|          |      | In case of overtemperature, the power stages are switched in tristate independent of the inputs signals and the status flag is switched low.                                                                                                                                                                                   |

|          |      | If the level changes from high to low on DI1 (IN1) or low to high on DI2 (IN2), the output stage switches on again if the temperature is below the specified limit. The status-flag is reset to high level (Pin names in brackets refer to coding Pin = VCC).                                                                  |

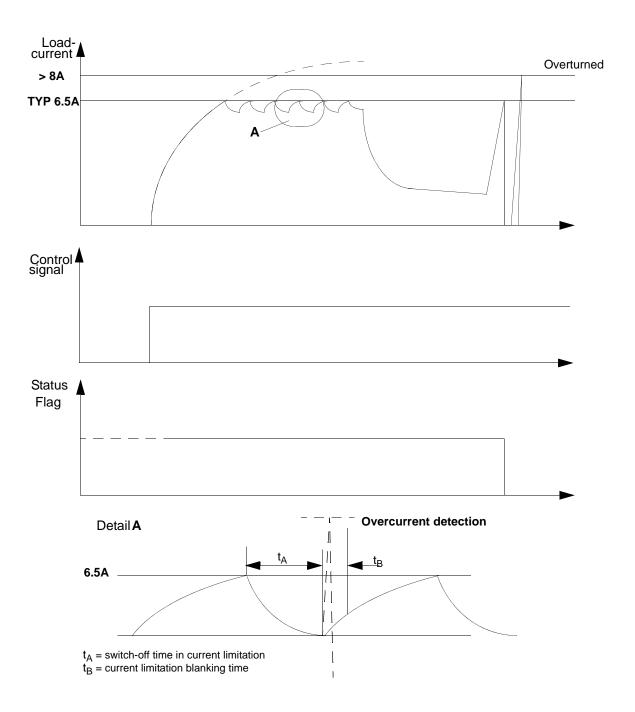

|          |      | c) Supervision of overcurrent on high sides and low sides                                                                                                                                                                                                                                                                      |

|          |      | In case of over-current detection, the power stages are switched in tristate independent of the inputs signals and the status flag is set.                                                                                                                                                                                     |

|          |      | If the level changes from high to low on DI1 (IN1) or low to high on DI2 (IN2) the output stage switches on again and the status flag is reset to high level (Pin names in brackets refer to coding Pin = VCC).                                                                                                                |

|          |      | The output stage switches into the mode defined by the inputs Pins provided, and/if the temperature is below the specified limits.                                                                                                                                                                                             |

|          |      | d) Current limiting on low sides                                                                                                                                                                                                                                                                                               |

|          |      | The maximum current which can flow under normal operating conditions is limited to Imax = 6,5 A +/- 20%. When the maximum current value is reached, the output stages are switched tristate for a fixed time. According to the time constant the current decreases until the next switch on occurs. See page 8 for schematics. |

| 17       | СР   | Charge Pump output Pin                                                                                                                                                                                                                                                                                                         |

|          |      | A filtering capacitor (up to 33 nF) can be connected between Pin 17 and Gnd. Device can operate without external capacitor, although Pin 17 decoupling capacitor help in noise reduction and allows the device to perform a maximum speed, timing and PWM frequency.                                                           |

## **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

### Table 2. MAXIMUM RATINGS

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                | Symbol            | Min   | Тур     | Max  | Unit |

|--------------------------------------------------------|-------------------|-------|---------|------|------|

| ELECTRICAL RATINGS                                     |                   |       |         | 1    |      |

| Supply Voltage                                         |                   |       |         |      | V    |

| Static Destruction Proof                               | $V_{BAT}$         | - 1.0 | _       | 28   |      |

| Dynamic Destruction Proof t < 0,5 s                    | $V_{Bat}$         | - 2.0 | -       | 40   |      |

| Logic Inputs (IN1, IN2, DI1, DI2, CODE)                | U                 | - 0.5 | -       | 7.0  | V    |

| Output Status - Flag SF                                | U <sub>SF</sub>   | - 0.5 | _       | 7.0  | V    |

| THERMAL RATINGS                                        |                   |       |         |      |      |

| Junction Temperature                                   | T <sub>J</sub>    | - 40  | _       | +150 | °C   |

| Storage Temperature                                    | T <sub>S</sub>    | - 55  | -       | +125 | °C   |

| Ambient Temperature                                    | T <sub>A</sub>    | - 40  | -       | +125 | °C   |

| Thermal Resistance (with power applied on 2            |                   |       |         |      |      |

| power MOS)                                             | $Rth_JC$          | -     | -       | +1.5 | K/W  |

| Thermal Resistance (with power applied on 2            |                   |       |         |      |      |

| power MOS)                                             | $Rth_{JC}$        | -     | _       | +1.5 | K/W  |

| Peak Package Reflow Temperature During Reflow (1), (2) | T <sub>PPRT</sub> |       | Note 2. |      | °C   |

### Notes

- 1. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),

Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

## STATIC ELECTRICAL CHARACTERISTICS

### **Table 3. STATIC ELECTRICAL CHARACTERISTICS**

Characteristic noted under conditions -40°C to +125 °C, VBAT from 5 V to 28 V, unless otherwise note. Typical values reflect approximate mean at 25°C, nominal VCC, at time of device characterization.

| Characteristics                                           | Symbol                             | Min   | Тур  | Max  | Unit      |

|-----------------------------------------------------------|------------------------------------|-------|------|------|-----------|

| POWER SUPPLY                                              |                                    |       |      |      |           |

| Operating Range:                                          |                                    |       |      |      |           |

| Static                                                    | $V_{BAT}$                          | 5.0   | _    | 28   | V         |

| Dynamic (t < 500 ms)                                      | $V_{BAT}$                          | _     | _    | 40   | V         |

| Stand-by current                                          |                                    |       |      |      |           |

| f = 0 to 10 KHz; IOUT = 0 A                               | I V <sub>BAT</sub>                 | -     | _    | 35   | mA        |

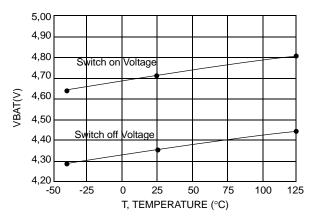

| VBAT-undervoltage switch-off (without load)               |                                    |       |      |      |           |

| Switch-off Voltage                                        |                                    | 4.15  | 4.4  | 4.65 | V         |

| Switch-on Voltage                                         |                                    | 4.5   | 4.75 | 5.0  | V         |

| Hysteresis                                                |                                    | 150   | _    | -    | mV        |

| CHARGE-PUMP SUPPLY                                        |                                    |       | l    |      |           |

| VBAT = 4.15 V                                             | V <sub>CP</sub> - V <sub>BAT</sub> | 3.35  | _    | -    | V         |

| VBAT < 40 V                                               | V <sub>CP</sub> - V <sub>BAT</sub> | _     | _    | 20   | V         |

| LOGIC INPUTS                                              |                                    | •     | •    |      |           |

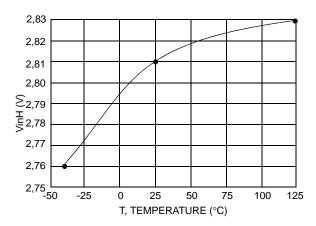

| Input High                                                | VINH                               | 3.4   | -    | -    | V         |

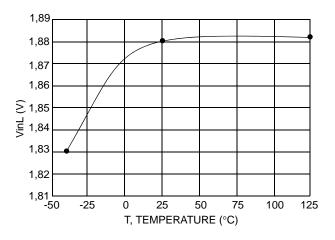

| Input Low                                                 | VINL                               | -     | -    | 1.4  | V         |

| Input Hysteresis                                          | U                                  | 0.7   | 1.0  | -    | V         |

| Input Pull Up Current (IN1, IN2, DI1)                     | I                                  | - 200 | - 80 | _    | μА        |

| UIN = 0.0 V                                               |                                    |       |      |      |           |

| Input Pull Down Current (DI2,COD)(3)                      | I <sub>DI2</sub>                   | _     | 25   | 100  | μА        |

| UDI2 = 5.0 V                                              | 2.2                                |       |      |      |           |

| POWER OUTPUTS: OUT1, OUT2                                 |                                    |       |      |      |           |

| Switch on resistance:                                     |                                    |       |      |      |           |

| R <sub>OUT - VBAT</sub> ; R <sub>OUT - GND</sub>          |                                    |       |      |      |           |

| VBAT = 5 to 28 V; CCP = 0 to 33 nF                        |                                    | _     | -    | 300  | $m\Omega$ |

| Switch-off Current during Current Limitation on Low Sides | (I <sub>OUT</sub> ) MAX            | 5.2   | 6.5  | 7.8  | Α         |

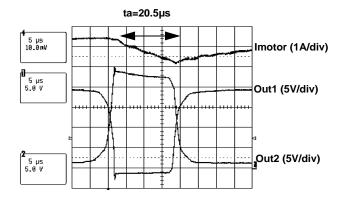

| Switch-off Time during Current Limitation on Low Sides    | t <sub>A</sub>                     | 15    | 20.5 | 26   | μS        |

| Blanking Time during Current Limitation on Low Sides      | t <sub>B</sub>                     | 12    | 16.5 | 21   | μs        |

### Notes

3. In case of negative voltage at OUT2 (respectively OUT1) this maximum pull down current at DI2 (respectively COD) Pin can be exceeded. This happens during recirculation when the current is flowing in the low side. See curve 22.

## Table 3. STATIC ELECTRICAL CHARACTERISTICS(continued)

Characteristic noted under conditions -40°C to +125 °C, VBAT from 5 V to 28 V, unless otherwise note. Typical values reflect approximate mean at 25°C, nominal VCC, at time of device characterization.

| Characteristics                                      | Symbol                          | Min          | Тур | Max | Unit |

|------------------------------------------------------|---------------------------------|--------------|-----|-----|------|

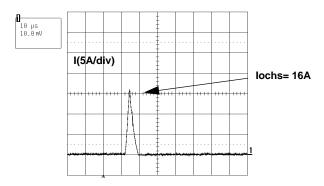

| High Side Overcurrent Detection <sup>(4)</sup>       | I <sub>ochs</sub>               | 11           | _   | -   | A    |

| Low Side Overcurrent Detection                       | locus                           | 8.0          | -   | -   |      |

| Leakage Current                                      |                                 |              |     |     |      |

| Output Stage Switched off                            |                                 | _            | -   | 100 | μΑ   |

| Free-Wheeling Diode Forward Voltage                  |                                 |              |     |     |      |

| IOU = 3.0 A                                          | $U_{D}$                         | _            | -   | 2.0 | V    |

| Free-Wheeling Diode Reverse                          |                                 |              |     |     |      |

| Recovery Time                                        | t <sub>RR</sub>                 | _            | 2.0 | 5.0 | μs   |

| IFM =1.0 A, $di/dt = 4.0 \text{ A/}\mu\text{s}$      |                                 |              |     |     |      |

| Switch-off Temperature                               |                                 | 160          | -   | 190 | °C   |

| Hysteresis                                           |                                 | 20           | -   | 30  | °C   |

| OUTPUT STATUS FLAG (OPEN DRAIN OUT                   | PUT)                            | <del>!</del> |     | !   |      |

| Output High (SF not set)                             |                                 |              |     |     |      |

| USF = 5.0 V                                          | I <sub>SF</sub>                 | _            | -   | 10  | μΑ   |

| Output Low (SF set)                                  |                                 |              |     |     |      |

| ISF = 300 μA                                         | VSF                             | _            | _   | 1.0 | V    |

| TIMING                                               |                                 | •            |     | •   |      |

| PWM frequency                                        |                                 |              |     |     |      |

| CCP = 33 nF                                          | f                               | _            | -   | 10  | KHz  |

| Maximum Switching Frequency During                   |                                 |              |     |     |      |

| Current Limitation                                   |                                 |              |     |     |      |

| $VBAT = 628 VC_{CP} = 33 nF$                         | f                               | _            | -   | 20  | KHz  |

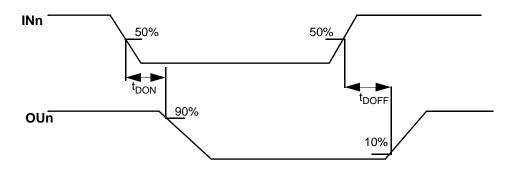

| Output ON Delay                                      |                                 |              |     |     |      |

| IN1 <sub>&gt;</sub> OUT1 or IN2 <sub>&gt;</sub> OUT2 | t <sub>DON</sub>                | _            | -   | 15  | μS   |

| Output OFF Delay                                     |                                 |              |     |     |      |

| IN1 <sub>&gt;</sub> OUT1 or IN2 <sub>&gt;</sub> OUT2 | t <sub>DOFF</sub>               | _            | _   | 15  | μs   |

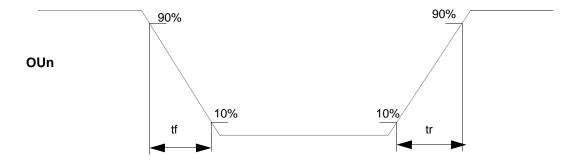

| Output Switching Time                                |                                 |              |     |     |      |

| CCP = 0 to 33 nF                                     |                                 |              |     |     |      |

| OUTiHOUTiL, OUTiLOUTiH,                              | t <sub>r</sub> , t <sub>f</sub> | 2.0          | _   | 5.0 | μS   |

| IOUT = 3.0 A                                         |                                 |              |     |     |      |

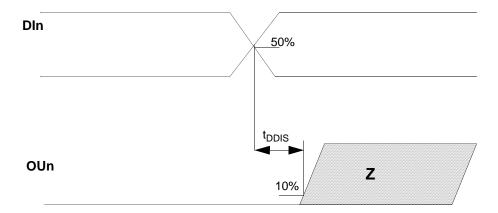

| Disable Delay Time                                   |                                 |              |     |     |      |

| DliOUTi                                              | t <sub>DDIS</sub>               | _            | -   | 8.0 | μS   |

| Turn off in Case of Overcurrent or                   |                                 | _            | 4.0 | 8.0 | μs   |

| Overtemperature                                      |                                 |              |     |     |      |

| Power On Delay Time (CCP = 33 nF) <sup>(5)</sup>     |                                 | _            | 1.0 | 5.0 | ms   |

## Notes

- 4. In case of overcurrent, the time when the current is greater than 7.8 A is lower than 30 μs, with a maximum frequency of 1 kHz.

- 5. This parameter corresponds to the time for CCP to reach its nominal value when VBAT is applied.

## **TRUTH TABLE**

Table 4. TRUTH TABLE

| Device State                      | Input Conditions   |                    |     | Sta | tus               | Out                | puts |     |

|-----------------------------------|--------------------|--------------------|-----|-----|-------------------|--------------------|------|-----|

|                                   | DI1 <sup>(8)</sup> | DI2 <sup>(8)</sup> | IN1 | IN2 | SF <sup>(9)</sup> | SF <sup>(10)</sup> | OU1  | OU2 |

| 1-Forward                         | L                  | Н                  | Н   | L   | Н                 | Н                  | Н    | L   |

| 2-Reverse                         | L                  | Н                  | L   | Н   | Н                 | Н                  | L    | Н   |

| 3-Free Wheeling Low               | L                  | Н                  | L   | L   | Н                 | Н                  | L    | L   |

| 4-Free Wheeling High              | L                  | Н                  | Н   | Н   | Н                 | Н                  | Н    | Н   |

| 5-Disable 1                       | Н                  | Х                  | Х   | Х   | L                 | Н                  | Z    | Z   |

| 6-Disable 2                       | Х                  | L                  | Х   | Х   | L                 | Н                  | Z    | Z   |

| 7-IN1 Disconnected                | L                  | Н                  | Z   | Х   | Н                 | Н                  | Н    | Х   |

| 8-IN2 Disconnected                | L                  | Н                  | Х   | Z   | Н                 | Н                  | Х    | Н   |

| 9-DI1 Disconnected                | Z                  | Х                  | Х   | Х   | L                 | Н                  | Z    | Z   |

| 10-DI2 Disconnected               | Х                  | Z                  | Х   | Х   | L                 | Н                  | Z    | Z   |

| 11-Current Limit.active           | L                  | Н                  | Х   | Х   | Н                 | Н                  | Z    | Z   |

| 12-Undervoltage <sup>(6)</sup>    | Х                  | Х                  | Х   | Х   | L                 | L                  | Z    | Z   |

| 13-Overtemperature <sup>(7)</sup> | Х                  | Х                  | Х   | Х   | L                 | L                  | Z    | Z   |

| 14-Overcurrent <sup>(7)</sup>     | Х                  | Х                  | Х   | Х   | L                 | L                  | Z    | Z   |

## Notes

- 6. In case of undervoltage, tristate and status-flag are reset automatically.

- 7. Whenever overcurrent or overtemperature is detected, the fault is stored (i.e. status-flag remains low). The tristate conditions and the status-flag are reset via DI1 (IN1) or DI2 (IN2). Pin names in brackets refer to coding Pin (COD = VCC).

- 8. If COD = VCC then DI1 and DI2 are not active.

- 9. COD = nc or GND

- 10. COD = VCC

L = Low

H = High X = High or Low

Z = High impedance (all output stage transistors are switched off).

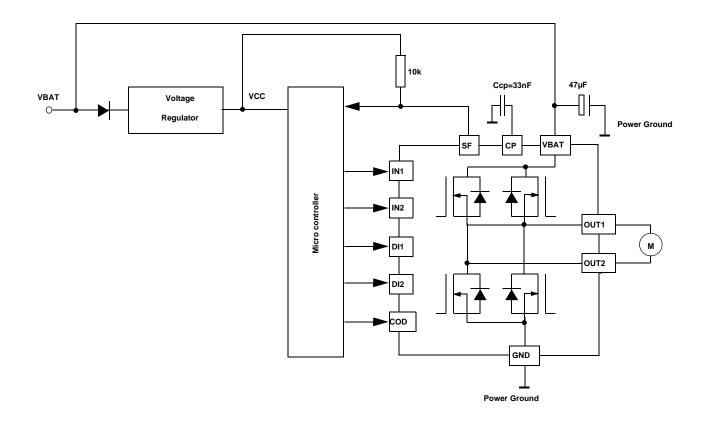

Figure 4. Typical Application

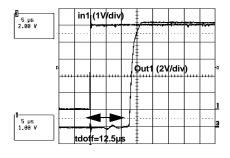

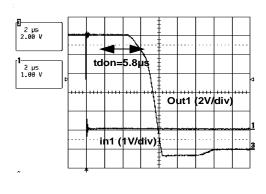

Figure 5. Output Delay Time

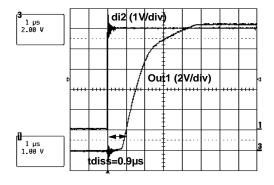

Figure 6. Disable Delay Time

Figure 7. Output Switching Time

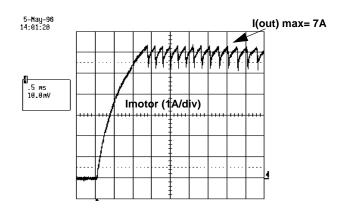

Figure 8. Current Limitation on Low Side

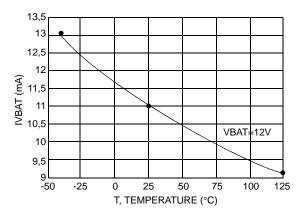

Figure 9. Stand-by Current vs. Temperature

Figure 10. VBAT Undervoltage vs. Temperature

Figure 11. Low Threshold Input Voltage vs. Temperature

Figure 12. High Threshold Input Voltage vs. Temperature

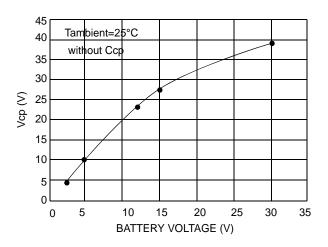

Figure 13. Vcp vs. Battery Voltage

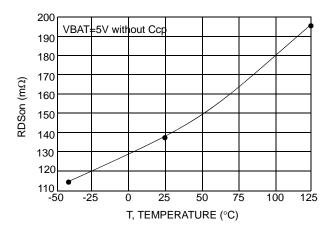

Figure 14. RDSON vs. Temperature

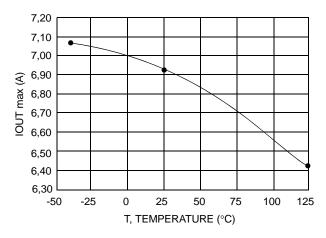

Figure 15. Switch off Current vs. Temperature

Figure 18. Switch off Time

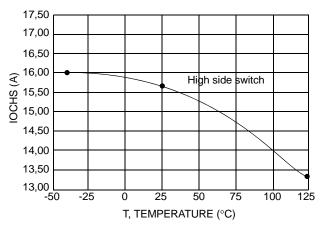

Figure 16. Overcurrent Detection vs. Temperature

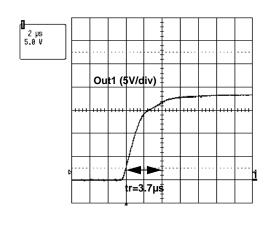

Figure 19. Output Switching Time: Tr

Figure 17. Current Limitation

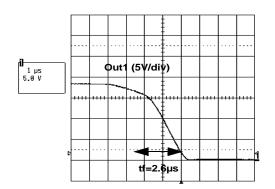

Figure 20. Output Switching Time: Tf

Figure 21. Output OFF Delay

Figure 22. Output ON Delay

Figure 23. Disable Delay Time

Figure 24. High Side Overcurrent High Side Detection

Note: Current through internal recirculation diode, @125°C in case of negative voltage at OUT2

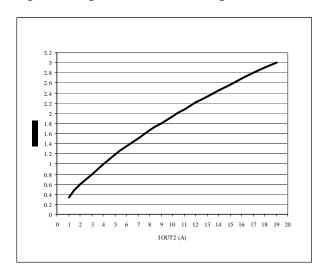

Figure 25. Maximum Di2 Input Current vs. lout2, current

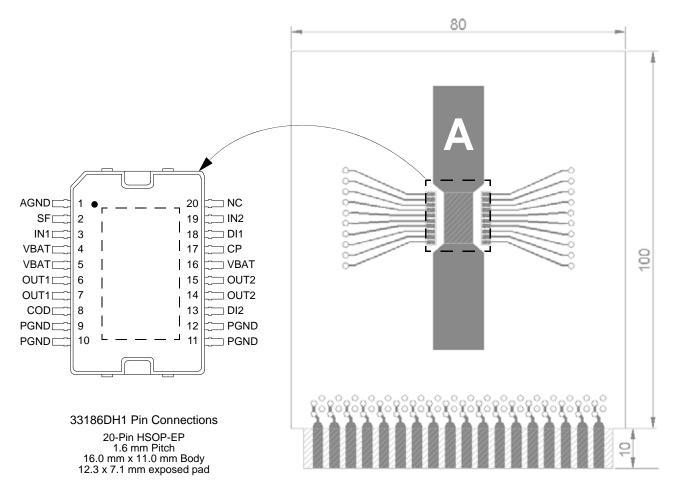

## **PACKAGING**

## **SOLDERING**

The 20 HSOP package is designed for enhanced thermal performance. The particularity of this package is its copper base plate on which the power die is soldered. The base plate is soldered on a PCB to provide heat flow to the ambient and also to provide a large thermal capacitance.

Of course, the more copper area on the PCB, the better the power dissipation and transient behavior.

We characterized the 20 HSOP on a double side PCB. The bottom side area of the copper is 7.8 cm<sup>2</sup>. The top surface is 2.7 cm<sup>2</sup>, see Figure 26.

Top Side

**Bottom Side**

Figure 26. PCB Test Layout

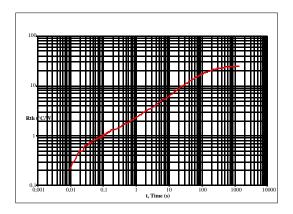

Figure 27. PHSOP20 Thermal Response

<u>Figure 27</u> shows the thermal response with the device soldered on to the test PCB described on <u>Figure 26</u>.

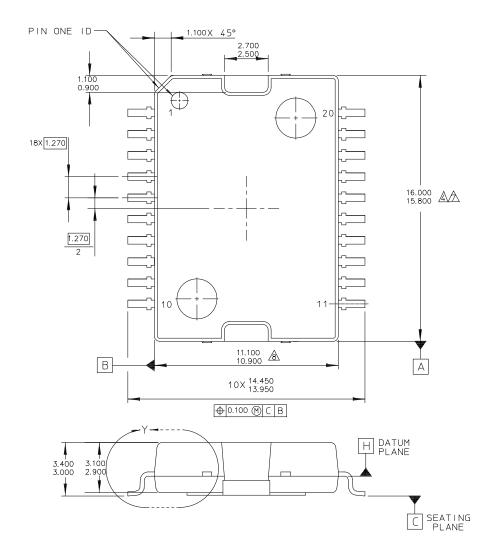

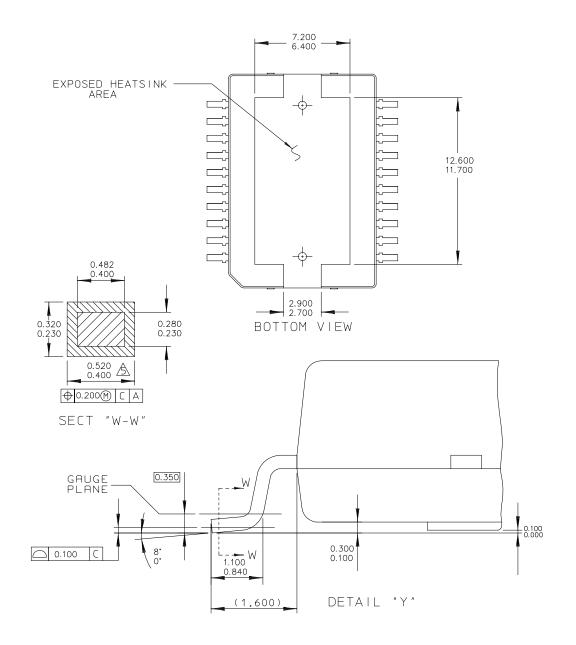

## **PACKAGE DIMENSIONS**

**Important:** Package dimensions are provided in package drawings. To find the most current package outline drawing, go to www.freescale.com and perform a keyword search for the drawing's document number.

**Table 5. Package Drawing Information**

| Package     | Suffix | Package Outline Drawing Number |

|-------------|--------|--------------------------------|

| 20-PIN HSOP | DH/VW  | 98ASH70702A                    |

Dimensions shown are provided for reference ONLY (For Layout and Design, refer to the Package Outline Drawing listed in the following figures).

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OU | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|---------------------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE:  20 LEAD HSOP  W/PROTRUDING HEATSINK             |               | DOCUME  | NT NO: 98ASH70702A | REV: C      |

|                                                         |               | CASE NU | JMBER: 979         | 11 OCT 2011 |

|                                                         |               | STANDAF | RD: NON-JEDEC      |             |

VW (Pb-FREE) SUFFIX 20-PIN HSOP 98ASH70702A ISSUE C

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OU | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|---------------------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE:  20 LEAD HSOP  W/PROTRUDING HEATSINK             |               | DOCUME  | NT NO: 98ASH70702A | REV: C      |

|                                                         |               | CASE NU | JMBER: 979         | 11 OCT 2011 |

|                                                         |               | STANDAF | RD: NON-JEDEC      |             |

VW (Pb-FREE) SUFFIX 20-PIN HSOP 98ASH70702A ISSUE C

### NOTES:

- 1. CONTROLLING DIMENSION: MILLIMETER.

- 2. DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

6. DATUM A AND B TO BE DETERMINED AT DATUM PLANE H.

3. DATUM PLANE H IS LOCATED AT BOTTOM OF THE LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION IS 0.127 TOTAL IN EXCESS OF THE DIMENSION AT MAXIMUM MATERIAL CONDITION.

7. DIMENSION DOES NOT INCLUDE TIEBAR PROTRUSIONS. ALLOWABLE TIEBAR PROTRUSIONS ARE 0.150 PER SIDE.

8. THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION IS 0.250 PER SIDE. THIS DIMENSION DOES INCLUDE MOLD MISMATCH AND IS DETERMINED AT DATUM H.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLI | NE PRINT VERSION NO    | T TO SCALE  |

|------------------------------------------------------|------------------|------------------------|-------------|

| TITLE: 20 LEAD HSO                                   |                  | CUMENT NO: 98ASH70702A | REV: C      |

| W/PROTRUDING HEATSINK                                |                  | SE NUMBER: 979         | 11 OCT 2011 |

|                                                      |                  | ANDARD: NON JEDEC      |             |

VW (Pb-FREE) SUFFIX 20-PIN HSOP 98ASH70702A ISSUE C

33186

## 33186DH 33186VW

## 20-PIN HSOP-EP

DH SUFFIX VW SUFFIX (Pb-FREE) 98ASH70273A 20-PIN HSOP-EP

**Note** For package dimensions, refer to the 33186 data sheet.

## ADDITIONAL DOCUMENTATION

### THERMAL ADDENDUM (REV 2.0)

#### Introduction

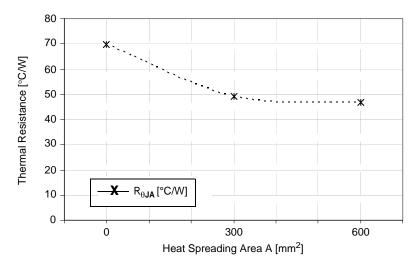

This thermal addendum is provided as a supplement to the MC33186 technical datasheet. The addendum provides thermal performance information that may be critical in the design and development of system applications. All electrical, application, and packaging information is provided in the datasheet.

### **Package and Thermal Considerations**

The MC33186 is offered in a 20 pin HSOP exposed pad, single die package. There is a single heat source (P), a single junction temperature ( $T_J$ ), and thermal resistance ( $R_{\theta JA}$ ).

$$\{T_J\} = [R_{\theta JA}] \cdot \{P\}$$

The stated values are solely for a thermal performance comparison of one package to another in a standardized environment. This methodology is not meant to and will not predict the performance of a package in an application-specific environment. Stated values were obtained by measurement and simulation according to the standards listed below.

### Standards

**Table 6. Thermal Performance Comparison**

| Thermal Resistance                   | [°C/W] |

|--------------------------------------|--------|

| R <sub>θJA</sub> <sup>(1), (2)</sup> | 29     |

| R <sub>0</sub> JB (2), (3)           | 9.0    |

| R <sub>0JA</sub> (1), (4)            | 69     |

| R <sub>θJC</sub> <sup>(5)</sup>      | 2.0    |

### Notes:

- 1. Per JEDEC JESD51-2 at natural convection, still air condition.

- 2s2p thermal test board per JEDEC JESD51-5 and JESD51-7.

- 3. Per JEDEC JESD51-8, with the board temperature on the center trace near the center lead.

- Single layer thermal test board per JEDEC JESD51-3 and JESD51-5.

- Thermal resistance between the die junction and the exposed pad surface; cold plate attached to the package bottom side, remaining surfaces insulated.

Figure 28. Thermal Land Pattern for Direct Thermal Attachment According to JESD51-5

Figure 29. Thermal Test Board

### **Device on Thermal Test Board**

Material: Single layer printed circuit board

FR4, 1.6 mm thickness

Cu traces, 0.07 mm thickness

Outline: 80 mm x 100 mm board area,

including edge connector for

thermal testing

Area A: Cu heat-spreading areas on board

surface

Ambient Conditions: Natural convection, still air

**Table 7. Thermal Resistance Performance**

| A [mm²] | R <sub>θJA</sub> [°C/W] |

|---------|-------------------------|

| 0       | 70                      |

| 300     | 49                      |

| 600     | 47                      |

$R_{\theta,JA}$  is the thermal resistance between die junction and ambient air.

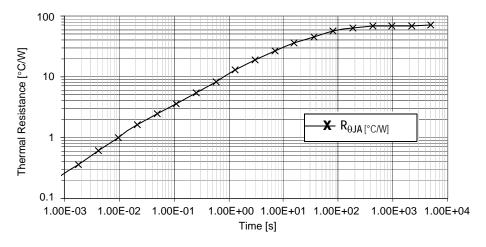

Figure 30. Device on Thermal Test Board  $R_{\theta JA}$

Figure 31. Transient Thermal Resistance  $R_{\theta JA}$  1 W Step Response, Device on Thermal Test Board Area A = 600 (mm²)

## **REVISION HISTORY**

| REVISION | DATE    | DESCRIPTION OF CHANGES                                                                                                                                                                                                        |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.0      | 5/2006  | <ul><li>Implemented Revision History page</li><li>Added Lead Free (Pb-Free) Part Number MC33186VW1</li></ul>                                                                                                                  |

| 6.0      | 10/2006 | Updated data sheet formal     Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from MAXIMUM RATINGS on page 5. Added note with instructions to obtain this information from www.freescale.com. |

| 7.0      | 10/2011 | <ul> <li>Updated Package Dimensions according to the latest Freescale package specification<br/>98ASH70702A_C</li> <li>Updated to the current Freescale form and style.</li> </ul>                                            |

### How to Reach Us:

### Home Page:

www.freescale.com

### Web Support:

http://www.freescale.com/support

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 10 5879 8000

support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further to products herein. Freescale Semiconductor makes no warranty, representation or regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", be validated for each customer application by technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are designed. intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Qorivva, \$12 MagniV, SMARTMOS and Xtrinsic are trademarks of Freescale Semiconductor, Inc. ARM is the registered trademark of ARM Limited. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. All other product or service names are the property of their respective owners. ©2011 Freescale Semiconductor, Inc.

MC33186 Rev. 7.0 10/2011