HI2309

Triple 10-Bit, 50 MSPS, 3-Channel D/A Converter

January 1998

## Features Maximum Conversion Speed . . . . . . . . . . 50MHz · RGB 3-Channel Input/Output Differential Linearity Error . . . . . . . . . . ±0.5 LSB (200 $\Omega$ Load for $2V_{P-P}$ Output)

- · Low Glitch

- Direct Replacement for Sony CXD2309

## Applications

- Digital TV

- Graphics Display

- · High Resolution Color Graphics

- · Video Reconstruction

- Instrumentation

- · Image Processing

- I/Q Modulation

## Description

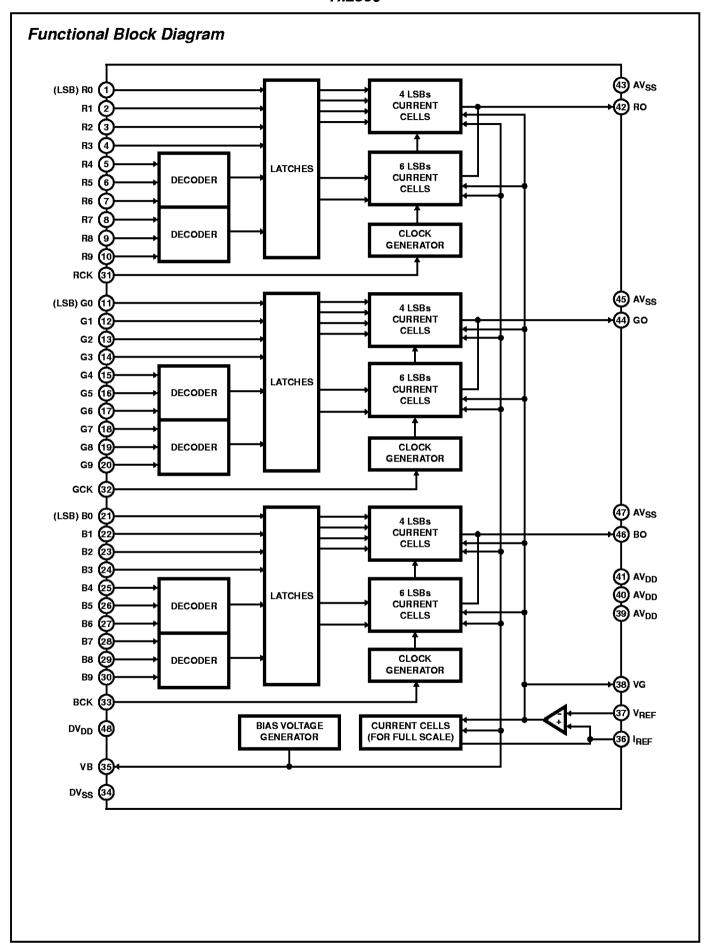

The HI2309 is a triple 10-bit, high-speed, CMOS D/A converter designed for video band use. It has three separate, 10-bit, pixel inputs, one each for red, green, and blue video data. A single 5.0V power supply and pixel clock input is all that is required to make the device operational. A bias voltage generator is internal. Each channel clock input can be controlled individually, or connected together as one. The HI2309 also has BLANK video control signal.

## Ordering Information

| PART<br>NUMBER | TEMP.<br>RANGE ( <sup>O</sup> C) | PACKAGE    | PKG. NO.    |  |

|----------------|----------------------------------|------------|-------------|--|

| HI2309JCQ      | -20 to 75                        | 48 Ld MQFP | Q48.12x12-S |  |

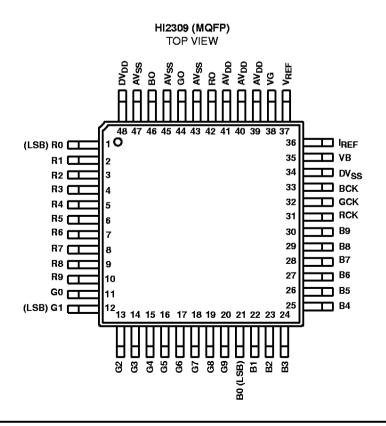

#### **Pinout**

| PIN NO.    | SYMBOL           | EQUIVALENT CIRCUIT                                 | DESCRIPTION                                                          |

|------------|------------------|----------------------------------------------------|----------------------------------------------------------------------|

| 1 to 10    | R0 to R9         | φ DV <sub>DD</sub>                                 | Digital Input.                                                       |

| 11 to 20   | G0 to G9         |                                                    |                                                                      |

| 21 to 30   | B0 to B9         | 1 TO 30 DV <sub>SS</sub>                           |                                                                      |

| 31         | RCLK             |                                                    | Clock pin.                                                           |

| 32         | GCLK             | → DV <sub>DD</sub>                                 |                                                                      |

| 33         | BCLK             | LaH                                                |                                                                      |

|            |                  | 31 TO 33 DV <sub>SS</sub>                          |                                                                      |

| 34         | DV <sub>SS</sub> |                                                    | Digital GND.                                                         |

| 35         | VB               | <b>₽</b> DV <sub>DD</sub>                          | Connect an approximately 0.1µF capacitor.                            |

|            |                  | 35 DV <sub>SS</sub>                                |                                                                      |

| 36         | REF              | AV <sub>DD</sub> • • AV <sub>DD</sub>              | Connect a "16R" resistor which is 16 times to output resistance "R". |

| 37         | V <sub>REF</sub> | <u> </u>                                           | Sets an output full scale value.                                     |

| 38         | VG               | AV <sub>DD</sub> AV <sub>DD</sub> AV <sub>SS</sub> | Connect an approximately 0.1μF capacitor.                            |

| 39 to 41   | AV <sub>DD</sub> |                                                    | Analog V <sub>DD</sub> .                                             |

| 42         | RO               | AV <sub>DD</sub> <b>9</b>                          | Current Output. Output can be obtained by                            |

| 44         | GO               | _ <del>```</del>                                   | connecting a resistor (200 $\Omega$ typical).                        |

| 46         | ВО               | 44<br>46<br>AV <sub>SS</sub>                       |                                                                      |

| 43, 45, 47 | AV <sub>DD</sub> |                                                    | Analog GND.                                                          |

| 47, 48     | DV <sub>DD</sub> |                                                    | Digital V <sub>DD</sub> .                                            |

#### HI2309

### **Absolute Maximum Ratings** T<sub>A</sub> = 25°C

##

#### **Operating Conditions**

| Supply Voltage                                     |

|----------------------------------------------------|

| AV <sub>DD</sub> , AV <sub>SS</sub>                |

| DV <sub>DD</sub> , DV <sub>SS</sub> 4.75V to 5.25V |

| Reference Input Voltage (VREF)0.5V to 2.0V         |

| Clock Pulse Width                                  |

| t <sub>PW1</sub>                                   |

| t <sub>PW0</sub>                                   |

| Temperature Range (T <sub>OPR</sub> )20°C to 75°C  |

#### Thermal Information

| Thermal Resistance (Typical, Note 1)           | θ <sub>JA</sub> ( <sup>o</sup> C/W) |

|------------------------------------------------|-------------------------------------|

| MQFP Package                                   | 94                                  |

| Maximum Junction Temperature (Plastic Package) | 150°C                               |

| Maximum Storage Temperature Range              | 65°C to 150°C                       |

| Maximum Lead Temperature (Soldering 10s)       | 300°C                               |

| (Lead Tips Only)                               |                                     |

|                                                |                                     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications  $f_{CLK} = 50MHz$ ,  $V_{DD} = 5V$ ,  $R = 200\Omega$ ,  $V_{REF} = 2.0V$ ,  $T_A = 25^{\circ}C$

| PARAMETER                                 |            | SYMBOL          | TEST CONDITIONS                               | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|------------|-----------------|-----------------------------------------------|------|------|------|-------|

| Resolution                                |            | n               |                                               | -    | 10   | -    | Bit   |

| Maximum Conversion Speed                  |            | fMAX            |                                               | 50   | -    | -    | MHz   |

| Linearity Error                           |            | EL              |                                               | -2.0 | -    | 2.0  | LSB   |

| Differential Linearity Error              |            | E <sub>D</sub>  |                                               | -0.5 | -    | 0.5  | LSB   |

| Output Full Scale Voltage                 |            | V <sub>FS</sub> |                                               | 1.8  | 1.92 | 2.0  | ٧     |

| Output Full Scale Current                 |            | I <sub>FS</sub> |                                               | 9.0  | 9.6  | 10   | mA    |

| Output Offset Voltage                     |            | Vos             |                                               | -    | -    | 1    | mV    |

| Supply Current                            |            | I <sub>DD</sub> |                                               | -    | 40   | 50   | mA    |

| Digital Input Current                     | High Level | ۱н              |                                               | -    | -    | 5    | μΑ    |

|                                           | Low Level  | I <sub>IL</sub> |                                               | -5   | -    | -    | μΑ    |

| Digital Input Voltage                     | High Level | V <sub>IH</sub> | DV <sub>DD</sub> = 4.75 to 5.25V              | 2.15 | -    | -    | ٧     |

|                                           | Low Level  | V <sub>IL</sub> | DV <sub>DD</sub> - 4.75 to 5.25V              | -    | -    | 0.85 | ٧     |

| Precision Guaranteed Output Voltage Range |            | Voc             |                                               | 1.8  | 1.92 | 2.0  | ٧     |

| Setup Time                                |            | ts              |                                               | 6    | -    | -    | ns    |

| Hold Time                                 |            | t <sub>H</sub>  |                                               | 3    | -    | -    | ns    |

| Propagation Delay Time                    |            | t <sub>PD</sub> |                                               | -    | 14   | -    | ns    |

| Glitch Energy                             |            | GE              | For $R_{OUT} = 100\Omega$ , $1V_{P-P}$ Output | -    | 50   | -    | pV/s  |

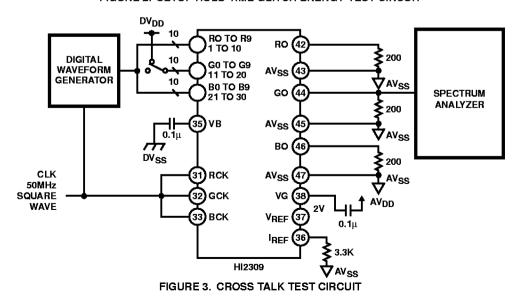

| Cross Talk                                |            | СТ              | For 10MHz Sine Wave Output                    | 40   | 42   | -    | dB    |

| SNR                                       |            | SNR             | For 1MHz Sine Wave Output                     | 50   | 55   | -    | dB    |

NOTE:

2. Output full scale ratio = Full scale voltage for each channel

Average of full scale voltage for each channel

1 x 100%

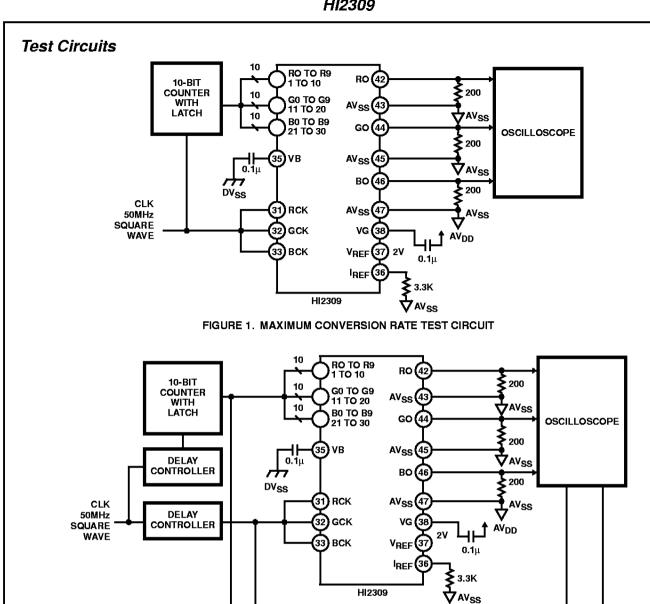

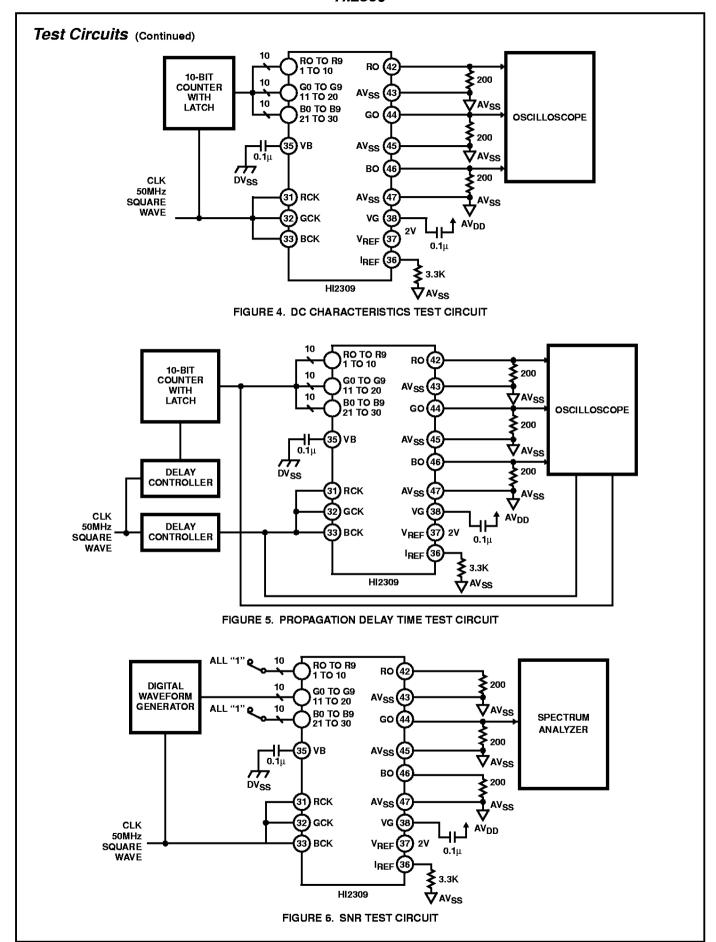

FIGURE 2. SETUP HOLD TIME GLITCH ENERGY TEST CIRCUIT

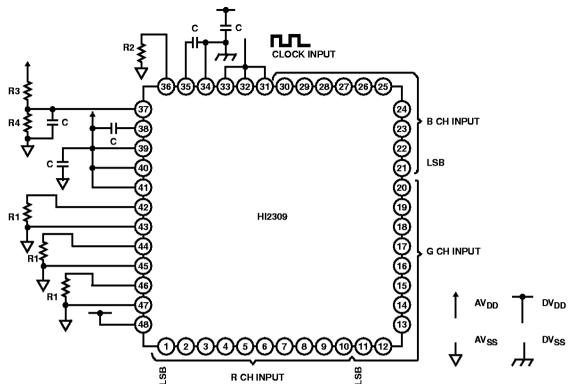

## **Application Circuit**

- When the power supply (AV $_{DD}$  and DV $_{DD}$  is 5.0.

- R1 200Ω.

- R2 =  $3.3k\Omega$ .

- R3 =  $3.0k\Omega$ .

- $R4 = 2.0k\Omega$ .

- $C = 0.1 \mu F$ .

Application circuits shown are typical examples illustrating the operation of the devices. Harris cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

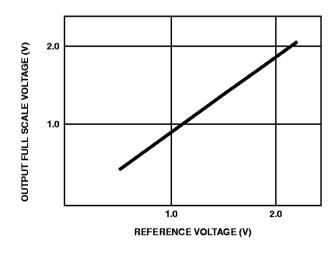

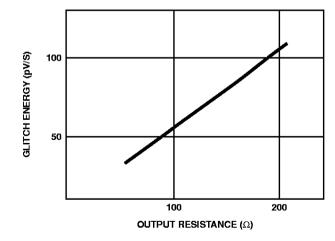

## **Typical Performance Curves**

FIGURE 7. OUTPUT FULL SCALE VOLTAGE vs REFERENCE VOLTAGE

FIGURE 8. OUTPUT RESISTANCE vs GLITCH ENERGY

#### Typical Performance Curves (Continued)

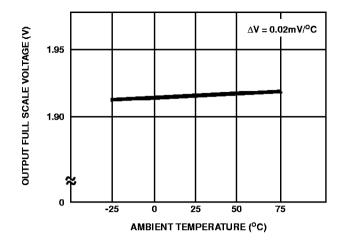

FIGURE 9. OUTPUT FULL SCALE VOLTAGE vs AMBIENT TEMPERATURE

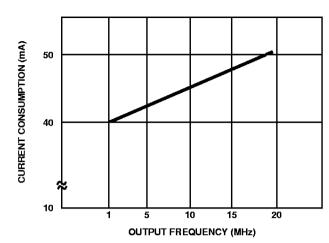

FIGURE 10. OUTPUT FREQUENCY vs CURRENT CONSUMPTION

# Standard Measurement Conditions and Description

$V_{DD} = 5.0 V.$

$V_{REF} = 2.0V.$

$R = 200\Omega$ .

$16R = 3.3k\Omega$ .

$T_A = 25$ °C.

V<sub>RFF</sub> in Figure 9 is fixed to 2V<sub>DC</sub> without resistor dividing.

Input data in Figure 10 = all "0" and "1" of rectangular wave, clock frequency = 50MHz for a total value of three channels.

## Notes On Operation

Selecting the Output Resistance:

HI2309 is a current output type D/A converter. To create the output voltage, connect the resistor to the current output pin.

Specifications:

Output full scale voltage VFS Max = 2.0 [V].

Output full scale current IFS Max = 10 [mA].

Calculate the output resistance from  $V_{FS} = I_{FS} x R$ . Connect a resistance sixteen times the output resistance to the reference current pin  $I_{REF}$ . In some cases, this value may not exist, a similar value can be used instead.

Note that the V<sub>FS</sub> will be the following:

$V_{FS} = V_{REF} \times 16 \text{ R/R}'$ .

R is the resistor to be connected to the IO and R' is the resistor to be connected to the  $I_{REF}$ . Power consumption can be reduced by increasing the resistance, but this will on the contrary, increase the glitch energy and data setting time. Set the best values according to the purpose of use.

Correlation Between Data and Clock:

For HI2309 to display the desired performance as a D/A converter, the data transmitted from outside and the clock must be synchronized properly. Adjust the setup time ( $t_{\rm H}$ ) and hold time ( $t_{\rm H}$ ) as specified in "Electrical Characteristics."

VDD, VSS:

Separate the analog and digital signals around the device to reduce noise effects. Bypass the  $V_{DD}$  pin to each GND with a  $0.1\mu F$  ceramic capacitor as near as possible to the pin for both digital and analog signals.

Latch Up:

The  $AV_{DD}$  and  $DV_{DD}$  pins must be able to share the same power supply of the board. This is to prevent latch up caused by potential difference between the two pins when the power is turned on.

IREF Pin:

The I<sub>REF</sub> pin is very sensitive to improve the AC Characteristics. Pay attention for capacitance component not to attach to this pin because its output may become unstable.

VG Pin:

It is recommended to use a 1 $\mu$ F capacitor to improve the AC Characteristics, though the typical capacitance value externally connected to the  $V_G$  Pin is 0.1 $\mu$ F.