# 3.3V ZERO DELAY CLOCK BUFFER, SPREAD SPECTRUM COMPATIBLE

#### FEATURES:

- Phase-Lock Loop Clock Distribution

- 10MHz to 200MHz operating frequency

- · Distributes one clock input to one bank of five outputs

- · Zero Input-Output Delay

- · Output Skew < 250ps

- Low jitter <200 ps cycle-to-cycle

- IDT23S05E-1 for Standard Drive

- IDT23S05E-1H for High Drive

- No external RC network required

- Operates at 3.3V VDD

- Power down mode

- Spread spectrum compatible

- · Available in SOIC package

### **DESCRIPTION:**

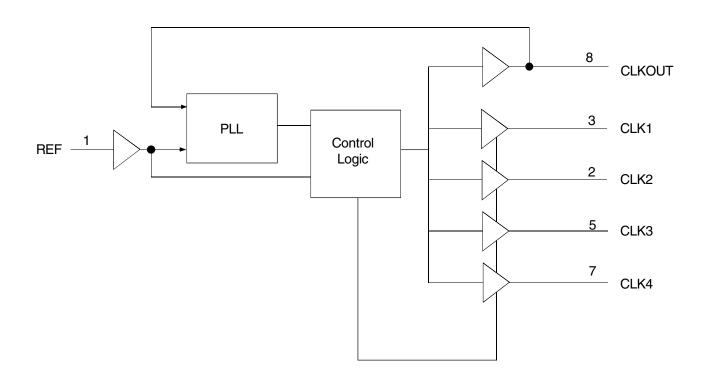

The IDT23S05E is a high-speed phase-lock loop (PLL) clock buffer, designed to address high-speed clock distribution applications. The zero delay is achieved by aligning the phase between the incoming clock and the output clock, operable within the range of 10 to 200MHz.

The IDT23S05E is an 8-pin version of the IDT23S09E. IDT23S05E accepts one reference input, and drives out five low skew clocks. The -1H version of this device operates up to 200MHz frequency and has a higher drive than the -1 device. All parts have on-chip PLLs which lock to an input clock on the REF pin. The PLL feedback is on-chip and is obtained from the CLKOUT pad. In the absence of an input clock, the IDT23S05E enters power down. In this mode, the device will draw less than 12µA for Commercial Temperature range and less than 25µA for Industrial temperature range, the outputs are tri-stated, and the PLL is not running, resulting in a significant reduction of power.

The IDT23S05E is characterized for both Industrial and Commercial operation.

## FUNCTIONAL BLOCK DIAGRAM

1

The IDT logo is a registered trademark of Integrated Device Technology, Inc

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

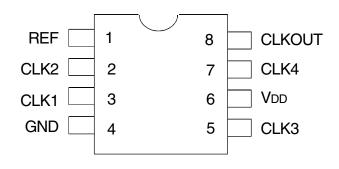

#### **PIN CONFIGURATION**

SOIC TOP VIEW

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol                        | Rating                    | Max.         | Unit |

|-------------------------------|---------------------------|--------------|------|

| Vdd                           | Supply Voltage Range      | -0.5 to +4.6 | V    |

| VI <sup>(2)</sup>             | Input Voltage Range (REF) | -0.5 to +5.5 | V    |

| VI                            | Input Voltage Range       | –0.5 to      | V    |

|                               | (except REF)              | VDD+0.5      |      |

| Iк (VI < 0)                   | Input Clamp Current       | -50          | mA   |

| Io (Vo = 0 to VDD)            | Continuous Output Current | ±50          | mA   |

| VDD or GND                    | Continuous Current        | ±100         | mA   |

| Ta = 55°C                     | Maximum Power Dissipation | 0.7          | W    |

| (in still air) <sup>(3)</sup> |                           |              |      |

| Tstg                          | Storage Temperature Range | -65 to +150  | °C   |

| Operating                     | CommercialTemperature     | 0 to +70     | °C   |

| Temperature                   | Range                     |              |      |

| Operating                     | Industrial Temperature    | -40 to +85   | °C   |

| Temperature                   | Range                     |              |      |

NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils.

### **APPLICATIONS:**

- SDRAM

- Telecom

- Datacom

- · PC Motherboards/Workstations

- · Critical Path Delay Designs

#### **PIN DESCRIPTION**

| Pin Name              | Pin Number | Туре   | Functional Description                       |

|-----------------------|------------|--------|----------------------------------------------|

| REF <sup>(1)</sup>    | 1          | IN     | Input reference clock, 5 Volt tolerant input |

| CLK2 <sup>(2)</sup>   | 2          | Out    | Output clock                                 |

| CLK1 <sup>(2)</sup>   | 3          | Out    | Output clock                                 |

| GND                   | 4          | Ground | Ground                                       |

| CLK3 <sup>(2)</sup>   | 5          | Out    | Output clock                                 |

| Vdd                   | 6          | PWR    | 3.3V Supply                                  |

| CLK4 <sup>(2)</sup>   | 7          | Out    | Output clock                                 |

| CLKOUT <sup>(2)</sup> | 8          | Out    | Output clock, internal feedback on this pin  |

NOTES:

1. Weak pull down.

2. Weak pull down on all outputs.

# **OPERATING CONDITIONS - COMMERCIAL**

| Symbol | Parameter                                   | Min. | Max. | Unit |

|--------|---------------------------------------------|------|------|------|

| Vdd    | Supply Voltage                              | 3    | 3.6  | V    |

| TA     | Operating Temperature (Ambient Temperature) | 0    | 70   | °C   |

| Cl     | Load Capacitance < 100MHz                   | —    | 30   | pF   |

|        | Load Capacitance 100MHz - 200MHz            | —    | 10   |      |

| Cin    | Input Capacitance                           | —    | 7    | pF   |

# DC ELECTRICAL CHARACTERISTICS - COMMERCIAL

| Symbol | Parameter                | 0                       | Conditions                   | Min. | Max. | Unit |

|--------|--------------------------|-------------------------|------------------------------|------|------|------|

| Vil    | Input LOW Voltage Level  |                         |                              | _    | 0.8  | V    |

| Vih    | Input HIGH Voltage Level |                         |                              | 2    | _    | V    |

| lil    | Input LOW Current        | VIN = 0V                |                              | _    | 50   | μA   |

| Ін     | Input HIGH Current       | VIN = VDD               | VIN = VDD                    |      | 100  | μA   |

| Vol    | Output LOW Voltage       | Standard Drive          | IOL = 8mA                    | _    | 0.4  | V    |

|        |                          | High Drive              | IOL = 12mA (-1H)             |      |      |      |

| Vон    | Output HIGH Voltage      | Standard Drive          | Iон = -8mA                   | 2.4  | _    | V    |

|        |                          | High Drive              | Іон = -12mA (-1H)            |      |      |      |

| DD_PD  | Power Down Current       | REF = 0MHz              |                              | _    | 12   | μA   |

| Idd    | Supply Current           | Unloaded Outputs at 66. | Unloaded Outputs at 66.66MHz |      | 32   | mA   |

# SWITCHING CHARACTERISTICS (23S05E-1) - COMMERCIAL<sup>(1,2)</sup>

| Symbol        | Parameter                                    | Conditions                                            | Min. | Тур. | Max. | Unit |

|---------------|----------------------------------------------|-------------------------------------------------------|------|------|------|------|

| tı            | Output Frequency                             | 10pFLoad                                              | 10   | _    | 200  | MHz  |

|               |                                              | 30pF Load                                             | 10   | —    | 100  |      |

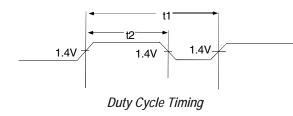

|               | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT = 66.66MHz                     | 40   | 50   | 60   | %    |

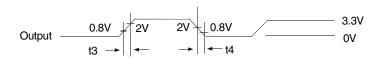

| t3            | RiseTime                                     | Measured between 0.8V and 2V                          | _    | —    | 2.5  | ns   |

| t4            | FallTime                                     | Measured between 0.8V and 2V                          | _    | —    | 2.5  | ns   |

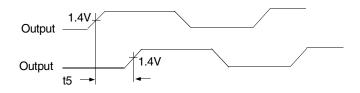

| ts            | Output to Output Skew                        | All outputs equally loaded                            | _    | —    | 250  | ps   |

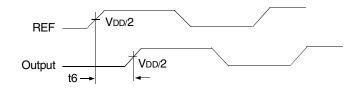

| t6            | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2                                     | _    | 0    | ±350 | ps   |

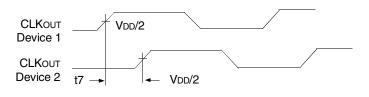

| đ             | Device-to-Device Skew                        | Measured at VDD/2 on the CLKOUT pins of devices       | _    | 0    | 700  | ps   |

| tı            | Cycle-to-Cycle Jitter, pk - pk               | Measured at 66.66MHz, loaded outputs                  | _    | _    | 200  | ps   |

| <b>t</b> LOCK | PLL Lock Time                                | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

NOTES:

1. REF Input has a threshold voltage of VDD/2.

2. All parameters specified with loaded outputs.

# SWITCHING CHARACTERISTICS (23S05E-1H) - COMMERCIAL

| Symbol        | Parameter                                    | Conditions                                            | Min. | Тур. | Max. | Unit |

|---------------|----------------------------------------------|-------------------------------------------------------|------|------|------|------|

| tı            | Output Frequency                             | 10pFLoad                                              | 10   | —    | 200  | MHz  |

|               |                                              | 30pF Load                                             | 10   | —    | 100  |      |

|               | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT = 66.66MHz                     | 40   | 50   | 60   | %    |

|               | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT <50MHz                         | 45   | 50   | 55   | %    |

| ß             | RiseTime                                     | Measured between 0.8V and 2V                          |      | _    | 1.5  | ns   |

| t4            | FallTime                                     | Measured between 0.8V and 2V                          |      | _    | 1.5  | ns   |

| ts            | Output to Output Skew                        | All outputs equally loaded                            | _    | _    | 250  | ps   |

| t6            | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2                                     | _    | 0    | ±350 | ps   |

| ħ             | Device-to-Device Skew                        | Measured at VDD/2 on the CLKOUT pins of devices       | _    | 0    | 700  | ps   |

| t8            | Output Slew Rate                             | Measured between 0.8V and 2V using Test Circuit #2    | 1    | _    | -    | V/ns |

| tı            | Cycle-to-Cycle Jitter, pk - pk               | Measured at 66.66MHz, loaded outputs                  | _    | _    | 200  | ps   |

| <b>t</b> LOCK | PLL Lock Time                                | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

NOTES:

1. REF Input has a threshold voltage of VDD/2.

2. All parameters specified with loaded outputs.

# **OPERATING CONDITIONS - INDUSTRIAL**

| Symbol | Parameter                                   | Min. | Max. | Unit |

|--------|---------------------------------------------|------|------|------|

| Vdd    | SupplyVoltage                               | 3    | 3.6  | V    |

| TA     | Operating Temperature (Ambient Temperature) | -40  | +85  | °C   |

| Cl     | Load Capacitance < 100MHz                   | —    | 30   | pF   |

|        | Load Capacitance 100MHz - 200MHz            | —    | 10   |      |

| Cin    | InputCapacitance                            | _    | 7    | pF   |

## DC ELECTRICAL CHARACTERISTICS - INDUSTRIAL

| Symbol | Parameter                | C                       | Conditions        | Min. | Max. | Unit |

|--------|--------------------------|-------------------------|-------------------|------|------|------|

| VIL    | Input LOW Voltage Level  |                         |                   | —    | 0.8  | V    |

| Vih    | Input HIGH Voltage Level |                         |                   | 2    | _    | V    |

| ١L     | Input LOW Current        | VIN = 0V                |                   | —    | 50   | μA   |

| Ін     | Input HIGH Current       | VIN = VDD               | VIN = VDD         |      | 100  | μA   |

| Vol    | OutputLOWVoltage         | Standard Drive          | Iol = 8mA         | —    | 0.4  | V    |

|        |                          | High Drive              | IOL = 12mA (-1H)  |      |      |      |

| Vон    | Output HIGH Voltage      | Standard Drive          | Іон = -8mA        | 2.4  | —    | V    |

|        |                          | High Drive              | Іон = -12mA (-1H) |      |      |      |

| IDD_PD | Power Down Current       | REF = 0MHz              |                   | —    | 25   | μA   |

| IDD    | Supply Current           | Unloaded Outputs at 66. | 66MHz             | _    | 35   | mA   |

# SWITCHING CHARACTERISTICS (23S05E-1) - INDUSTRIAL<sup>(1,2)</sup>

| Symbol | Parameter                                    | Conditions                                            | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------------|-------------------------------------------------------|------|------|------|------|

| tı     | Output Frequency                             | 10pF Load                                             | 10   | _    | 200  | MHz  |

|        |                                              | 30pF Load                                             | 10   | _    | 100  |      |

|        | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT = 66.66MHz                     | 40   | 50   | 60   | %    |

| t3     | RiseTime                                     | Measured between 0.8V and 2V                          | _    | —    | 2.5  | ns   |

| t4     | FallTime                                     | Measured between 0.8V and 2V                          | _    | —    | 2.5  | ns   |

| ts     | Output to Output Skew                        | All outputs equally loaded                            | _    | —    | 250  | ps   |

| t6     | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2                                     |      | 0    | ±350 | ps   |

| ħ      | Device-to-Device Skew                        | Measured at VDD/2 on the CLKOUT pins of devices       | _    | 0    | 700  | ps   |

| tı     | Cycle-to-Cycle Jitter, pk - pk               | Measured at 66.66MHz, loaded outputs                  | _    | —    | 200  | ps   |

| tlocк  | PLL Lock Time                                | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

NOTES:

1. REF Input has a threshold voltage of VDD/2.

2. All parameters specified with loaded outputs.

# SWITCHING CHARACTERISTICS (23S05E-1H) - INDUSTRIAL<sup>(1,2)</sup>

| Symbol        | Parameter                                    | Conditions                                            | Min. | Тур. | Max. | Unit |

|---------------|----------------------------------------------|-------------------------------------------------------|------|------|------|------|

| tı            | Output Frequency                             | 10pFLoad                                              | 10   | —    | 200  | MHz  |

|               |                                              | 30pF Load                                             | 10   | _    | 100  |      |

|               | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT = 66.66MHz                     | 40   | 50   | 60   | %    |

|               | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT <50MHz                         | 45   | 50   | 55   | %    |

| t3            | RiseTime                                     | Measured between 0.8V and 2V                          | _    | _    | 1.5  | ns   |

| t4            | FallTime                                     | Measured between 0.8V and 2V                          | _    | _    | 1.5  | ns   |

| ts            | Output to Output Skew                        | All outputs equally loaded                            | _    | _    | 250  | ps   |

| t6            | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2                                     | _    | 0    | ±350 | ps   |

| tz            | Device-to-Device Skew                        | Measured at VDD/2 on the CLKOUT pins of devices       | _    | 0    | 700  | ps   |

| t8            | Output Slew Rate                             | Measured between 0.8V and 2V using Test Circuit #2    | 1    | _    | _    | V/ns |

| tı            | Cycle-to-Cycle Jitter, pk - pk               | Measured at 66.66MHz, loaded outputs                  | _    | _    | 200  | ps   |

| <b>t</b> LOCK | PLL Lock Time                                | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

NOTES:

1. REF Input has a threshold voltage of VDD/2.

2. All parameters specified with loaded outputs.

### **ZERO DELAY AND SKEW CONTROL**

All outputs should be uniformly loaded in order to achieve Zero I/O Delay. Since the CLKOUT pin is the internal feedback for the PLL, its relative loading can affect and adjust the input/output delay.

For designs utilizing zero I/O Delay, all outputs including CLKOUT must be equally loaded. Even if the output is not used, it must have a capacitive load equal to that on the other outputs in order to obtain true zero I/O Delay. For zero output-to-output skew, all outputs must be loaded equally.

## SPREAD SPECTRUM COMPATIBLE

Many systems being designed now use a technology called Spread Spectrum Frequency Timing Generation. This product is designed not to filter off the Spread Spectrum feature of the reference input, assuming it exists. When a zero delay buffer is not designed to pass the Spread Spectrum feature through, the result is a significant amount of tracking skew, which may cause problems in systems requiring synchronization.

### SWITCHING WAVEFORMS

All Outputs Rise/Fall Time

Output to Output Skew

Input to Output Propagation Delay

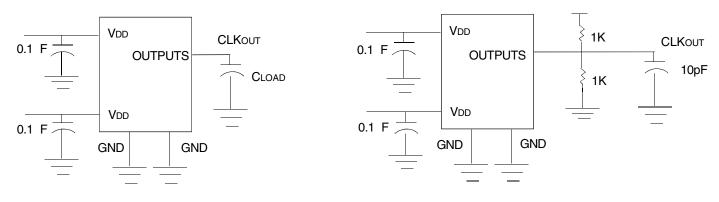

## **TEST CIRCUITS**

Test Circuit 1 (all Parameters Except t8)

Test Circuit 2 (t8, Output Slew Rate On -1H Devices)

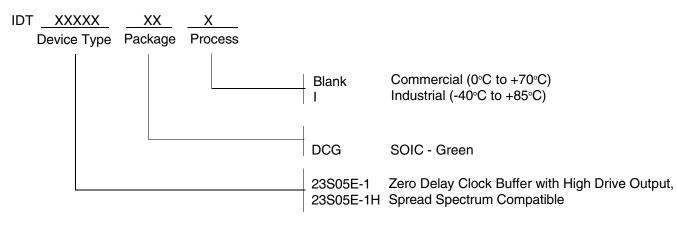

### **ORDERING INFORMATION**

| Part / Order Number | Shipping Packaging | Package    | Temperature   |

|---------------------|--------------------|------------|---------------|

|                     |                    |            |               |

| 23S05E-1DCG         | Tubes              | 8-pin SOIC | 0° to +70° C  |

| 23S05E-1DCG8        | Tape and Reel      | 8-pin SOIC | 0° to +70° C  |

| 23S05E-1DCGI        | Tubes              | 8-pin SOIC | -40° to +85°C |

| 23S05E-1DCGI8       | Tape and Reel      | 8-pin SOIC | -40° to +85°C |

| 23S05E-1HDCG        | Tubes              | 8-pin SOIC | 0° to +70° C  |

| 23S05E-1HDCG8       | Tape and Reel      | 8-pin SOIC | 0° to +70° C  |

| 23S05E-1HDCGI       | Tubes              | 8-pin SOIC | -40° to +85°C |

| 23S05E-1HDCGI8      | Tape and Reel      | 8-pin SOIC | -40° to +85°C |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.