## 1.5MHz, 2A Synchronous Step-Down Converter

### **General Description**

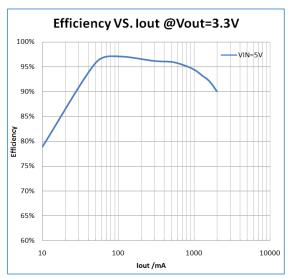

The LP3202 is a 1.5MHz constant frequency current mode PWM step-down converter. integrates main switch and synchronous rectifier switch. The LP3201 integrates two operation modes, PWM control and PFM mode switching control, which allows a high efficiency over the wider range of the load. It is ideal for portable equipment which requires very high current up to 2.0A from single-cell Lithium-ion batteries while still achieving over 96% efficiency during peak load conditions. The LP3202 also can run at 100% duty cycle for low dropout operation, extending battery life in portable systems while light load operation provides very low output ripple for noisy sensitive applications.

The LP3202 can supply up to 2.0A output load current from at  $V_{\rm IN}$  = 3V and has an input voltage 2.5V to 6V and the output voltage can be regulated as low as 0.61V. The high switching frequency minimizes the size of external components while keeping switching losses low. The internal slope compensation setting allows the device to operate with smaller inductor values to optimize size and provide efficient operation. The device is available in a Pb-free SOT23-5 package and is rated over the temperature range of -40°C to +85°C.

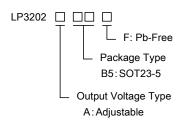

## **Order Information**

### **Features**

- ◆ Input Voltage Range: 2.5V to 6V

- Output Voltage Range: 0.61V to VIN

- ◆ 2.0A Output Current

- ♦ Low R(DSON) Internal Switches:80mΩ/70mΩ

- ♦ High Efficiency: Up to 96%

- ◆ 100% Duty Cycle in Dropout

- ♦ Low Shutdown Current: <1uA</p>

- ♦ 1.5MHz Switching Frequency

- ◆ Soft-star Function

- Short Circuit Protection

- ◆ Thermal Fault Protection

- ♦ SOT23-5Package

- ◆ RoHS Compliant and 100% Lead (Pb)-Free

## **Applications**

- ♦ Portable Instruments

- ♦ DSP Core Supplies

- ♦ Cellular Phone and Smart mobile phone

- ♦ PDA

- ♦ GPS Applications

### **Marking Information**

| Device                                                 | Marking      | Package | Shipping |  |

|--------------------------------------------------------|--------------|---------|----------|--|

| LP3202AB5F                                             | LPS<br>AJYWX | SOT23-5 | 3K/REEL  |  |

| Marking indication:                                    |              |         |          |  |

| Y:Production year W:Production week X:Production batch |              |         |          |  |

LP3202-06 S

Sep. -2022

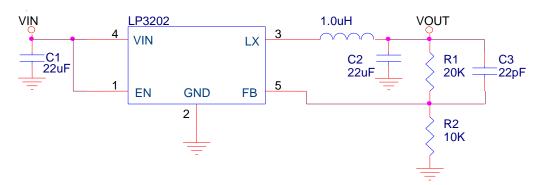

# **Typical Application Circuit**

# **Functional Pin Description**

| Package Type | Pin Configurations  |  |  |

|--------------|---------------------|--|--|

|              | Top View            |  |  |

|              | EN 1 5 FB           |  |  |

| SOT23-5      | GND 2               |  |  |

|              | LPSemi LOWA 3 4 VIN |  |  |

|              | 微源平导体               |  |  |

# **Pin Description**

| Pin | Name | Description                                                                                                                     |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------|

| 1   | EN   | Enable pin. Active high. There is an internal 500K resistor pull down when EN is floating.                                      |

| 2   | GND  | Ground.                                                                                                                         |

| 3   | LX   | Switch Mode Connection to Inductor. This pin connects to the drains of the internal main and synchronous power MOSFET switches. |

| 4   | Vin  | Supply Input. Power supply input pin. Must be closely decoupled to AGND with a 22µF or greater ceramic capacitor.               |

| 5   | FB   | Feedback Input. Connect FB to the center point of the external resistor divider. Normal voltage for this pin is 0.6V.           |

LP3202-06

Sep. -2022

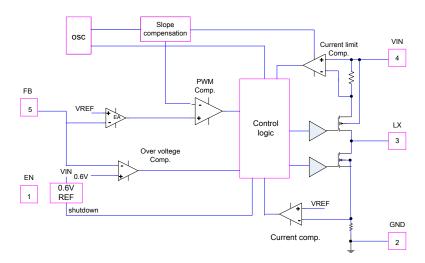

### **Function Diagram**

# Absolute Maximum Ratings Note 1

| <b></b> | VIN , LX to GND                                        |

|---------|--------------------------------------------------------|

| <b></b> | LX to GND (5nS transient)                              |

| <b></b> | Other pin Voltage to GND                               |

| <b></b> | Maximum Junction Temperature 150°C                     |

| <b></b> | Operating Ambient Temperature Range (T <sub>A</sub> )  |

| <b></b> | Storage Temperature Range ( $T_J$ )                    |

| <b></b> | Maximum Soldering Temperature (at leads, 10 sec) 260°C |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Information**

- ♦ Thermal Resistance (SOT23-5, θ<sub>JA</sub>) ------ 250℃/W

## **ESD Susceptibility**

- ♦ HBM(Human Body Mode) ------ 2KV

- ♦ MM(Machine Mode) ------ 200V

### **Electrical Characteristics**

(L=1uH,  $C_{IN}$ =22uF,  $C_{OUT}$ =22uF,  $V_{IN}$  = $V_{EN}$ =5V, Typical values are  $T_A$ =25  $^{\circ}$ C )

| Symbol               | Parameter                           | Condition                                                             | Min   | Тур | Max   | Units      |

|----------------------|-------------------------------------|-----------------------------------------------------------------------|-------|-----|-------|------------|

| V <sub>IN</sub>      | Input Voltage                       |                                                                       | 2.5   |     | 6     | V          |

| V <sub>UVLO</sub>    | Under voltage Lockout Threshold     | VIN falling                                                           | 1.7   |     | 2.4   | V          |

| V <sub>OUT</sub>     | Output Voltage Range                |                                                                       | 0.61  |     | VIN   | V          |

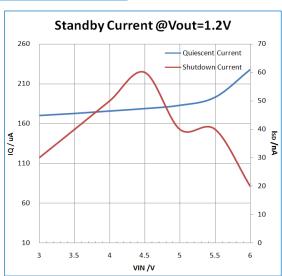

| IQ                   | Quiescent Current                   | V <sub>FB</sub> =0.7V                                                 |       | 150 |       | μΑ         |

| I <sub>SHDN</sub>    | Shutdown Current                    | EN=GND                                                                |       |     | 1     | μΑ         |

| I <sub>LIM</sub>     | P-Channel Current Limit             |                                                                       | 2.5   | 4   | 5.5   | Α          |

| R <sub>DS(ON)H</sub> | High-Side Switch On Resistance      |                                                                       |       | 80  |       | mΩ         |

| R <sub>DS(ON)L</sub> | Low-Side Switch On Resistance       |                                                                       |       | 70  |       | mΩ         |

| Isw_LEAK             | SW Leakage Current                  | V <sub>EN</sub> =0V,<br>V <sub>SW</sub> =0 or 5V, V <sub>IN</sub> =5V |       | 1   |       | μА         |

| V <sub>FB</sub>      | Feedback Threshold Voltage Accuracy | <b>MLOMEL26</b> 1                                                     | 0.588 | 0.6 | 0.612 | V          |

| I <sub>FB</sub>      | FB Leakage Current                  | V <sub>FB</sub> =1.0V                                                 | 太     | 30  |       | nA         |

| Fosc                 | Oscillator Frequency                | , 443× 1 ×3 1                                                         |       | 1.5 |       | MHz        |

| ts                   | Startup Time                        | From Enable to Output Regulation                                      |       | 110 |       | μs         |

| T <sub>SD</sub>      | Over-Temperature Shutdown Threshold |                                                                       |       | 150 |       | $^{\circ}$ |

| V <sub>EN(L)</sub>   | Enable Threshold Low                |                                                                       |       |     | 0.4   | V          |

| V <sub>EN(H)</sub>   | Enable Threshold High               |                                                                       | 1.4   |     |       | V          |

| I <sub>EN</sub>      | Input Low Current                   | V <sub>EN</sub> =5.0V                                                 |       | 10  |       | μA         |

Note: Output Voltage:  $V_{OUT} = 0.6 \times (1 + R_1/R_2)$  Volts;

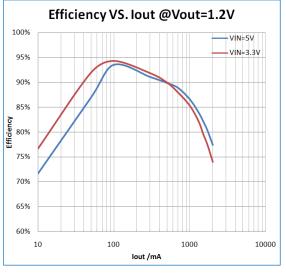

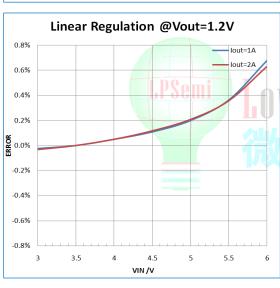

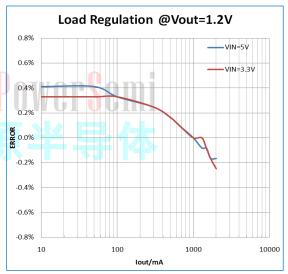

## **Typical Operating Characteristics**

$(V_{IN}=V_{EN}=5V,L=1uH,C_{IN}=22uF,C_{OUT}=22uF,C_{FB}=22pF,T_A=25\%$ , unless otherwise noted)

LP3202-06

Sep. -2022

Fm

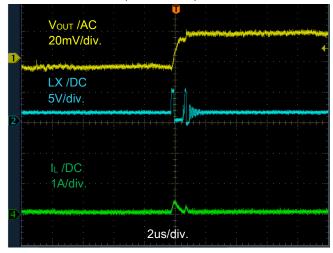

### **Output Ripple**

V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>=0A

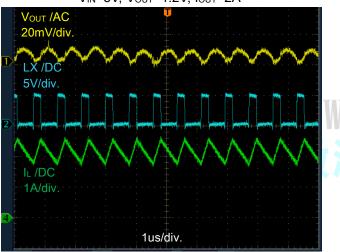

### **Output Ripple**

V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>=2A

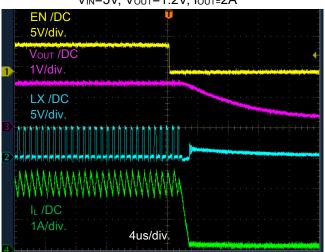

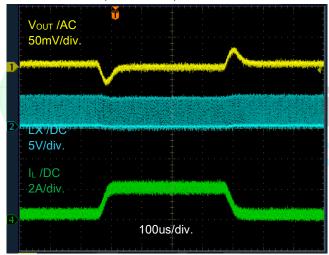

#### **EN Shutdown Waveform**

V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>=2A

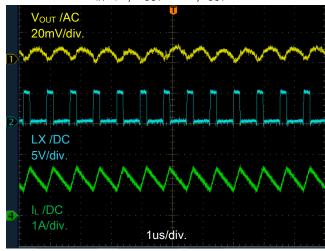

### **Output Ripple**

V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>=1A

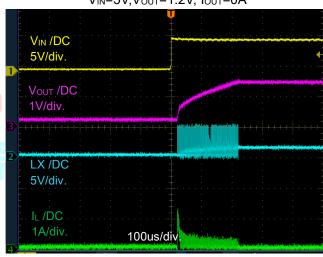

### **VIN Power Up**

V<sub>IN</sub>=5V,V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>=0A

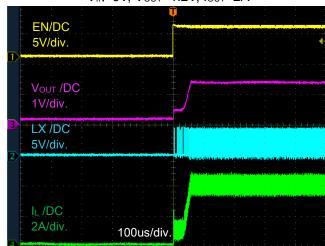

### **Power On from EN**

V<sub>IN</sub>=5V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>=2A

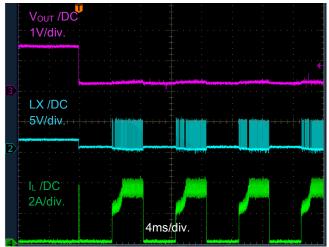

### **Over current Waveform**

$V_{IN}$ =5V,  $V_{OUT}$ =1.2V,  $R_{LOAD}$ =0.01 $\Omega$

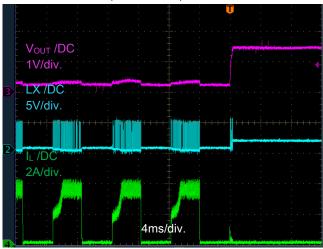

### **Over current Release Waveform**

VIN=5V,  $V_{OUT}$ =1.2V,  $R_{LOAD}$ =0.01 $\Omega$

### **Load Transient Response**

$V_{IN}$ =5V,  $V_{OUT}$ =1.2V,  $I_{OUT}$ =0.3A ~ 2A

### **Functional Description**

The LP3202 is a high output current monolithic switch-mode step-down DC-DC converter. The device operates at a fixed 1.5MHz switching frequency, and uses a slope compensated current mode architecture.

This step-down DC-DC converter can supply up to 2A output current from at VIN = 3V and has an input voltage range from 2.5V to 6V. It minimizes external component size and optimizes efficiency at the heavy load range. The slope compensation allows the device to remain stable over a wider range of inductor values so that smaller values (1µH to 4.7µH) with lower DCR can be used to achieve higher efficiency. Apart from the small bypass input capacitor, only a small L-C filter is required at the output. The device can be programmed with external feedback to any voltage, ranging from 0.61V to near the input voltage. It uses internal MOSFETs to achieve high efficiency and can generate very low output voltages by using an internal reference of 0.6V. At dropout, the converter duty cycle increases to 100% and the output voltage tracks the input voltage minus the low RDS (ON) drop of the P-channel high-side MOSFET and the inductor DCR.

The internal error amplifier and compensation provides excellent transient response, load and line regulation. Internal soft start eliminates any output voltage over-shoot when the enable or the input voltage is applied.

#### **Current Mode PWM Control**

Slope compensated current mode PWM control provides stable switching and cycle-by-cycle current limit for excellent load and line response with protection of the internal main switch (P-channel MOSFET) and synchronous rectifier (N-channel MOSFET). During normal operation, the internal P-channel MOSFET is turned on for a specified time to ramp the inductor current at each rising edge of the internal oscillator, and switched off when the peak inductor current is above the error volt-age. The current comparator limits the peak inductor current. When the main switch is off, the synchronous rectifier turns on immediately and stays on until either the inductor current starts to reverse, as indicated by the current reversal comparator or the beginning of the next clock cycle.

#### **Control Loop**

The LP3202 is a peak current mode step-down converter. The current through the P-channel MOSFET (high side) is sensed for current loop control, as well as short circuit and overload protection. A slope compensation signal is added to the sensed current to maintain stability for duty cycles greater than 50%. The peak current mode loop appears as a voltage-programmed current source in parallel with the output capacitor. The output of the voltage error amplifier programs the current mode loop for the necessary peak switch current to force a constant output voltage for all load and line conditions. Internal loop compensation terminates the trans-conductance voltage error amplifier output. The error amplifier reference is fixed at 0.6V.

#### Soft Start / Enable

Soft start limits the current surge seen at the input and eliminates output voltage overshoot. The enable pin is active high. When pulled low, the enable input (EN) forces the LP3202 into a low-power, non-switching state. The total input current during shutdown is less than  $1\mu A$ .

#### **Current Limit and Over-Temperature Protection**

For overload conditions, the peak input current is limited to 4A. To minimize power dissipation and stresses under current limit and short-circuit conditions, switching is terminated after entering current limit for a series of pulses. The termination lasts for seven consecutive clock cycles after a current limit has been sensed during a series of four consecutive clock cycles.

Thermal protection completely disables switching when internal dissipation becomes excessive. The junction over-temperature threshold is 150°C with 10°C of hysteresis. Once an over-temperature or over-current fault conditions is removed, the output voltage automatically recovers.

### **Dropout Operation**

When the battery input voltage decreases near the value of the output voltage, the LP3202 allows the main switch to remain on for more than one switching cycle and increases the duty cycle until it reaches 100%. The duty cycle D of a step-down converter is defined as:

$$D = T_{ON} \cdot F_{OSC} \cdot 100\% \approx \frac{V_{OUT}}{V_{IN}} \cdot 100\%$$

Where Ton is the main switch on time and FOSC is the oscillator frequency. The output voltage then is the input voltage minus the voltage drop across the main switch and the inductor. At low input supply voltage, the R<sub>DS(ON)</sub> of the P-channel MOSFET increases, and the efficiency of the converter decreases. Caution must be exercised to ensure the heat dissipated does not exceed the maximum junction temperature of the IC.

#### **Maximum Load Current**

The LP3202 will operate with an input supply voltage as low as 2.5V, however, the maximum load current decreases at lower input voltages due to a large IR drop on the main switch and synchronous rectifier. The slope compensation signal reduces the peak inductor current as a function of the duty cycle to prevent sub-harmonic oscillations at duty cycles greater than 50%. Conversely, the current limit increases as the duty cycle decreases.

#### **Setting the Output Voltage**

The LP3202 can be externally programmed. Resistors R1 and R2 program the output to regulate at a voltage higher than 0.6V. To limit the bias current required for the external feedback resistor string while maintaining good noise immunity, the minimum suggested value for R2 is  $10k\Omega$ . Although a larger value will further reduce quiescent current, it will also increase the impedance of the feedback node, making it more sensitive to external noise and interference. The LP3202 delivers enhanced transient response for extreme pulsed load applications. The addition of the feed forward capacitor CFB typically requires a larger output capacitor Cout for stability. The external resistor sets the output voltage according to the following equation:

$$V_{OUT}=0.6V\times(1+R_1/R_2)$$

$$R_1 = (V_{OUT}/0.6V-1) \times R_2$$

#### **Inductor Selection**

For most designs, the LP3202 operates with inductor values of 1µH to 4.7µH. Low inductance values are physically smaller but require faster switching, which results in some efficiency loss. The inductor value can be derived from the following equation:

$$L = \frac{V_{OUT} \cdot (V_{IN} - V_{OUT})}{V_{IN} \cdot \Delta I_{L} \cdot f_{OSC}}$$

Where AIL is inductor ripple current. Large value inductors lower ripple current and small value inductors result in high ripple currents. Choose inductor ripple current approximately 60% of the maximum load current 2A, or

$$\Delta I_L=1.2A$$

For output voltages above 2.0V, when light-load efficiency is important, the minimum recommended inductor is 1µH. Manufacturer's specifications list both the inductor DC current rating, which is a thermal limitation, and the peak current rating, which is determined by the saturation characteristics. The inductor should not show any appreciable saturation under normal load conditions. Some inductors may meet the peak and average current ratings yet result in excessive losses due to a high DCR.

Always consider the losses associated with the DCR and its effect on the total converter efficiency when selecting an inductor. For optimum voltage-positioning load transients, choose an inductor with DC series resistance in the 20mΩ to  $100m\Omega$  range. For higher efficiency at heavy loads (above 200mA), or minimal load regulation (but some transient overshoot), the resistance should be kept below  $100m\Omega$ . The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation (2A+600A).

LP3202-06

Sep. -2022

Email: marketing@lowpowersemi.com

www.lowpowersemi.com

#### **Output Capacitor Selection**

The function of output capacitance is to store energy to attempt to maintain a constant voltage. The energy is stored in the capacitor's electric field due to the voltage applied.

The value of output capacitance is generally selected to limit output voltage ripple to the level required by the specification. Since the ripple current in the output inductor is usually determined by L, Vout and VIN, the series impedance of the capacitor primarily determines the output voltage ripple. The three elements of the capacitor that contribute to its impedance (and output voltage ripple) are equivalent series resistance (ESR), equivalent series inductance (ESL), and capacitance (C). The output voltage droop due to a load transient is dominated by the capacitance of the ceramic output capacitor. During a step increase in load current, the ceramic output capacitor alone supplies the load current until the loop responds. Within several switching cycles, the loop responds and the inductor current increases to match the load current demand.

In many practical designs, to get the required ESR, a capacitor with much more capacitance than is needed must be selected. For continuous or discontinuous inductor current mode operation, the ESR of the Cout needed to limit the ripple to  $\Delta VO$ :

$$ESR \le \frac{\Delta V_O}{\Delta I_L}$$

Ripple current flowing through a capacitor's ESR causes power dissipation in the capacitor. This power dissipation causes a temperature increase internal to the capacitor. Excessive temperature can seriously shorten the expected life of a capacitor. Capacitors have rippled current ratings that are dependent on ambient temperature and should not be exceeded. The output capacitor ripple current is the inductor current, IL, minus the output current, Io. The RMS value of the ripple current flowing in the output capacitance (continuous inductor current mode operation) is given by:

$$I_{CRMS} = I_{O} \times \sqrt{\frac{D}{1 - D}}$$

ESL can be a problem by causing ringing in the low megahertz region but can be controlled by choosing low ESL capacitors, limiting lead length (PCB and capacitor), and replacing one large device with several smaller ones connected in parallel. In conclusion, in order to meet the requirement of out-put voltage ripple small and regulation loop stability, ceramic capacitors with X5R or X7R dielectrics are recommended due to their low ESR and high ripple current ratings. The output ripple VOUT is determined by:

$$\Delta V_{OUT} \le \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{OSC} \times L} \times (ESR + \frac{1}{8 \times f_{OSC} \times C_{OUT}})$$

A 22µF ceramic capacitor can satisfy most applications.

#### **Thermal Calculations**

There are three types of losses associated with the LP8008 step-down converter: switching losses, conduction losses, and quiescent current losses. Conduction losses are associated with the RDS(ON) characteristics of the power output switching devices. Switching losses are dominated by the gate charge of the power output switching devices.

At full load, assuming continuous conduction mode (CCM), a simplified form of the losses is given by:

$$P_{TOTAL} = \frac{I_0^2 \times [R_{DSON(HS)} \times V_0 + R_{DSON(LS)} \times (V_{IN} - V_0)]}{V_{IN}}$$

$$+ (t_{SW} \times F \times I_0 + I_0) \times V_{IN}$$

IQ is the step-down converter quiescent current. The term tsw is used to estimate the full load step-down converter switching losses.

For the condition where the step-down converter is in dropout at 100% duty cycle, the total device dissipation reduces to:

$$P_{TOTAL} = I_0^2 \times R_{DSON(HS)} + I_0 \times V_{IN}$$

Since R<sub>DS(ON)</sub>, quiescent current, and switching losses all vary with input voltage, the total losses should be investigated over the complete input voltage range. Given the total losses, the maximum junction temperature can be derived from the  $\theta_{JA}$  for the SOT23-5 package which is 250 °C/W.

LP3202-06

Sep. -2022

Email: marketing@lowpowersemi.com

www.lowpowersemi.com

Page 10 of 15

### **Layout Guidance**

When laying out the PC board, the following layout guideline should be followed to ensure proper operation of the LP8008:

- 1. The power traces, including the GND trace, the LX trace and the IN trace should be kept short, direct and wide to allow large current flow. The L connection to the LX pins should be as short as possible. Use several VIA pads when routing between layers.

- 2. The feedback trace or OUT pin should be separate from any power trace and connect as closely as possible to the load point. Sensing along a high-current load trace will degrade DC load regulation. If external feedback resistors are used, they should be placed as closely as possible to the FB pin to minimize the length of the high impedance feedback trace.

- 3. The input capacitor  $(C_{\text{IN}})$  should connect as closely as possible to VIN and GND to get good power filtering.

- 4. Keep the switching node, LX away from the sensitive FB node.

- 5. The output capacitor  $C_{\text{OUT}}$  and L should be connected as closely as possible. The connection of L to the LX pin should be as short as possible and there should not be any signal lines under the inductor.

- 6. The resistance of the trace from the load return to GND should be kept to a minimum. This will help to minimize any error in DC regulation due to differences in the potential of the internal signal ground and the power ground.

LP3202-06

Sep. -2022

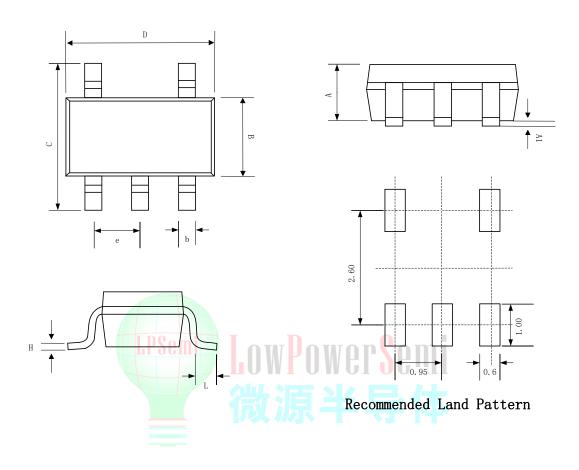

# **Packaging Information**

### SOT23-5

| SYMBOL  | Dimensions In Millimeters |       |       |  |

|---------|---------------------------|-------|-------|--|

| OTWIDGE | MIN                       | NOM   | MAX   |  |

| А       | 0.889                     | 1.100 | 1.295 |  |

| A1      | 0.000                     | 0.050 | 0.152 |  |

| В       | 1.397                     | 1.600 | 1.803 |  |

| b       | 0.28                      | 0.35  | 0.559 |  |

| С       | 2.591                     | 2.800 | 3.000 |  |

| D       | 2.692                     | 2.920 | 3.120 |  |

| е       | 0.95BSC                   |       |       |  |

| Н       | 0.080                     | 0.152 | 0.254 |  |

| L       | 0.300                     | 0.450 | 0.610 |  |

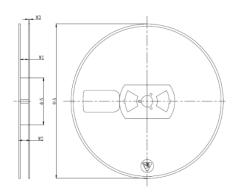

# **Tape and Reel Information**

### REEL DIMENSIONS (Unit:mm)

| ФА    | W2     |

|-------|--------|

| 180±4 | 12±0.6 |

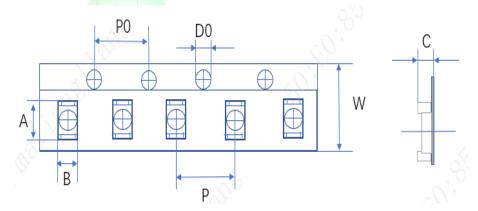

### TAPE DIMENSIONS (Unit:mm)

| Α         | В         | P0        | Р         | D0        | W         | С       |

|-----------|-----------|-----------|-----------|-----------|-----------|---------|

| 3.20±0.20 | 3.26±0.20 | 4.00±0.10 | 4.00±0.10 | 1.50±0.15 | 8.00±0.30 | 1.4±0.2 |

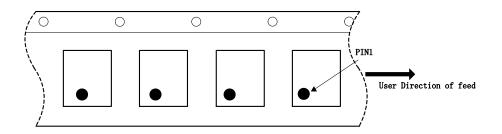

### PIN1 AND TAPE FEEDING DIRECTION

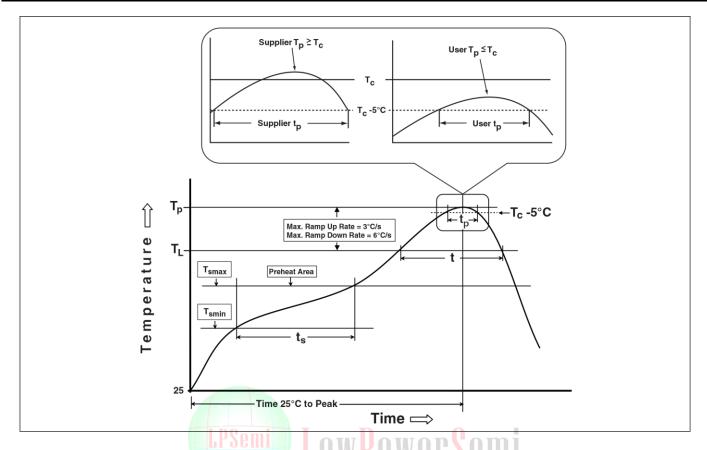

## **Classification of IR Reflow Profile**

| Profile Feature                                                                                                 | Sn-Pb Eutectic Assembly                    | Pb-Free Assembly                           |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|--|--|

| Preheat/Soak                                                                                                    |                                            |                                            |  |  |

| Temperature Min(T <sub>SMIN</sub> )                                                                             | 100℃                                       | 150℃                                       |  |  |

| Temperature Max(T <sub>SMAX</sub> )                                                                             | 150℃                                       | 200℃                                       |  |  |

| Time(T <sub>S</sub> ) from (T <sub>SMIN</sub> to T <sub>SMAX</sub> )                                            | 60~120 seconds                             | 60~120 seconds                             |  |  |

| Ramp-up rate (T <sub>L</sub> to T <sub>P</sub> )                                                                | 3℃/second max                              | 3℃/second max                              |  |  |

| Liquidous temperature(T <sub>L</sub> )                                                                          | 183℃                                       | 217℃                                       |  |  |

| Time(t <sub>L</sub> ) maintained above T <sub>L</sub>                                                           | 60~150 seconds                             | 60~150 seconds                             |  |  |

|                                                                                                                 | For users T <sub>P</sub> must not exceed   | For users T <sub>P</sub> must not exceed   |  |  |

|                                                                                                                 | theClassification temp in Table 1.         | theClassification temp in Table 2.         |  |  |

| Peak package body temperature (T <sub>P</sub> )                                                                 | For suppliers T <sub>P</sub> must equal or | For suppliers T <sub>P</sub> must equal or |  |  |

|                                                                                                                 | exceedthe Classification temp in           | exceedthe Classification temp in           |  |  |

|                                                                                                                 | Table 1.                                   | Table 2.                                   |  |  |

| Time(t <sub>P</sub> )* within 5°C of the specified                                                              |                                            |                                            |  |  |

| classification temperature(T <sub>C</sub> ), see                                                                | 20* seconds                                | 30* seconds                                |  |  |

| Figure1                                                                                                         | LOWPOWER'SE                                | mi                                         |  |  |

| Ramp-down rate (T <sub>P</sub> to T <sub>L</sub> )                                                              | 6℃/second max                              | 6℃/second max                              |  |  |

| Time 25℃ to peak temperature                                                                                    | 6 minutes max                              | 8minutes max                               |  |  |

| * Tolerance for peak profile temperature (T <sub>P</sub> ) is defined as a supplier minimum and a user maximum. |                                            |                                            |  |  |

### **Table 1 Sn-Pb Eutectic Process - Classification Temperatures (TC)**

| Package   | Volume mm3 | Volume mm3 |

|-----------|------------|------------|

| Thickness | <350       | ≥350       |

| <2.5mm    | 235℃       | 220℃       |

| ≥2.5mm    | 220℃       | 220℃       |

### Table 2 Pb-Free Process - Classification Temperatures (TC)

| Package     | Volume mm3 | Volume mm3   | Volume mm3 |

|-------------|------------|--------------|------------|

| Thickness   | <350       | 350~2000     | ≥350       |

| <1.6mm      | 260℃       | 260℃         | 260℃       |

| 1.6mm~2.5mm | 260℃       | 250℃         | 245℃       |

| >2.5mm      | 250℃       | <b>245</b> ℃ | 245℃       |

LP3202-06 Sep. -2022 Email: <u>marketing@lowpowersemi.com</u> <u>www.lowpowersemi.com</u> Page 14 of 15

Figure 1 Classification Profile (Not to scale)

Products Shipped Conform to "ROHS" Standards;

Moisture Sensitivity Level : MSL3 ( CONDITION :  $\leq$  30 °C/60%RH、 Time control:168 hours ) ;

LP3202-06

Sep. -2022