## RAA227063

4.5V to 60V 3-Phase Smart Gate Driver

The RAA227063 is a smart gate driver IC for 3-phase Brushless DC (BLDC) motor applications. It integrates three half-bridge smart gate drivers that are capable of driving up to three N-channel MOSFET bridges and supports bridge voltages from 4.5V to 60V. Each gate driver supports up to 1A source and 2A sink peak drive current with programmable drive strength control. Adjustable and adaptive dead-times are implemented to ensure robustness and flexibility. The active gate holding mechanism prevents a Miller effect-induced cross-conduction and further enhances robustness.

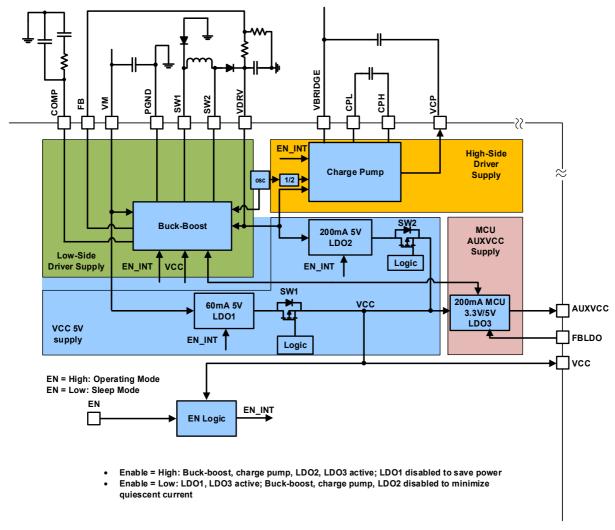

The device integrates power supplies that power internal analog and logic circuitry, high-side and low-side drivers, and a dedicated supply for powering external microcontrollers. The device also features a low-power Sleep mode that consumes only 20µA to maximize battery life in portable applications.

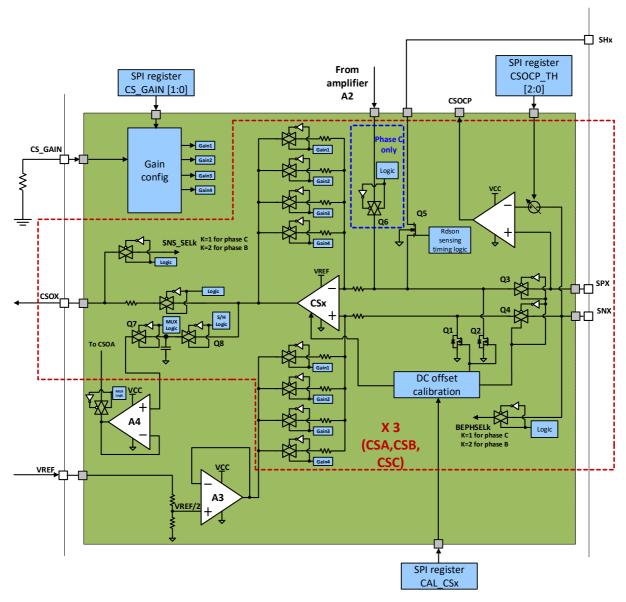

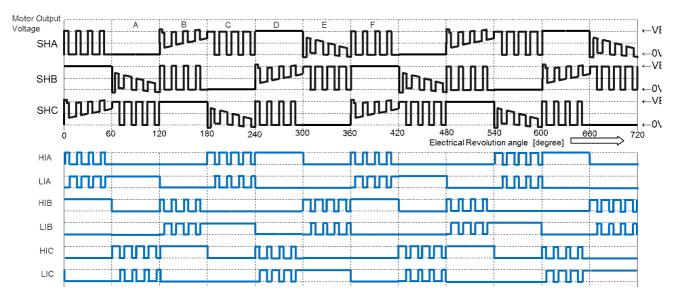

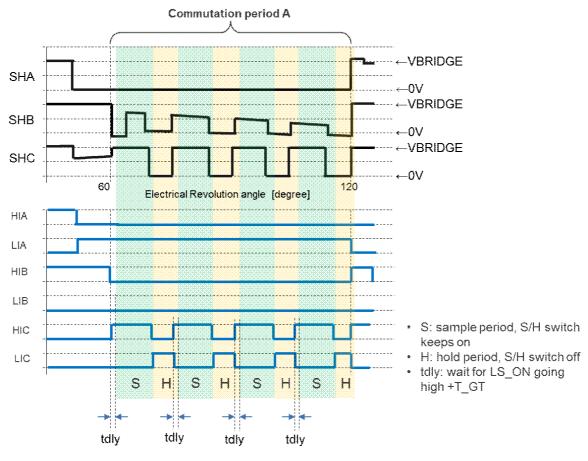

The driver control inputs can be configured to either 3-phase LI/HI or 3-phase PWM modes. Three accurate differential amplifiers with adjustable gain are integrated to support ground-side shunt current sensing or low-side  $r_{\rm DS(ON)}$  current sensing for each bridge. The device can also support sensorless operation using back EMF in brushless DC motors.

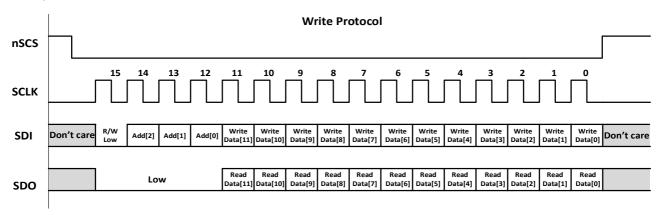

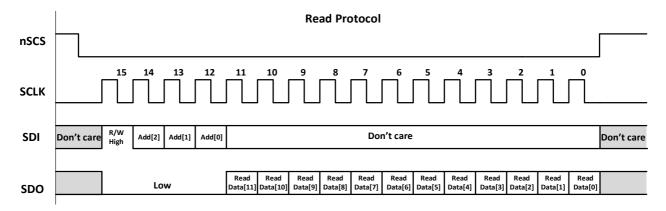

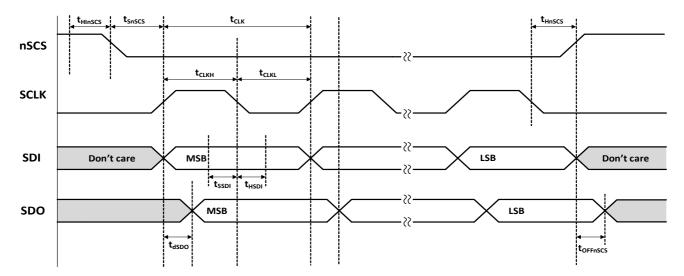

The device can be configured to use either a hardware interface or SPI interface. For hardware interface configuration, key driver operating parameters can be set using resistor pin-straps. For SPI configuration, all the parameters can be set through the SPI Bus, which allows better monitoring.

Extensive protection functions include bridge voltage UV protection, buck-boost OV/UV/OC protection, charge pump UV protection, MOSFET drain-to-source voltage OC protection, current sense overcurrent protection, thermal warning, and shutdown. Fault conditions are indicated on a dedicated nFAULT pin and in SPI status registers.

## **Applications**

- Power tools, fans, pumps, E-bikes

- Industrial automation, robotics, drones

## **Features**

- Wide V<sub>IN</sub> range: 4.5V to 60V (65V abs max)

- Switching frequency range up to 200kHz

- 3-Phase drive for BLDC application

- Peak 1A/2A source/sink current with programmable drive strength

- Supports 8 adjustable levels of drive strength through hardware interface and 16 adjustable levels of drive strength through SPI interface

- Adaptive and adjustable dead time

- Fully integrated power supply architecture

- Two VCC LDOs allow for Sleep mode low I<sub>O</sub>

- 500mA buck-boost switching regulator generates drive voltage (5V to 15V adjustable)

- 200mA adjustable output LDO for MCU supplies

- Flexible configuration

- · 3-phase HI/LI mode and 3-phase PWM mode

- · Support half-bridge, full-bridge configuration

- Three current sense amplifiers

- · Four levels of sense gain setting

- Supports DC offset calibration during power-up and on-the-fly

- Supports both ground-side shunt sense or low-side MOSFET r<sub>DS(ON)</sub> sense

- Back-EMF sensing for BLDC sensorless operation

- Features both hardware interface and SPI interface

- Extensive fault protection functions (VCC UV, VM/ VBRIDGE UV, charge pump UV, MOSFET VDS OCP, current sense OCP, thermal warning/shutdown, buck-boost current limiting, buck-boost OCP, buck-boost UV/OV)

- Supports reverse battery protection by additional external circuitry

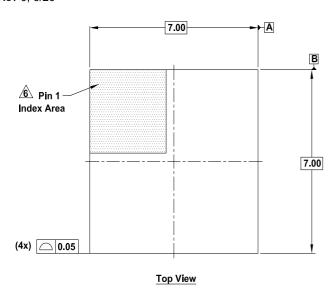

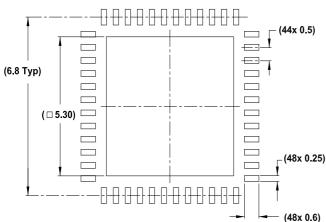

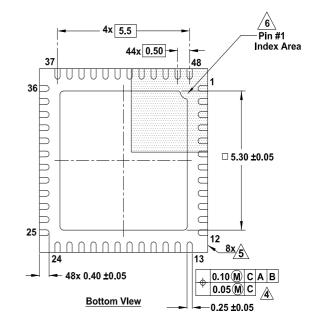

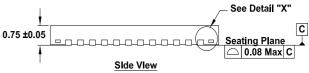

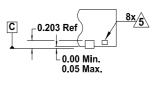

- 7mm x 7mm 48 Ld QFN package (0.5mm pitch)

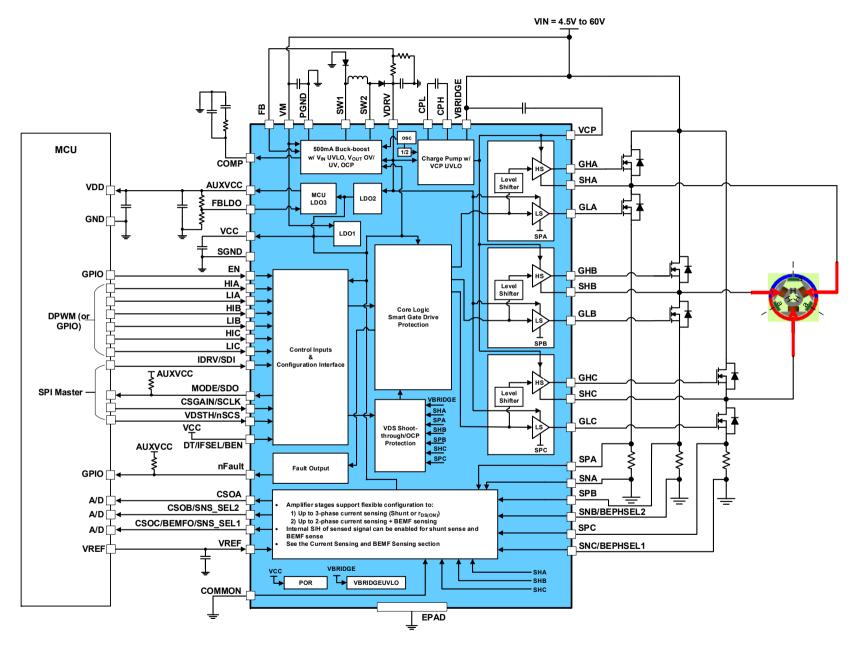

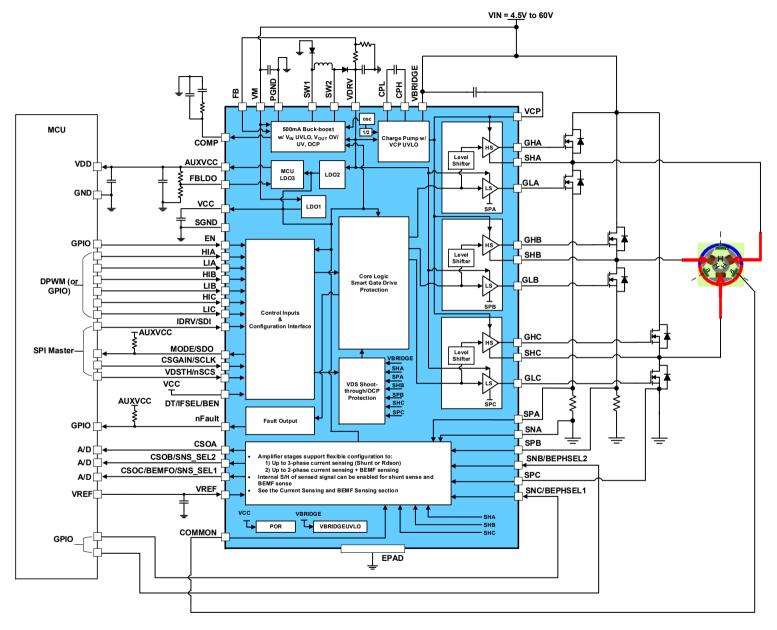

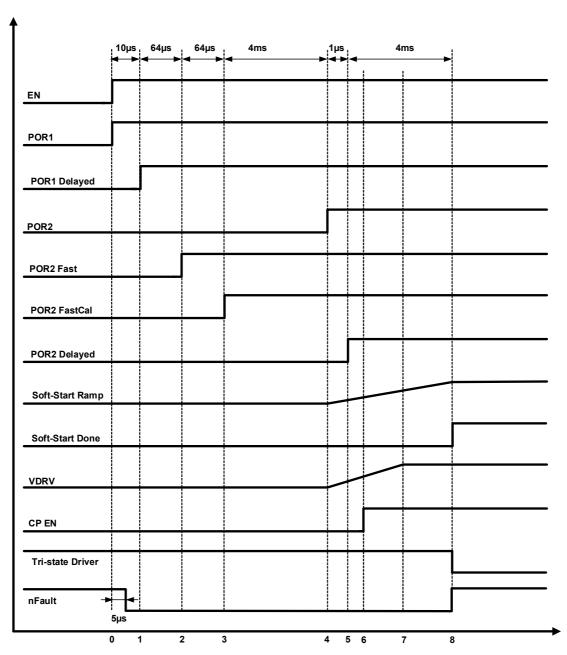

**Figure 1. Typical Application Diagram**

## RAA227063 Datasheet

# **Contents**

| 1. | Ove                             | rview                                                                                                                                                                     | . 4            |

|----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|    | 1.1                             | Typical Application Circuits                                                                                                                                              | . 4            |

| 2. | Pin I                           | Information                                                                                                                                                               | . 9            |

|    | 2.1<br>2.2                      | Pin Assignments                                                                                                                                                           |                |

| 3. | Spec                            | cifications                                                                                                                                                               | 13             |

|    | 3.1<br>3.2<br>3.3<br>3.4        | Absolute Maximum Ratings Thermal Information Recommended Operating Conditions Electrical Specifications                                                                   | 13<br>14       |

| 4. | Typi                            | cal Performance Curves                                                                                                                                                    | 24             |

| 5. | Fund                            | ctional Description                                                                                                                                                       | 26             |

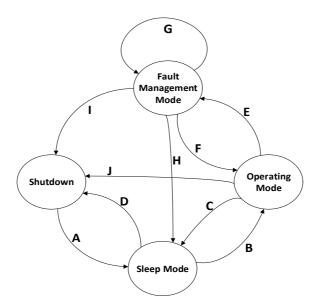

|    | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Modes of Operation and Power-On Sequence  Fault Management  Current Sensing and BEMF Sensing  Hardware Interface for Parameter Setting  Serial Peripheral Interface (SPI) | 37<br>42<br>65 |

| 6. | Regi                            | ister Map                                                                                                                                                                 | 68             |

| 7. | Pack                            | kage Outline Drawing                                                                                                                                                      | 72             |

| 8. | Orde                            | ering Information                                                                                                                                                         | 73             |

| 9. | Revi                            | sion History                                                                                                                                                              | 73             |

R16DS0045EU0103 Rev.1.03 Aug 5, 2022

## 1. Overview

# 1.1 Typical Application Circuits

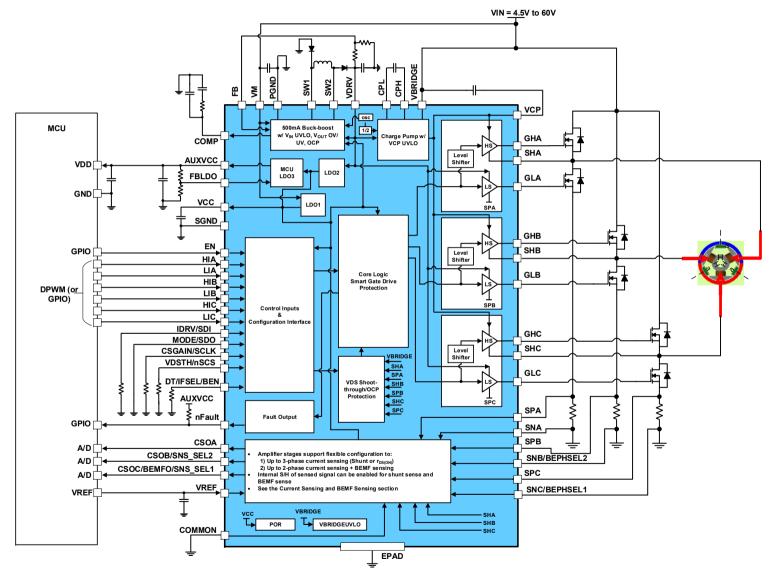

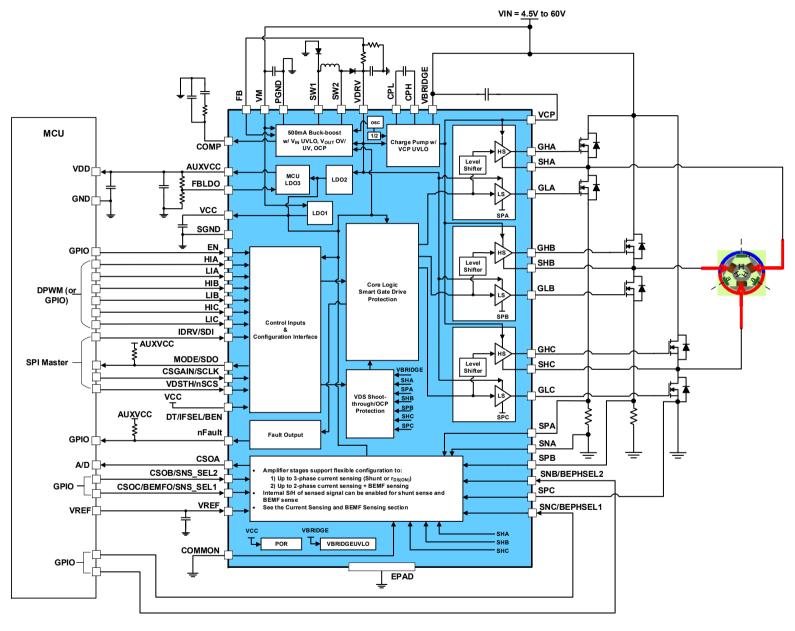

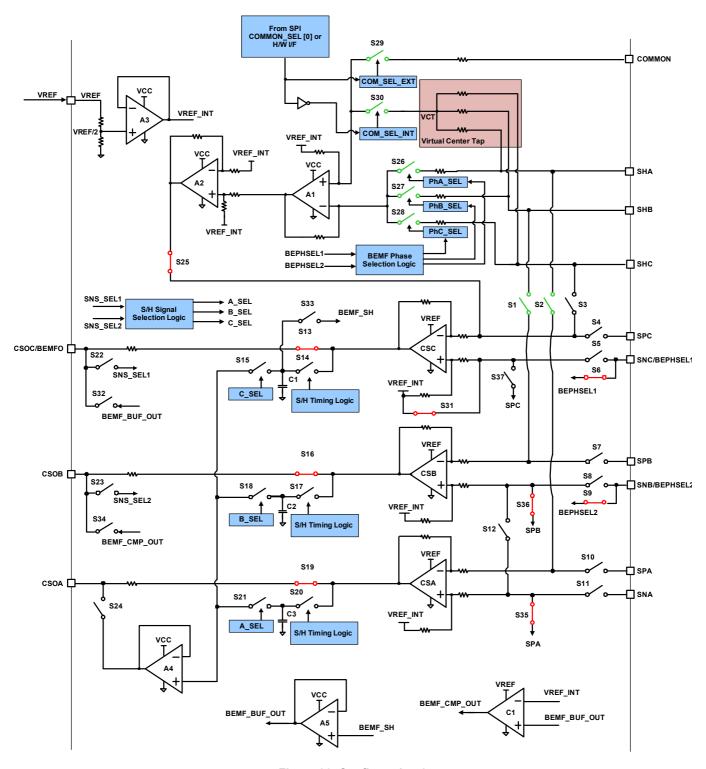

Figure 2. RAA227063 Simplified Diagram and Application – Hardware Interface Operation, BEMF Sensing Disabled, No S/H for Current Sense

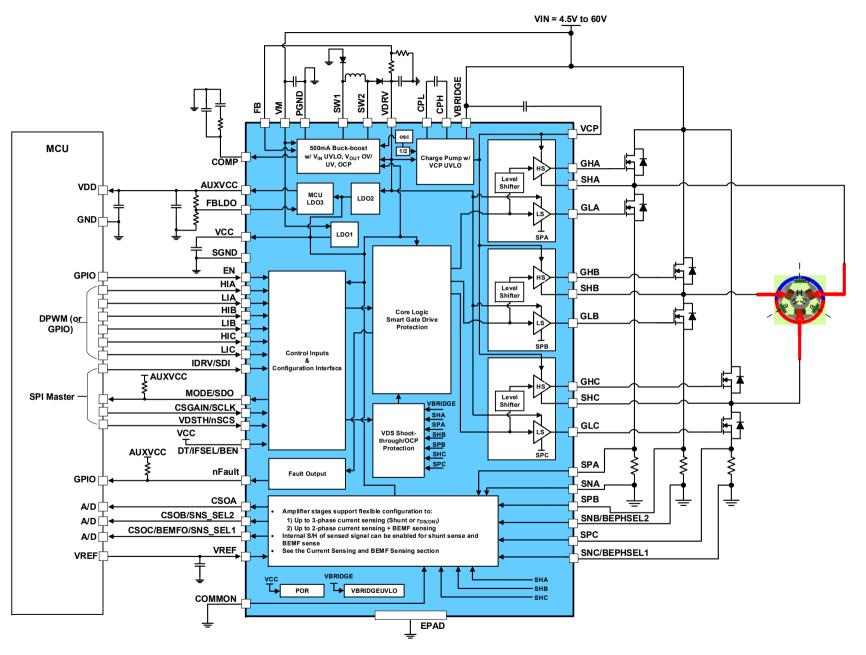

Figure 3. RAA227063 Simplified Diagram and Application – SPI Interface Operation, BEMF Sensing Disabled, No S/H for Current Sense

R16DS0045EU0103 Aug 5, 2022

Rev.1.03

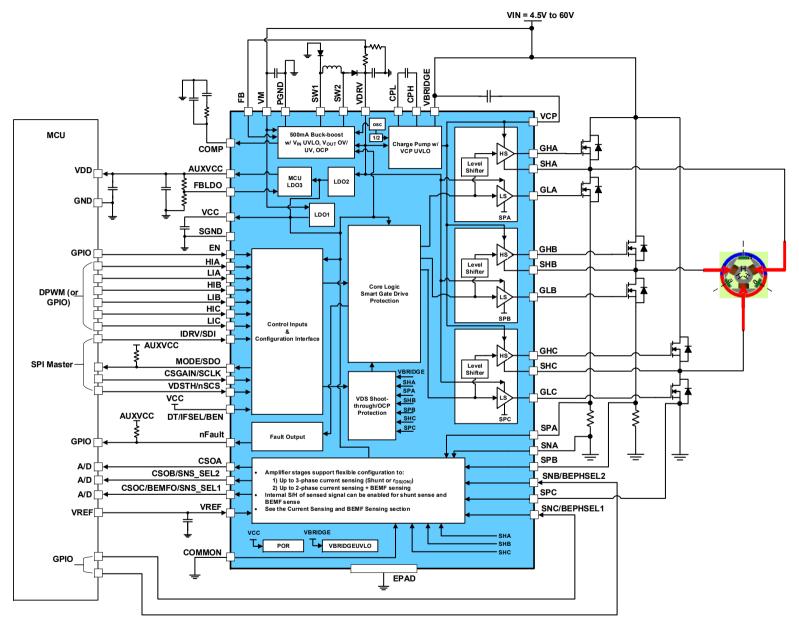

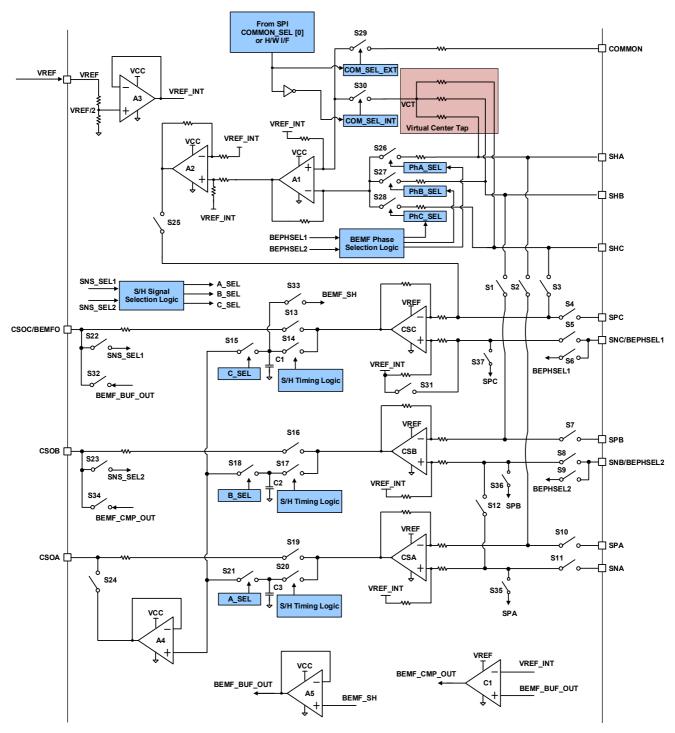

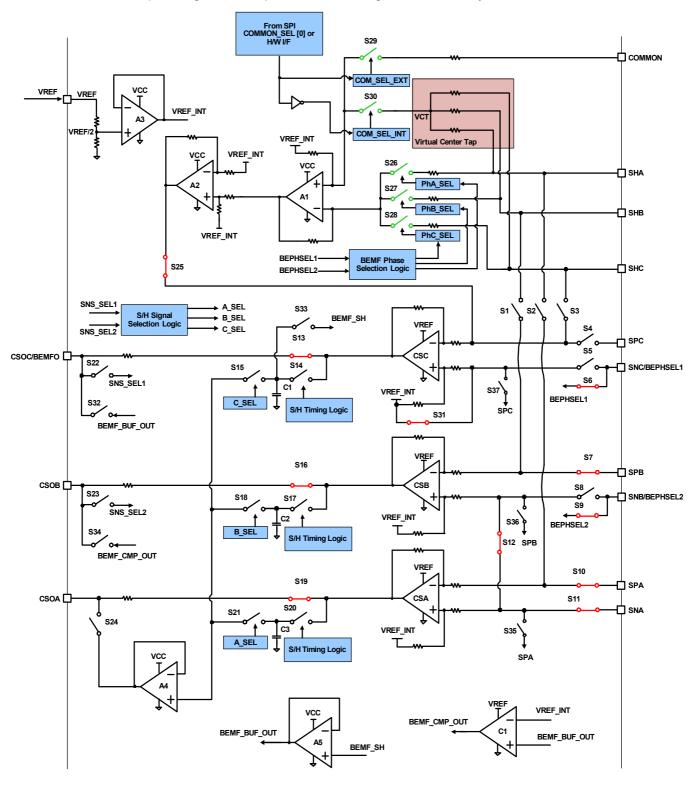

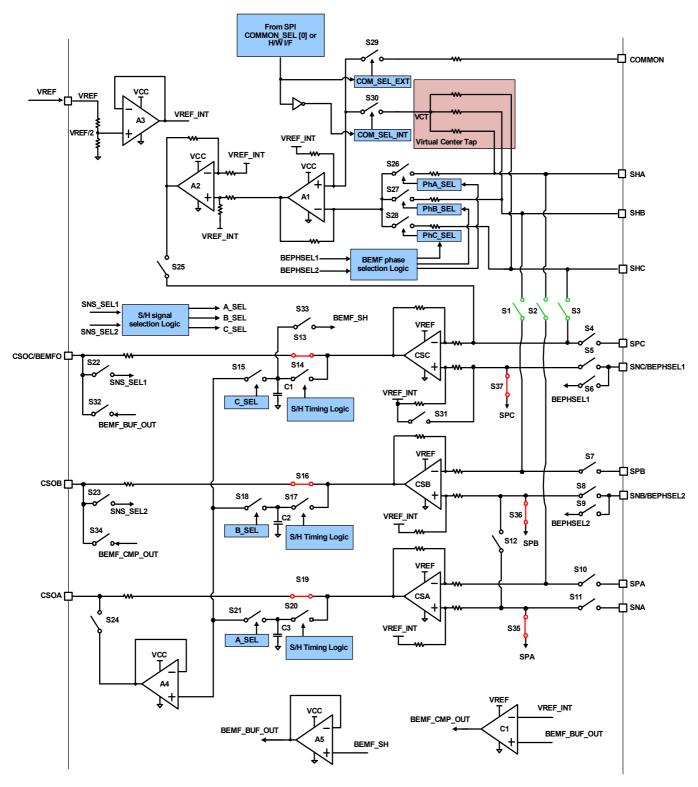

Figure 4. RAA227063 Simplified Diagram and Application – SPI Interface Operation, BEMF Sensing Enabled Using Internal Virtual Common Signal, No S/H for Current Sense or BEMF Sense

R16DS0045EU0103 Aug 5, 2022

Rev.1.03

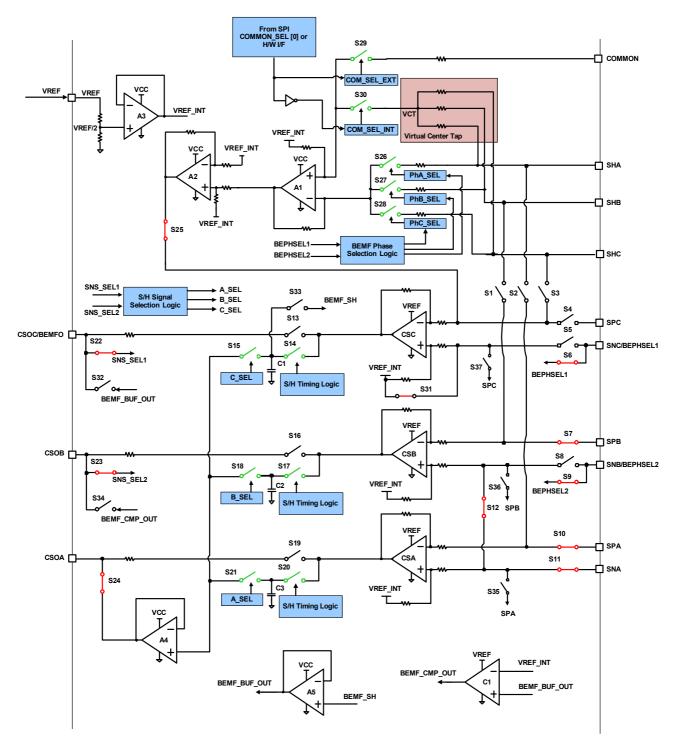

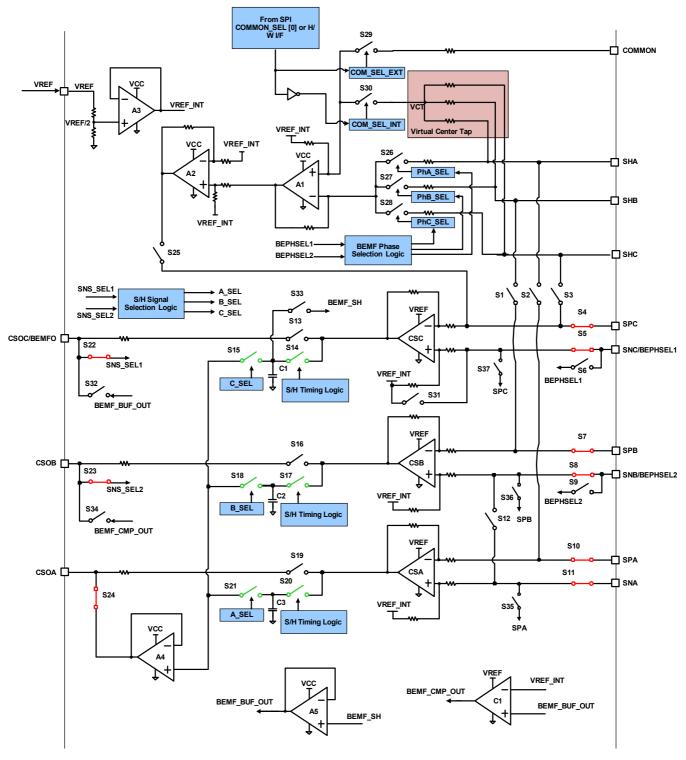

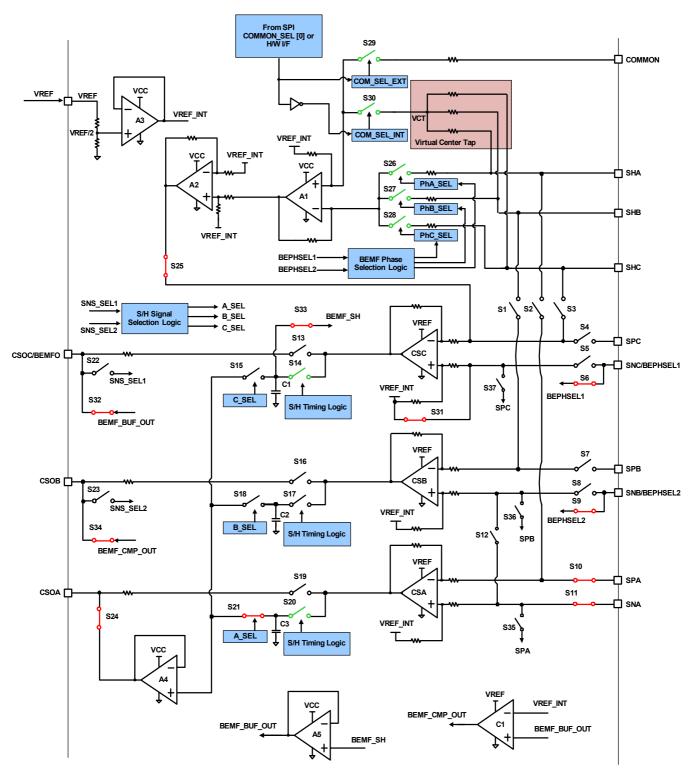

Figure 5. RAA227063 Simplified Diagram and Application – SPI Interface Operation, BEMF Sensing Enabled Using External Direct Motor Common (center tap)

Connection, No S/H for Either Current Sensing or BEMF Sensing

R16DS0045EU0103 Aug 5, 2022

Rev.1.03

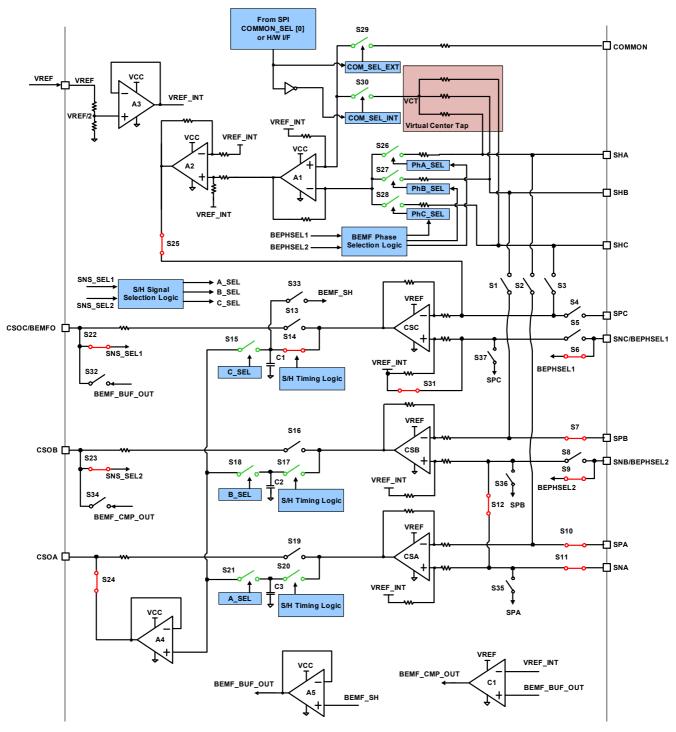

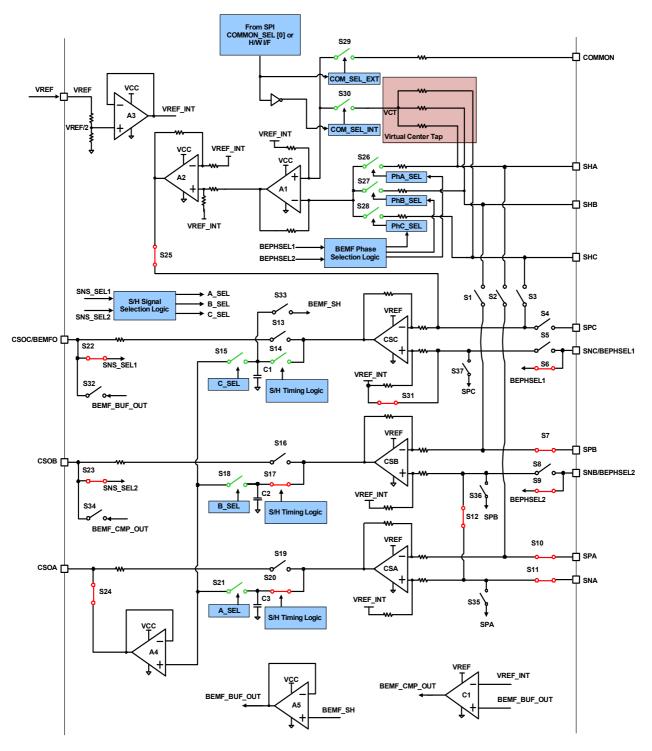

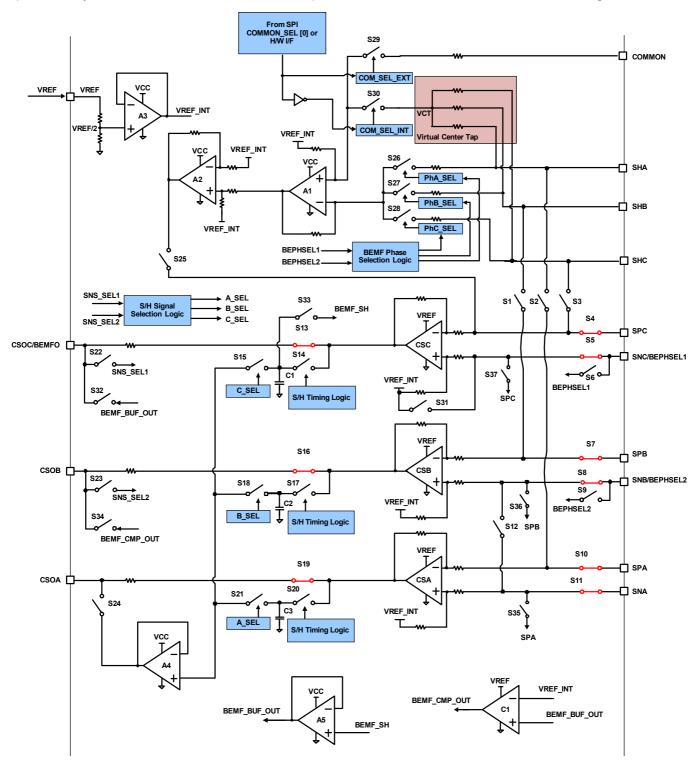

Figure 6. RAA227063 Simplified Diagram and Application –

SPI Interface Operation, BEMF Sensing Enabled Using Internal Virtual Common Signal, Internal S/H Enabled for Both Current Sensing or BEMF Sensing

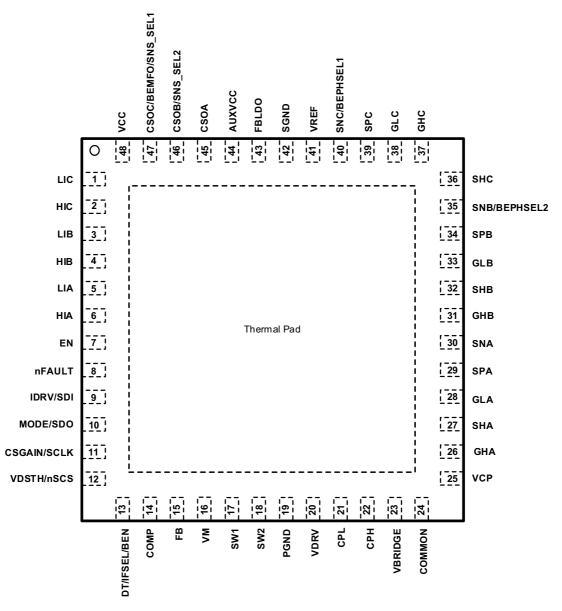

# 2. Pin Information

# 2.1 Pin Assignments

Top View

# 2.2 Pin Descriptions

| Pin# | Pin Name | Description                             |

|------|----------|-----------------------------------------|

| 1    | LIC      | Phase C low-side driver control input.  |

| 2    | HIC      | Phase C high-side driver control input. |

| 3    | LIB      | Phase B low-side driver control input.  |

| 4    | HIB      | Phase B high-side driver control input. |

| 5    | LIA      | Phase A low-side driver control input.  |

| 6    | HIA      | Phase A high-side driver control input. |

| Pin# | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | EN          | IC normal operation mode enable pin. Pulling high puts the IC into normal operating mode; pulling low or being left floating puts the IC into low power Sleep mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8    | nFAULT      | Fault indicator pin. This is an open-drain output pin that requires an external pull-up resistor. If not being set to take no action through the SPI interface, this pin is pulled low if any fault occurs, and released if all fault conditions are removed and all necessary power rails are up. <b>Note:</b> This pin is only in valid state 5µs after EN goes high. In shutdown mode, the internal pull-down device is disabled to lower the shutdown current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

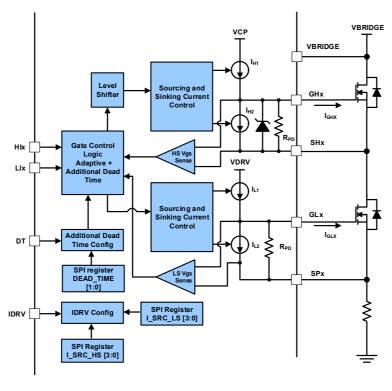

| 9    | IDRV/SDI    | <ul> <li>Dual function pin.</li> <li>If the device is Eight as a hardware interface, this pin serves as the driver peak source current setting pin. Eight levels of source current settings are supported through resistor on this pin. The setting is detected and latched up after the device is put into operating mode and all the power rail soft-starts are done.</li> <li>If the device is configured as an SPI interface, this pin serves as the SPI data input pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10   | MODE/SDO    | <ul> <li>Dual function pin.</li> <li>If the device is configured as a hardware interface, this pin serves as the mode setting pin that sets PWM mode and current sensing mode.</li> <li>If tied to VCC directly, the device works in 3-phase PWM mode, using ground-side shunt resistor for current sensing.</li> <li>If tied to SGND through a 60.4kΩ resistor, the device works in 3-phase PWM mode and uses low-side r<sub>DS(ON)</sub> for current sensing.</li> <li>If tied to SGND through a 25kΩ resistor, the device works in 3-phase HI/LI mode and uses low-side r<sub>DS(ON)</sub> for current sensing.</li> <li>If tied to SGND directly, the device works in 3-phase HI/LI mode and uses ground-side shunt resistors for current sensing.</li> <li>The setting is detected and latched after the device is put into operating mode and all the power rail soft-starts are done.</li> <li>If the device is configured as an SPI interface, this pin serves as the SPI data output pin.</li> </ul> |

| 11   | CSGAIN/SCLK | <ul> <li>Dual function pin.</li> <li>If the device is configured as a hardware interface, this pin serves as the shunt amplifier sensing gain setting pin. Four levels of gain (5V/V, 10V/V, 20V/V, 40V/V) settings are supported through resistors on this pin. The setting is detected and latched up after the device is put into operating mode and all the power rail soft-starts are done.</li> <li>If the device is configured as an SPI interface, this pin serves as the SPI clock input pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12   | VDSTH/nSCS  | <ul> <li>Dual function pin.</li> <li>If the device is configured as a hardware interface, this pin serves as the VDS OCP threshold setting pin. Eight levels of settings are supported through resistor on this pin. The setting is detected and latched after the device is put into operating mode and all the power rail soft-starts are done.</li> <li>If the device is configured as an SPI interface, this pin serves as the SPI chip select pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin# | Pin Name     | Description                                                                                                                                                                                                                                                                                                                                |

|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13   | DT/IFSEL/BEN | Configuration pin for dead time, interface selection, and BEMF sensing. Five levels of different settings are supported.                                                                                                                                                                                                                   |

|      |              | If tied to VCC directly, the device is set to use SPI interface. Default dead time 150ns. BEMF sensing is disabled by default. <b>Note:</b> The dead time setting and BEMF sensing related functionalities can be modified through the SPI interface after the device is put into operating mode when all power rail soft-starts are done. |

|      |              | <ul> <li>If tied to SGND through a 120kΩ resistor, the device is set to use hardware interface,<br/>450ns dead time, BEMF sensing feature disabled.</li> </ul>                                                                                                                                                                             |

|      |              | <ul> <li>If tied to SGND through a 60.4kΩ resistor, the device is set to use hardware interface,<br/>250ns dead time, BEMF sensing feature disabled.</li> </ul>                                                                                                                                                                            |

|      |              | <ul> <li>If tied to SGND through a 25kΩ resistor, the device is set to use hardware interface,<br/>150ns dead time, BEMF sensing feature is enabled with gain set to 0.5 and using the<br/>COMMON pin as the motor center tap input.</li> </ul>                                                                                            |

|      |              | <ul> <li>If tied to SGND directly, the device is set to use hardware interface, 150ns dead time,</li> <li>BEMF sensing feature is enabled with gain set to 0.5 and using internal virtual center tap.</li> </ul>                                                                                                                           |

|      |              | The setting is detected first during device power-up (entering operating mode) because the interface selection determines other configuration pin settings. Settings are latched after the device is put into operating mode and all the power rail soft-starts are done.                                                                  |

| 14   | COMP         | Compensation pin. Place a type 2 compensation network from this pin to SGND.                                                                                                                                                                                                                                                               |

| 15   | FB           | FB pin of buck-boost regulator. Internal reference voltage is 0.8V.                                                                                                                                                                                                                                                                        |

| 16   | VM           | Supply input for device internal power chains. It is the input for the buck-boost regulator and main 60mA LDO. VM and VBRIDGE are shorted inside the IC.                                                                                                                                                                                   |

| 17   | SW1          | Buck-boost switch node (Buck side)                                                                                                                                                                                                                                                                                                         |

| 18   | SW2          | Buck-boost switch node (Boost side)                                                                                                                                                                                                                                                                                                        |

| 19   | PGND         | Device power ground.                                                                                                                                                                                                                                                                                                                       |

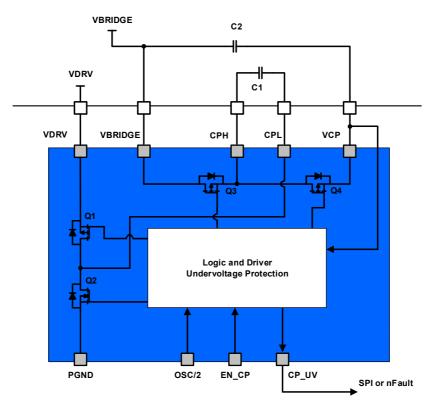

| 20   | VDRV         | Output of the buck-boost switching regulator. It is the low-side driver supply and also supplies 200mA VCC LDO in Operating mode.                                                                                                                                                                                                          |

| 21   | CPL          | Charge pump low-side switch node.                                                                                                                                                                                                                                                                                                          |

| 22   | CPH          | Charge pump high-side switch node.                                                                                                                                                                                                                                                                                                         |

| 23   | VBRIDGE      | Bridge voltage input pin and charge pump output reference. It also senses the high-side MOSFET drain voltage. Route a trace from this pin directly to the area as close as possible to the high-side MOSFET drain pad. VM and VBRIDGE are shorted inside the IC.                                                                           |

| 24   | COMMON       | External motor center tap connection for BEMF sensing. If the device is configured to use the internal virtual common signal for BEMF sensing, or BEMF sensing is disabled, tie this pin directly to SGND.                                                                                                                                 |

| 25   | VCP          | Charge pump output. It is the high-side driver supply. Place a minimum 1µF 25V MLCC capacitor from this pin to the VBRIDGE pin.                                                                                                                                                                                                            |

| 26   | GHA          | Phase A high-side driver output.                                                                                                                                                                                                                                                                                                           |

| 27   | SHA          | Phase A high-side driver output return. It is also the Phase A switch node voltage sense for the purposes of VDS OCP and BEMF sense.                                                                                                                                                                                                       |

| 28   | GLA          | Phase A low-side driver output.                                                                                                                                                                                                                                                                                                            |

| 29   | SPA          | Phase A low-side driver output return. It is also the current sense Amplifier A positive input and the Phase A low-side MOSFET source sense for VDS OCP and adaptive dead time.                                                                                                                                                            |

| 30   | SNA          | Negative input of current sense amplifier A. <b>Note:</b> If BEMF sensing is enabled, the Phase A and B current sense amplifier negative inputs are both connected to the SNA pin internally.                                                                                                                                              |

| 31   | GHB          | Phase B high-side driver output.                                                                                                                                                                                                                                                                                                           |

| 32   | SHB          | Phase B high-side driver output return. It is also the Phase B switch node voltage sense, for the purposes of VDS OCP and BEMF sense.                                                                                                                                                                                                      |

| Pin# | Pin Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33   | GLB                 | Phase B low-side driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 34   | SPB                 | Phase B low-side driver output return. It is also the current sense Amplifier B positive input and the Phase B low-side MOSFET source sense for VDS OCP and adaptive dead time.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 35   | SNB/BEPHSEL2        | <ul> <li>Dual function pin:</li> <li>If the BEMF function is disabled, it is the negative input of current sense Amplifier B.</li> <li>If the BEMF function is enabled, it is the BEMF sensing phase selection control signal input 2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                      |

| 36   | SHC                 | Phase C high-side driver output return. It is also the Phase C switch node voltage sense, for the purposes of VDS OCP and BEMF sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 37   | GHC                 | Phase C high-side driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 38   | GLC                 | Phase C low-side driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 39   | SPC                 | Phase C low-side driver output return. It is also the current sense Amplifier C positive input. It is also the Phase C low-side MOSFET source sense for VDS OCP and adaptive dead time                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 40   | SNC/BEPHSEL1        | Dual function pin:  If the BEMF function is disabled, it is the negative input of current sense Amplifier C.  If the BEMF function is enabled, it is the BEMF sensing phase selection control signal input 1.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 41   | VREF                | Current sense amplifier reference voltage input. It is divided down to ½ to supply actual amplifier reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 42   | SGND                | IC signal ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 43   | FBLDO               | Auxiliary LDO output voltage feedback pin. AUXVCC output voltage can be adjusted by changing resistor divider ratio. <b>Note:</b> The internal reference voltage is 1.2V nominal.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 44   | AUXVCC              | Auxiliary LDO supply for MCU and peripheral. <b>Note:</b> Its voltage can be adjusted through the FBLDO pin. The input to this LDO is VCC, which is 5V. Therefore, if the MCU needs 5V supply, tie directly to VCC instead of AUXVCC.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 45   | CSOA                | If internal S/H is disabled, this pin is current sense amplifier A output. If S/H is enabled for either current sense, BEMF sensing or both, this pin is the buffered output of an internal analog multiplexer that selects from the S/H output of CSA, CSB, and CSC.                                                                                                                                                                                                                                                                                                                                                                  |

| 46   | CSOB/SNS_SEL2       | <ul> <li>Dual function pin.</li> <li>If internal S/H is disabled, this pin is a current-sense amplifier B output.</li> <li>If internal S/H is enabled for either current sense, BEMF sensing, or both, this pin is the control signal 2 input for an internal analog multiplexer that selects from the S/H output of CSA, CSB, and CSC.</li> </ul>                                                                                                                                                                                                                                                                                     |

| 47   | CSOC/BEMFO/SNS_SEL1 | <ul> <li>Multiple function pin.</li> <li>If internal S/H is disabled:</li> <li>If the Back-EMF sensing function is enabled, Amplifier C is used to sense the motor backemf. This pin is the sensed motor back-EMF output.</li> <li>If the Back-EMF sensing function is disabled, Amplifier C is used to sense voltage across external shunt or r<sub>DS(ON)</sub>. This pin is the sensed voltage output.</li> <li>If internal S/H is enabled for either current sense, BEMF sensing or both, this pin is the control signal 1 input for internal analog multiplexer that selects from the S/H output of CSA, CSB, and CSC.</li> </ul> |

| 48   | VCC                 | Internal LDO output that supplies IC analog and logic bias. At start up, before IC is enabled, VCC is powered by LDO1 from VM. When the IC is enabled and the buck-boost regulator is running, VCC is obtained from LDO2 fed by VDRV. A value of 10µF MLCC decoupling capacitor is recommended to be placed as close as possible between this pin and SGND.                                                                                                                                                                                                                                                                            |

| -    | EPAD                | Thermal and GND pad. Connect it to the system ground plane on the board level to achieve low thermal impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# 3. Specifications

# 3.1 Absolute Maximum Ratings

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Para                                                      | ameter                              | Minimum                             | Maximum      | Unit |

|-----------------------------------------------------------|-------------------------------------|-------------------------------------|--------------|------|

| VBRIDGE to GND, VM to GND                                 |                                     | -0.3                                | 65           | V    |

| VCC to GND                                                |                                     | -0.3                                | 5.5          | V    |

| GHx to SHx (x = A, B, C)                                  |                                     | -0.3                                | 16           | V    |

| VDRV to GND                                               |                                     | -0.3                                | 16           | V    |

| VCP to GND, VCP to SHx (x = 2                             | A, B, C), CPH to GND                | -0.3                                | VBRIDGE + 16 | V    |

| SHx (x = A, B, C) to GND, COM                             | IMON to GND                         | -5                                  | VBRIDGE + 5  | V    |

| SPx (x = A, B, C) to GND, SNA<br>GND, SNC/BEPHSEL1 to GND |                                     | DC: -0.3<br>Transient (< 200ns): -1 | VCC + 0.3    | V    |

| GHx (x = A, B, C) to GND -5                               |                                     |                                     | VCP + 0.3    | V    |

| GLx (x = A, B, C) to GND                                  | x(x = A, B, C) to GND -1 VDRV + 0.3 |                                     |              | V    |

| CPL to GND                                                |                                     | -0.3 VDRV + 0.3                     |              | V    |

| SW2 to GND                                                |                                     | -0.3                                | VDRV + 2     | V    |

| SW1 to GND                                                |                                     | -0.3                                | VM + 0.3     | V    |

| All Other Pins                                            |                                     | -0.3                                | VCC + 0.3    | V    |

| ESD                                                       | Rating                              | Value                               |              | Unit |

| Human Body Model (Tested pe                               | r JS-001-2017)                      | 1.5                                 |              | kV   |

| Charged Device Model (Tested per JS-002-2018)             |                                     | 75                                  | 0            | V    |

| Latch-Up (Tested per<br>JESD78E; Class 2, Level B,        | GHA, GHB, GHC, SHA, SHB,<br>SHC     | 90                                  | )            | mA   |

| 125°C)                                                    | All other pins                      | 100                                 |              | mA   |

## 3.2 Thermal Information

| Thermal Resistance (Typical) | θ <sub>JA</sub> (°C/W) <sup>[1]</sup> | θ <sub>JC</sub> (°C/W) <sup>[2]</sup> |

|------------------------------|---------------------------------------|---------------------------------------|

| 48 Ld 7x7 QFN Package        | 25                                    | 1.2                                   |

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features.

See TB379.

<sup>2.</sup> For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                             | Minimum | Maximum   | Unit |

|---------------------------------------|---------|-----------|------|

| Junction Temperature, T <sub>J</sub>  | -55     | +150      | °C   |

| Operating Temperature, T <sub>A</sub> | -40     | +125      | °C   |

| Storage Temperature Range             | -65     | +150      | °C   |

| Pb-Free Reflow Profile                |         | See TB493 |      |

# 3.3 Recommended Operating Conditions

| Parameter                                                                                                                                                                  | Minimum | Maximum | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|------|

| VBRIDGE to GND, VM to GND                                                                                                                                                  | 4.5     | 60      | V    |

| VCC to GND                                                                                                                                                                 | 0       | 5.25    | V    |

| VDRV to GND                                                                                                                                                                | 5       | 14      | V    |

| EN, VDSTH/nSCS, DT/IFSEL/BEN, HIx (x = A, B, C), LIx (x = A, B, C), IDRV/SDI, FBLDO, AUXVCC, MODE/SDO, CSGAIN/SCLK, nFAULT, CSOA, CSOB/SNS_SEL2, CSOC/BEMFO/SNS_SEL1, VREF | 0       | 5.25    | V    |

| Operating Ambient Temperature Range, T <sub>A</sub>                                                                                                                        | -40     | 125     | °C   |

| Operating Junction Temperature Range, T <sub>J</sub>                                                                                                                       | -40     | 150     | °C   |

# 3.4 Electrical Specifications

| Parameter                                          | Symbol               | Test Conditions                                                                                                                                                | Min <sup>[1]</sup> | Тур  | Max <sup>[1]</sup> | Unit |

|----------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

| Bridge Supply                                      |                      |                                                                                                                                                                | <del>!</del>       |      | -1                 | *    |

| Operating Supply Current (VM and VBRIDGE combined) | I <sub>DDO</sub>     | VM = VBRIDGE = 48V, EN = 3.3V,<br>HIx/LIx = 0V, COMP = 0,<br>VDRV = 0, Charge Pump and<br>Buck-boost regulator not switching<br>VREF = 0                       |                    | 2.4  |                    | mA   |

| VM Sleep Mode<br>Supply Current                    | l <sub>VMsleep</sub> | EN = 0V, VM = 48V, T <sub>A</sub> = 25°C, no load on AUXVCC                                                                                                    |                    | 23   | 40                 | μA   |

| Sleep Mode Entry<br>Time Delay                     | t <sub>sleep</sub>   | Transition time from EN = 0V to Sleep mode                                                                                                                     |                    | 0.5  |                    | ms   |

| Wake-Up Delay from<br>Sleep Mode                   | t <sub>wake</sub>    | VCC > VCC_POR, EN goes from 0V to 3.3V to all power rails startup ready, with recommended 2.2µF and 0.22µF capacitors between VM-VCP and CPH-CPL, respectively |                    | 6.5  |                    | ms   |

| Internal Main 5V LDO1                              |                      |                                                                                                                                                                | I I                |      |                    | _I   |

| Output Voltage                                     | VCC1                 | VM = 60V, EN = 0V, load = 0mA                                                                                                                                  |                    | 5    |                    | V    |

|                                                    |                      | VM = 4.5V, EN = 0V, load = 10mA                                                                                                                                | 4.0                | 4.4  |                    | V    |

|                                                    |                      | VM = 8V, EN = 0V, load = 10mA                                                                                                                                  |                    | 5    |                    | V    |

| Current Limit                                      |                      | VM = 12V, EN = 0V                                                                                                                                              |                    | 39   |                    | mA   |

|                                                    |                      | VM = 12V, EN = 3.3V, LDO2 is off                                                                                                                               |                    | 128  |                    | mA   |

| AUXVCC LDO3                                        |                      |                                                                                                                                                                | 1                  |      | 1                  |      |

| Output Voltage                                     | AUXVCC               | EN = 3.3V, VDRV = 5V, AUXVCC<br>set to 3.3V, load = 0mA                                                                                                        | 3.05               | 3.30 | 3.60               | V    |

| Operating Mode<br>Current Limit                    |                      | EN = 3.3V, VDRV = 12V, AUXVCC set to 3.3V                                                                                                                      |                    | 220  |                    | mA   |

| Sleep Mode Output<br>Voltage                       |                      | EN = 0V, load = 1mA, VM = 24V                                                                                                                                  |                    | 3.5  |                    | V    |

| Parameter                                          | Symbol               | Test Conditions                                         | Min <sup>[1]</sup> | Тур   | Max <sup>[1]</sup> | Unit |

|----------------------------------------------------|----------------------|---------------------------------------------------------|--------------------|-------|--------------------|------|

| Internal 5V LDO2                                   |                      | 1                                                       | I I                |       | I                  |      |

| Output Voltage                                     | VCC2                 | EN = 3.3V, VDRV = 8V,<br>load = 0mA                     | 4.65               | 5.00  | 5.45               | V    |

|                                                    |                      | EN = 3.3V, VDRV = 15V,<br>load = 0mA                    | 4.65               | 5.00  | 5.45               | V    |

| Current Limit                                      |                      | EN = 3.3V, VDRV = 12V                                   |                    | 220   |                    | mA   |

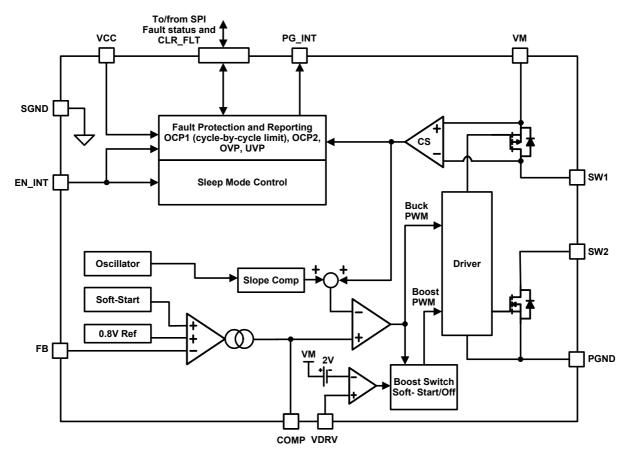

| Buck-Boost Supply                                  |                      |                                                         |                    |       | 1                  |      |

| Output Voltage<br>Adjustment Range                 | VDRV                 |                                                         | 5                  |       | 15                 | V    |

| Reference Voltage                                  | V <sub>REF_BB</sub>  |                                                         |                    | 0.8   |                    | V    |

| Operating Source<br>Current                        | I <sub>DDO_BB</sub>  |                                                         |                    | 5     |                    | mA   |

| FB Pin Source Current                              |                      |                                                         | -50                |       | 50                 | nA   |

| Transconductance<br>Amplifier Gain                 | gm                   |                                                         |                    | 200   |                    | μS   |

| Transconductance<br>Amplifier Output<br>Capability |                      |                                                         |                    | ±18   |                    | μА   |

| Transconductance<br>Amplifier Maximum<br>Output    |                      | FB = 0.7V                                               |                    | 3.95  |                    | V    |

| Transconductance<br>Amplifier Minimum<br>Output    |                      | FB = 1V                                                 |                    | 0.02  |                    | V    |

| Ramp Offset                                        |                      |                                                         |                    | 870   |                    | mV   |

| Oscillator Frequency                               | f <sub>SWBB</sub>    |                                                         | 410                | 500   | 590                | kHz  |

| Minimum On-Time                                    | t <sub>min_on</sub>  |                                                         |                    | 130   |                    | ns   |

| Minimum Off-Time                                   | t <sub>min_off</sub> |                                                         |                    | 142   |                    | ns   |

| Soft-Start Time                                    | t <sub>ss</sub>      |                                                         |                    | 5.5   |                    | ms   |

| Cycle-By-Cycle<br>Current Limit                    | l <sub>oc_1</sub>    |                                                         |                    | 1.4   |                    | А    |

| Hiccup Current Limit<br>Threshold                  | l <sub>oc_2</sub>    |                                                         |                    | 1.6   |                    | А    |

| Buck to Buck-Boost<br>Transition Threshold         | VM - VDRV            | VM = 10V and ramp VDRV voltage                          |                    | 1.9   |                    | V    |

| Buck-Boost to Buck<br>Transition Hysteresis        |                      |                                                         |                    | 1.6   |                    | V    |

| Charge Pump Supply                                 |                      |                                                         | · '                |       | -                  |      |

| Charge Pump Voltage to VBRIDGE                     | VCP - VBRIDGE        | VM = VBRIDGE = 4.5V, VDRV = 5V, I <sub>VCP</sub> = 0mA  |                    | 4.93  |                    | V    |

|                                                    |                      | VM = VBRIDGE = 24V, VDRV = 12V, I <sub>VCP</sub> = 25mA |                    | 10.75 |                    | V    |

|                                                    |                      | VM = VBRIDGE = 48V, VDRV = 12V, I <sub>VCP</sub> = 25mA |                    | 10.58 |                    | V    |

| Parameter                                   | Symbol              | Test Conditions                      | Min <sup>[1]</sup> | Тур         | Max <sup>[1]</sup> | Unit |

|---------------------------------------------|---------------------|--------------------------------------|--------------------|-------------|--------------------|------|

| EN Logic Level                              |                     |                                      | 1                  |             |                    |      |

| EN Rise Threshold                           | V <sub>RS_TH</sub>  |                                      |                    | 1.1         |                    | V    |

| EN Fall Threshold                           | V <sub>FL_TH</sub>  |                                      |                    | 0.92        |                    | V    |

| EN Threshold<br>Hysteresis                  | V <sub>EN_HYS</sub> |                                      |                    | 160         |                    | mV   |

| Logic Level Input Signal CSOB/SNS_SEL2, CSO |                     | DI, CSGAIN/SCLK, VDSTH/nSCS, S<br>1) | NB/BEPHSI          | EL2, SNC/BE | PHSEL1,            | •    |

| Logic-Low Voltage<br>Level Threshold        | V_IL                |                                      |                    | 1.21        |                    | V    |

| Logic-High Voltage<br>Level Threshold       | V_IH                |                                      |                    | 1.57        |                    | V    |

| Logic Level Hysteresis                      | V_HYS               |                                      |                    | 350         |                    | mV   |

| Logic-Low Current                           | I_IL                | Voltage level = 0V                   |                    | 15          |                    | nA   |

| Logic-High Current                          | I_IH                | Voltage level = 5V, EN = 3.3V        |                    | 14          |                    | μΑ   |

|                                             |                     | Voltage level = 3.3V, EN = 3.3V      |                    | 9           |                    | μΑ   |

| Internal Pull-Down<br>Resistance            | R_IPD               |                                      |                    | 380         |                    | kΩ   |

| Logic Level Output Sig                      | nals (nFault, MODE/ | SDO)                                 | l l                |             |                    |      |

| Logic-Low Voltage<br>Level                  | V_OL                | I <sub>O</sub> = 2mA sinking         |                    | 0.24        |                    | V    |

| High Impedance<br>Output Leakage            | I_OHLk              | V <sub>O</sub> = 5V                  |                    | 50          |                    | nA   |

| Gate Drivers                                |                     |                                      | 1                  |             |                    |      |

| Gate Driver Strength                        |                     |                                      |                    |             |                    |      |

| Peak Source Current                         | I <sub>src</sub>    | IDRV/SDI tied to SGND                |                    | 70          |                    | mA   |

|                                             | (HW I/F selected)   | IDRV/SDI 25kΩ to SGND                |                    | 160         |                    | mA   |

|                                             |                     | IDRV/SDI 62kΩ to SGND                |                    | 220         |                    | mA   |

|                                             |                     | IDRV/SDI 133kΩ to SGND               |                    | 310         |                    | mA   |

|                                             |                     | IDRV/SDI 91kΩ to VCC                 |                    | 400         |                    | mA   |

|                                             |                     | IDRV/SDI 50kΩ to VCC                 |                    | 500         |                    | mA   |

|                                             |                     | IDRV/SDI 25kΩ to VCC                 |                    | 700         |                    | mA   |

|                                             |                     | IDRV/SDI tied to VCC                 |                    | 1100        |                    | mA   |

| Parameter           | Symbol             | Test Conditions        | Min <sup>[1]</sup> | Тур  | Max <sup>[1]</sup> | Unit |

|---------------------|--------------------|------------------------|--------------------|------|--------------------|------|

| Peak Source Current | I <sub>src</sub>   | I_SRC_HS[3:0] = 0000b  |                    | 50   |                    | mA   |

| (Cont.)             | (SPI I/F selected) | I_SRC_HS[3:0] = 0001b  |                    | 70   |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 0010b  |                    | 120  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 0011b  |                    | 160  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 0100b  |                    | 200  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 0101b  |                    | 220  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 0110b  |                    | 250  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 0111b  |                    | 310  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1000b  |                    | 350  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1001b  |                    | 400  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1010b  |                    | 440  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1011b  |                    | 500  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1100b  |                    | 580  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1101b  |                    | 700  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1110b  |                    | 900  |                    | mA   |

|                     |                    | I_SRC_HS[3:0] = 1111b  |                    | 1100 |                    | mA   |

| Peak Sink Current   | I <sub>snk</sub>   | IDRV/SDI tied to SGND  |                    | 180  |                    | mA   |

|                     | (HW I/F selected)  | IDRV/SDI 25kΩ to SGND  |                    | 350  |                    | mA   |

|                     |                    | IDRV/SDI 62kΩ to SGND  |                    | 500  |                    | mA   |

|                     |                    | IDRV/SDI 133kΩ to SGND |                    | 650  |                    | mA   |

|                     |                    | IDRV/SDI 91kΩ to VCC   |                    | 800  |                    | mA   |

|                     |                    | IDRV/SDI 50kΩ to VCC   |                    | 1000 |                    | mA   |

|                     |                    | IDRV/SDI 25kΩ to VCC   |                    | 1400 |                    | mA   |

|                     |                    | IDRV/SDI Tied to VCC   |                    | 2400 |                    | mA   |

| Parameter                                             | ,                     |                                                                                            | Min <sup>[1]</sup>                           | Тур  | Max <sup>[1]</sup> | Unit |

|-------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|----------------------------------------------|------|--------------------|------|

| Peak Sink Current                                     | I <sub>snk</sub>      | I_SRC_HS[3:0] = 0000b                                                                      |                                              | 130  |                    | mA   |

| (Cont.)                                               | (SPI I/F selected)    | I_SRC_HS[3:0] = 0001b                                                                      |                                              | 180  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 0010b                                                                      |                                              | 280  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 0011b                                                                      |                                              | 350  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 0100b                                                                      |                                              | 420  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 0101b                                                                      |                                              | 500  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 0110b                                                                      |                                              | 560  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 0111b                                                                      |                                              | 650  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1000b                                                                      |                                              | 700  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1001b                                                                      |                                              | 800  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1010b                                                                      |                                              | 880  |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1011b                                                                      |                                              | 1000 |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1100b                                                                      |                                              | 1200 |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1101b                                                                      |                                              | 1400 |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1110b                                                                      |                                              | 1800 |                    | mA   |

|                                                       |                       | I_SRC_HS[3:0] = 1111b                                                                      |                                              | 2400 |                    | mA   |

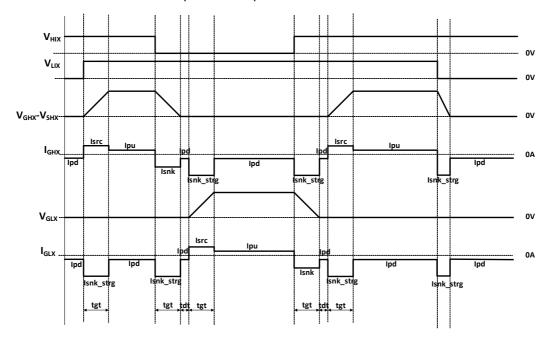

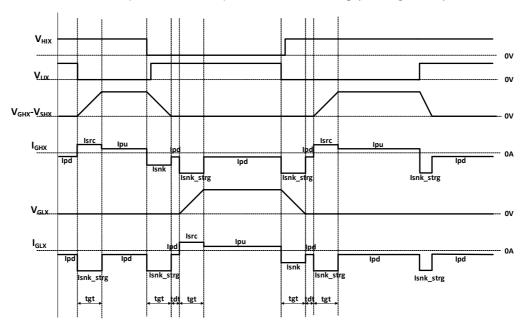

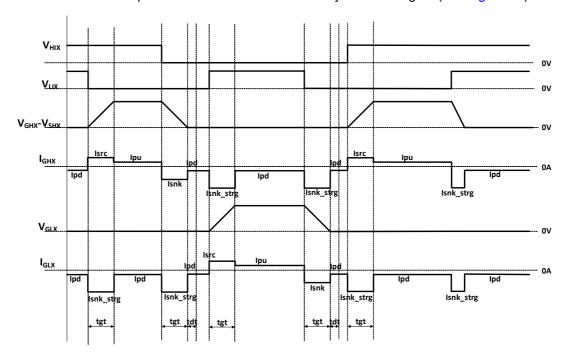

| Strong Sink Current                                   | I <sub>snk_strg</sub> |                                                                                            |                                              | 2500 |                    | mA   |

| Pull-Up Source<br>Current                             | I <sub>pu</sub>       |                                                                                            |                                              | 40   |                    | mA   |

| Pull-Down Sink<br>Current                             | I <sub>pd</sub>       |                                                                                            |                                              | 100  |                    | mA   |

| Gate Pull-Down<br>Resistor                            | $R_{pd}$              |                                                                                            |                                              | 90   |                    | kΩ   |

| High-Side Gate Clamp                                  | VGH_CLAMP             | I <sub>pu</sub> = 40mA                                                                     | 13.3                                         | 14.3 | 15.3               | V    |

| High-Side Gate Driver<br>High-Level Output<br>Voltage | VGSHH                 | 1mA load, VDRV = 10V,<br>SHx = VBRIDGE = 12V, differential<br>voltage between GHx and SHx  |                                              | 9.7  |                    | V    |

| High-Side Gate Driver<br>Low-Level Output<br>Voltage  | VGSHL                 | -1mA load, VDRV = 10V,<br>SHx = VBRIDGE = 12V, differential<br>voltage between GHx and SHx |                                              | 3.0  |                    | mV   |

| Low-Side Gate Driver<br>High-Level Output<br>Voltage  | VGSLH                 | 1mA load, VDRV = 10V,<br>SHx = VBRIDGE = 12V, differential<br>voltage between GLx and SPx  |                                              | 10.0 |                    | V    |

| Low-Side Gate Driver<br>Low-Level Output<br>Voltage   | VGSLL                 | -1mA load, VDRV = 10V,<br>SHx = VBRIDGE = 12V, differential<br>voltage between GLx and SPx |                                              | 2.5  |                    | mV   |

| Dead-Time and Maximu                                  | um Gate Transition T  | ime                                                                                        | <u>.                                    </u> |      | l                  | 1    |

| Adaptive Dead Time<br>VGS Falling Threshold           |                       |                                                                                            |                                              | 1    |                    | V    |

| Adaptive Dead Time<br>VGS Threshold<br>Hysteresis     |                       |                                                                                            |                                              | 2    |                    | V    |

| Parameter                                 | Symbol                                    | Test Conditions                                       | Min <sup>[1]</sup> | Тур | Max <sup>[1]</sup> | Unit |

|-------------------------------------------|-------------------------------------------|-------------------------------------------------------|--------------------|-----|--------------------|------|

| Gate Drive Default                        | t <sub>dt</sub>                           | DT/IFSEL/BEN tied to SGND                             |                    | 150 |                    | ns   |

| Dead Time                                 | (HW I/F is selected)                      | DT/IFSEL/BEN 25kΩ to SGND                             |                    | 150 |                    | ns   |

|                                           |                                           | DT/IFSEL/BEN 60.4kΩ to SGND                           |                    | 250 |                    | ns   |

|                                           |                                           | DT/IFSEL/BEN 120kΩ to SGND                            |                    | 450 |                    | ns   |

|                                           | t <sub>dt</sub><br>(SPI I/F is selected)  | DT/IFSEL/BEN tied to VCC,<br>DEAD_TIME[1:0] = 00b     |                    | 100 |                    | ns   |

|                                           |                                           | DT/IFSEL/BEN tied to VCC,<br>DEAD_TIME[1:0] = 01b     |                    | 150 |                    | ns   |

|                                           |                                           | DT/IFSEL/BEN tied to VCC,<br>DEAD_TIME[1:0] = 10b     |                    | 250 |                    | ns   |

|                                           |                                           | DT/IFSEL/BEN tied to VCC,<br>DEAD_TIME[1:0] = 11b     |                    | 450 |                    | ns   |

| Max Gate Transition<br>Time               | t <sub>gt_max</sub><br>(SPI I/F selected) | DT/IFSEL/BEN tied to VCC,<br>T_GT[1:0] = 00b          |                    | 0.5 |                    | μs   |

|                                           |                                           | DT/IFSEL/BEN tied to VCC,<br>T_GT[1:0] = 01b          |                    | 1.0 |                    | μs   |

|                                           |                                           | DT/IFSEL/BEN tied to VCC,<br>T_GT[1:0] = 10b          |                    | 2.0 |                    | μs   |

|                                           |                                           | DT/IFSEL/BEN tied to VCC,<br>T_GT[1:0] = 11b          |                    | 4.0 |                    | μs   |

| 3-phase HI/LI Mode Pro                    | opagation Delay                           |                                                       |                    |     | •                  | •    |

| HIX Turn-On Delay                         | t <sub>rh</sub>                           | LIX = L, HIX = L to H to VGHX-<br>VSHX starts to rise |                    | 40  |                    | ns   |

| HIX Turn-Off Delay                        | t <sub>fh</sub>                           | LIX = L, HIX = H to L to VGHX-<br>VSHX starts to fall |                    | 40  |                    | ns   |

| LIX Turn-On Delay                         | t <sub>rl</sub>                           | HIX = L, LIX = L to H to VGLX starts to rise          |                    | 40  |                    | ns   |

| LIX turn-Off Delay                        | t <sub>fl</sub>                           | HIX = L, LIX = H to L to VGLX starts to fall          |                    | 40  |                    | ns   |

| Gate Drive Off Delay when HIX and LIX     | <sup>t</sup> goff_LI_HI                   | HIX = H, LIX = L to H to VGHX-<br>VSHX starts to fall |                    | 40  |                    | ns   |

| Turning High                              |                                           | LIX = H, HIX = L to H to VGLX starts to fall          |                    | 40  |                    | ns   |

| Gate Drive On Delay when HIX and LIX      | <sup>t</sup> gon_LI_HI                    | HIX = H, LIX = H to L to VGHX-<br>VSHX starts to rise |                    | 40  |                    | ns   |

| Recover from Both<br>High Conditions      |                                           | LIX = H, HIX = H to L to VGLX starts to rise          |                    | 40  |                    | ns   |

| 3-phase PWM Mode Pr                       | opagation Delay                           |                                                       | <del>'</del>       |     | 1                  |      |

| PWM GHX Turn-Off<br>Delay                 | t <sub>GHxpwm</sub>                       | LIX = H, HIX = H to L to VGHX – VSHX falling          |                    | 40  |                    | ns   |

| PWM GLX Turn-Off<br>Delay                 | t <sub>GLxpwm</sub>                       | LIX = H, HIX = HIX = L to H to<br>GLX = H to L        |                    | 40  |                    | ns   |

| Gate Drive Off Delay when LIX Turning Low | t <sub>goff_pwm</sub>                     | LIX = H to L to VGHX-VSHX/GLX falling                 |                    | 40  |                    | ns   |

VM = 48V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C (Cont.)

| Parameter                                                            | Symbol               | Test Conditions                                                           | Min <sup>[1]</sup> | Тур                 | Max <sup>[1]</sup>     | Uni |

|----------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------|--------------------|---------------------|------------------------|-----|

| Gate Drive On Delay<br>when LIX Turning High                         | t <sub>gon_pwm</sub> | LIX = L to H to VGHX-VSHX/GLX rising                                      | 40                 |                     |                        | ns  |

| Current Sense Amplifie                                               | er                   |                                                                           | 1 1                |                     | 1                      |     |

| Amplifier Gain (Shunt                                                | G <sub>cs</sub>      | CSGAIN/SCLK tied to SGND                                                  | 4.5                | 5                   | 5.2                    | V/V |

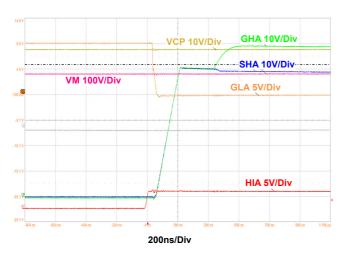

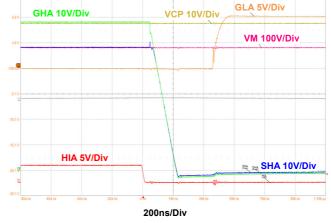

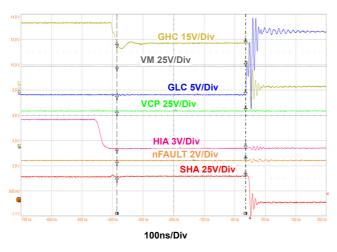

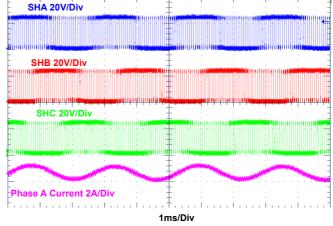

| sense)                                                               | (HW I/F selected)    | CSGAIN/SCLK 25kΩ to SGND                                                  | 9.1                | 10                  | 10.4                   | V/\ |