# **Quad 3-State Noninverting Buffers**

#### **Features**

Output Drive Capability: 15 LSTTL Loads

Outputs Directly Interface to CMOS, NMOS, and TTL

Operating Voltage Range: 2.0 to 6.0 V

Low Input Current: 1.0 μA

High Noise Immunity Characteristic of CMOS Devices

• In Compliance with the JEDEC Standard No. 7A Requirements

• ESD Performance: HBM > 2000 V; Machine Model > 200 V

• Chip Complexity: 72 FETs or 18 Equivalent Gates

• These are Pb-Free Devices

#### **Ordering Information**

| DEVICE       | Package Type | MARKING | Packing | Packing Qty  |

|--------------|--------------|---------|---------|--------------|

| 74HC125M/TR  | SOP-14       | 74HC125 | REEL    | 2500pcs/Reel |

| 74HC125MT/TR | TSSOP-14     | HC125   | REEL    | 2500pcs/Reel |

#### **High-Performance Silicon-Gate CMOS**

The 74HC125 is identical in pinout to the LS125. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

The 74HC125 noninverting buffer is designed to be used with 3-state memory address drivers, clock drivers, and other bus-oriented systems. The device has four separate output enables that are active-low.

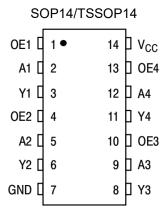

#### **Pin Connection**

#### **Function Table**

| 74HC125       |    |   |  |  |  |  |  |  |

|---------------|----|---|--|--|--|--|--|--|

| Inputs Output |    |   |  |  |  |  |  |  |

| Α             | OE | Y |  |  |  |  |  |  |

| Н             | L  | Н |  |  |  |  |  |  |

| L             | L  | L |  |  |  |  |  |  |

| Х             | Н  | Z |  |  |  |  |  |  |

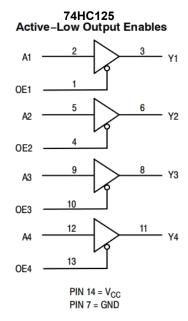

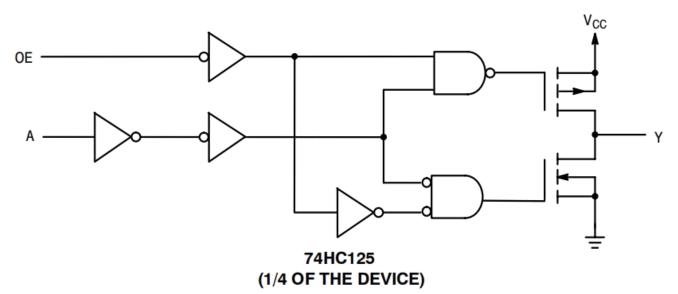

#### **Logic Diagram**

#### **Maximum Ratings**

| Symbol           | Parameter                                                              | Value                          | Unit |

|------------------|------------------------------------------------------------------------|--------------------------------|------|

| Vcc              | DC Supply Voltage (Referenced to GND)                                  | – 0.5 to + 7.0                 | V    |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND)                                   | - 0.5 to V <sub>CC</sub> + 0.5 | V    |

| V <sub>out</sub> | DC Output Voltage (Referenced to GND)                                  | - 0.5 to V <sub>CC</sub> + 0.5 | V    |

| l <sub>in</sub>  | DC Input Current, per Pin                                              | ±20                            | mA   |

| l <sub>out</sub> | DC Output Current, per Pin                                             | ±35                            | mA   |

| Icc              | DC Supply Current, VCC and GND Pins                                    | ±75                            | mA   |

| P <sub>D</sub>   | Power Dissipation in Still Air, SOP Package† TSSOP Package†            | 500<br>450                     | mW   |

| T <sub>stg</sub> | Storage Temperature                                                    | - 65 to + 150                  | °C   |

| T∟               | Lead Temperature, 1 mm from Case for 10 Seconds (SOP or TSSOP Package) | 245                            | °C   |

**Note**: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured.

This device contains protection circuitry to guard against damagedue to high static voltages or electric fields. However, precautions must be taken to avoid applications of anyvoltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $GND \le (V_{in} \text{ or } V_{out}) \le VCC$ . Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or VCC).

Unused outputs must be left open.Stresses exceeding Maximum Ratinommended Operating Conditions may affect device reliability.†Derating – SOP Package: – 7 mW/°C from 65° to 125°C TSSOP Package: – 6.1 mW/°C fgs may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recrom 65° to 125°C

### **Recommended Operating Conditions**

| Symbol                          | Parameter                                       | Min                     | Max  | Unit |    |

|---------------------------------|-------------------------------------------------|-------------------------|------|------|----|

| Vcc                             | DC Supply Voltage (Referenced to GND)           | 2.0                     | 6.0  | V    |    |

| Vin, Vout                       | DC Input Voltage, Output Voltage (Referenced to | 0                       | VCC  | V    |    |

| T <sub>A</sub>                  | Operating Temperature, All Package Types        | -40                     | + 85 | Ŝ    |    |

|                                 | Input Rise and Fall Time                        | V <sub>CC</sub> = 2.0 V | 0    | 1000 |    |

| t <sub>r</sub> , t <sub>f</sub> | $t_r, t_f$                                      | V <sub>CC</sub> = 4.5 V | 0    | 500  | ns |

|                                 | (Figure 1)                                      | V <sub>CC</sub> = 6.0 V | 0    | 400  |    |

## Dc Electrical Characteristics (Voltages Referenced to GND)

|                    |                                                   |                                                                                     |                     | Gua            | aranteed L | imit    |      |

|--------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|---------------------|----------------|------------|---------|------|

| Symbol             | Parameter                                         | Test Conditions                                                                     | V <sub>cc</sub> (V) | -40 to<br>25°C | ≤ 85°C     | ≤ 125°C | Unit |

|                    |                                                   |                                                                                     | 2.0                 | 1.5            | 1.5        | 1.5     |      |

| V <sub>IH</sub>    | Minimum High-Level                                | $V_{out} = 0.1 \text{ V or } V_{CC} - 0.1 \text{ V}$                                | 3.0                 | 2.1            | 2.1        | 2.1     | .,   |

| VIH                | Input Voltage                                     | I <sub>out</sub>   ≤ 20 μΑ                                                          | 4.5                 | 3.15           | 3.15       | 3.15    | V    |

|                    |                                                   |                                                                                     | 6.0                 | 4.2            | 4.2        | 4.2     |      |

|                    |                                                   |                                                                                     | 2.0                 | 0.5            | 0.5        | 0.5     |      |

|                    | Maximum Low-Level                                 | $V_{out} = 0.1 \text{ V or } V_{CC} - 0.1 \text{ V}$                                | 3.0                 | 0.9            | 0.9        | 0.9     | .,   |

| VIL                | Input Voltage                                     | I <sub>out</sub>   ≤ 20 µA                                                          | 4.5                 | 1.35           | 1.35       | 1.35    | V    |

|                    |                                                   |                                                                                     | 6.0                 | 1.8            | 1.8        | 1.8     |      |

|                    |                                                   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                               | 2.0                 | 1.9            | 1.9        | 1.9     |      |

|                    |                                                   | $V_{in} = V_{IH} \text{ or } V_{IL}$                                                | 4.5                 | 4.4            | 4.4        | 4.4     | V    |

| Minimum High Lovel | National Control of the Control                   | I <sub>out</sub>   ≤ 20 µA                                                          | 6.0                 | 5.9            | 5.9        | 5.9     |      |

| Vон                | V <sub>OH</sub> Minimum High-Level Output Voltage | $V_{in} = V_{IH} \text{ or } V_{IL}$<br>$ I_{out}  \le 2.4 \text{ mA}$              | 3.0                 | 2.48           | 2.34       | 2.20    |      |

|                    |                                                   | <br>   I <sub>out</sub>   ≤ 4.0 mA                                                  | 4.5                 | 3.98           | 3.84       | 3.70    |      |

|                    |                                                   | I <sub>out</sub>   ≤ 5.2 mA                                                         | 6.0                 | 5.48           | 5.34       | 5.20    |      |

|                    |                                                   | ., ., .,                                                                            | 2.0                 | 0.1            | 0.1        | 0.1     |      |

|                    |                                                   | $V_{in} = V_{IH} \text{ or } V_{IL}$<br>$ I_{out}  \le 20  \mu\text{A}$             | 4.5                 | 0.1            | 0.1        | 0.1     |      |

|                    | <b>.</b>                                          |                                                                                     | 6.0                 | 0.1            | 0.1        | 0.1     |      |

| V <sub>OL</sub>    | Maximum Low-Level Output Voltage                  | $V_{in} = V_{IH} \text{ or } V_{IL}$                                                | 3.0                 | 0.26           | 0.33       | 0.40    | V    |

|                    |                                                   | I <sub>out</sub>   ≤ 2.4 mA                                                         | 4.5                 | 0.26           | 0.33       | 0.40    |      |

|                    |                                                   | $ I_{out}  \le 4.0 \text{ mA}$<br>$ I_{out}  \le 5.2 \text{ mA}$                    | 6.0                 | 0.26           | 0.33       | 0.40    |      |

| l <sub>in</sub>    | Maximum Input Leakage<br>Current                  | V <sub>in</sub> =V <sub>CC</sub> or GND                                             | 6.0                 | ±0.1           | ±1.0       | ±1.0    | μА   |

| loz                | Maximum Three-State<br>Leakage Current            | Output in High-Impedance State $V_{in} = V_{IL}$ or $V_{IH}$ $V_{out} = VCC$ or GND | 6.0                 | 0.5            | 5.0        | 10      | μA   |

| Icc                | Maximum Quiescent Supply Current (per Package)    | V <sub>in</sub> =V <sub>CC</sub> or GND I <sub>out</sub> =0 μA                      | 6.0                 | 2.0            | 20         | 40      | μА   |

### Ac Electrical Characteristics ( $C_L$ = 50 pF, Input $t_r$ = $t_f$ = 6.0 ns)

|                    |                                                |                     | Gua       | aranteed L | imit    |      |

|--------------------|------------------------------------------------|---------------------|-----------|------------|---------|------|

| Symbol             | Parameter                                      | V <sub>cc</sub> (V) | -40 to    | ≤ 85°C     | ≤ 125°C | Unit |

|                    |                                                |                     | 25°C      |            | 20 0    |      |

|                    |                                                | 2.0                 | 90        | 115        | 135     |      |

| t <sub>PLH</sub> , | Maximum Propagation Delay, Input A to Output Y | 3.0                 | 36        | 45         | 60      | ns   |

| t <sub>PHL</sub>   | (Figures 1 and 3)                              | 4.5                 | 18        | 23         | 27      | 113  |

|                    |                                                | 6.0                 | 15        | 20         | 23      |      |

|                    |                                                | 2.0                 | 120       | 150        | 180     |      |

| t <sub>PLZ,</sub>  | Maximum Propagation Delay, Output Enable to Y  | 3.0                 | 45        | 60         | 80      | ns   |

| $t_{\text{PHZ}}$   | (Figures 2 and 4)                              | 4.5                 | 24        | 30         | 36      | 115  |

|                    |                                                | 6.0                 | 20        | 26         | 31      |      |

|                    |                                                | 2.0                 | 90        | 115        | 135     |      |

| $t_{\text{PZL}},$  | Maximum Propagation Delay, Output Enable to Y  | 3.0                 | 36        | 45         | 60      | no   |

| $t_{PZH}$          | (Figures 2 and 4)                              | 4.5                 | 18        | 23         | 27      | ns   |

|                    |                                                | 6.0                 | 15        | 20         | 23      |      |

|                    |                                                | 2.0                 | 60        | 75         | 90      |      |

| t <sub>TLH</sub> , | Maximum Output Transition Time, Any Output     | 3.0                 | 22        | 28         | 34      |      |

| t <sub>THL</sub>   | (Figures 1 and 3)                              | 4.5                 | 12        | 15         | 18      | ns   |

|                    |                                                | 6.0                 | 10        | 13         | 15      |      |

| Cin                | Maximum Input Capacitance                      | -                   | 10        | 10         | 10      | pF   |

|                    | Maximum 3-State Output Capacitance (Output in  |                     | 45        | 4.5        | 45      |      |

| C <sub>out</sub>   | High-Impedance State)                          | _                   | 15        | 15         | 15      | pF   |

| CPD                | Power Dissipation Capacitance (Per Buffer)*    |                     | Typical @ | nF         |         |      |

| 0, 0               | i ower bissipation capacitance (i ei bullei)   |                     | pF        |            |         |      |

<sup>\*</sup> Used to determine the no-load dynamic power consumption:  $P_D = C_{PD} V_{CC}^{2f} + I_{CC} V_{CC}$ .

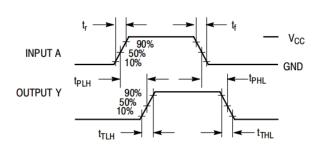

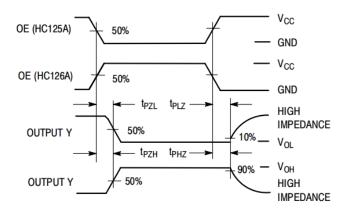

### **Switching Waveforms**

Figure 1.

Figure 2.

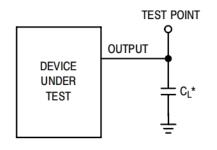

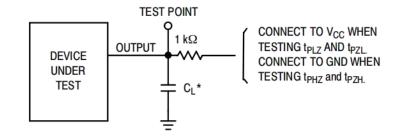

\*Includes all probe and jig capacitance

Figure 4. Test Circuit

Figure 3. Test Circuit

<sup>\*</sup>Includes all probe and jig capacitance

# **Physical Dimensions**

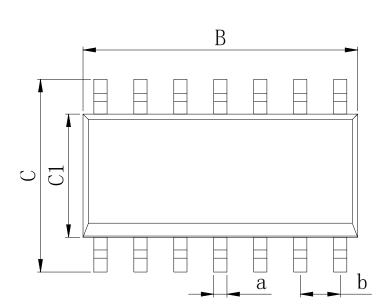

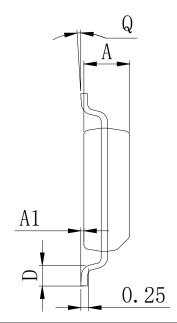

### SOP-14

| Dimensions In Millimeters(SOP-14) |      |      |      |      |      |      |    |      |          |

|-----------------------------------|------|------|------|------|------|------|----|------|----------|

| Symbol:                           | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |

| Min:                              | 1.35 | 0.05 | 8.55 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1 27 DCC |

| Max:                              | 1.55 | 0.20 | 8.75 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |

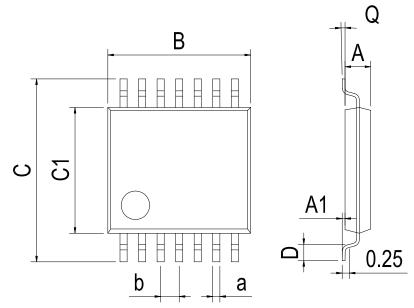

TSSOP-14

| Dimensions In Millimeters(TSSOP-14) |      |      |      |      |      |      |    |      |          |

|-------------------------------------|------|------|------|------|------|------|----|------|----------|

| Symbol:                             | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |

| Min:                                | 0.85 | 0.05 | 4.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65.050 |

| Max:                                | 0.95 | 0.20 | 5.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 | 0.65 BSC |

# **Revision History**

| DATE      | REVISION                                                                              | PAGE |

|-----------|---------------------------------------------------------------------------------------|------|

| 2014-9-6  | New                                                                                   | 1-9  |

| 2023-9-18 | Update Lead Temperature、Update encapsulation type、Add annotation for Maximum Ratings. | 1、3  |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.