# Presettable synchronous BCD decade up/down counter

#### **FEATURES**

- Synchronous reversible counting

- Asynchronous parallel load

- Asynchronous reset

- Expandable without external logic

- Output capability: standard

- I<sub>CC</sub> category: MSI

### PACKAGE/ORDERING INFORMATION

| DEVICE        | Package Type | MARKING  | Packing | Packing Qty  |

|---------------|--------------|----------|---------|--------------|

| 74HC192N      | DIP-16       | 74HC192  | TUBE    | 1000pcs/Box  |

| 74HC192M/TR   | SOP-16       | 74HC192  | REEL    | 2500pcs/Reel |

| 74HC192MT/TR  | TSSOP-16     | HC192    | REEL    | 2500pcs/Reel |

| 74HCT192N     | DIP-16       | 74HCT192 | TUBE    | 1000pcs/Box  |

| 74HCT192M/TR  | SOP-16       | 74HCT192 | REEL    | 2500pcs/Reel |

| 74HCT192MT/TR | TSSOP-16     | HCT192   | REEL    | 2500pcs/Reel |

#### GENERAL DESCRIPTION

The 74HC/HCT192 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

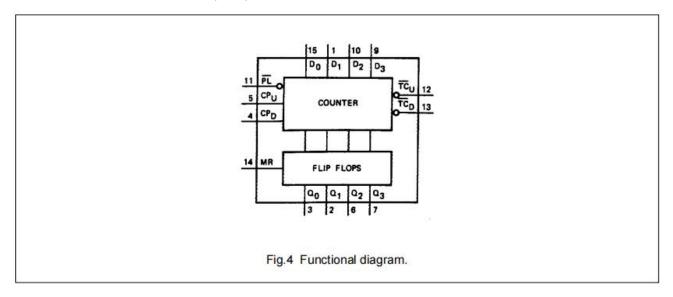

The 74HC/HCT192 are synchronous BCD up/down counters. Separate up/down clocks,  $CP_U$  and CPD respectively, simplify operation. The outputs change state synchronously with the LOW-to-HIGH transition of either clock input. If the  $CP_U$  clock is pulsed while CPD is held HIGH, the device will count up. If the CPD clock is pulsed while CPU is held HIGH, the device will count down. Only one clock input can be held HIGH at any time, or erroneous operation will result. The device can be cleared at any time by the asynchronous master reset input (MR); it may also be loaded in parallel by activating the asynchronous parallel load input ( $\overline{PL}$ ).

The "192" contains four master-slave JK flip-flops with the necessary steering logic to provide the asynchronous reset, load, and synchronous count up and count down functions.

Each flip-flop contains JK feedback from slave to master, such that a LOW-to-HIGH transition on the CPD input will decrease the count by one, while a similar transition on the CPU input will advance the count by one.

One clock should be held HIGH while counting with the other, otherwise the circuit will either count by two's or not at all, depending on the state of the first flip-flop, which cannot toggle as long as either clock input is LOW. Applications requiring reversible operation must make the reversing decision while the activating clock is HIGH to avoid erroneous counts.

The terminal count up  $(\overline{TC}_U)$  and terminal count down  $(\overline{TC}D)$  outputs are normally HIGH. When the circuit has reached the maximum count state of 9, the next HIGH-to-LOW transition of  $CP_U$  will cause  $\overline{TC}_U$  to go LOW.  $\overline{TC}_U$  will stay LOW until  $CP_U$  goes HIGH again, duplicating the count up clock.

Likewise, the  $\overline{\text{TC}}_D$  output will go LOW when the circuit is in the zero state and the CPD goes LOW. The terminal count outputs can be used as the clock input signals to the next higher order circuit in a multistage counter, since they duplicate the clock wave forms. Multistage counters will not be fully synchronous, since there is a slight delay time difference added for each stage that is added.

The counter may be preset by the asynchronous parallel load capability of the circuit. Information present on the parallel data inputs ( $D_0$  to  $D_3$ ) is loaded into the counter and appears on the outputs ( $Q_0$  to  $Q_3$ ) regardless of the conditions of the clock inputs when the parallel load ( $\overline{PL}$ ) input is LOW. A HIGH level on the master reset (MR) input will disable the parallel load gates, override both clock inputs and set all outputs ( $Q_0$  to  $Q_3$ ) LOW. If one of the clock inputs is LOW during and after a reset or load operation, the next LOW-to-HIGH transition of that clock will be interpreted as a legitimate signal and will be counted.

### **QUICK REFERENCE DATA**

GND = 0 V;  $T_{amb} = 25^{\circ}C$ ;  $t_r = t_f = 6 \text{ ns}$

| SYMBOL                              | PARAMETER                                 | CONDITIONS            | TYP | UNIT |      |  |

|-------------------------------------|-------------------------------------------|-----------------------|-----|------|------|--|

| STWIBOL                             | PARAMETER                                 | CONDITIONS            | нс  | нст  | ONIT |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay CPD, CPU to Qn          | CL = 45 = 5: VCC = 5V | 20  | 20   | ns   |  |

| f <sub>max</sub>                    | maximum clock frequency                   | CL = 15 pF; VCC =5V   | 40  | 45   | MHz  |  |

| T∟                                  | Soldering temperature                     | 10s                   | -   | 245  | °C   |  |

| Cı                                  | input capacitance                         |                       | 3.5 | 3.5  | pF   |  |

| C <sub>PD</sub>                     | power dissipation capacitance per package | notes 1 and 2         | 24  | 28   | pF   |  |

Notes: 1. CPD is used to determine the dynamic power dissipation (PD in  $\mu W$ ):

$P_D {=} C_{PD} {\times} V_{CC}{}^2 {\times} fi \ {+} \Sigma (CL {\times} V_{CC}{}^2 {\times} F_O) where:$

fi=input frequency in MHz fo=output frequency in MHz  $\Sigma (CL \times V_{CC}{}^2 \times F_O) = sum \ of \ outputs$   $C_L = output \ load \ capacitance \ in \ pF$

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_{I}$  = GND to VCC

For HCT the condition is  $V_1$  = GND to VCC-1.5V

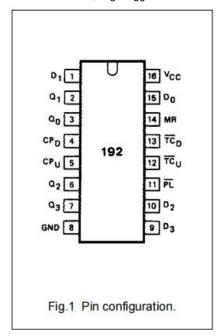

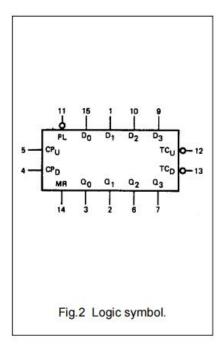

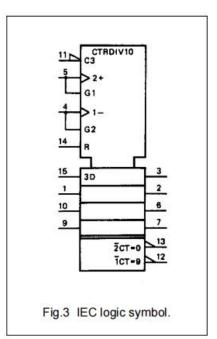

### **PIN DESCRIPTION**

| PIN NO.      | SYMBOL                           | NAME AND FUNCTION                                |

|--------------|----------------------------------|--------------------------------------------------|

| 3, 2, 6, 7   | Q0 to Q3                         | flip-flop outputs                                |

| 4            | CP <sub>D</sub>                  | count down clock input(1)                        |

| 5            | CPu                              | count up clock input(1)                          |

| 8            | GND                              | ground (0 V)                                     |

| 11           | PL                               | asynchronous parallel load input (active LOW)    |

| 12           | TC∪                              | terminal count up (carry) output (active LOW)    |

| 13           | TCD                              | terminal count down (borrow) output (active LOW) |

| 14           | MR                               | asynchronous master reset input (active HIGH)    |

| 15, 1, 10, 9 | D <sub>0</sub> to D <sub>3</sub> | data inputs                                      |

| 16           | V <sub>CC</sub>                  | positive supply voltage                          |

#### Note

#### 1. LOW-to-HIGH, edge triggered

## **FUNCTION TABLE**

| OPERATING MODE |    |    |     | INP | UTS |    |    |    | OUTPUTS      |      |      |                  |                  |                   |

|----------------|----|----|-----|-----|-----|----|----|----|--------------|------|------|------------------|------------------|-------------------|

| OPERATING MODE | MR | PL | CPU | CPD | D0  | D1 | D2 | D3 | Q0           | Q1   | Q2   | Q3               | ΤCυ              | $\overline{TC}_D$ |

| reset (clear)  | Н  | Х  | Х   | L   | Х   | Х  | Х  | Х  | L            | L    | L    | L                | Н                | L                 |

| reset (clear)  | Н  | Х  | Х   | Н   | Х   | Х  | Х  | Х  | L            | L    | L    | L                | Н                | Н                 |

|                | L  | L  | Х   | L   | L   | L  | L  | L  | L            | L    | L    | L                | Н                | L                 |

| navellal land  | L  | L  | Х   | Н   | L   | L  | L  | L  | L            | L    | L    | L                | Н                | Н                 |

| parallel load  | L  | L  | L   | Х   | Н   | Х  | Х  | н  |              | Qn = | = Dn |                  | L                | Н                 |

|                | L  | L  | Н   | Х   | Н   | Х  | Х  | н  | Qn = Dn      |      | Н    | Н                |                  |                   |

| count up       | L  | Н  |     | Н   | Х   | Х  | Х  | Х  | count up     |      |      | H <sup>(2)</sup> | Н                |                   |

| count down     | L  | Н  | Н   |     | Х   | Х  | Х  | Х  | count down F |      |      | Н                | H <sup>(3)</sup> |                   |

#### Notes

H = HIGH voltage level

L = LOW voltage level

X = don't care

↑= LOW-to-HIGH clock transition

$\overline{TC}_U$  = CPU at terminal count up (HLLH)

$\overline{TC}_D$  = CPD at terminal count down (LLLL)

Clear overrides load, data and count inputs.

When counting up the count down clock input (CPD) must be HIGH, when counting down the count up clock input (CPU) must be HIGH. **Sequence**

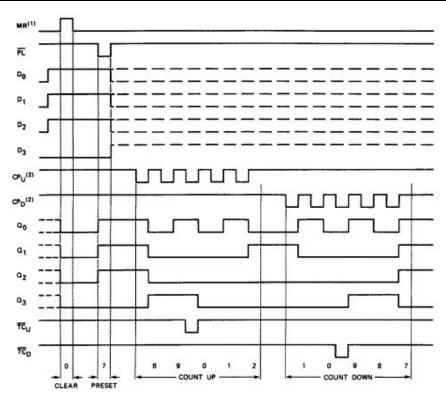

Clear (reset outputs to zero); load (preset) to BCD seven; count up to eight, nine, terminal count up, zero, one and two; count down to one, zero, terminal count down, nine, eight, and seven.

Fig.5 Typical clear, load and count sequence.

Fig.6 Logic diagram.

#### DC CHARACTERISTICS FOR 74HC

Output capability: standard

Icc category: MSI

#### **AC CHARACTERISTICS FOR 74HC**

$GND = 0 V; t_r = t_f = 6 ns; CL = 50 pF$

|                                     |                                                      |      |      | T    | amb (° | C)    |        |        |      | TEST CONDITIONS |           |  |

|-------------------------------------|------------------------------------------------------|------|------|------|--------|-------|--------|--------|------|-----------------|-----------|--|

|                                     |                                                      |      |      |      | 74HC   | :     |        |        | 1    |                 |           |  |

| SYMBOL                              | PARAMETER                                            |      | 25   |      | -40 t  | o +85 | -40 to | o +125 | UNIT | VCC             | WAVEFORMS |  |

|                                     |                                                      | min. | typ. | max. | min.   | max.  | min.   | max.   |      | (V)             |           |  |

|                                     | propagation delay                                    |      | 66   | 215  |        | 270   |        | 325    |      | 2.0             |           |  |

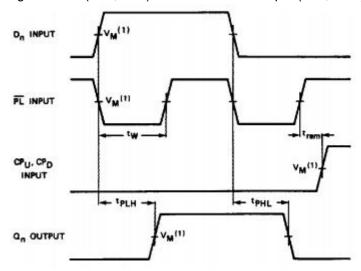

| $t_{\text{PHL}}/\ t_{\text{PLH}}$   | propagation delay $CP_{U}, CP_{D} \text{ to Qn}$     |      | 24   | 43   |        | 54    |        | 65     | ns   | 4.5             | Fig.7     |  |

|                                     | CPU, CPD to QII                                      |      | 19   | 37   |        | 46    |        | 55     |      | 6.0             |           |  |

|                                     | propagation delay                                    |      | 33   | 125  |        | 155   |        | 190    |      | 2.0             |           |  |

| $t_{\text{PHL}}/\ t_{\text{PLH}}$   | CP <sub>U</sub> to TC <sub>U</sub>                   |      | 12   | 25   |        | 31    |        | 38     | ns   | 4.5             | Fig.8     |  |

|                                     | CPU to TCU                                           |      | 10   | 21   |        | 26    |        | 32     |      | 6.0             |           |  |

|                                     | propagation delay                                    |      | 39   | 125  |        | 155   |        | 190    |      | 2.0             |           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay CP <sub>D</sub> to TC <sub>D</sub> |      | 14   | 25   |        | 31    |        | 38     | ns   | 4.5             | Fig.8     |  |

|                                     | CPD to TCD                                           |      | 11   | 21   |        | 26    |        | 32     |      | 6.0             |           |  |

|                                     |                                                      |      | 69   | 215  |        | 270   |        | 325    |      | 2.0             |           |  |

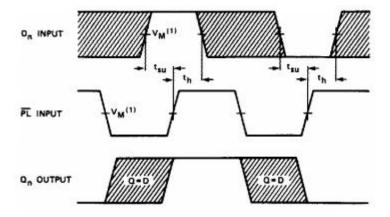

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay PE to Qn                           |      | 25   | 43   |        | 54    |        | 65     | ns   | 4.5             | Fig.9     |  |

|                                     |                                                      |      | 20   | 37   |        | 46    |        | 55     |      | 6.0             |           |  |

|                                     | propagation dolay                                    |      | 63   | 200  |        | 250   |        | 300    |      | 2.0             |           |  |

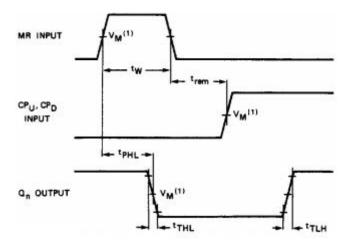

| $t_{PHL}$                           | propagation delay                                    |      | 23   | 40   |        | 50    |        | 60     | ns   | 4.5             | Fig.10    |  |

|                                     | MR to Qn                                             |      | 18   | 34   |        | 43    |        | 51     |      | 6.0             |           |  |

|                                     |                                                      |      | 91   | 275  |        | 345   |        | 415    |      | 2.0             |           |  |

| $t_{PHL}$                           | propagation delay                                    |      | 33   | 55   |        | 69    |        | 83     | ns   | 4.5             | Fig.9     |  |

|                                     | Dn to Qn                                             |      | 26   | 47   |        | 59    |        | 71     |      | 6.0             |           |  |

|                                     |                                                      |      | 80   | 240  |        | 300   |        | 360    |      | 2.0             |           |  |

| $t_{PHL}$                           | propagation delay                                    |      | 29   | 48   |        | 60    |        | 72     | ns   | 4.5             | Fig.9     |  |

|                                     | Dn to Qn                                             |      | 23   | 41   |        | 51    |        | 61     |      | 6.0             |           |  |

|                                     | propagation delay                                    |      | 102  | 315  |        | 395   |        | 475    |      | 2.0             |           |  |

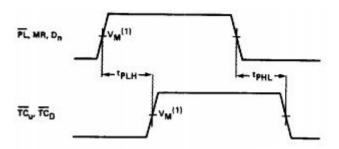

| $t_{\text{PHL}}/\ t_{\text{PLH}}$   | PL to TCU,                                           |      | 37   | 63   |        | 79    |        | 95     | ns   | 4.5             | Fig.12    |  |

|                                     | PL to TC <sub>D</sub>                                |      | 30   | 54   |        | 67    |        | 81     |      | 6.0             |           |  |

|                                     | propagation delay                                    |      | 96   | 285  |        | 355   |        | 430    |      | 2.0             |           |  |

| $t_{\text{PHL}}/t_{\text{PLH}}$     | MR to $\overline{TC}_{U}$ ,                          |      | 35   | 57   |        | 71    |        | 86     | ns   | 4.5             | Fig.12    |  |

|                                     | MR to $\overline{TC}_D$                              |      | 28   | 48   |        | 60    |        | 73     |      | 6.0             |           |  |

|                                     | propagation delay                                    |      | 83   | 290  |        | 365   |        | 435    |      | 2.0             |           |  |

| $t_{\text{PHL}}/t_{\text{PLH}}$     | Dn to $\overline{TC}_{U}$ ,                          |      | 30   | 58   |        | 73    |        | 87     | ns   | 4.5             | Fig.12    |  |

|                                     | Dn to $\overline{TC}_D$                              |      | 24   | 49   |        | 62    |        | 74     |      | 6.0             |           |  |

|                                     |                                                      |      | 19   | 75   |        | 95    |        | 110    |      | 2.0             |           |  |

| $t_{THL}/t_{TLH}$                   | output transition time                               |      | 7    | 15   |        | 19    |        | 22     | ns   | 4.5             | Fig.10    |  |

|                                     |                                                      |      | 6    | 13   |        | 16    |        | 19     |      | 6.0             |           |  |

|        |                               |      |      | T    | amb (° | (C)   |        |        |      | TES   | TEST CONDITIONS                            |  |  |

|--------|-------------------------------|------|------|------|--------|-------|--------|--------|------|-------|--------------------------------------------|--|--|

| OVMDOL | DADAMETED                     |      |      |      | 74HC   |       |        |        |      | .,,,, |                                            |  |  |

| SYMBOL | PARAMETER                     |      | +25  |      | -40 t  | o +85 | -40 to | o +125 | UNIT | VCC   | WAVEFORMS                                  |  |  |

|        |                               | min. | typ. | max. | min.   | max.  | min.   | max.   |      | (V)   |                                            |  |  |

|        | up clock pulse width          | 120  | 39   |      | 150    |       | 180    |        |      | 2.0   |                                            |  |  |

| tW     | HIGH or LOW                   | 24   | 14   |      | 30     |       | 36     |        | ns   | 4.5   | Fig.7                                      |  |  |

|        | THISTI OF LOW                 | 20   | 11   |      | 26     |       | 31     |        |      | 6.0   |                                            |  |  |

|        | down clock pulse width        | 140  | 50   |      | 175    |       | 210    |        |      | 2.0   |                                            |  |  |

| tW     | HIGH or LOW                   | 28   | 18   |      | 35     |       | 42     |        | ns   | 4.5   | Fig.7                                      |  |  |

|        | HIGH OF LOW                   | 24   | 14   |      | 30     |       | 36     |        |      | 6.0   |                                            |  |  |

|        | magter reget pulse width      | 80   | 22   |      | 100    |       | 120    |        |      | 2.0   |                                            |  |  |

| tW     | master reset pulse width HIGH | 16   | 8    |      | 20     |       | 24     |        | ns   | 4.5   | Fig.10                                     |  |  |

|        | ПСП                           | 14   | 6    |      | 17     |       | 20     |        |      | 6.0   |                                            |  |  |

|        | parallal land pulse width     | 80   | 22   |      | 100    |       | 120    |        |      | 2.0   |                                            |  |  |

| tW     | parallel load pulse width LOW | 16   | 8    |      | 20     |       | 24     |        | ns   | 4.5   | Fig.9                                      |  |  |

|        | LOW                           | 14   | 6    |      | 17     |       | 20     |        |      | 6.0   |                                            |  |  |

|        | removal time                  | 50   | 3    |      | 65     |       | 75     |        |      | 2.0   |                                            |  |  |

| trem   | removal time                  | 10   | 1    |      | 13     |       | 15     |        | ns   | 4.5   | Fig.9                                      |  |  |

|        | PL to CPU, CPD                | 9    | 1    |      | 11     |       | 13     |        |      | 6.0   |                                            |  |  |

|        | removal time                  | 50   | 0    |      | 65     |       | 75     |        |      | 2.0   |                                            |  |  |

| trem   | removal time  MR to CPU, CPD  | 10   | 0    |      | 13     |       | 15     |        | ns   | 4.5   | Fig.10                                     |  |  |

|        | WIR to CPO, CPD               | 9    | 0    |      | 11     |       | 13     |        |      | 6.0   |                                            |  |  |

|        | act up time                   | 80   | 22   |      | 100    |       | 120    |        |      | 2.0   | Fig 11 pates CD                            |  |  |

| tsu    | set-up time                   | 16   | 8    |      | 20     |       | 24     |        | ns   | 4.5   | Fig.11 note: $CP_{U}$<br>= $CP_{D}$ = HIGH |  |  |

|        | Dn to PL                      | 14   | 6    |      | 17     |       | 20     |        |      | 6.0   |                                            |  |  |

|        | hald time                     | 0    | 14   |      | 0      |       | 0      |        |      | 2.0   |                                            |  |  |

| th     | hold time                     | 0    | 5    |      | 0      |       | 0      |        | ns   | 4.5   | Fig.11                                     |  |  |

|        | Dn to PL                      | 0    | 4    |      | 0      |       | 0      |        |      | 6.0   |                                            |  |  |

|        | hold time CDU to CDD          | 80   | 19   |      | 100    |       | 120    |        |      | 2.0   |                                            |  |  |

| th     | hold time CPU to CPD,         | 16   | 7    |      | 20     |       | 24     |        | ns   | 4.5   | Fig.13                                     |  |  |

|        | CPD to CPU                    | 14   | 6    |      | 17     |       | 20     |        |      | 6.0   |                                            |  |  |

|        |                               | 4.0  | 12   |      | 3.2    |       | 2.6    |        |      | 2.0   |                                            |  |  |

| fmax   | maximum up, down              | 20   | 36   |      | 16     |       | 13     |        | MHz  | 4.5   | Fig.7                                      |  |  |

|        | clock pulse frequency         | 24   | 43   |      | 19     |       | 15     |        |      | 6.0   |                                            |  |  |

### DC CHARACTERISTICS FOR 74HCT

Output capability: standard I<sub>CC</sub> category: MSI

## Note to HCT types

The value of additional quiescent supply current ( $\triangle$ ICC) for a unit load of 1 is given in the family specifications. To determine  $\triangle$ ICC per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT                             | UNIT LOAD COEFFICIENT |

|-----------------------------------|-----------------------|

| Dn                                | 0.35                  |

| CP <sub>U</sub> , CP <sub>D</sub> | 1.40                  |

| PL                                | 0.65                  |

| MR                                | 1.05                  |

## **AC CHARACTERISTICS FOR 74HCT**

GND = 0 V;  $t_r = t_f = 6 \text{ ns}$ ;  $C_L = 50 \text{ pF}$

|                                     |                                                                                    |      |      | T    | amb ( | °C)   |             |      |      | TEST CONDITIONS |           |  |

|-------------------------------------|------------------------------------------------------------------------------------|------|------|------|-------|-------|-------------|------|------|-----------------|-----------|--|

| SYMBOL                              | PARAMETER                                                                          |      |      |      | 74HC  | Т     |             |      | UNIT | VCC             |           |  |

| STWIBOL                             | PARAMETER                                                                          |      | +25  |      | -40 t | o +85 | -40 to +125 |      | ONT  | (V)             | WAVEFORMS |  |

|                                     |                                                                                    | min. | typ. | max. | min.  | max.  | min.        | max. |      | (*)             |           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP <sub>∪</sub> , CP <sub>D</sub> to Qn                       |      | 23   | 43   |       | 54    |             | 65   | ns   | 4.5             | Fig.7     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay CPU to $\overline{TC}_U$                                         |      | 16   | 30   |       | 38    |             | 45   | ns   | 4.5             | Fig.8     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay CPD to $\overline{TC}_D$                                         |      | 17   | 30   |       | 38    |             | 45   | ns   | 4.5             | Fig.8     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay  PL to Qn                                                        |      | 28   | 46   |       | 58    |             | 69   | ns   | 4.5             | Fig.9     |  |

| t <sub>PHL</sub>                    | propagation delay MR to Qn                                                         |      | 24   | 40   |       | 50    |             | 60   | ns   | 4.5             | Fig.10    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>Dn to Qn                                                      |      | 36   | 62   |       | 78    |             | 93   | ns   | 4.5             | Fig.9     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay $\overline{PL}$ to $\overline{TC}_U$ , $PL$ to $\overline{TC}_D$ |      | 36   | 64   |       | 80    |             | 96   | ns   | 4.5             | Fig.12    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay MR to $\overline{TC}_{U}$ , MR to $\overline{TC}_{D}$            |      | 36   | 64   |       | 80    |             | 96   | ns   | 4.5             | Fig.12    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay Dn to $\overline{TC}_{U}$ , Dn to $\overline{TC}_{D}$            |      | 33   | 58   |       | 73    |             | 87   | ns   | 4.5             | Fig.12    |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                                             |      | 7    | 15   |       | 19    |             | 22   | ns   | 4.5             | Fig.10    |  |

| t <sub>W</sub>                      | up, down clock pulse width HIGH or LOW                                             | 25   | 14   |      | 31    |       | 38          |      | ns   | 4.5             | Fig.7     |  |

| t <sub>W</sub> | master reset pulse width HIGH                                                       | 16 | 6  | 20 | 24 | ns  | 4.5 | Fig.10                                  |

|----------------|-------------------------------------------------------------------------------------|----|----|----|----|-----|-----|-----------------------------------------|

| t <sub>W</sub> | parallel load pulse width LOW                                                       | 20 | 10 | 25 | 30 | ns  | 4.5 | Fig.9                                   |

| trem           | removal time PL to CP <sub>U</sub> , CP <sub>D</sub>                                | 10 | 1  | 13 | 15 | ns  | 4.5 | Fig.9                                   |

| trem           | removal time MR to CP <sub>U</sub> , CP <sub>D</sub>                                | 10 | 2  | 13 | 15 | ns  | 4.5 | Fig.10                                  |

| tsu            | set-up time Dn to PL                                                                | 16 | 8  | 20 | 24 | ns  | 4.5 | Fig.11 note:<br>$CP_U = CP_D =$<br>HIGH |

| th             | hold time Dn to PL                                                                  | 0  | -6 | 0  | 0  | ns  | 4.5 | Fig.11                                  |

| th             | hold time  CP <sub>U</sub> to CP <sub>D</sub> ,  CP <sub>D</sub> to CP <sub>U</sub> | 20 | 9  | 25 | 30 | ns  | 4.5 | Fig.13                                  |

| fmax           | maximum up, down clock pulse frequency                                              | 20 | 41 | 16 | 13 | MHz | 4.5 | Fig.7                                   |

## **AC WAVEFORMS**

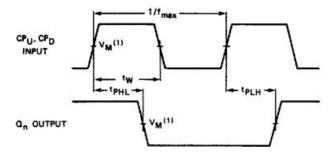

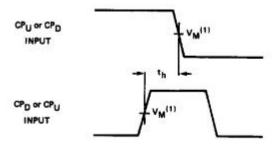

(1) HC :  $V_M = 50\%$ ;  $V_I = GND$  to  $V_{CC}$ .

HCT: V<sub>M</sub> = 1.3 V; V<sub>I</sub> = GND to 3 V.

Fig.7 Wave forms showing the clock (CP<sub>U</sub>, CP<sub>D</sub>) to output (Qn) propagation delays, the clock pulse width and the maximum clock pulse frequency.

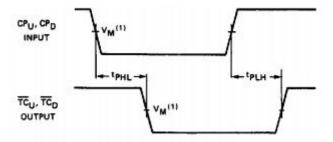

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ .

HCT:  $V_M = 1.3 V$ ;  $V_I = GND$  to 3 V.

Fig.8 Wave forms showing the clock ( $CP_U$ ,  $CP_D$ ) to terminal count output ( $\overline{TC}_U$ ,  $\overline{TC}_D$ ) propagation delays.

(1) HC :  $V_M = 50\%$ ;  $V_I = GND$  to  $V_{CC}$ .

HCT: V<sub>M</sub> = 1.3 V; V<sub>I</sub> = GND to 3 V.

Fig.9 Wave forms showing the parallel load input ( $\overline{PL}$ ) and data (Dn) to Qn output propagation delays and  $\overline{PL}$  removal time to clock input ( $\overline{CP_U}$ ,  $\overline{CP_D}$ ).

(1) HC :  $V_M = 50\%$ ;  $V_I = GND$  to  $V_{CC}$ .

HCT:  $V_M = 1.3 V$ ;  $V_I = GND$  to 3 V.

Fig.10 Wave forms showing the master reset input (MR) pulse width, MR to Qn propagation delays, MR to  $CP_U$ ,  $CP_D$  removal time and output transition times.

The shaded areas indicate when the input is permitted to change for predictable output performance.

(1) HC :  $V_M = 50\%$ ;  $V_I = GND$  to  $V_{CC}$ .

HCT:  $V_M = 1.3 \text{ V}$ ;  $V_I = \text{GND to 3 V}$ .

Fig.11 Waveforms showing the data input (Dn) to parallel load input (PL) set-up and hold times.

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ .

HCT:  $V_M = 1.3 V$ ;  $V_I = GND$  to 3 V.

Fig.12 Waveforms showing the data input (Dn), parallel load input ( $\overline{PL}$ ) and the master reset input (MR) to the terminal count outputs ( $\overline{TC}_{D}$ ) propagation delays.

(1) HC :  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ . HCT:  $V_M$  = 1.3 V;  $V_I$  = GND to 3 V.

Fig.13 Waveforms showing the CP<sub>U</sub> to CP<sub>D</sub> or CPD to CPU hold times.

# **APPLICATION INFORMATION**

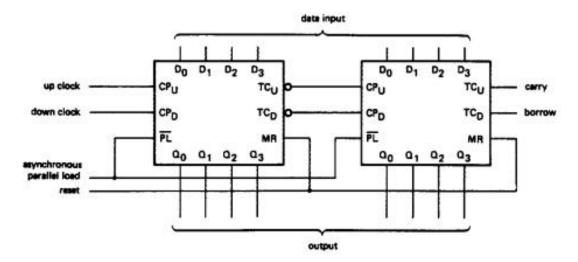

Fig.14 Cascaded up/down counter with parallel load.

# **PHYSICAL DIMENSIONS**

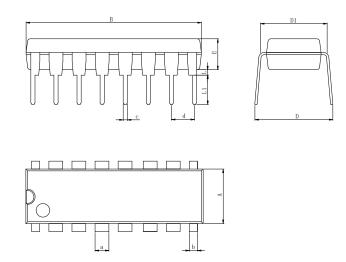

## DIP-16

| Dimensions In Millimeters(DIP-16) |      |       |      |      |      |      |      |      |      |      |          |

|-----------------------------------|------|-------|------|------|------|------|------|------|------|------|----------|

| Symbol:                           | Α    | В     | D    | D1   | E    | L    | L1   | а    | b    | С    | d        |

| Min:                              | 6.10 | 18.94 | 8.10 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 0.54.000 |

| Max:                              | 6.68 | 19.56 | 10.9 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

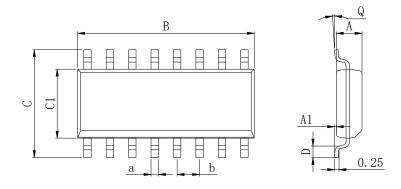

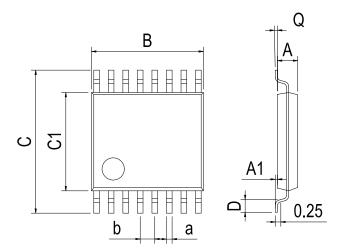

## SOP-16

| Dimensions In Millimeters(SOP-16) |      |      |      |      |      |      |    |      |          |  |  |

|-----------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                           | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                              | 1.35 | 0.05 | 9.80 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |  |

| Max:                              | 1.55 | 0.20 | 10.0 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 630 |  |  |

## TSSOP-16

| Dimensions In M | Dimensions In Millimeters(TSSOP-16) |      |      |      |      |      |    |      |          |  |  |  |

|-----------------|-------------------------------------|------|------|------|------|------|----|------|----------|--|--|--|

| Symbol:         | Α                                   | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |  |

| Min:            | 0.85                                | 0.05 | 4.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65 BSC |  |  |  |

| Max:            | 0.95                                | 0.20 | 5.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 | 0.00 650 |  |  |  |

# **REVISION HISTORY**

| DATE      | REVISION                                                                                                                      | PAGE      |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|-----------|

| 2018-9-8  | New                                                                                                                           | 1-17      |

| 2023-9-15 | Modify the package dimension diagram TSSOP-16、Update encapsulation type、Update Soldering temperature、Updated DIP-16 dimension | 1、3、14、15 |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.