## TS63420K – 1.9Ω On Resistance GaN Broadband RF Switch SP4T

### 1.0 Features

- Ultra low 1.9Ω on resistance

- 0.35pF C<sub>off</sub>

- RF peak voltage handling of 100V

- Each state can be controlled independently

- 16 possible independent state configuration

- No external DC blocking capacitors on RF lines

- Versatile 2.6~5.5V power supply

- 1.2~5.0V digital control

## 2.0 Applications

- Filter and antenna tuning

- Dynamic matching

- Private mobile radio handsets

- Public safety handsets

- Cellular infrastructure

- Satellite terminals

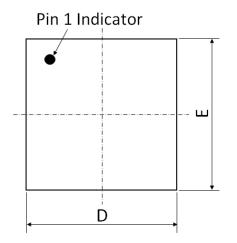

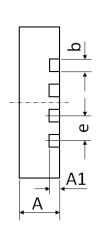

Figure 1 Device Image (16 Pin 3x3x0.8mm QFN Package)

RoHS/REACH/Halogen Free Compliance

# 3.0 Description

The TS63420K is a reflective open Single Pole Four Throw (SP4T) switch designed for antenna or filter tuning applications where high RF peak voltage handling is desired. TS63420K is suitable for frequency range from 1MHz to 1GHz. The TS63420K has a very low 1.9 $\Omega$  on resistance and off capacitance of 0.35pF. This switch can select up to 16 independent states.

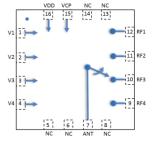

Figure 2 Function Block Diagram (Top View)

# 4.0 Ordering Information

**Table 1 Ordering Information**

| Base Part<br>Number | Package Type            | Form          | Qty  | Reel<br>Diameter | Reel<br>Width | Orderable<br>Part Number |

|---------------------|-------------------------|---------------|------|------------------|---------------|--------------------------|

| TS63420K            | 16 Pin 3×3×0.8mm<br>QFN | Tape and Reel | 3000 | 13" (330mm)      | 18mm          | TS63420KMTRPBF           |

| Evaluation Board    |                         |               |      |                  |               | TS63420K-EVB             |

## 5.0 Pin Description

**Table 2 Pin Definition**

| Pin Number  | Pin Name | Description                                                                                                |

|-------------|----------|------------------------------------------------------------------------------------------------------------|

| 1           | V1       | Switch control input 1                                                                                     |

| 2           | V2       | Switch control input 2                                                                                     |

| 3           | V3       | Switch control input 3                                                                                     |

| 4           | V4       | Switch control input 4                                                                                     |

| 5,6,8,13,14 | NC       | No internal connection, can be grounded                                                                    |

| 7           | ANT      | Antenna port                                                                                               |

| 9           | RF4      | RF port 4                                                                                                  |

| 10          | RF3      | RF port 3                                                                                                  |

| 11          | RF2      | RF port 2                                                                                                  |

| 12          | RF1      | RF port 1                                                                                                  |

| 15          | VCP      | Internal charge pump voltage output. Connect a 1nF capacitor to GND on this pin to improve switching time. |

| 16          | VDD      | DC power supply                                                                                            |

**Note:** The backside ground (thermal) pad of the package must be grounded directly to the ground plane of PCB with multiple vias to ensure proper operation and thermal management.

## 6.0 Absolute Maximum Ratings

Table 3 Absolute Maximum Ratings @T<sub>A</sub>=+25°C Unless Otherwise Specified

| Parameter                                           | Symbol            | Value        | Unit |  |  |  |  |  |

|-----------------------------------------------------|-------------------|--------------|------|--|--|--|--|--|

| Electrical Ratings                                  |                   |              |      |  |  |  |  |  |

| Power Supply Voltage                                | VDD               | 2.6 to 5.5   | V    |  |  |  |  |  |

| Storage Temperature Range                           | T <sub>st</sub>   | -55 to +125  | °C   |  |  |  |  |  |

| Operating Temperature Range                         | Тор               | -40 to +85   | °C   |  |  |  |  |  |

| Maximum Junction Temperature                        | TJ                | +140         | °C   |  |  |  |  |  |

| RF Input Power CW, 800MHz                           | RFx               | 41           | dBm  |  |  |  |  |  |

| Thermal Ratings                                     |                   |              |      |  |  |  |  |  |

| Thermal Resistance (junction-to-case) – Bottom side | Rejc              | 20           | °C/W |  |  |  |  |  |

| Thermal Resistance (junction-to-top)                | R <sub>θ</sub> ЈТ | ≤ 39         | °C/W |  |  |  |  |  |

| Soldering Temperature                               | T <sub>SOLD</sub> | 260          | °C   |  |  |  |  |  |

| ESD Rating                                          | gs                |              |      |  |  |  |  |  |

| Human Body Model (HBM)                              | Level 1B          | 500 to <1000 | V    |  |  |  |  |  |

| Charged Device Model (CDM)                          | Level C3          | ≥1000        | V    |  |  |  |  |  |

| Moisture Rating                                     |                   |              |      |  |  |  |  |  |

| Moisture Sensitivity Level                          | MSL               | 1            | -    |  |  |  |  |  |

### Attention:

Maximum ratings are absolute ratings. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Exceeding one or a combination of the absolute maximum ratings may cause permanent and irreversible damage to the device and/or to surrounding circuit.

# 7.0 Electrical Specifications

**Table 4 Electrical Specifications** @T<sub>A</sub>=+25°C Unless Otherwise Specified; VDD=+2.7V; 50Ω Source/Load.

| Parameter                   | Condition                                                           | Minimum | Typical | Maximum | Unit |

|-----------------------------|---------------------------------------------------------------------|---------|---------|---------|------|

| Operating Frequency         |                                                                     | 10      |         | 1000    | MHz  |

| ON Resistance               | On state, DC measurement                                            |         | 1.9     |         | Ω    |

| OFF Capacitance             | Total capacitance of each OFF path                                  |         | 0.35    |         | pF   |

| RF Peak Voltage             | Measured with $50\Omega$                                            |         | 100     |         | V    |

| Insertion Loss, RFx         | 100MHz                                                              |         | 0.25    |         | dB   |

|                             | 500MHz                                                              |         | 0.40    |         |      |

|                             | 1.0GHz                                                              |         | 0.60    |         |      |

| Isolation ANT-RFx           | 100MHz                                                              |         | 37      |         | dB   |

|                             | 500MHz                                                              |         | 25      |         |      |

|                             | 1.0GHz                                                              |         | 20      |         |      |

| Return Loss ANT-            | 100MHz                                                              |         | 30      |         | dB   |

| RFx                         | 500MHz                                                              |         | 18      |         |      |

|                             | 1.0GHz                                                              |         | 16      |         |      |

| H2                          | 800MHz, Pin=35dBm                                                   |         | 80      |         | dBc  |

| H3                          | 800MHz, Pin=35dBm                                                   |         | 85      |         | dBc  |

| IIP3                        | 800MHz                                                              |         | 71      |         | dBm  |

| P0.1dB <sup>[1]</sup>       | 1~10MHz                                                             |         | 40      |         | dBm  |

| P0.10D(1)                   | 10~1000MHz                                                          |         | 42      |         | dBm  |

| Switching Time              | 50% ctrl to 10/90% of the RF value is settled. C1=1nF to Gnd on VCP |         | 2.0     |         | μS   |

| Start-up Time               | 50% ctrl to 10/90% of the RF value is settled. C1=1nF to Gnd on VCP |         | TBD     |         | μS   |

| Control Voltage             | Power supply VDD                                                    | 2.6     | 2.7     | 5.5     | V    |

|                             | All control pins high, Vih                                          | 1.0     | 2.7     | 5.25    | V    |

|                             | All control pins low, Vil                                           | -0.3    |         | 0.5     | V    |

| Control Current             | All control pins low, Iii                                           |         | 0       |         | μΑ   |

|                             | All control pins high, Iih                                          |         |         | 7.5     | μΑ   |

| Current<br>Consumption, IDD | Active mode                                                         |         | 160     | 200     | μА   |

#### Note:

- [1] P0.1dB is a figure of merit.

- [2] No external DC blocking capacitors required on RF pins unless DC voltage is applied on a RF pin.

- [3] Start-up time is the time from VDD ON to RF signal settled on a throw or transition time from low power mode to active mode.

### 8.0 Switch Truth Table

**Table 5 Switch Truth Table**

| V1 | V2 | V3 | V4 | Active RF Path |

|----|----|----|----|----------------|

| 0  | 0  | 0  | 0  | All OFF state  |

| 0  | 0  | 0  | 1  | RF4            |

| 0  | 0  | 1  | 0  | RF3            |

| 0  | 0  | 1  | 1  | RF3, RF4       |

| 0  | 1  | 0  | 0  | RF2            |

| 0  | 1  | 0  | 1  | RF2, RF4       |

| 0  | 1  | 1  | 0  | RF2, RF3       |

| 0  | 1  | 1  | 1  | RF2, RF3, RF4  |

| 1  | 0  | 0  | 0  | RF1            |

| 1  | 0  | 0  | 1  | RF1, RF4       |

| 1  | 0  | 1  | 0  | RF1, RF3       |

| 1  | 0  | 1  | 1  | RF1, RF3, RF4  |

| 1  | 1  | 0  | 0  | RF1, RF2       |

| 1  | 1  | 0  | 1  | RF1, RF2, RF4  |

| 1  | 1  | 1  | 0  | RF1, RF2, RF3  |

| 1  | 1  | 1  | 1  | All ON state   |

#### Attention:

- [1] VDD should be applied first before V1, V2, V3 and V4, otherwise may cause damage to the device.

- [2] There are internal pull-downs to ground on all control pins, the state at start-up without any control voltage applied will be All OFF.

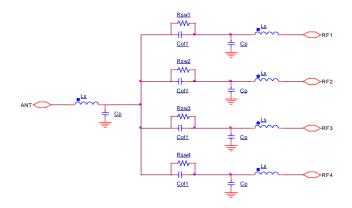

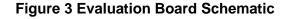

### 9.0 Evaluation Board

**Figure 4 Evaluation Board Image**

**Table 6 Recommended Values**

| Component | Value       | Unit |  |

|-----------|-------------|------|--|

| Ср        | 0.25        | pF   |  |

| Coff      | 0.35        | pF   |  |

| Rswx      | 1.9 if ON   | Ω    |  |

| RSWX      | 500K if OFF | Ω    |  |

| Ls        | 0.4         | nH   |  |

Note: Ron/Off is measured at DC. This model will not accurately predict losses in a tunable filter or antenna design

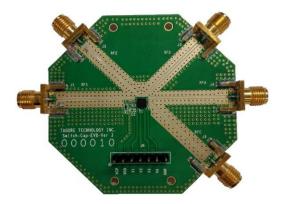

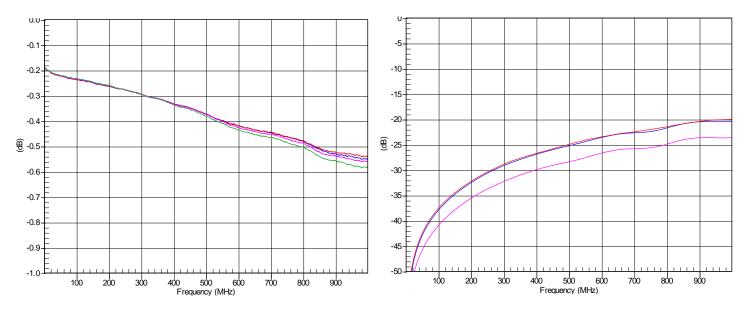

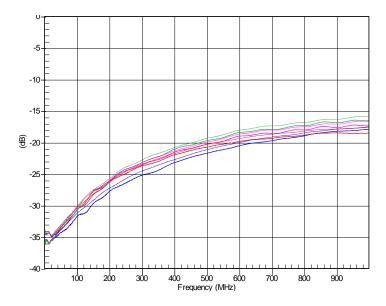

# **10.0 Typical Characteristics**

Figure 5 RF1 - 4 Insertion Loss

Figure 6 RF2 - 4 Isolation

Figure 7 Return Loss

# 11.0 Device Package Information

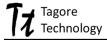

Figure 8 Device Package Drawing

(All dimensions are in mm)

**Table 7 Device Package Dimensions**

| Dimension (mm) | Value (mm) | Tolerance (mm) | Dimension (mm) | Value (mm) | Tolerance (mm) |

|----------------|------------|----------------|----------------|------------|----------------|

| Α              | 0.80       | ±0.05          | Е              | 3.00 BSC   | ±0.05          |

| A1             | 0.203      | ±0.02          | E1             | 1.70       | ±0.05          |

| b              | 0.25       | +0.05/-0.07    | F              | 0.625      | ±0.05          |

| D              | 3.00 BSC   | ±0.05          | G              | 0.625      | ±0.05          |

| D1             | 1.70       | ±0.05          | L              | 0.25       | ±0.05          |

| е              | 0.50 BSC   | ±0.05          | K              | 0.40       | ±0.05          |

**Note:** Lead finish: Pure Sn without underlayer; Thickness: 7.5μm ~ 20μm (Typical 10μm ~ 12μm)

### Attention:

Please refer to application notes *TN-001* and *TN-002* at http://www.tagoretech.com for PCB and soldering related guidelines.

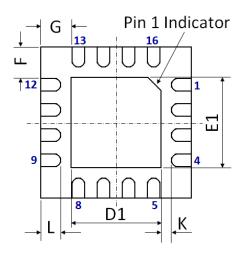

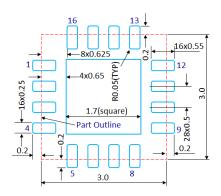

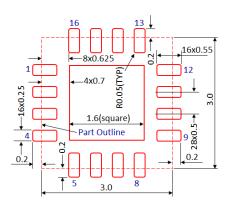

## 12.0 PCB Land Design

### **Guidelines:**

- [1] 4 layer PCB is recommended.

- [2] Via diameter is recommended to be 0.2mm to prevent solder wicking inside the vias.

- [3] Thermal vias shall only be placed on the center pad.

- [4] The maximum via number for the center pad is  $3(X)\times3(Y)=9$ .

Figure 9 PCB Land Pattern (Dimensions are in mm)

O.07Max

All Around

Non-Solder Mask Defined (Preferred)

Solder Mask Opening

Solder Mask Defined

Solder Mask

Figure 10 Solder Mask Pattern

(Dimensions are in mm)

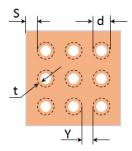

Figure 11 Thermal Via Pattern

(Recommended Values: S≥0.15mm; Y≥0.20mm; d=0.2mm; Plating Thickness t=25µm or 50µm)

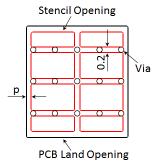

## 13.0 PCB Stencil Design

### **Guidelines:**

- [1] Laser-cut, stainless steel stencil is recommended with electro-polished trapezoidal walls to improve the paste release.

- [2] Stencil thickness is recommended to be 125µm.

Figure 12 Stencil Openings

(Dimensions are in mm)

Figure 13 Stencil Openings Shall not Cover Via Areas If Possible (Dimensions are in mm)

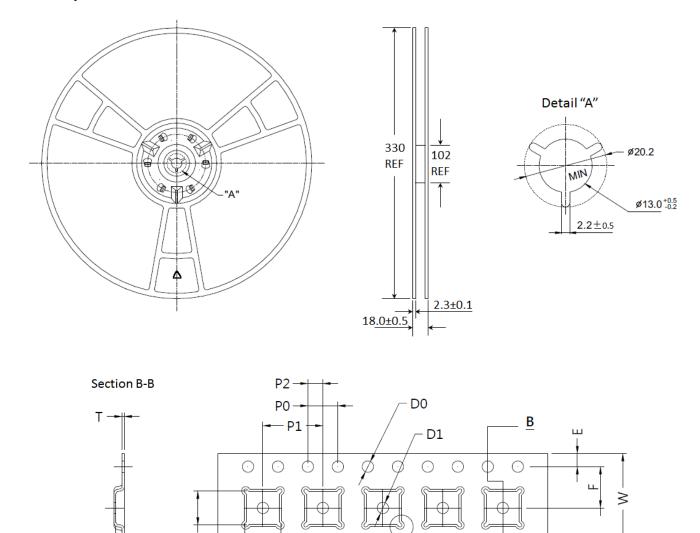

# 14.0 Tape and Reel Information

**Figure 14 Tape and Reel Drawing**

→ A0 +

**Table 8 Tape and Reel Dimensions**

| Dimension (mm) | Value (mm) | Tolerance (mm) | Dimension (mm) | Value (mm) | Tolerance (mm) |

|----------------|------------|----------------|----------------|------------|----------------|

| A0             | 3.35       | ±0.10          | K0             | 1.10       | ±0.10          |

| В0             | 3.35       | ±0.10          | P0             | 4.00       | ±0.10          |

| D0             | 1.50       | +0.10/-0.00    | P1             | 8.00       | ±0.10          |

| D1             | 1.50       | +0.10/-0.00    | P2             | 2.00       | ±0.05          |

| E              | 1.75       | ±0.10          | Т              | 0.30       | ±0.05          |

| F              | 5.50       | ±0.05          | W              | 12.00      | ±0.30          |

K0 -

В

### Edition Revision 1.6 - 2020-04-24

## **Published by**

Tagore Technology Inc. 5 East College Drive, Suite 200 Arlington Heights, IL 60004, USA

©2018 All Rights Reserved

### **Legal Disclaimer**

The information provided in this document shall in no event be regarded as a guarantee of conditions or characteristics. Tagore Technology assumes no responsibility for the consequences of the use of this information, nor for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of Tagore Technology. The specifications mentioned in this document are subject to change without notice.

### Information

For further information on technology, delivery terms and conditions and prices, please contact Tagore Technology: support@tagoretech.com.