# 80C51 8-Bit Microcontroller

The 87C552 Single-Chip 8-Bit Microcontroller is manufactured in an advanced CMOS process and is a derivative of the 80C51 microcontroller family. The 87C552 has the same instruction set as the 80C51.

The 87C552 contains a 8k × 8 non-volatile EPROM, a 256 × 8 read/write data memory, five 8-bit I/O ports, one 8-bit input port, two 16-bit timer/event counters (identical to the timers of the 80C51), an additional 16-bit timer coupled to capture and compare latches, a 15-source, four-priority-level, nested interrupt structure, an 8-input ADC, a dual DAC pulse width modulated interface, two serial interfaces (UART and I2C-bus), a *watchdog* timer and on-chip oscillator and timing circuits. For systems that require extra capability, the 8xC552 can be expanded using standard TTL compatible memories and logic.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# FOR REFERENCE ONLY

# INTEGRATED CIRCUITS

low power

Product data Supersedes data of 1999 Mar 30 2003 Apr 01

# DESCRIPTION

The 87C552 Single-Chip 8-Bit Microcontroller is manufactured in an advanced CMOS process and is a derivative of the 80C51 microcontroller family. The 87C552 has the same instruction set as the 80C51.

The 87C552 contains a 8k × 8 non-volatile EPROM, a 256 × 8 read/write data memory, five 8-bit I/O ports, one 8-bit input port, two 16-bit timer/event counters (identical to the timers of the 80C51), an additional 16-bit timer coupled to capture and compare latches, a 15-source, four-priority-level, nested interrupt structure, an 8-input ADC, a dual DAC pulse width modulated interface, two serial interfaces (UART and I<sup>2</sup>C-bus), a "watchdog" timer and on-chip oscillator and timing circuits. For systems that require extra capability, the 8xC552 can be expanded using standard TTL compatible memories and logic.

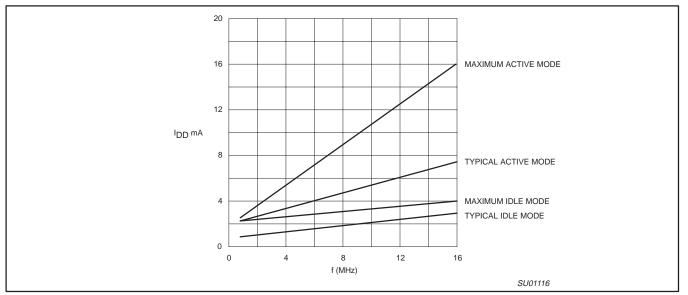

In addition, the 8xC552 has two software selectable modes of power reduction—idle mode and power-down mode. The idle mode freezes the CPU while allowing the RAM, timers, serial ports, and interrupt system to continue functioning. Optionally, the ADC can be operated in Idle mode. The power-down mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative.

The device also functions as an arithmetic processor having facilities for both binary and BCD arithmetic plus bit-handling capabilities. The instruction set consists of over 100 instructions: 49 one-byte, 45 two-byte, and 17 three-byte. With a 16MHz crystal, 58% of the instructions are executed in 0.75µs and 40% in 1.5µs. Multiply and divide instructions require 3µs.

# **FEATURES**

- 80C51 central processing unit

- 8k × 8 EPROM expandable externally to 64k bytes

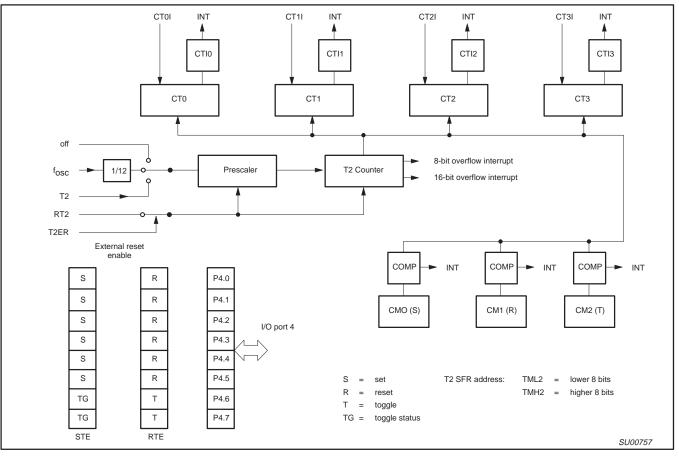

- An additional 16-bit timer/counter coupled to four capture registers and three compare registers

- Two standard 16-bit timer/counters

- 256 × 8 RAM, expandable externally to 64k bytes

- Capable of producing eight synchronized, timed outputs

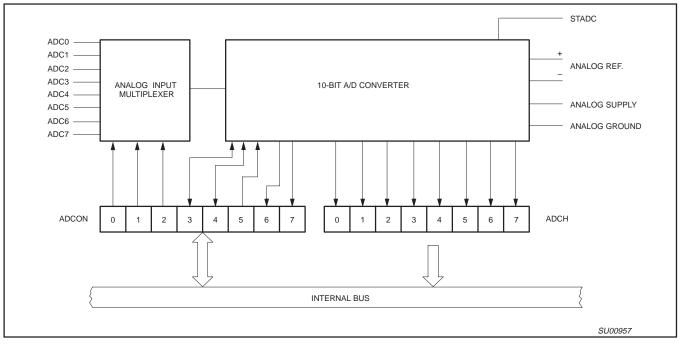

- A 10-bit ADC with eight multiplexed analog inputs

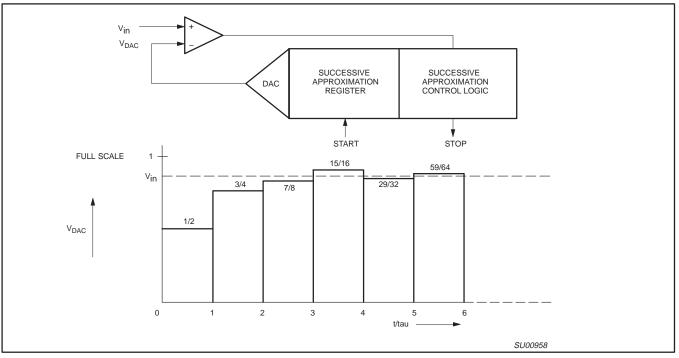

- Fast 8-bit ADC option

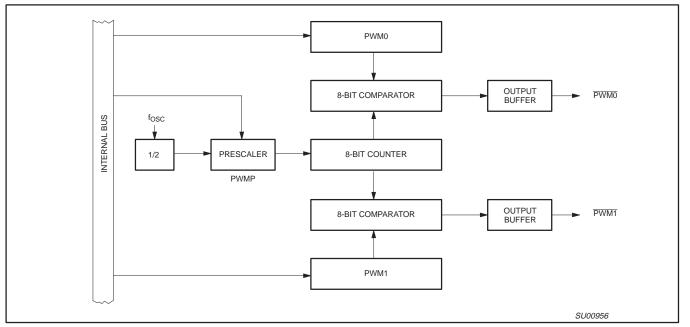

- Two 8-bit resolution, pulse width modulation outputs

- Five 8-bit I/O ports plus one 8-bit input port shared with analog inputs

- I<sup>2</sup>C-bus serial I/O port with byte oriented master and slave functions

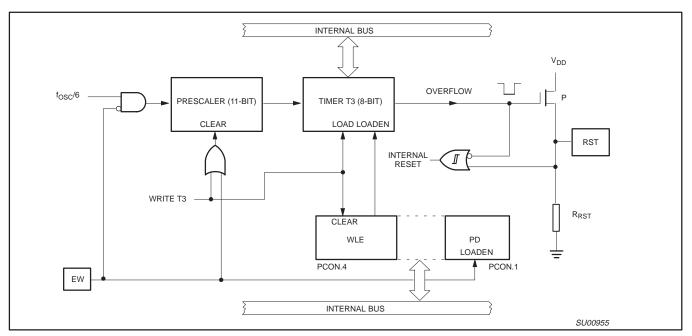

- On-chip watchdog timer

- Extended temperature ranges

- Full static operation 0 to 16 MHz

- Operating voltage range: 2.7V to 5.5V (0 to 16MHz)

- Security bits:

- OTP/EPROM 3 bits

- Encryption array 64 bytes

- 4 level priority interrupt

- 15 interrupt sources

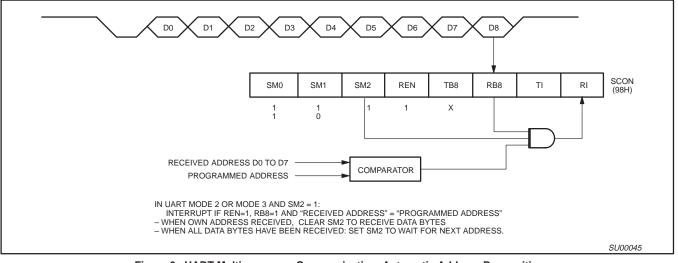

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Power control modes

- Clock can be stopped and resumed

- Idle mode

- Power down mode

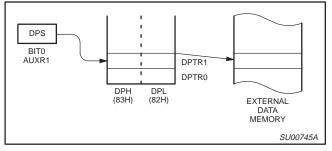

- Second DPTR register

- ALE inhibit for EMI reduction

- Programmable I/O pins

- Wake-up from power-down by external interrupts

- Software reset

- Power-on detect reset

- ADC charge pump disable

- ONCE mode

- ADC active in Idle mode

# ORDERING INFORMATION

| OTP/EPROM   | TEMPERATURE °C AND PACKAGE            | FREQ.<br>(MHz) | DRAWING NUMBER |

|-------------|---------------------------------------|----------------|----------------|

| P87C552SBAA | 0 to +70, Plastic Leaded Chip Carrier | 16             | SOT188–3       |

# PART NUMBER DERIVATION

| DEVICE NUMBER (P87C552) | FREQUENCY MAX (S) | TEMPERATURE RANGE (B)                                                               | PACKAGE (AA) |

|-------------------------|-------------------|-------------------------------------------------------------------------------------|--------------|

| P87C552 OTP             | S = 16 MHz        | $B = 0^{\circ}C \text{ to } 70^{\circ}C$ $F = -40^{\circ}C \text{ to } 85^{\circ}C$ | AA = PLCC    |

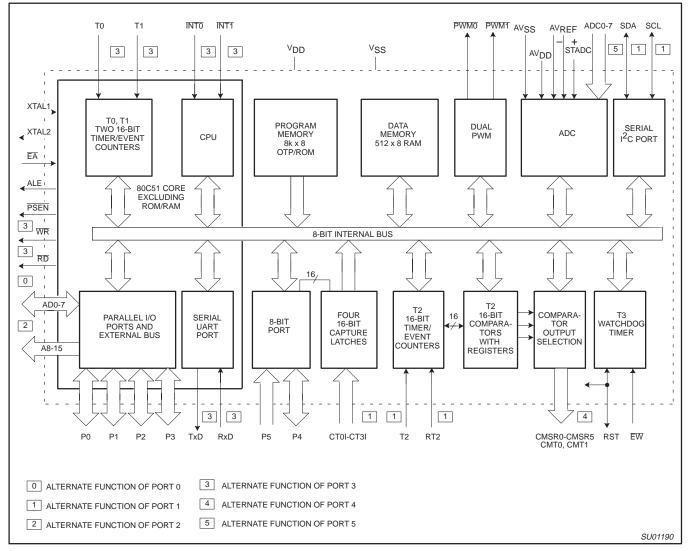

# **BLOCK DIAGRAM**

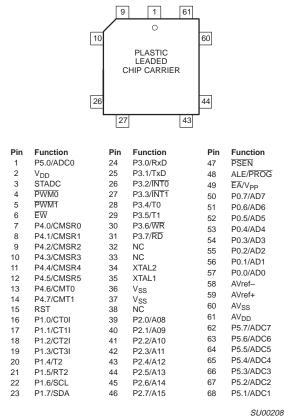

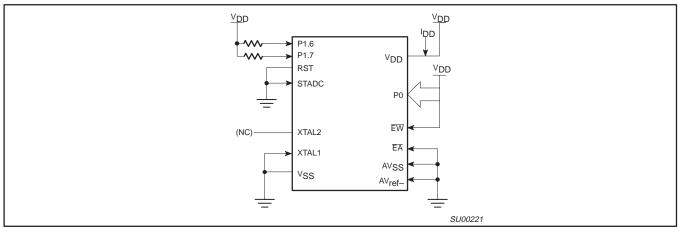

# PIN CONFIGURATIONS Plastic Leaded Chip Carrier pin functions

# **PIN DESCRIPTION**

|                 | PIN   | NO.             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-----------------|-------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MNEMONIC        | PLCC  | QFP             | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| V <sub>DD</sub> | 2     | 72              | I    | <b>Digital Power Supply:</b> Positive voltage power supply pin during normal operation, idle and power-down mode.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| STADC           | 3     | 74              | I    | Start ADC Operation: Input starting analog to digital conversion (ADC operation can also be started by software).                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| PWM0            | 4     | 75              | 0    | Pulse Width Modulation: Output 0.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| PWM1            | 5     | 76              | 0    | Pulse Width Modulation: Output 1.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| EW              | 6     | 77              | 1    | Enable Watchdog Timer: Enable for T3 watchdog timer and disable power-down mode.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P0.0-P0.7       | 57-50 | 58-51           | I/O  | <b>Port 0:</b> Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application it uses strong internal pull-ups when emitting 1s. Port 0 is also used to input the code byte during programming and to output the code byte during verification. |  |  |  |  |  |

| P1.0-P1.7       | 16-23 | 10-17           | I/O  | Port 1: 8-bit I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                 | 16-21 | 10-15           | I/O  | (P1.0-P1.5): Programmable I/O port pins.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                 | 22-23 | 16-17           | I/O  | (P1.6, P1.7): Open drain port pins.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                 | 16-19 | 10-13           |      | CT0I-CT3I (P1.0-P1.3): Capture timer input signals for timer T2.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                 | 20    | 14              |      | T2 (P1.4): T2 event input.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                 | 21    | 15              |      | <b>RT2 (P1.5):</b> T2 timer reset signal. Rising edge triggered.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

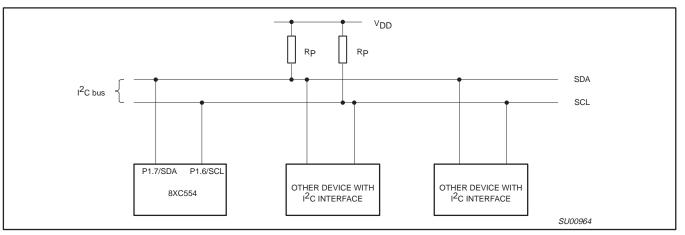

|                 | 22    | 16              | 1/0  | SCL (P1.6): Serial port clock line I <sup>2</sup> C-bus.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                 | 23    | 17              | I/O  | <b>SDA (P1.7):</b> Serial port data line I <sup>2</sup> C-bus.<br>Port 1 has four modes selected on a per bit basis by writing to the P1M1 and P1M2                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                 |       |                 |      | registers as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                 |       |                 |      | P1M1.xP1M2.xMode Description00Pseudo-bidirectional (standard c51 configuration; default)01Push-Pull10High impedance11Open drain                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                 |       |                 |      | Port 1 is also used to input the lower order address byte during EPROM programming and verification. A0 is on P1.0, etc.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| P2.0-P2.7       | 39-46 | 38-42,<br>45-47 | I/O  | <b>Port 2:</b> 8-bit programmable I/O port.<br>Alternate function: High-order address byte for external memory (A08-A15). Port 2 is also used to input the upper order address during EPROM programming and verification. A8 is on P2.0, A9 on P2.1, through A12 on P2.4.                                                                                                                                                                                              |  |  |  |  |  |

|                 |       |                 |      | Port 2 has four output modes selected on a per bit basis by writing to the P2M1 and P2M2 registers as follows:                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                 |       |                 |      | P2M1.xP2M2.xMode Description00Pseudo-bidirectional (standard c51 configuration; default)01Push-Pull10High impedance11Open drain                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| P3.0-P3.7       | 24-31 | 18-20,<br>23-27 | I/O  | Port 3: 8-bit programmable I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                 | 24    | 18              |      | RxD(P3.0): Serial input port.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                 | 25    | 19              |      | TxD (P3.1): Serial output port.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                 | 26    | 20              |      | INTO (P3.2): External interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                 | 27    | 23              |      | INT1 (P3.3): External interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                 | 28    | 24              |      | T0 (P3.4): Timer 0 external input.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                 | 29    | 25              |      | T1 (P3.5): Timer 1 external input.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                 | 30    | 26              |      | WR (P3.6): External data memory write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                 | 31    | 27              |      | RD (P3.7): External data memory read strobe.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                 |       |                 |      | Port 3 has four modes selected on a per bit basis by writing to the P3M1 and P3M2 registers as follows:                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                 |       |                 |      | P3M1.xP3M2.xMode Description00Pseudo-bidirectional (standard c51 configuration; default)01Push-Pull10High impedance11Open drain                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

# **PIN DESCRIPTION** (Continued)

|                    | PIN         | NO.            |      |                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|--------------------|-------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MNEMONIC           | PLCC        | QFP            | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| P4.0-P4.7          | 7-14        | 80, 1-2<br>4-8 | I/O  | Port 4: 8-bit programmable I/O port. Alternate functions include:                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                    | 7-12        | 80, 1-2<br>4-6 | 0    | <b>CMSR0-CMSR5 (P4.0-P4.5):</b> Timer T2 compare and set/reset outputs on a match with timer T2.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                    | 13, 14      | 7, 8           | 0    | CMT0, CMT1 (P4.6, P4.7): Timer T2 compare and toggle outputs on a match with timer T2.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                    |             |                |      | Port 4 has four modes selected on a per bit basis by writing to the P4M1 and P4M2 registers as follows:                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                    |             |                |      | P4M1.xP4M2.xMode Description00Pseudo-bidirectional (standard c51 configuration; default)01Push-Pull10High impedance11Open drain                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| P5.0-P5.7          | 68-62,<br>1 | 71-64          | I    | <b>Port 5:</b> 8-bit input port.<br><b>ADC0-ADC7 (P5.0-P5.7):</b> Alternate function: Eight input channels to the ADC.                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| RST                | 15          | 9              | I/O  | <b>Reset:</b> Input to reset the 87C552. It also provides a reset pulse as output when timer T3 overflows.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| XTAL1              | 35          | 32             | I    | <b>Crystal Input 1:</b> Input to the inverting amplifier that forms the oscillator, and input to the internal clock generator. Receives the external clock signal when an external oscillator is used.                                                                                                                                                                              |  |  |  |  |  |  |

| XTAL2              | 34          | 31             | 0    | <b>Crystal Input 2:</b> Output of the inverting amplifier that forms the oscillator. Left open-circuit when an external clock is used.                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| V <sub>SS</sub>    | 36, 37      | 34-36          | 1    | Digital ground.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| PSEN               | 47          | 48             | 0    | Program Store Enable: Active-low read strobe to external program memory.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| ALE/PROG           | 48          | 49             | 0    | Address Latch Enable: Latches the low byte of the address during accesses to external memory. It is activated every six oscillator periods. During an external data memory access, one ALE pulse is skipped. ALE can drive up to eight LS TTL inputs and handles CMOS inputs without an external pull-up. This pin is also the program pulse input (PROG) during EPROM programming. |  |  |  |  |  |  |

| EA/V <sub>PP</sub> | 49          | 50             | I    | <b>External Access:</b> When EA is held at TTL level high, the CPU executes out of the internal program ROM provided the program counter is less than 8,192. When EA is held at TTL low level, the CPU executes out of external program memory. EA is not allowed to float. This pin also receives the 12.75V programming supply voltage ( $V_{PP}$ ) during EPROM programming.     |  |  |  |  |  |  |

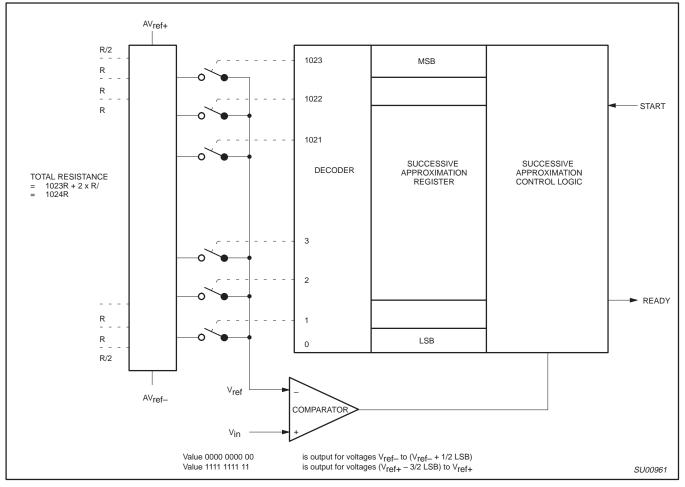

| AV <sub>REF-</sub> | 58          | 59             | 1    | Analog to Digital Conversion Reference Resistor: Low-end.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| AV <sub>REF+</sub> | 59          | 60             | I 1  | Analog to Digital Conversion Reference Resistor: High-end.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| AV <sub>SS</sub>   | 60          | 61             | I 1  | Analog Ground                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| AV <sub>DD</sub>   | 61          | 63             | 1    | Analog Power Supply                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

NOTE:

1. To avoid "latch-up" effect at power-on, the voltage on any pin at any time must not be higher or lower than  $V_{DD}$  + 0.5V or  $V_{SS}$  – 0.5V, respectively.

# Table 1. 87C552 Special Function Registers

| SYMBOL     | DESCRIPTION                                         | DIRECT<br>ADDRESS | MSB   | BI    | ADDRESS, | SYMBOL, OR | ALTERNATIV | E PORT FUN  | ICTION | LSB   | RESET<br>VALUE |

|------------|-----------------------------------------------------|-------------------|-------|-------|----------|------------|------------|-------------|--------|-------|----------------|

| ACC*       | Accumulator                                         | E0H               | E7    | E6    | E5       | E4         | E3         | E2          | E1     | E0    | 00H            |

| ADCH#      | A/D converter high                                  | C6H               |       |       |          |            |            |             |        |       | xxxxxxxB       |

| ADCON#     | A/D control                                         | C5H               | ADC.1 | ADC.0 | ADEX     | ADCI       | ADCS       | AADR2       | AADR1  | AADR0 | xx000000B      |

| AUXR       | Auxillary                                           | 8EH               | -     | -     | -        | -          | -          | LVADC       | -      | A0    | xxxxx110B      |

| AUXR1      | Auxillary                                           | A2H               | ADC8  | AIDL  | SRST     | GF2        | WUPD       | 0           | -      | DPS   | 000000x0B      |

| B*         | B register                                          | F0H               | F7    | F6    | F5       | F4         | F3         | F2          | F1     | F0    | 00H            |

| CTCON#     | Capture control                                     | EBH               | CTN3  | CTP3  | CTN2     | CTP2       | CTN1       | CTP1        | CTN0   | CTP0  | 00H            |

| CTH3#      | Capture high 3                                      | CFH               |       |       |          |            |            |             |        |       | xxxxxxxB       |

| CTH2#      | Capture high 2                                      | CEH               |       |       |          |            |            |             |        |       | хххххххВ       |

| CTH1#      | Capture high 1                                      | CDH               |       |       |          |            |            |             |        |       | хххххххВ       |

| CTH0#      | Capture high 0                                      | ССН               |       |       |          |            |            |             |        |       | хххххххВ       |

| CMH2#      | Compare high 2                                      | СВН               |       |       |          |            |            |             |        |       | 00H            |

| CMH1#      | Compare high 1                                      | CAH               |       |       |          |            |            |             |        |       | 00H            |

| CMH0#      | Compare high 0                                      | C9H               |       |       |          |            |            |             |        |       | 00H            |

| CTL3#      | Capture low 3                                       | AFH               |       |       |          |            |            |             |        |       | xxxxxxxB       |

| CTL2#      | Capture low 2                                       | AEH               |       |       |          |            |            |             |        |       | xxxxxxxB       |

| CTL1#      | Capture low 1                                       | ADH               |       |       |          |            |            |             |        |       | xxxxxxxB       |

| CTL0#      | Capture low 0                                       | ACH               |       |       |          |            |            |             |        |       | хххххххВ       |

| CML2#      | Compare low 2                                       | ABH               |       |       |          |            |            |             |        |       | 00H            |

| CML1#      | Compare low 1                                       | AAH               |       |       |          |            |            |             |        |       | 00H            |

| CML0#      | Compare low 0                                       | A9H               |       |       |          |            |            |             |        |       | 00H            |

| DPTR:      | Data pointer                                        |                   |       |       |          |            |            |             |        |       |                |

| DPH<br>DPL | (2 bytes):<br>Data pointer high<br>Data pointer low | 83H<br>82H        |       |       |          |            |            |             |        |       | 00H<br>00H     |

|            |                                                     |                   | AF    | AE    | AD       | AC         | AB         | AA          | A9     | A8    |                |

| IEN0*#     | Interrupt enable 0                                  | A8H               | EA    | EAD   | ES1      | ES0        | ET1        | EX1         | ET0    | EX0   | 00H            |

|            |                                                     |                   | EF    | EE    | ED       | EC         | EB         | EA          | E9     | E8    | ]              |

| IEN1*#     | Interrupt enable 1                                  | E8H               | ET2   | ECM2  | ECM1     | ECM0       | ECT3       | ECT2        | ECT1   | ECT0  | 00H            |

|            |                                                     |                   | BF    | BE    | BD       | BC         | BB         | BA          | B9     | B8    | 1              |

| IP0*#      | Interrupt priority 0                                | B8H               | -     | PAD   | PS1      | PS0        | PT1        | PX1         | PT0    | PX0   | x0000000B      |

|            |                                                     |                   | FF    | FE    | FD       | FC         | FB         | FA          | F9     | F8    | ]              |

| IP0H       | Interrupt priority 0 high                           | B7H               | -     | PADH  | PS1H     | PS0H       | PT1H       | PX1H        | PT0H   | PX0H  | x0000000B      |

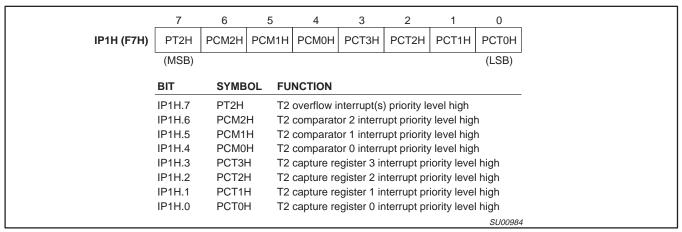

| IP1*#      | Interrupt priority1                                 | F8H               | PT2   | PCM2  | PCM1     | PCM0       | PCT3       | PCT2        | PCT1   | PCT0  | 00H            |

| IP1H       | Interrupt priority 1 high                           | F7H               | PT2H  | PCM2H | PCM1H    | PCM0H      | РСТ3H      | PCT2H       | PCT1H  | PCT0H | 00H            |

| P5#        | Port 5                                              | C4H               | ADC7  | ADC6  | ADC5     | ADC4       | ADC3       | ADC2        | ADC1   | ADC0  | xxxxxxxB       |

|            |                                                     |                   | C7    | C6    | C5       | C4         | C3         | C2          | C1     | C0    | 1              |

| P4#*       | Port 4                                              | COH               | CMT1  | CMT0  | CMSR5    | CMSR4      | CMSR3      | CMSR2       | CMSR1  | CMSR0 | FFH            |

|            |                                                     |                   | B7    | B6    | B5       | B4         | B3         | B2          | B1     | B0    | 1              |

| P3*        | Port 3                                              | B0H               | RD    | WR    | T1       | ТО         | INT1       | <b>INTO</b> | TXD    | RXD   | FFH            |

|            |                                                     |                   | A7    | A6    | A5       | A4         | A3         | A2          | A1     | A0    | 1              |

| P2*        | Port 2                                              | A0H               | A15   | A14   | A13      | A12        | A11        | A10         | A9     | A8    | FFH            |

|            |                                                     |                   | 97    | 96    | 95       | 94         | 93         | 92          | 91     | 90    | 1              |

| P1*        | Port 1                                              | 90H               | SDA   | SCL   | RT2      | T2         | CT3I       | CT2I        | CT1I   | CT0I  | FFH            |

|            |                                                     |                   | 87    | 86    | 85       | 84         | 83         | 82          | 81     | 80    | 1              |

| P0*        | Port 0                                              | 80H               | AD7   | AD6   | AD5      | AD4        | AD3        | AD2         | AD1    | AD0   | FFH            |

P87C552

# 80C51 8-bit microcontroller 8K/256 OTP, 8 channel 10 bit A/D, I<sup>2</sup>C, PWM, capture/compare, high I/O, low voltage (2.7 V to 5.5 V), low power

| SYMBOL                                     | DESCRIPTION                                                                               | DIRECT<br>ADDRESS                      | MSB    | BIT   | ADDRESS, S | SYMBOL, OR | ALTERNATIV | E PORT FUN | CTION | LSB   | RESET<br>VALUE                         |

|--------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|--------|-------|------------|------------|------------|------------|-------|-------|----------------------------------------|

| P1M1                                       | Port 1 output mode 1                                                                      | 92H                                    |        |       |            |            |            |            |       |       | xx000000B                              |

| P1M2                                       | Port 1 output mode 2                                                                      | 93H                                    |        |       |            |            |            |            |       |       | xx000000B                              |

| P2M1                                       | Port 2 output mode 1                                                                      | 94H                                    |        |       |            |            |            |            |       |       | 00H                                    |

| P2M2                                       | Port 2 output mode 2                                                                      | 95H                                    |        |       |            |            |            |            |       |       | 00H                                    |

| P3M1                                       | Port 3 output mode 1                                                                      | 9AH                                    |        |       |            |            |            |            |       |       | 00H                                    |

| P3M2                                       | Port 3 output mode 2                                                                      | 9BH                                    |        |       |            |            |            |            |       |       | 00H                                    |

| P4M1                                       | Port 4 output mode 1                                                                      | 9CH                                    |        |       |            |            |            |            |       |       | 00H                                    |

| P4M2                                       | Port 4 output mode 2                                                                      | 9DH                                    |        | _     | _          | _          |            |            | _     | _     | 00H                                    |

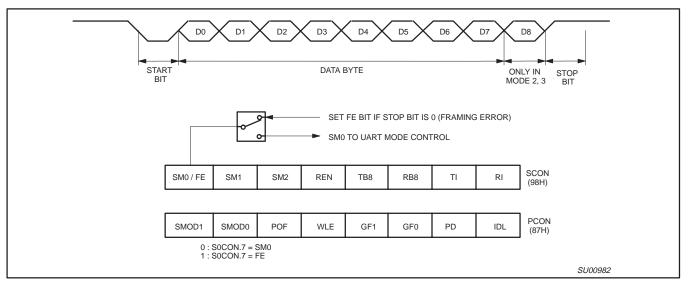

| PCON                                       | Power control                                                                             | 87H                                    | SMOD1  | SMOD0 | POF        | WLE        | GF1        | GFO        | PD    | IDL   | 00x00000B                              |

| PSW                                        | Program status word                                                                       | D0H                                    | CY     | AC    | FO         | RS1        | RS0        | OV         | F1    | Р     | 00H                                    |

| PWMP#                                      | PWM prescaler                                                                             | FEH                                    |        |       |            |            |            |            |       |       | 00H                                    |

| PWM1#                                      | PWM register 1                                                                            | FDH                                    |        |       |            |            |            |            |       |       | 00H                                    |

| PWM0#                                      | PWM register 0                                                                            | FCH                                    |        | -     |            |            |            |            | _     |       | 00H                                    |

| RTE#                                       | Reset/toggle enable                                                                       | EFH                                    | TP47   | TP46  | RP45       | RP44       | RP43       | RP42       | RP41  | RP40  | 00H                                    |

| SOADDR                                     | Serial 0 slave address                                                                    | F9H                                    |        |       |            |            |            |            |       |       | 00H                                    |

| SOADEN                                     | Slave address mask                                                                        | B9H                                    |        |       |            |            |            |            |       |       | 00H                                    |

| SOBUF                                      | Serial 0 data buffer                                                                      | 99H                                    |        |       |            |            |            |            |       |       | xxxxxxxB                               |

|                                            |                                                                                           |                                        | 9F     | 9E    | 9D         | 9C         | 9B         | 9A         | 99    | 98    |                                        |

| S0CON*                                     | Serial 0 control                                                                          | 98H                                    | SM0/FE | SM1   | SM2        | REN        | TB8        | RB8        | TI    | RI    | 00H                                    |

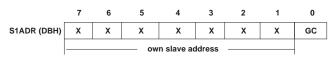

| S1ADR#                                     | Serial 1 address                                                                          | DBH                                    |        |       | SL         | AVE ADDRE  | SS         |            |       | GC    | 00H                                    |

| SIDAT#                                     | Serial 1 data                                                                             | DAH                                    |        |       |            |            |            |            |       |       | 00H                                    |

| S1STA#                                     | Serial 1 status                                                                           | D9H                                    | SC4    | SC3   | SC2        | SC1        | SC0        | 0          | 0     | 0     | F8H                                    |

|                                            |                                                                                           |                                        | DF     | DE    | DD         | DC         | DB         | DA         | D9    | D8    |                                        |

| SICON#*                                    | Serial 1 control                                                                          | D8H                                    | CR2    | ENS1  | STA        | ST0        | SI         | AA         | CR1   | CR0   | 00H                                    |

| SP                                         | Stack pointer                                                                             | 81H                                    |        |       |            |            |            |            |       |       | 07H                                    |

| STE#                                       | Set enable                                                                                | EEH                                    | TG47   | TG46  | SP45       | SP44       | SP43       | SP42       | SP41  | SP40  | СОН                                    |

| TH1<br>TH0<br>TL1<br>TL0<br>TMH2#<br>TML2# | Timer high 1<br>Timer high 0<br>Timer low 1<br>Timer low 0<br>Timer high 2<br>Timer low 2 | 8DH<br>8CH<br>8BH<br>8AH<br>EDH<br>ECH |        |       |            |            |            |            | -     |       | 00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| TMOD                                       | Timer mode                                                                                | 89H                                    | GATE   | C/T   | M1         | MO         | GATE       | C/T        | M1    | MO    | 00H                                    |

|                                            |                                                                                           |                                        | 8F     | 8E    | 8D         | 8C         | 8B         | 8A         | 89    | 88    | ]                                      |

| TCON*                                      | Timer control                                                                             | 88H                                    | TF1    | TR1   | TF0        | TR0        | IE1        | IT1        | IE0   | IT0   | 00H                                    |

| TM2CON#                                    | Timer 2 control                                                                           | EAH                                    | T2IS1  | T2IS0 | T2ER       | T2B0       | T2P1       | T2P0       | T2MS1 | T2MS0 | 00H                                    |

|                                            |                                                                                           |                                        | CF     | CE    | CD         | СС         | СВ         | CA         | C9    | C8    | ]                                      |

| TM2IR#*                                    | Timer 2 int flag reg                                                                      | C8H                                    | T20V   | CMI2  | CMI1       | CMI0       | CTI3       | CTI2       | CTI1  | CTI0  | 00H                                    |

| T3#                                        | Timer 3                                                                                   | FFH                                    |        |       |            |            |            |            |       |       | 00H                                    |

SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

## **OSCILLATOR CHARACTERISTICS**

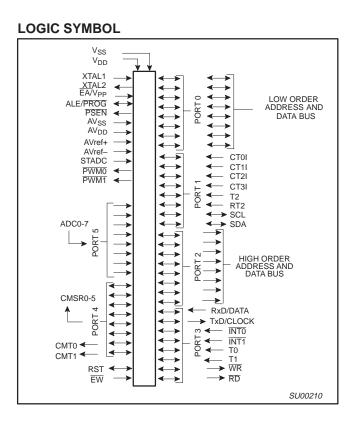

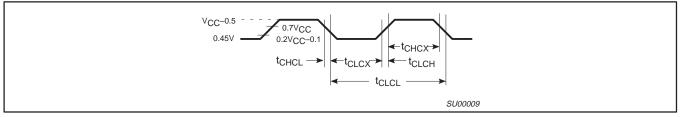

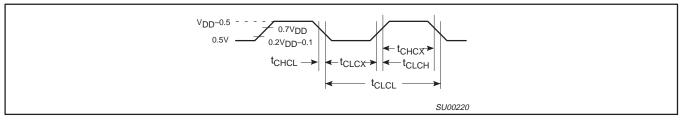

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by-two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

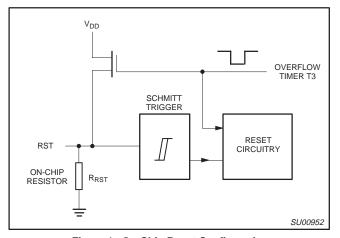

## RESET

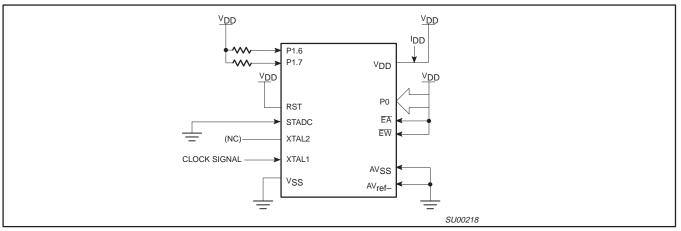

A reset is accomplished by either (1) externally holding the RST pin high for at least two machine cycles (24 oscillator periods) or (2) internally by an on-chip power-on detect (POD) circuit which detects  $V_{CC}$  ramping up from 0V.

To insure a good external power-on reset, the RST pin must be high long enough for the oscillator to start up (normally a few milliseconds) plus two machine cycles. The voltage on  $V_{DD}$  and the RST pin must come up at the same time for a proper startup.

For a successful internal power-on reset, the  $V_{CC}$  voltage must ramp up from 0V smoothly at a ramp rate greater than 5V/100 ms.

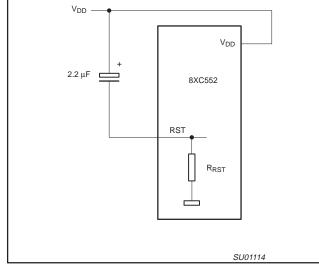

The RST line can also be pulled HIGH internally by a pull-up transistor activated by the watchdog timer T3. The length of the output pulse from T3 is 3 machine cycles. A pulse of such short duration is necessary in order to recover from a processor or system fault as fast as possible.

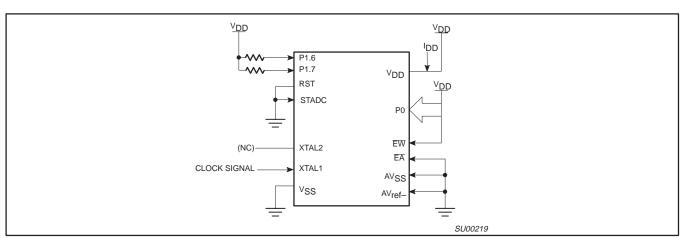

Note that the short reset pulse from Timer T3 cannot discharge the power-on reset capacitor (see Figure 2). Consequently, when the watchdog timer is also used to set external devices, this capacitor arrangement should not be connected to the RST pin, and a different circuit should be used to perform the power-on reset operation. A timer T3 overflow, if enabled, will force a reset condition to the 8XC554 by an internal connection, independent of the level of the RST pin.

A reset may be performed in software by setting the software reset bit, SRST (AUXR1.5).

Figure 1. On-Chip Reset Configuration

Figure 2. Power-On Reset

# LOW POWER MODES

## Stop Clock Mode

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and permits reduced system power consumption by lowering the clock frequency down to any value. For lowest power consumption the Power Down mode is suggested.

### **Idle Mode**

In the idle mode (see Table 2), the CPU puts itself to sleep while some of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

#### Power-Down Mode

To save even more power, a Power Down mode (see Table 2) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0V and care must be taken to return V<sub>CC</sub> to the minimum specified operating voltages before the Power Down Mode is terminated.

Either a hardware reset or external interrupt can be used to exit from Power Down. The Wake-up from Power-down bit, WUPD (AUXR1.3) must be set in order for an external interrupt to cause a wake-up from power-down. Reset redefines all the SFRs but does not change the on-chip RAM. An external interrupt allows both the SFRs and the on-chip RAM to retain their values.

To properly terminate Power Down the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10ms).

| Table 2. | Exter | nal Pin Status | During Idl | e and Pov | ver-Down | Modes | - |

|----------|-------|----------------|------------|-----------|----------|-------|---|

|          |       |                |            |           |          |       |   |

| MODE       | PROGRAM<br>MEMORY | ALE | PSEN | PORT 0 | PORT 1 | PORT 2  | PORT 3 | PORT 4 | PWM0/<br>PWM1 |

|------------|-------------------|-----|------|--------|--------|---------|--------|--------|---------------|

| Idle       | Internal          | 1   | 1    | Data   | Data   | Data    | Data   | Data   | High          |

| Idle       | External          | 1   | 1    | Float  | Data   | Address | Data   | Data   | High          |

| Power-down | Internal          | 0   | 0    | Data   | Data   | Data    | Data   | Data   | High          |

| Power-down | External          | 0   | 0    | Float  | Data   | Data    | Data   | Data   | High          |

With an external interrupt, INT0 and INT1 must be enabled and configured as level-sensitive. Holding the pin low restarts the oscillator but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put the device into Power Down.

# POWER OFF FLAG

The Power Off Flag (POF) is set by on-chip circuitry when the V<sub>CC</sub> level on the 8XC552 rises from 0 to 5V. The POF bit can be set or cleared by software allowing a user to determine if the reset is the result of a power-on or a warm start after powerdown. The V<sub>CC</sub> level must remain above 3V for the POF to remain unaffected by the V<sub>CC</sub> level.

# **Design Consideration**

When the idle mode is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write when Idle is terminated by reset,

the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

# **ONCE™** Mode

The ONCE ("On-Circuit Emulation") Mode facilitates testing and debugging of systems without the device having to be removed from the circuit. The ONCE Mode is invoked by:

- 1. Pull ALE low while the device is in reset and PSEN is high;

- 2. Hold ALE low as RST is deactivated.

While the device is in ONCE Mode, the Port 0 pins go into a float state, and the other port pins and ALE and PSEN are weakly pulled high. The oscillator circuit remains active. While the device is in this mode, an emulator or test CPU can be used to drive the circuit. Normal operation is restored when a normal reset is applied.

## **Reduced EMI Mode**

The ALE-Off bit, AO (AUXR.0) can be set to disable the ALE output. It will automatically become active when required for external memory accesses and resume to the OFF state after completing the external memory access.

| BCON           | 1                                                       | _                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                          | +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | SMOD1                                                   | SMOD0                                                                                                                                                                                             | POF                                                                                                                                                                                                                                                                                                                                                                        | WLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GF1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

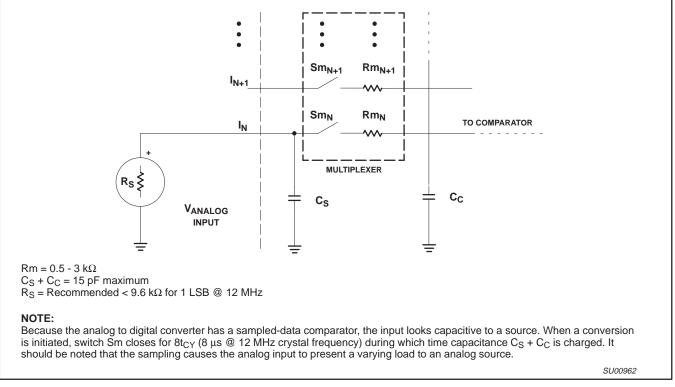

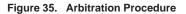

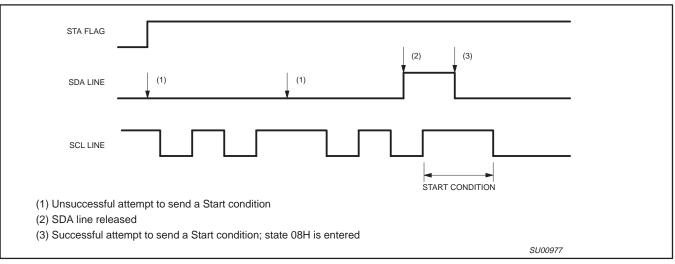

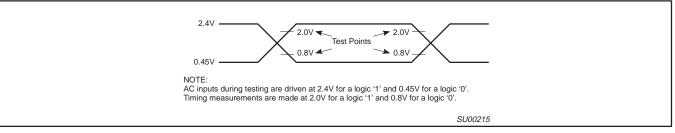

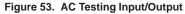

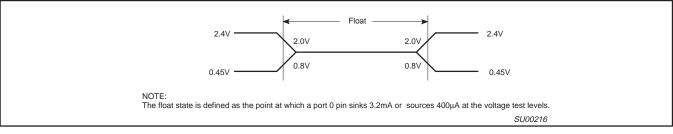

|                | (MSB)                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |