# D8748H, D8749H

# HMOS-E Single-Component 8-Bit Microcontroller

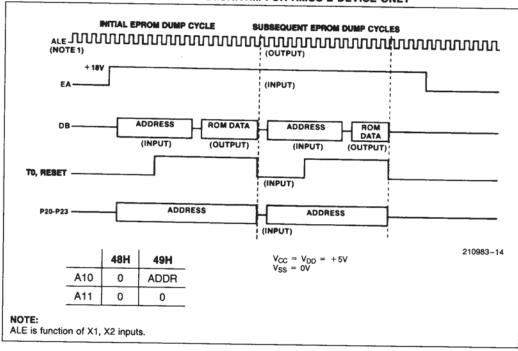

The Intel D8749H/D8748H are totally self-sufficient, 8-bit parallel computers fabricated on single silicon chips using Intel's advanced N-channel silicon gate HMOS-E process.

The family contains 27 I/O lines, an 8-bit timer/counter, on-chip RAM and on-board oscillator/clock circuits. For systems that require extra capability, the family can be expanded using MCS-80/MCS-85 peripherals.

These microcomputers are designed to be efficient as well as arithmetic processors. They have extensive bit handling capability as well as facilities for both binary and BCD arithmetic. Efficient use of program memory results from an instruction set consisting mostly of single byte instructions and no instructions over 2 bytes in length.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## D8748H/D8749H HMOS-E SINGLE-COMPONENT 8-BIT MICROCONTROLLER

- High Performance HMOS-E

- Interval Timer/Event Counter

- Two Single Level Interrupts

- Single 5-Volt Supply

- Over 96 Instructions; 90% Single Byte

- Compatible with 8080/8085 Peripherals

- Easily Expandable Memory and I/O

- Up to 1.35 µs Instruction Cycle; All Instructions 1 or 2 Cycles

The Intel D8749H/D8748H are totally self-sufficient, 8-bit parallel computers fabricated on single silicon chips using Intel's advanced N-channel silicon gate HMOS-E process.

The family contains 27 I/O lines, an 8-bit timer/counter, on-chip RAM and on-board oscillator/clock circuits. For systems that require extra capability, the family can be expanded using MCS®-80/MCS®-85 peripherals.

These microcomputers are designed to be efficient controllers as well as arithmetic processors. They have extensive bit handling capability as well as facilities for both binary and BCD arithmetic. Efficient use of program memory results from an instruction set consisting mostly of single byte instructions and no instructions over 2 bytes in length.

| Device | Internal I   | Memory      |

|--------|--------------|-------------|

| D8749H | 2K x 8 EPROM | 128 x 8 RAM |

| D8748H | 1K x 8 EPROM | 64 x 8 RAM  |

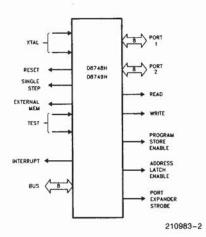

Figure 1. Block Diagram

Figure 2. Logic Symbol

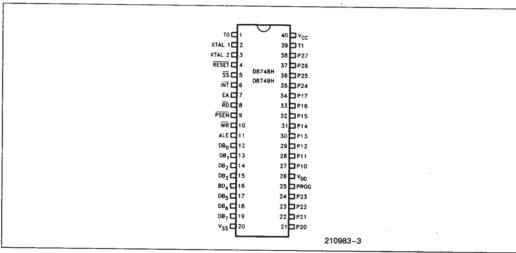

Figure 3. Pin Configuration

Table 1. Pin Description (40-Pin DIP)

| Symbol                 | Pin No.        | Function                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>        | 20             | Circuit GND potential.                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{DD}$               | 26             | +5V during normal operation.                                                                                                                                                                                                                                                                                                                                                                                       |

|                        |                | Programming power supply (+21V).                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>CC</sub>        | 40             | Main power supply; +5V during operation and programming.                                                                                                                                                                                                                                                                                                                                                           |

| PROG                   | 25             | Output strobe for 8243 I/O expander.                                                                                                                                                                                                                                                                                                                                                                               |

|                        |                | Program pulse (+ 18V) input pin during programming.                                                                                                                                                                                                                                                                                                                                                                |

| P10-P17<br>Port 1      | 27-34          | 8-bit quasi-bidirectional port.                                                                                                                                                                                                                                                                                                                                                                                    |

| P20-P23 P24-P27 Port 2 | 21-24<br>35-38 | 8-bit quasi-bidirectional port. P20-P23 contain the four high order program counter bits during an external program memory fetch and serve as a 4-bit I/O expander bus for 8243.                                                                                                                                                                                                                                   |

| DB0-DB7<br>BUS         | 12-19          | True bidirectional port which can be written or read synchronously using the RD, WR strobes. The port can also be statically latched. Contains the 8 low order program counter bits during an external program memory fetch, and receives the addressed instruction under the control of PSEN. Also contains the address and data during an external RAM data store instruction, under control of ALE, RD, and WR. |

| ТО                     | 1              | Input pin testable using the conditional transfer instructions JT0 and JNT0. T0 can be designated as a clock output using ENT0 CKL instruction.                                                                                                                                                                                                                                                                    |

|                        |                | Used during programming.                                                                                                                                                                                                                                                                                                                                                                                           |

| T1                     | 39             | Input pin testable using the JT1, and JNT1 instructions. Can be designated the timer/counter input using the STRT CNT instruction.                                                                                                                                                                                                                                                                                 |

| INT                    | 6              | Interrupt input. Initiates an interrupt if interrupt is enabled. Interrupt is disabled after a reset. Also testable with conditional jump instruction. (Active low) interrupt must remain low for at least 3 machine cycles for proper operation.                                                                                                                                                                  |

| RD                     | 8              | Output strobe activated during a BUS read. Can be used to enable data onto the bus from an external device.  Used as a read strobe to external data memory. (Active low)                                                                                                                                                                                                                                           |

Table 1. Pin Description (40-Pin DIP) (Continued)

| Symbol | Pin No. | Function                                                                                                                                                                          |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET  | 4       | Input which is used to initialize the processor. (Active low) (Non TTL VIH)                                                                                                       |

|        |         | Used during programming.                                                                                                                                                          |

| WR     | 10      | Output strobe during a bus write. (Active low) Used as write strobe to external data memory.                                                                                      |

| ALE    | 11      | Address latch enable. This signal occurs once during each cycle and is useful as a clock output.  The negative edge of ALE strobes address into external data and program memory. |

| PSEN   | 9       | Program store enable. This output occurs only during a fetch to external program memory. (Active low.)                                                                            |

| SS     | 5       | Single step input can be used in conjunction with ALE to "single step" the processor through each instruction.                                                                    |

| EA     | 7       | External access input which forces all program memory fetches to reference external memory. Useful for emulation and debug. (Active high.)                                        |

|        |         | Used during (18V) programming.                                                                                                                                                    |

| XTAL1  | 2       | One side of crystal input for internal oscillator. Also input for external source (Non TTL V <sub>IH</sub> .)                                                                     |

| XTAL2  | 3       | Other side of crystal input.                                                                                                                                                      |

### Table 2. Instruction Set

| Mnemonic<br>ACCUMULATOR | Description                      | Bytes | Cycles |

|-------------------------|----------------------------------|-------|--------|

| ADD A, R                | Add register to A                | 1     | 1      |

| ADD A,@R                | Add data<br>memory to A          | 1     | 1      |

| ADD A, #data            | Add immediate to A               | 2     | 2      |

| ADDC A, R               | Add register with carry          | 1     | 1      |

| ADDC A, @R              | Add data<br>memory with<br>carry | 1     | 1      |

| ADDC A, #data           | Add immediate with carry         | 2     | 2      |

| ANL A, R                | And register to A                | 1     | 1      |

| ANL A, @R               | And data<br>memory to A          | 1     | 1      |

| ANL A, #data            | And immediate to A               | 2     | 2      |

| ORL A, R                | Or register to A                 | 1     | 1      |

| ORL A, @R               | Or data memory to A              | 1     | 1      |

| ORL A, #data            | Or immediate to<br>A             | 2     | 2      |

| XRL A, R                | Exclusive or register to A       | 1     | 1      |

| XRL A, @R               | Exclusive or data memory to A    | 1     | 1      |

| XRL A, #data            | Exclusive or<br>immediate to A   | 2     | 2      |

| Mnemonic       | Description                    | Bytes | Cycles |

|----------------|--------------------------------|-------|--------|

| ACCUMULATOR (  | Continued)                     |       |        |

| INC A          | Increment A                    | 1     | 1      |

| DEC A          | Decrement A                    | 1     | 1      |

| CLR A          | Clear A                        | 1     | 1      |

| CPL A          | Complement A                   | 1     | 1      |

| DA A           | Decimal adjust A               | 1     | 1      |

| SWAP A         | Swap nibbles of<br>A           | 1     | 1      |

| RLA            | Rotate A left                  | 1     | 1      |

| RLC A          | Rotate A left<br>through carry | 1     | 1      |

| RR A           | Rotate A right                 | 1     | 1      |

| RRC A          | Rotate A right through carry   | 1     | 1      |

| INPUT/OUTPUT   |                                |       |        |

| IN A, P        | Input port to A                | 1     | 2      |

| OUTL P, A      | Output A to port               | - 1   | 2      |

| ANL P, #data   | And immediate to port          | 2     | 2      |

| ORL P, #data   | Or immediate to port           | 2     | 2      |

| INS A, BUS     | Input BUS to A                 | 1     | 2      |

| OUTL BUS, A    | Output A to BUS                | 1     | 2      |

| ANL BUS, #data | And immediate to BUS           | 2     | 2      |

| ORL BUS, #data | Or immediate to BUS            | 2     | 2      |

| MOVD A, P      | Input expander port to A       | 1     | 2      |

Table 2. Instruction Set (Continued)

| Mnemonic<br>INPUT/OUTPI | Description UT (Continued)        | Bytes | Cycles |

|-------------------------|-----------------------------------|-------|--------|

| MOVD P, A               | Output A to expander port         | 1     | 2      |

| ANLD P, A               | And A to expander port            | 1     | 2      |

| ORLD P, A               | Or A to expander port             | 1     | 2      |

| REGISTERS               | port                              |       |        |

| INCR                    | Increment register                | 1     |        |

| INC @R                  | Increment data                    | 1     | 1      |

|                         | memory                            | '     | '      |

| DECR                    | Decrement register                | 1     | 1      |

| BRANCH                  |                                   |       | •      |

| JMP addr                | Jump unconditional                | 2     | 2      |

| JMPP @A                 | Jump indirect                     | 1     | . 2    |

| DJNZ R, addr            | Decrement register                | 2     | 2      |

|                         | and skip                          | _     | -      |

| JC addr                 | Jump on carry = 1                 | 2     | 2      |

| JNC addr                | Jump on carry = 0                 | 2     | 2      |

| JZ addr                 | Jump on A zero                    | 2     | 2      |

| JNZ addr                | Jump on A not zero                | 2     | 2      |

| JT0 addr                | Jump on T0 = 1                    | 2     | 2      |

| JNT0 addr               | Jump on T0 = 0                    | 2     | 2      |

| JT1 addr                | Jump on $T1 = 1$                  | 2     | 2      |

| JNT1 addr               | Jump on $T1 = 0$                  | 2     | 2      |

| JF0 addr                | Jump on $F0 = 1$                  | 2     | 2      |

| JF1 addr<br>JTF addr    | Jump on F1 = 1                    | 2     | 2      |

| JNI addr                | Jump on timer flag                | 2     | 2      |

| JBb addr                | Jump on INT = 0<br>Jump on        | 2     | 2      |

| obb addi                | accumulator bit                   | 2     | 2      |

|                         | accumulator bit                   |       |        |

| SUBROUTINE              |                                   |       |        |

| CALL addr               | Jump to subroutine                | 2     | 2      |

| RET                     | Return                            | 1     | 2      |

| RETR                    | Return and restore                | 1     | 2      |

|                         | status                            |       |        |

|                         |                                   |       |        |

| FLAGS                   | 01                                |       |        |

| CLR C<br>CPL C          | Clear carry                       | 1     | 1      |

| CLR F0                  | Close floa 0                      | . 1   | 1      |

| CPL F0                  | Clear flag 0                      | 1     | 1      |

| CLR F1                  | Complement flag 0<br>Clear flag 1 | 1     | 1      |

| CPL F1                  | Complement flag 1                 | 1     | 1 1    |

| DATA MOVES              | Complement hay I                  | '     | '      |

| MOV A, R                | Move register to A                | 1     | 1      |

| MOV A, @R               | Move data memory<br>to A          | 1     | 1      |

| MOV A, #data            | Move immediate<br>to A            | 2     | 2      |

| - Cortanaca)              |                           |       |        |

|---------------------------|---------------------------|-------|--------|

| Mnemonic<br>DATA MOVES (C | Description<br>Continued) | Bytes | Cycles |

| MOV R, A                  | Move A to register        | 1     | 1      |

| MOV @R, A                 | Move A to data            | 1     | i      |

|                           | memory                    |       | ,      |

| MOV R, #data              | Move immediate to         | 2     | 2      |

|                           | register                  | -     | -      |

| MOV @R, #data             |                           | 2     | 2      |

|                           | data memory               | -     | ~      |

| MOV A, PSW                | Move PSW to A             | 1     | 1      |

| MOV PSW, A                | Move A to PSW             | 1     | 1      |

| XCH A, R                  | Exchange A and            | 1     | 1      |

| 7.5                       | register                  | ,     | '      |

| XCH A, @R                 | Exchange A and            | 1     | 1      |

| 7.4, 2                    | data memory               | '     | '      |

| XCHD A, @R                | Exchange nibble           | 1     | 1      |

| /                         | of A and register         | ,     | 1      |

| MOVX A, @R                | Move external             | 1     | 2      |

| WOTA, SI.                 | data memory to A          | '     | 2      |

| MOVX @R, A                | Move A to external        | 1     | •      |

| MOTA GILLA                |                           | 1     | 2      |

| MOVP A, @A                | data memory               | 4     | 2      |

| MOAL V' AV                | Move to A from            | 1     | 2      |

| MOVP3 A, @A               | current page              |       | 2      |

| MOVES A, SA               | Move to A from            | 1     | 2      |

|                           | page 3                    |       |        |

| TIMER/COUNTE              | R                         |       |        |

| MOV A, T                  | Read                      | 1     | 1      |

|                           | timer/counter             | •     | •      |

| MOVT, A                   | Load                      | 1     | 1      |

| ,                         | timer/counter             | •     |        |

| STRTT                     | Start timer               | 1     | 1      |

| STRT CNT                  | Start counter             | 1     | 1      |

| STOP TONT                 | Stop timer/counter        | 1     | 1      |

| EN TONTI                  | Enable timer/             | 1     | 1      |

|                           | counter interrupt         | •     | •      |

| DIS TONTI                 | Disable timer/            | 1     | 1      |

|                           | counter interrupt         | ,     | ,      |

|                           | oomor monapi              |       |        |

| CONTROL                   |                           |       |        |

| ENI                       | Enable external           | 1     | 1      |

|                           | interrupt                 |       |        |

| DISI                      | Disable external          | 1     | 1      |

|                           | interrupt                 |       |        |

| SEL RB0                   | Select register           | 1     | 1      |

|                           | bank 0                    |       |        |

| SEL RB1                   | Select register           | 1     | 1      |

|                           | bank 1                    |       |        |

| SEL MB0                   | Select memory             | 1     | 1      |

|                           | bank 0                    |       |        |

| SEL MB1                   | Select memory             | 1     | 1      |

|                           | bank 1                    | -     |        |

| ENTO CLK                  | Enable clock              | 1     | 1      |

|                           | output on T0              | -     | -      |

| NOP                       | No operation              | 1     | 1      |

|                           | F                         |       | •      |

#### D8748H/D8749H

#### **ABSOLUTE MAXIMUM RATINGS\***

Ambient Temperature Under Bias ...0°C to +70°C

Storage Temperature ....-65°C to +150°C

Voltage On Any Pin With Respect to Ground ....-0.5V to +7V

Power Dissipation ......1.0 Watt

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

DC CHARACTERISTICS  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ;  $V_{CC} = V_{DD} = 5V \pm 10\%$ ;  $V_{SS} = 0V$

|                                   | _                                                        |      | Limits | 3               |          |                                                     | Device |  |

|-----------------------------------|----------------------------------------------------------|------|--------|-----------------|----------|-----------------------------------------------------|--------|--|

| Symbol                            | Parameter                                                | Min  | Тур    | Max             | Unit     | Test Conditions                                     |        |  |

| V <sub>IL</sub>                   | Input Low Voltage (All<br>Except RESET, X1, X2)          | -0.5 |        | 0.8             | <b>V</b> |                                                     | All    |  |

| V <sub>IL1</sub>                  | Input Low Voltage<br>(RESET, X1, X2)                     | -0.5 |        | 0.6             | >        |                                                     | Ali    |  |

| V <sub>IH</sub>                   | Input High Voltage<br>(All Except XTAL1,<br>XTAL2, RESET | 2.0  |        | V <sub>CC</sub> | ٧        | ,                                                   | All    |  |

| V <sub>IH1</sub>                  | Input High Voltage<br>(X1, X2, RESET)                    | 3.8  |        | V <sub>CC</sub> | ٧        |                                                     | All    |  |

| V <sub>OL</sub>                   | Output Low Voltage (BUS)                                 |      |        | 0.45            | ٧        | $I_{OL} = 2.0 \text{ mA}$                           | All    |  |

| V <sub>OL1</sub>                  | Output Low Voltage<br>(RD, WR, PSEN, ALE)                |      |        | 0.45            | ٧        | I <sub>OL</sub> = 1.8 mA                            | All    |  |

| V <sub>OL2</sub>                  | Output Low Voltage<br>(PROG)                             |      |        | 0.45            | ٧        | I <sub>OL</sub> = 1.0 mA                            | All    |  |

| V <sub>OL3</sub>                  | Output Low Voltage<br>(All Other Outputs)                |      |        | 0.45            | V        | I <sub>OL</sub> = 1.6 mA                            | All    |  |

| V <sub>OH</sub>                   | Output High Voltage (BUS)                                | 2.4  |        |                 | ٧        | $I_{OH} = -400 \mu\text{A}$                         | All    |  |

| V <sub>OH1</sub>                  | Output High Voltage<br>(RD, WR, PSEN, ALE)               | 2.4  |        |                 | ٧        | $I_{OH} = -100 \mu\text{A}$                         | All    |  |

| V <sub>OH2</sub>                  | Output High Voltage<br>(All Other Outputs)               | 2.4  |        |                 | ٧        | $I_{OH} = -40 \mu A$                                | All    |  |

| I <sub>L1</sub>                   | Leakage Current<br>(T1, INT)                             |      |        | ±10             | μΑ       | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> | All    |  |

| I <sub>LI1</sub>                  | Input Leakage Current<br>(P10-P17, P20-P27,<br>EA, SS)   |      |        | -500            | μА       | $V_{SS} + 0.45 \le V_{IN} \le V_{CC}$               | All    |  |

| I <sub>LI2</sub>                  | Input Leakage Current<br>RESET                           | -10  |        | -300            | μΑ       | $V_{SS} \le V_{IN} \le 3.8V$                        | All    |  |

| ILO                               | Leakage Current<br>(BUS, T0) (High<br>Impedance State)   |      |        | ±10             | μΑ       | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> | All    |  |

| I <sub>DD</sub> + I <sub>CC</sub> | Total Supply Current*                                    |      | 80     | 100             | mA       |                                                     | 8748H  |  |

|                                   |                                                          |      | 95     | 110             | mA       |                                                     | 8749H  |  |

#### NOTE

<sup>\*</sup>I<sub>CC</sub> + I<sub>DD</sub> is measured with all outputs disconnected; SS, RESET, and INT equal to V<sub>CC</sub>; EA equal to V<sub>SS</sub>.

# intel.

AC CHARACTERISTICS  $T_A = 0$ °C to +70°C;  $V_{CC} = V_{DD} = 5V \pm 10$ %;  $V_{SS} = 0V$

| Symbol             | Parameter                     | f(t)        | 11   | MHz  |      | Conditions |

|--------------------|-------------------------------|-------------|------|------|------|------------|

|                    | Parameter                     | (Note 3)    | Min  | Max  | Unit | (Note 1)   |

| t                  | Clock Period                  | 1/xtal freq | 90.9 | 1000 | ns   | (Note 3)   |

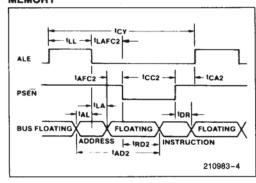

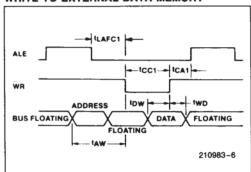

| t <sub>LL</sub>    | ALE Pulse Width               | 3.5t - 170  | 150  |      | ns   |            |

| t <sub>AL</sub>    | Addr Setup to ALE             | 2t - 110    | 70   |      | ns   | (Note 2)   |

| t <sub>LA</sub>    | Addr Hold from ALE            | t - 40      | 50   |      | ns   |            |

| t <sub>CC1</sub>   | Control Pulse Width (RD, WR)  | 7.5t - 200  | 480  |      | ns   |            |

| t <sub>CC2</sub>   | Control Pulse Width (PSEN)    | 6t - 200    | 350  |      | ns   |            |

| t <sub>DW</sub>    | Data Setup before WR          | 6.5t - 200  | 390  |      | ns   |            |

| two                | Data Hold after WR            | t - 50      | 40   |      | ns   |            |

| t <sub>DR</sub>    | Data Hold (RD, PSEN)          | 1.5t - 30   | 0    | 110  | ns   |            |

| t <sub>RD1</sub>   | RD to Data In                 | 6t - 170    |      | 375  | ns   |            |

| t <sub>RD2</sub>   | PSEN to Data In               | 4.5t - 170  |      | 240  | ns   |            |

| t <sub>AW</sub>    | Addr Setup to WR              | 5t - 150    | 300  |      | ns   |            |

| t <sub>AD1</sub>   | Addr Setup to Data (RD)       | 10.5t - 220 |      | 730  | ns   |            |

| t <sub>AD2</sub>   | Addr Setup to Data (PSEN)     | 7.5t - 200  |      | 460  | ns   |            |

| t <sub>AFC1</sub>  | Addr Float to RD, WR          | 2t - 40     | 140  |      | ns   | (Note 2)   |

| t <sub>AFC2</sub>  | Addr Float to PSEN            | 0.5t - 40   | 10   |      | ns   | (Note 2)   |

| t <sub>LAFC1</sub> | ALE to Control (RD, WR)       | 3t - 75     | 200  |      | ns   |            |

| tLAFC2             | ALE to Control (PSEN)         | 1.5t - 75   | 60   |      | ns   |            |

| t <sub>CA1</sub>   | Control to ALE (RD, WR, PROG) | t - 65      | 25   |      | ns   |            |

| t <sub>CA2</sub>   | Control to ALE (PSEN)         | 4t - 70     | 290  |      | ns   |            |

| t <sub>CP</sub>    | Port Control Setup to PROG    | 1.5t - 80   | 50   |      | ns   |            |

| t <sub>PC</sub>    | Port Control Hold to PROG     | 4t - 260    | 100  |      | ns   |            |

| t <sub>PR</sub>    | PROG to P2 Input Valid        | 8.5t - 120  |      | 650  | ns   |            |

| tpF                | Input Data Hold from PROG     | 1.5t        | 0    | 140  | ns   |            |

| t <sub>DP</sub>    | Output Data Setup             | 6t - 290    | 250  |      | ns   | -          |

| t <sub>PD</sub>    | Output Data Hold              | 1.5t - 90   | 40   |      | ns   |            |

| tpp                | PROG Pulse Width              | 10.5t - 250 | 700  |      | ns   | - /-       |

| t <sub>PL</sub>    | Port 2 I/O Setup to ALE       | 4t - 200    | 160  |      | ns   |            |

| t <sub>LP</sub>    | Port 2 I/O Hold to ALE        | 0.5t - 30   | 15   |      | ns   |            |

| t <sub>PV</sub>    | Port Output from ALE          | 4.5t + 100  |      | 510  | ns   |            |

| toper              | T0 Rep Rate                   | 3t          | 270  |      | ns   |            |

| tcy                | Cycle Time                    | 15t         | 1.36 | 15.0 | μs   |            |

<sup>1.</sup> Control outputs CL = 80 pF; BUS outputs CL = 150 pF.

2. BUS High Impedance Load 20 pF.

3. f(t) assumes 50% duty cycle on X1, X2. Max clock period is for a 1 MHz crystal input.

#### D8748H/D8749H

#### **WAVEFORMS**

#### INSTRUCTION FETCH FROM PROGRAM **MEMORY**

#### WRITE TO EXTERNAL DATA MEMORY

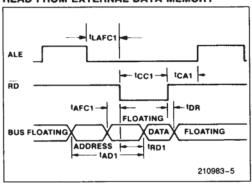

#### READ FROM EXTERNAL DATA MEMORY

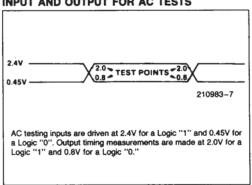

#### INPUT AND OUTPUT FOR AC TESTS

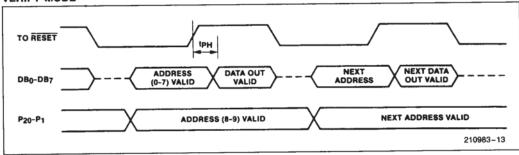

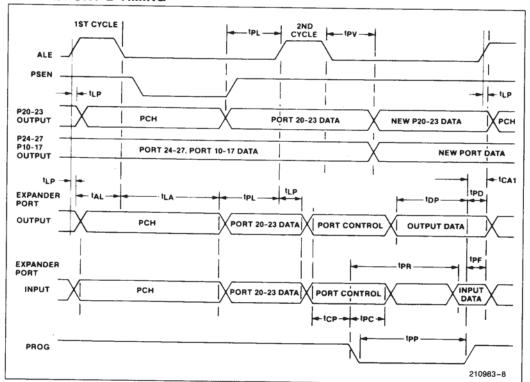

### **PORT 1/PORT 2 TIMING**

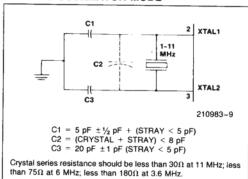

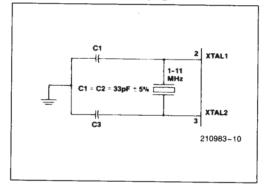

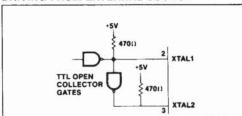

#### **CRYSTAL OSCILLATOR MODE**

### CERAMIC RESONATOR MODE

#### DRIVING FROM EXTERNAL SOURCE

210983-11

210983-11

For XTAL1 and XTAL2 define "high" as voltages above 1.6V and "low" as voltages below 1.6V. The duty cycle requirements for externally driving XTAL1 and XTAL2 using the circuit shown above are as follows: XTAL1 must be high 35-65% of the period and XTAL2 must be high 36-65% of the period. Rise and fall times must be faster than 20 ns.

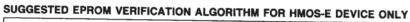

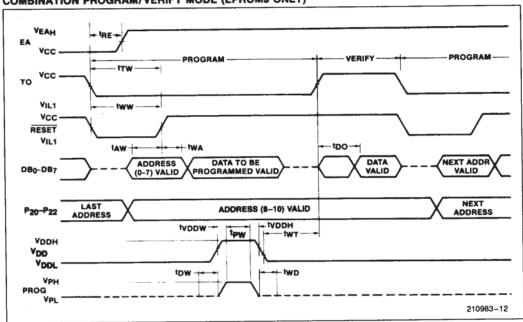

#### PROGRAMMING, VERIFYING AND ERASING THE 8749H (8748H) EPROM

#### **Programming Verification**

In brief, the programming process consists of: activating the program mode, applying an address, latching the address, applying data, and applying a programming pulse. Each word is programmed completely before moving on to the next and is followed by a verification step. The following is a list of the pins used for programming and a description of their functions:

| Pin              | Function                            |

|------------------|-------------------------------------|

| XTAL 1<br>XTAL 2 | Clock Input (3 to 4.0 MHz)          |

| RESET            | Initialization and Address Latching |

| TEST 0           | Selection of Program or Verify Mode |

| EA               | Activation of Program/Verify Modes  |

| BUS              | Address and Data Input              |

|                  | Data Output During Verify           |

| P20-P22          | Address Input                       |

| V <sub>DD</sub>  | Programming Power Supply            |

| PROG             | Program Pulse Input                 |

#### WARNING

An attempt to program a missocketed 8749H (8748H) will result in severe damage to the part. An indication of a property socketed part is the appearance of the ALE clock output. The lack of this clock may be used to disable the programmer.

The Program/Verify sequence is:

- 1) V<sub>DD</sub> = 5V, Clock applied or internal oscillator operating. RESET = 0V, TEST 0 = 5V, EA = 5V, BUS and PROG floating. P10 and P11 must be tied to ground.

- 2) Insert 8749H (8748H) in programming socket.

- 3) TEST 0 = 0V (select program mode)

- 4) EA = 18V (activate program mode)

- 5) Address applied to BUS and P20-22

- 6) RESET = 5V (latch address)

- 7) Data applied to BUS

- 8) V<sub>DD</sub> = 21V (programming power)

- 9) PROG = V<sub>CC</sub> or float followed by one 50 ms pulse to 18V

- 10)  $V_{DD} = 5V$

- 11) TEST 0 = 5V (verify mode)

- 12) Read and verify data on BUS

- 13) TEST 0 = 0V

- 14) RESET = 0V and repeat from step 5

- 15) Programmer should be at conditions of step 1 when 8749H (8748H) is removed from socket.

# AC TIMING SPECIFICATION FOR PROGRAMMING 8748H/8749H

$T_A$  = 25°C ±5°C;  $V_{CC}$  = 5V ±5%;  $V_{DD}$  = 21V ±0.5V

| Symbol                          | Parameter                                    | Min              | Max              | Unit                                    | Test Conditions |

|---------------------------------|----------------------------------------------|------------------|------------------|-----------------------------------------|-----------------|

| t <sub>AW</sub>                 | Address Setup Time to RESET↑                 | 4t <sub>CY</sub> |                  |                                         |                 |

| t <sub>WA</sub>                 | Address Hold Time after RESET ↑              | 4t <sub>CY</sub> |                  |                                         |                 |

| t <sub>DW</sub>                 | Data in Setup Time to PROG ↑                 | 4t <sub>CY</sub> |                  |                                         |                 |

| two                             | Data in Hold Time after PROG ↓               | 4t <sub>CY</sub> |                  |                                         |                 |

| t <sub>PH</sub>                 | RESET Hold Time to Verify                    | 4t <sub>CY</sub> |                  |                                         |                 |

| t <sub>VDDW</sub>               | V <sub>DD</sub> Hold Time before PROG ↑      | 0                | 1.0              | ms                                      |                 |

| t <sub>VDDH</sub>               | V <sub>DD</sub> Hold Time after PROG ↓       | 0                | 1.0              | ms                                      |                 |

| tpw                             | Program Pulse Width                          | 50               | 60               | ms                                      |                 |

| t <sub>TW</sub>                 | TEST 0 Setup Time for Program Mode           | 4t <sub>CY</sub> |                  |                                         |                 |

| twr                             | TEST 0 Hold Time after Program Mode          | 4t <sub>CY</sub> |                  |                                         |                 |

| t <sub>DO</sub>                 | TEST 0 to Data Out Delay                     |                  | 4t <sub>CY</sub> |                                         |                 |

| t <sub>WW</sub>                 | RESET Pulse Width to Latch Address           | 4t <sub>CY</sub> |                  |                                         |                 |

| t <sub>r</sub> , t <sub>f</sub> | V <sub>DD</sub> and PROG Rise and Fall Times | 0.5              | 100              | μѕ                                      |                 |

| t <sub>CY</sub>                 | CPU Operation Cycle Time                     | 3.75             | 5                | μs                                      |                 |

| t <sub>RE</sub>                 | RESET Setup Time before EA↑                  | 4t <sub>CY</sub> |                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                 |

#### NOTE

If TEST 0 is high, t<sub>DO</sub> can be triggered by RESET ↑.

# DC SPECIFICATION FOR PROGRAMMING 8748H/8749H

$T_A$  = 25°C ±5°C;  $V_{CC}$  = 5V ±5%;  $V_{DD}$  = 21V ±0.5V

| Symbol          | Parameter                                   | Min  | Max             | Unit | Test Conditions |

|-----------------|---------------------------------------------|------|-----------------|------|-----------------|

| $V_{DDH}$       | V <sub>DD</sub> Program Voltage High Level  | 20.5 | 21.5            | V    |                 |

| $V_{DDL}$       | V <sub>DD</sub> Voltage Low Level           | 4.75 | 5.25            | V    |                 |

| V <sub>PH</sub> | PROG Program Voltage High Level             | 17.5 | 18.5            | V    |                 |

| $V_{PL}$        | PROG Voltage Low Level                      | 4.0  | V <sub>CC</sub> | V    |                 |

| VEAH            | EA Program or Verify Voltage High Level     | 17.5 | 18.5            | V    |                 |

| I <sub>DD</sub> | V <sub>DD</sub> High Voltage Supply Current |      | 20.0            | mA   |                 |

| IPROG           | PROG High Voltage Supply Current            |      | 1.0             | mA   |                 |

| I <sub>EA</sub> | EA High Voltage Supply Current              |      | 1.0             | mA   |                 |

### **WAVEFORMS**

#### **VERIFY MODE**