# RENESAS

## RAA458100GNP

Wireless Charging System Transmitter IC for Low Power Applications

1. Product Outline

#### Description

RAA458100 is wireless charging system transmitter IC for low power applications. When RAA457100 is used in a receiver, a wireless charging system with bi-directional communication can be constructed.

#### Features

- Three operation modes which are available for various applications

- ATPC(AuTomatic Power Control) Mode , MCU Control Mode , Stand Alone Mode

- Gate drive output for MOSFET bridge circuit : half bridge or full bridge is selectable

- Over current protection for bridge circuit (OCP), Over temperature protection (THM), and various protection functions

- Monitoring input voltage or current of bridge circuit and thermistor voltage (Temperature) by 12bit A/D convertor

- Modulation/Demodulation function for bi-directional communication between transmitter and receiver

- RAA457100 registers can be set by bi-directional communication from RAA458100 (ATPC Mode)

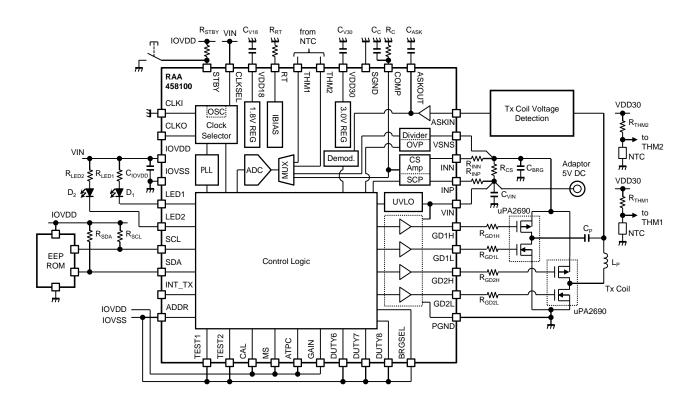

## 2. Block Diagram ( Example for Application Circuit : ATPC Mode )

Rev.1.01 Sep.03.2018

R19DS0096EJ0101

## 3. Pin Functions

| Pin<br>No. | Pin<br>Name | 1 V Flinction |     | Function                                                                                     | Remark                                                                                                                                                |  |  |

|------------|-------------|---------------|-----|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | CLKI        | D             | Ι   | Reference clock input / Connection pin to ceramic resonator                                  | Connect to IOVSS when on-chip clock is used.                                                                                                          |  |  |

| 2          | CLKO        | D             | 0   | Connection pin to ceramic resonator                                                          | This pin should be open, when ceramic resonator is not used                                                                                           |  |  |

| 3          | IOVDD       | А             | Ι   | Power supply voltage input for digital I/O                                                   | Connect CIOVDD to IOVSS.                                                                                                                              |  |  |

| 4          | IOVSS       | -             | -   | GND for digital I/O                                                                          | -                                                                                                                                                     |  |  |

| 5          | LED1        | D             | 0   | LED driver output 1                                                                          | Open drain.                                                                                                                                           |  |  |

| 6          | LED2        | D             | 0   | LED driver output 2                                                                          | Open drain.                                                                                                                                           |  |  |

| 7          | SCL         | D             | I/O | Clock input or output for 2-wire serial interface                                            | Connect R <sub>SCL</sub> to IOVDD.                                                                                                                    |  |  |

| 8          | SDA         | D             | I/O | Data input or output for 2-wire serial interface                                             | Connect R <sub>SDA</sub> to IOVDD.                                                                                                                    |  |  |

| 9          | INT_TX      | D             | 0   | Notification output at WPT communication packet reception or<br>abnormal condition detection | -                                                                                                                                                     |  |  |

| 10         | ADDR        | D             | Ι   | Slave address setting pin for 2-wire serial interface                                        | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 11         | TEST1       | -             | Ι   | Test pin 1                                                                                   | Connect to IOVSS.                                                                                                                                     |  |  |

| 12         | TEST2       | -             | Ι   | Test pin 2                                                                                   | Connect to IOVSS.                                                                                                                                     |  |  |

| 13         | CAL         | D             | Ι   | Enable pin for CS amplifier offset calibration function                                      | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 14         | MS          | D             | Ι   | Master or slave device setting pin for 2-wire serial interface                               | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 15         | ATPC        | D             | Ι   | Enable pin for automatic transmission power control function                                 | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 16         | GAIN        | D             | Ι   | Gain setting pin for automatic transmission power control                                    | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 17         | DUTY6       | D             | Ι   | Bridge driver output pulse duty setting pin 6                                                | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 18         | DUTY7       | D             | I   | Bridge driver output pulse duty setting pin 7                                                | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 19         | DUTY8       | D             | Ι   | Bridge driver output pulse duty setting pin 8                                                | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 20         | BRGSEL      | D             | Ι   | Selection pin for Half or Full bridge circuit                                                | Connect to IOVDD or IOVSS.                                                                                                                            |  |  |

| 21         | PGND        | -             | -   | GND for bridge driver                                                                        | -                                                                                                                                                     |  |  |

| 22         | GD2L        | D             | 0   | Bridge driver output 2 (Low Side)                                                            | Driving low Side Nch MOSFET.                                                                                                                          |  |  |

| 23         | GD2H        | D             | 0   | Bridge driver output 2 (High Side)                                                           | Driving high Side Pch MOSFET.                                                                                                                         |  |  |

| 24         | GD1L        | D             | 0   | Bridge driver output 1 (Low Side)                                                            | Driving low Side Nch MOSFET.                                                                                                                          |  |  |

| 25         | GD1H        | D             | 0   | Bridge driver output 1 (High Side)                                                           | Driving high Side Pch MOSFET.                                                                                                                         |  |  |

| 26         | VIN         | А             | Ι   | Power supply voltage input                                                                   | Input DC5V, connect C <sub>VIN</sub> to SGND.                                                                                                         |  |  |

| 27         | INP         | А             | Ι   | CS amplifier positive input                                                                  | Connect $R_{INP}(1k\Omega)$ to $R_{CS}$ .                                                                                                             |  |  |

| 28         | INN         | А             | Ι   | CS amplifier negative input                                                                  | Connect $R_{INN}(1k\Omega)$ to $R_{CS}$ .                                                                                                             |  |  |

| 29         | VSNS        | А             | Ι   | Voltage sense pin for bridge circuit input voltage                                           | -                                                                                                                                                     |  |  |

| 30         | ASKIN       | А             | Ι   | Amplitude modulation signal input                                                            | -                                                                                                                                                     |  |  |

| 31         | ASKOUT      | А             | 0   | Amplitude modulation signal output                                                           | Connect C <sub>ASK</sub> to SGND.                                                                                                                     |  |  |

| 32         | COMP        | А             | 0   | CS amplifier output                                                                          | Connect $R_c(10k\Omega)$ and $C_c$ to SGND.                                                                                                           |  |  |

| 33         | SGND        | -             | -   | GND for internal circuits                                                                    | -                                                                                                                                                     |  |  |

| 34         | VDD30       | А             | 0   | 3.0V regulator output                                                                        | Connect $C_{V30}$ to SGND. Bias voltage for thermistor.                                                                                               |  |  |

| 35         | THM2        | А             | Ι   | Connection pin to thermistor 2                                                               | Input divided VDD30 voltage by $R_{THM2}$ and thermistor.                                                                                             |  |  |

| 36         | THM1        | А             | Ι   | Connection pin to thermistor 1                                                               | Input divided VDD30 voltage by R <sub>THM1</sub> and thermistor.                                                                                      |  |  |

| 37         | RT          | А             | 0   | Internal circuits bias current setting pin                                                   | Connect $R_{RT}(100k\Omega)$ to SGND.                                                                                                                 |  |  |

| 38         | VDD18       | А             | 0   | 1.8V regulator output                                                                        | Connect C <sub>V18</sub> to SGND.                                                                                                                     |  |  |

| 39         | CLKSEL      | D             | Ι   | Clock selection pin (on-chip clock or external clock input)                                  | Connect to VIN or SGND.                                                                                                                               |  |  |

| 40         | STBY        | D             | I   | Standby control                                                                              | Applied to IOVDD or IOVSS voltage level.<br>IC is activated when STBY is applied to IOVDD.<br>IC is initialized(reset) when STBY is applied to IOVSS. |  |  |

\*1 A means analog signal (Including power supply voltage) and D means Digital signal.

\*2 I : Input pin, O : Output pin, I/O : Input and Output pin.

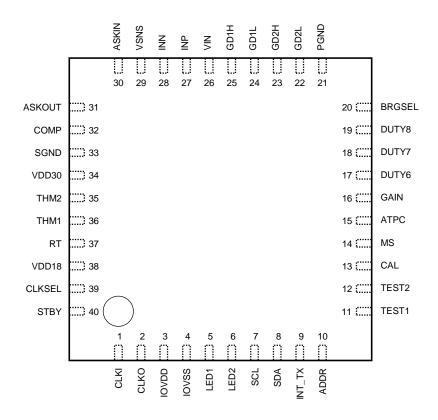

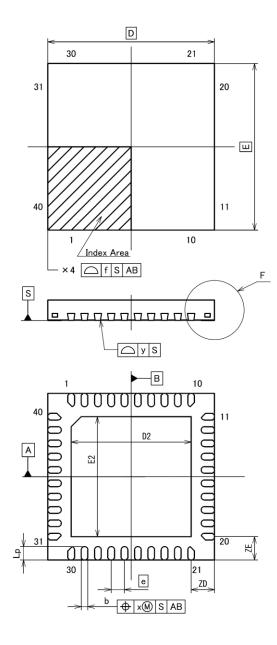

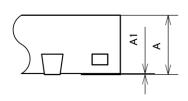

#### 4. Pin Configuration (Top View)

#### 5. Absolute Maximum Ratings (Tj=25[degC] unless otherwise noted)

| Item                  | Symbol                                                                                                      | Value             | Unit   | Remark                               |

|-----------------------|-------------------------------------------------------------------------------------------------------------|-------------------|--------|--------------------------------------|

| Pin Voltage           | VIN, IOVDD                                                                                                  | -0.3 to 5.5       | V      |                                      |

|                       | VSNS, INP, INN, CLKSEL<br>ASKIN, LED1, LED2                                                                 | -0.3 to VIN+0.3   | v      | Max. 5.5V                            |

|                       | SDA, SCL, INT_TX, MS, ATPC,<br>GAIN, ADDR, CLKI, BRGSEL,<br>STBY, DUTY6, DUTY7, DUTY8,<br>TEST1, TEST2, CAL | -0.3 to IOVDD+0.3 | v      | Max. 5.5V                            |

|                       | THM1, THM2, COMP, ASKOUT                                                                                    | VDD30             | V      |                                      |

| Pin Current           | SDA, SCL, INT_TX                                                                                            | ±1                | mA     |                                      |

|                       | RT                                                                                                          | -300              | uA     |                                      |

|                       | COMP                                                                                                        | -1                | mA     |                                      |

|                       | LED1, LED2                                                                                                  | 10                | mA     |                                      |

|                       | VDD18, VDD30                                                                                                | -100              | uA     |                                      |

| Operating temperature | Та                                                                                                          | -20 to 60         | degC   |                                      |

| Junction temperature  | Tj                                                                                                          | -20 to 80         | degC   |                                      |

| Storage temperature   | Tstg                                                                                                        | -40 to 125        | degC   |                                      |

| Thermal resistance    | θj-а                                                                                                        | 35.0              | degC/W | JEDEC 4L board<br>(76.2mm x 114.3mm) |

#### 6. Recommended Operating Conditions

| Item                  | Symbol             | Value       | Unit | Remark |

|-----------------------|--------------------|-------------|------|--------|

| VIN pin voltage       | V <sub>VIN</sub>   | 4.4 to 5.25 | V    |        |

| IOVDD pin voltage     | V <sub>IOVDD</sub> | 3 to 5.25   | V    |        |

| Input clock frequency | f <sub>clkin</sub> | 8           | MHz  |        |

Tj=25[degC] unless otherwise noted.

| Items                                      | Symbol                    | Condition                                                                | min     | typ     | max                | Unit |

|--------------------------------------------|---------------------------|--------------------------------------------------------------------------|---------|---------|--------------------|------|

| Power Supply Pin : VIN                     |                           | •                                                                        |         |         |                    |      |

| Operating voltage range                    | V <sub>OP_VIN</sub>       |                                                                          | 4.4     | 5.0     | 5.25               | V    |

| UVLO detection voltage                     | V <sub>UVLO_DET_VIN</sub> |                                                                          | 3.8     | 3.9     | 4.0                | V    |

| UVLO Hysteresis voltage                    | V <sub>UVLO_HYS_VIN</sub> |                                                                          | 0.1     | 0.2     | 0.3                | V    |

| Operating current                          | I <sub>OP_VIN</sub>       | F <sub>DRV</sub> =125kHz, C <sub>L</sub> =510pF <sup>*1</sup> , BRGSEL=L | -       | 5       | -                  | mA   |

| Standby current                            | I <sub>STBY_VIN</sub>     | STBY=L                                                                   | -       | -       | 20                 | uA   |

| PLL                                        |                           |                                                                          |         |         | I                  |      |

| PLL output frequency                       | F <sub>PLL</sub>          |                                                                          | -       | 128     | -                  | MHz  |

| Bridge Driver Pin : GD1H, GD1L, GD2H,      | GD2L                      |                                                                          |         | •       |                    |      |

| Switching frequency                        | F <sub>DRV</sub>          | Register f_drive[10:0]=1024                                              | -       | 125     | -                  | kHz  |

| High level output voltage                  | V <sub>OH_GD</sub>        | Source current=-5mA                                                      | VIN-0.2 | VIN-0.1 | -                  | V    |

| Low level output voltage                   | V <sub>OL_GD</sub>        | Sink current=5mA                                                         | -       | 0.1     | 0.2                | V    |

| 3.0V Regulator Pin : VDD30                 |                           |                                                                          |         |         | -                  | •    |

| VDD30 output voltage                       | V <sub>VDD30</sub>        |                                                                          | -       | 3.0     | -                  | V    |

| 1.8V Regulator Pin : VDD18                 |                           |                                                                          | •       |         |                    |      |

| VDD18 output voltage                       | V <sub>VDD18</sub>        |                                                                          | -       | 1.8     | -                  | V    |

| Temperature Detection Pin : THM1, THM      | Л2                        |                                                                          | •       |         |                    |      |

| Input voltage range                        | VI_THM                    |                                                                          | 0.0     | -       | V <sub>VDD30</sub> | V    |

| Bridge Circuit Current Pin : INP, INN      | •                         | •                                                                        | •       |         |                    |      |

| Short circuit protection detection voltage | V <sub>SCP_DET</sub>      | R <sub>cs</sub> voltage drop                                             | -       | 2.2     | -                  | V    |

| LED Pin : LED1, LED2                       |                           | •                                                                        |         |         |                    |      |

| Low level output voltage                   | V <sub>OL_LED</sub>       | Sink current=1mA                                                         | -       | -       | 0.1                | V    |

| Leak current                               | I <sub>I_LED</sub>        | LED1=5V, LED2=5V                                                         | -       | -       | 1                  | uA   |

| Standby Pin : STBY                         |                           | •                                                                        | •       |         |                    |      |

| High level input voltage                   | V <sub>IH_STBY</sub>      | IOVDD=5V                                                                 | 3.5     | -       | -                  | V    |

| Low level input voltage                    | V <sub>IL_STBY</sub>      | IOVDD=5V                                                                 | -       | -       | 1.5                | V    |

| Input current                              | I <sub>I_STBY</sub>       | STBY=5V                                                                  | -       | 15      | -                  | uA   |

| ASK Input Pin : ASKIN                      |                           |                                                                          |         |         |                    |      |

| ASKIN Input voltage range                  | V <sub>I_ASK</sub>        |                                                                          | 0.0     | -       | V <sub>VDD30</sub> | V    |

| ASKIN Input current                        | I <sub>I_ASK</sub>        |                                                                          | -       | 1       | -                  | uA   |

| Digital Input Pin : ADDR, MS, ATPC, GA     | IN, DUTY6, DUT            | Y7, DUTY8, BRGSEL, CLKSEL *2                                             | •       |         |                    |      |

| High level input voltage                   | VIH                       | IOVDD=5V, VIN=5V                                                         | 3.5     | -       | -                  | V    |

| Low level input voltage                    | V <sub>IL</sub>           | IOVDD=5V, VIN=5V                                                         | -       | -       | 1.5                | V    |

| Digital Output Pin : INT_TX                |                           | •                                                                        | •       |         |                    |      |

| High level output voltage                  | V <sub>OH_INT</sub>       | IOVDD=5V, Source current=-1mA                                            | 3.6     | -       | -                  | V    |

| Low level output voltage                   | V <sub>OL_INT</sub>       | IOVDD=5V, Sink current=1mA                                               | -       | -       | 1.4                | V    |

| Digital Input/Output Pin : SDA, SCL        |                           |                                                                          |         |         |                    |      |

| High level input voltage                   | V <sub>IH_I2C</sub>       | IOVDD=5V                                                                 | 3.5     | -       | -                  | V    |

| Low level input voltage                    | V <sub>IL_I2C</sub>       | IOVDD=5V                                                                 | -       | -       | 1.5                | V    |

| Low level output voltage                   | V <sub>OL_I2C</sub>       | IOVDD=5V, Sink current=1mA                                               | -       | -       | 0.2                | V    |

|                                            |                           |                                                                          |         |         | -                  |      |

\*1  $C_L$  shows the load capacitance to the bridge drivers (GD1H, GD1L, GD2H, GD2L).

\*2 High level reference voltage of CLKSEL is VIN. High level reference voltage of other digital input pins is IOVDD.

#### 8. Functions Description (The values described in this chapter are reference values, not guaranteed values.)

#### 8.1 Operation Mode and Start Up Flow

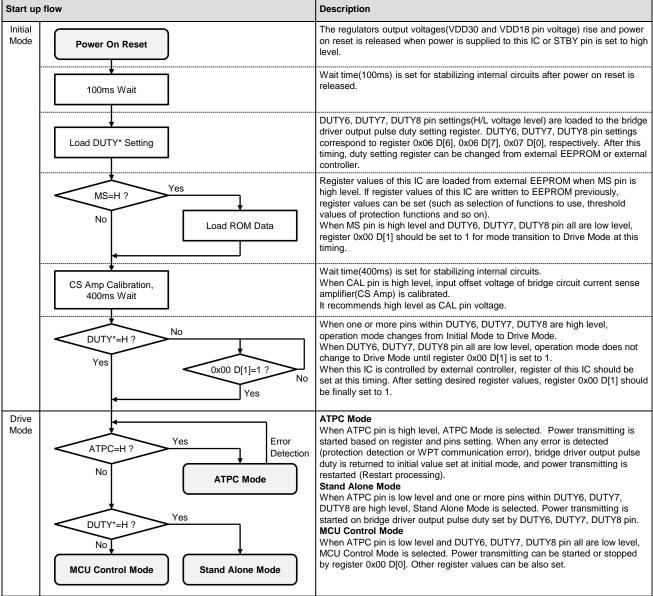

This IC has two operation modes of Initial Mode and Drive Mode. Initial Mode is an operation mode to perform initial setting such as this IC's register setting before changing to Drive Mode. Drive Mode is an operation mode to drive a bridge circuit and transmit power to receiver. Drive Mode includes the three operation modes of ATPC Mode, MCU Control Mode and Stand Alone Mode which can be selected by some pins setting(MS, ATPC, DUTY6, DUTY7, DUTY8). Table 8.1.1 shows operation mode overview. Figure 8.1.1 shows start up flow from Initial Mode(power on reset is released) to Drive Mode(power transmitting is started).

#### Table 8.1.1 Operation mode overview

| Omenetien meede                     |    | I    | Pin setting                           | 9 |       | Description                                                                                                                                                    |  |

|-------------------------------------|----|------|---------------------------------------|---|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operation mode                      | MS | ATPC | DUTY6 DUTY7 DUTY8                     |   | DUTY8 | Description                                                                                                                                                    |  |

| Initial Mode                        | x  | х    | х                                     | х | х     | Initial setting such as register setting is performed based on pins setting.                                                                                   |  |

| Drive Mode                          |    |      |                                       |   |       |                                                                                                                                                                |  |

| Stand Alone Mode<br>(w/o ROM , MCU) | L  | L    | Set one or more pins<br>to high level |   |       | This IC operates independently. Power is transmitted on a fixed bridge frequency and duty.                                                                     |  |

| ATPC Mode<br>(w/ ROM)               | н  | н    | L                                     | L | L     | Transmission power is controlled on receiver power information which is included in WPT communication packet. Register of this IC can be set from              |  |

| ATPC Mode<br>(w/ MCU)               | L  | н    | L                                     | L | L     | external EEPROM or external controller(MCU) by 2-wire serial communication.<br>MS pin should be high level when external EEPROM is used.                       |  |

| MCU Control Mode<br>(w/ MCU)        | L  | L    | L                                     | L | L     | This IC is controlled by external controller. Register setting and start / stop control of power transmitting can be performed by 2-wire serial communication. |  |

| Start up flow                       |    |      |                                       |   |       | Description                                                                                                                                                    |  |

Figure 8.1.1 Start up flow from Initial Mode(power on reset is released) to Drive Mode(power transmitting is started)

#### 8.2 Reference Clock

The reference clock frequency should be 8[MHz]. The reference clock source can be selected within external clock, ceramic resonator, and on chip oscillator by setting of CLKSEL, CLKI, and CLKO pin. Table 8.2.1 shows the selection of reference clock.

#### Table 8.2.1 Selection of reference clock

| Reference clock    |        | Pin setting    |           | Remark                                               |  |

|--------------------|--------|----------------|-----------|------------------------------------------------------|--|

| 8[MHz]             | CLKSEL | CLKI           | CLKO      | Remark                                               |  |

| External clock     | L      | External clock |           | CLKSEL H / L voltage level H : VIN / L : SGND        |  |

| Ceramic resonator  | L      | Ceramic        | resonator | CLKI, CLKO H / L voltage level H : IOVDD / L : IOVSS |  |

| On chip oscillator | Н      | L              | Open      |                                                      |  |

#### 8.3 Bridge Driver (GD1H, GD1L, GD2H, GD2L pin)

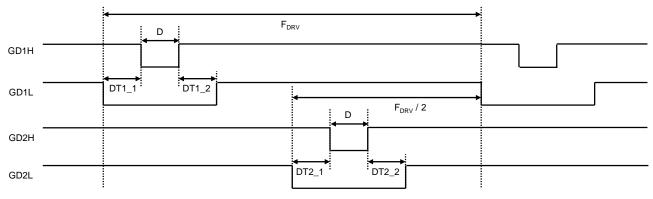

Bridge driver drives full or half bridge circuit composed of external MOSFET (high side switch : Pch MOSFET, low side switch : Nch MOSFET). Figure 8.3.1 shows bridge driver output waveform for driving full bridge circuit. When half bridge circuit is selected, bridge driver outputs driving pulse from GD1H, GD1L and stops to output driving pulse from GD2H, GD2L (GD2H=H, GD2L=L). Table 8.3.1 shows parameters setting for bridge driver. Soft start function as changing duty slowly is implemented for start up and changing bridge driver output pulse duty.

Figure 8.3.1 Bridge driver output waveform for driving MOSFET gate of full bridge circuit

| Table 8.3.1  | Parameters  | setting | for | bridge d  | Iriver |

|--------------|-------------|---------|-----|-----------|--------|

| 1 able 0.5.1 | i arameters | setting |     | billuge u | an ver |

| Item                             | Symbol           | Setting                                               | Calculation formula, Remark                                                                                                                                                                                 |  |  |

|----------------------------------|------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Full or half bridge selection    | -                | BRGSEL pin                                            | BRGSEL=L : Driver output for full bridge circuit<br>BRGSEL=H : Driver output for half bridge circuit                                                                                                        |  |  |

| Output pulse F <sub>DRV</sub>    |                  | Register f_drive[10:0]<br>(0x05 D[2:0] , 0x04 D[7:0]) | $\label{eq:F_DRV} \begin{array}{l} F_{DRV} = 1000 \; x \; ( \; 128 \; / \; ( \; f\_drive[10:0] \; ) \; ) \; \; [kHz] \\ The \; condition \; F_{DRV} \; \leq \; 125 [kHz] \; is \; recommended. \end{array}$ |  |  |

| Output pulse D                   |                  | Register duty[9:0]<br>(0x07 D[1:0] , 0x06 D[7:0])     | D = 100 x ( duty[9:0] / f_drive[10:0] ) [%]<br>The condition D $\leq$ 50[%] is needed.                                                                                                                      |  |  |

| Output pulse<br>dead time        | DT1_1            | Register dt_gd1_1[4:0]<br>(0x09 D[4:0])               | DT1_1 = 100 x ( dt_gd1_1[4:0] / f_drive[10:0] ) [%]                                                                                                                                                         |  |  |

|                                  | DT1_2            | Register dt_gd1_2[4:0]<br>(0x0A D[4:0])               | DT1_2 = 100 x ( dt_gd1_2[4:0] / f_drive[10:0] ) [%]                                                                                                                                                         |  |  |

|                                  | DT2_1            | Register dt_gd2_1[4:0]<br>(0x0B D[4:0])               | DT2_1 = 100 x ( dt_gd2_1[4:0] / f_drive[10:0] ) [%]                                                                                                                                                         |  |  |

|                                  | DT2_2            | Register dt_gd2_2[4:0]<br>(0x0C D[4:0])               | DT2_2 = 100 x ( dt_gd2_2[4:0] / f_drive[10:0] ) [%]                                                                                                                                                         |  |  |

| Output pulse duty for modulation |                  | Register modulation_duty[6:0]<br>(0x0D D[6:0])        | $\Delta D_{MOD}$ = 100 x ( modulation_duty[6:0] / f_drive[10:0] ) [%]<br>(For transmitting of WPT communication packet)                                                                                     |  |  |

| Output pulse D <sub>M</sub>      |                  | Register duty_max[9:0]<br>(0x14 D[1:0] , 0x13 D[7:0]) | $\begin{array}{l} D_{MAX} = 100 \; x \; ( \; duty\_max[9:0] \; / \; f\_drive[10:0] \; ) \; \; [\%] \\ The \; condition \; D_{MAX} \leq 50[\%] \; is \; needed. \end{array}$                                 |  |  |

| Output pulse setting con         | straints         |                                                       |                                                                                                                                                                                                             |  |  |

| Only condition (1) should b      | be satisfied for | r BRGSEL=H. Both of condition (1) a                   | nd (2) should be satisfied for BRGSEL=L.                                                                                                                                                                    |  |  |

Only condition (1) should be satisfied for BRGSEL=H. Both of condition (1) and (2) should be satisfied for BRGSEL=L.

- (1) (0.5 x f\_drive[10:0] > duty[9:0] + dt\_gd1\_1[4:0] + dt\_gd1\_2[4:0] + modulation\_duty[6:0])

- And  $(duty_max[9:0] > duty[9:0] + dt_gd1_1[4:0] + dt_gd1_2[4:0] + modulation_duty[6:0])$

- (2) (0.5 x f\_drive[10:0] > duty[9:0] + dt\_gd2\_1[4:0] + dt\_gd2\_2[4:0] + modulation\_duty[6:0] ) And (duty\_max[9:0] > duty[9:0] + dt\_gd2\_1[4:0] + dt\_gd2\_2[4:0] + modulation\_duty[6:0] )

#### 8.4 A/D Converter

Some pin voltages are converted to digital code by 12bit A/D converter. Table 8.4.1 shows the monitored items by A/D converter. These items are monitored in 4[ms] period. Some protection functions are detected by using A/D converted data. The storage registers of A/D converted data can be read by 2-wire serial communication. The storage registers aren't updated automatically. When register 0x20 D[0] is set to 1, the storage registers are updated.

| Item                                                                 | Monitored pin                         | Output code *1                                                                                                                                                       | Input voltage range *2 | Register                   |

|----------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|

| Input voltage<br>of bridge circuit                                   | VSNS pin voltage<br>V <sub>SNS</sub>  | ( 4096 / 3 ) x V <sub>SNS</sub> / 2.16                                                                                                                               | 0 to 5.5 V             | 0x21 D[7:4]<br>0x22 D[7:0] |

| Average input current<br>of bridge circuit<br>(I <sub>BRIDGE</sub> ) | COMP pin voltage<br>V <sub>COMP</sub> | $ \begin{array}{l} (4096/3)xV_{COMP} \\ V_{COMP} = CS\_AMP\_GAINxV_{RCS} = 10xV_{RCS} \\ (CS\_AMP\_GAIN=R_C/R_{INP}=10) \\ I_{BRIDGE} = V_{RCS}/R_{CS} \end{array} $ | 0 to 3.0 V             | 0x23 D[7:4]<br>0x24 D[7:0] |

| Thermistor temperature (THM1)                                        | THM1 pin voltage<br>V <sub>THM1</sub> | ( 4096 / 3 ) x V <sub>THM1</sub>                                                                                                                                     | 0 to 3.0 V             | 0x25 D[7:4]<br>0x26 D[7:0] |

| Thermistor temperature (THM2)                                        | THM2 pin voltage<br>V <sub>THM2</sub> | ( 4096 / 3 ) x V <sub>THM2</sub>                                                                                                                                     | 0 to 3.0 V             | 0x27 D[7:4]<br>0x28 D[7:0] |

#### Table 8.4.1 Monitored items by A/D converter

\*1 Output code range is from 0 to 4095.

\*2 Pin voltage should be within input voltage range to prevent error conversion.

#### 8.5 LED Flashing Pattern

LED1 and LED2 pin are LED driver for displaying operation state. Flashing patterns on each operation state are implemented. External controller (MCU) can select any flashing pattern in MCU Control Mode. Table 8.5.1 shows operation mode, operation state, setting register, and LED flashing pattern.

| Table 8.5.1 Operation mode, Operation state, Setting register, and LED flashing pattern |

|-----------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------|

| Mode           | Operation state                    | Setting register 1                  | Setting register 2          |       | LED1               | LED2               |

|----------------|------------------------------------|-------------------------------------|-----------------------------|-------|--------------------|--------------------|

| mouo           |                                    |                                     |                             | Value |                    |                    |

| Initial        | During start up                    | -                                   | -                           | -     | Off                | Off                |

|                |                                    |                                     |                             | 0     | Flashing (0.25sec) | Off                |

|                | Under<br>WPT communication         |                                     | 0x12 D[1:0]                 | 1     | Off                | Flashing (0.25sec) |

|                | (Battery charging is<br>available) |                                     | led_trans_sel               | 2     | On                 | Off                |

|                | availabio                          |                                     |                             | 3     | Off                | On                 |

|                |                                    |                                     | 0x12 D[2]                   | 0     | On                 | Off                |

| ATPC           | Under battery charging             |                                     | led_charge_sel              | 1     | Off                | On                 |

| AIPC           |                                    |                                     | 0x12 D[4]                   | 0     | Off                | Off                |

|                | Battery charge complete            | 0x10 D[3]=0<br>led_force_mode<br>*3 | led_end_sel                 | 1     | Off                | On                 |

|                | Restart                            |                                     | 0x12 D[6]<br>led_err_sel    | 0     | Flashing (1sec)    | Off                |

|                | *1                                 |                                     |                             | 1     | Off                | Off                |

|                | Transmitting power                 |                                     | 0x12 D[7]<br>led_errend_sel | 0     | Flashing (1sec)    | Off                |

|                | stopped<br>*2                      |                                     |                             | 1     | Off                | Off                |

|                | Transmitting power                 |                                     | -                           | -     | On                 | Off                |

| Stand<br>Alone | Transmitter timer timeout          |                                     | -                           | -     | Off                | Off                |

| ,              | Protection detected                |                                     | -                           | -     | Flashing (1sec)    | Off                |

|                |                                    |                                     |                             | 0     | Off                | -                  |

|                |                                    |                                     | 0x10 D[1:0]                 | 1     | Flashing (1sec)    | -                  |

|                |                                    |                                     | led1_force_sel              | 2     | Flashing (0.25sec) | -                  |

| MCU            | Selection by                       | 0x10 D[3]=1                         |                             | 3     | On                 | -                  |

| Control        | external controller(MCU)           | led_force_mode<br>*4                |                             | 0     | -                  | Off                |

|                |                                    |                                     | 0x10 D[5:4]                 | 1     | -                  | Flashing (1sec)    |

|                |                                    |                                     | led2_force_sel              | 2     | -                  | Flashing (0.25sec) |

|                |                                    |                                     |                             | 3     | -                  | On                 |

\*1 Restart is processing when protection is detected or WPT communication error is occurred.

\*2 Transmitting power is completely stopped when the count of protection detection or WPT communication error becomes specified number.

\*3 Register setting of 0x10 D[3] should be 0 in ATPC Mode and Stand Alone Mode.

\*4 Register setting of 0x10 D[3] should be 1 in MCU Control Mode. LED is off regardless of setting in 0x10 D[1:0] and 0x10 D[5:4] when 0x10 D[3] is 0.

#### 8.6 Protection Functions

The protection functions for power supply voltage, bridge circuit and temperature are implemented. Table 8.6.1 shows protection functions. Transmitter timer is also implemented. Transmitter timer starts at the timing of mode transition to Drive Mode, power transmitting is stopped when Drive Mode continues for a fixed period. Table 8.6.2 shows the registers related to transmitter timer. Reset of this IC by power on again or STBY pin is needed to return from stopping power transmitting caused by transmitter timer.

| Item<br>(Detecting target)                                                                                                       | Detection<br>timing | Threshold<br>(Release)                                      | Detection delay time     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Under voltage lock out<br>(VIN pin voltage)                                                                                      | At any time         | 3.9V<br>( 4.1V )                                            | -                        | This IC becomes power on reset(POR) condition when under voltage lock out is detected. (This IC becomes POR condition regardless of VIN pin voltage when STBY pin is low.)                                                                                                                                                                                                                                                                                    |

| Short circuit protection<br>for bridge circuit<br>(R <sub>CS</sub> voltage drop)                                                 | Drive<br>Mode       | 2.2V                                                        | 1us                      | Bridge driver is stopped (latch stop) when short circuit or over current<br>for bridge circuit is detected at Drive Mode. The reset of this IC by<br>power on again or STBY pin is needed to return from this protection.                                                                                                                                                                                                                                     |

| Over current protection<br>for bridge circuit<br>(COMP pin voltage)                                                              | Drive<br>Mode       | 0x16 D[3:0]<br>0x15 D[7:0]                                  | 16ms<br>x<br>0x36 D[3:0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Over voltage protection<br>for bridge circuit <sup>*2</sup><br>(VSNS pin voltage) After<br>16ms passed<br>after releasing<br>POR |                     | 5.7V<br>(5.5V)                                              | 1ms x 4                  | Bridge driver is stopped when over voltage for bridge circuit is<br>detected at Drive Mode. Operation mode does not change to Drive<br>Mode when over voltage is detected at Initial Mode.<br>In ATPC Mode, bridge driver output pulse duty is returned to initial<br>value set at Initial Mode, then bridge driver restarts.<br>In Stand Alone Mode and MCU Control Mode, bridge driver restarts<br>when the voltage decreases to release threshold voltage. |

| Temperature protection 1<br>(THM1 pin voltage)                                                                                   | Drive<br>Mode       | 0x18 D[3:0]<br>0x17 D[7:0]<br>( 0x29 D[7:0] <sup>*1</sup> ) | 16ms                     | Over temperature of a target is detected by NTC thermistor <sup>*3</sup> . Detection threshold and hysteresis can be adjusted by setting the registers. If register value can not be changed, a threshold can be changed by adjusting a value of pull up resistor connected to the thermistor. Bridge driver is stopped when temperature protection is                                                                                                        |

| Temperature protection 2<br>(THM2 pin voltage)                                                                                   | Drive<br>Mode       | 0x1A D[3:0]<br>0x19 D[7:0]<br>( 0x2A D[7:0] <sup>*1</sup> ) | x<br>0x36 D[7:4]         | detected.<br>In ATPC Mode, bridge driver output pulse duty is returned to initial<br>value set at Initial Mode, then bridge driver restarts.<br>In Stand Alone Mode and MCU Control Mode, bridge driver restarts<br>when temperature decreases to release threshold.                                                                                                                                                                                          |

| Maximum output pulse<br>duty of bridge driver                                                                                    | Drive<br>Mode       | 0x14 D[1:0]<br>0x13 D[7:0]                                  | 1us                      | Bridge driver is stopped when bridge driver output pulse duty exceeds<br>maximum output pulse duty.<br>In ATPC Mode, bridge driver output pulse duty is returned to initial<br>value set at Initial Mode, then bridge driver restarts.<br>In MCU Control Mode, bridge driver restarts when pulse duty is set<br>under maximum output pulse duty.                                                                                                              |

\*1 Hysteresis setting register.

\*2 Detection voltage of over voltage protection is higher than absolute maximum rating.

The system design that this protection doesn't work is needed substantially to avoid device destruction or deterioration. \*3 NCP03WF104F05RL, NCP15WF104F03RC(Murata) or an equivalent device is recommended.

| Item                                     | Register    | Description                                                                                                           |

|------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| Transmitter timer enable                 | 0x11 D[5]   | Enable or disable selection of transmitter timer.<br>0 : Enable 1 : Disable(Bridge driver pulse output is continued.) |

| Transmitter timer timeout period setting | 0x11 D[7:6] | Timeout period setting<br>0 : 198[min] 1 : 264[min] 2 : 330[min] 3 : 396[min]                                         |

| Transmitter timer timeout notification   | 0x12 D[5]   | Timeout notification<br>0 : Timeout is not detected 1 : Timeout is detected                                           |

#### 8.7 Interruption Signal Output Function (INT\_TX pin)

Interruption signal (event detection signal) is outputted from INT\_TX pin when WPT communication packet is received or protection is operated (refer to Table 8.6.1). Table 8.7.1 shows the events that interruption signal is outputted. Events to output the signal can be selected by setting enable registers. When enable register value is "1", low level is outputted from INT\_TX pin when applicable event is occurred. Reset register should be set to "1" in order to return to high level at INT\_TX pin. If an event occurs continuously, low level is outputted again from INT\_TX pin even though reset register is set to "1". When enable register value is "0" (disable), low level is not outputted from INT\_TX pin but applicable notification register is set to "1".

| Event                                          | Notification register                        | Enable<br>register     | Reset<br>register | Condition to notify (Notification register is asserted.)                                                                                                                                                                                                                                                                      |  |  |  |  |

|------------------------------------------------|----------------------------------------------|------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| WPT communication<br>packet is received        | 0x1B D[1]                                    | 0x1B D[7]              | 0x1B D[0]         | Notification register is set to "1" when WPT communication packet is received in MCU Control Mode.                                                                                                                                                                                                                            |  |  |  |  |

| WPT communication<br>write completion          | 0x1B D[2]                                    | 0x1B D[7]              | 0x1B D[0]         | These events occur in ATPC Mode.<br>RAA458100 can write or read register of receiver device (RAA457100) by WPT<br>communication. When register write / read operation is normally performed in<br>receiver device, command completion information is sent from receiver device.                                               |  |  |  |  |

| WPT communication read completion              | 0x1B D[3]                                    | 0x1B D[3]              |                   | When this IC receives the information, notification register of write completion o<br>read completion is set to "1" and interruption signal is outputted.<br>When register write / read operation is not performed in receiver device, this IC<br>recognizes as WPT communication error and then the bridge driver is stopped |  |  |  |  |

| Restart operation                              | 0x1B D[4]                                    |                        |                   | and restarted(restart operation). Register 0x1B D[4] is set to "1" when restart is performed.                                                                                                                                                                                                                                 |  |  |  |  |

| Temperature protection 1                       | 0x1D D[0]                                    | 0x1F D[0]<br>0x1C D[1] | 0x1C D[0]         | Notification register is set to "1" and interruption signal is outputted when protection showed in Table 8.6.1 is detected except for under voltage lock out detection. Enable registers(0x1F D[5:0]) for interruption signal output are assigned for each event. If interruption signal output is not needed, register 0x1C  |  |  |  |  |

| Temperature protection 2                       | rotection 2 0x1D D[1] 0x1F D[1]<br>0x1C D[1] |                        |                   | D[1] should be set to "0".<br>When temperature protection 1, temperature protection 2, over voltage protection<br>for bridge circuit, or maximum output pulse duty of bridge driver is detected in<br>ATPC Mode, the bridge driver is stopped and restarted(restart operation).                                               |  |  |  |  |

| Over voltage protection<br>for bridge circuit  | 0x1D D[2]                                    | 0x1F D[2]<br>0x1C D[1] |                   | Register 0x1B D[4] is set to "1" when restart is performed.                                                                                                                                                                                                                                                                   |  |  |  |  |

| Short circuit protection<br>for bridge circuit | 0x1D D[3]                                    | 0x1F D[3]<br>0x1C D[1] |                   |                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Maximum output pulse duty of bridge driver     | 0x1D D[4]                                    | 0x1F D[4]<br>0x1C D[1] |                   |                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Over current protection<br>for bridge circuit  | 0x1D D[5]                                    | 0x1F D[5]<br>0x1C D[1] |                   |                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

#### Table 8.7.1 Event to interruption signal output

#### 8.8 2-wire Serial Communication Interface

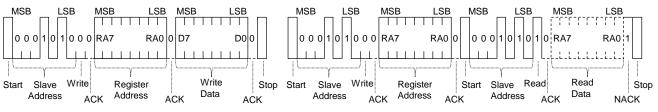

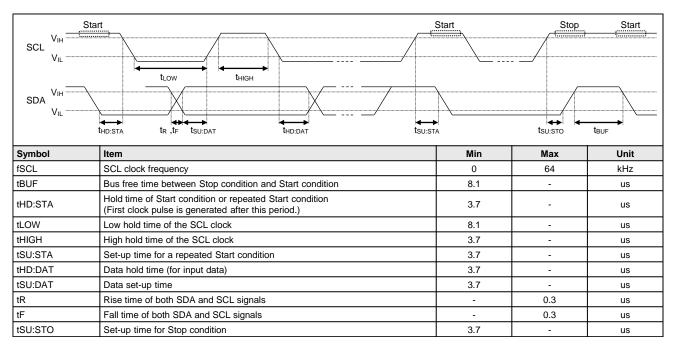

RAA458100 can communicate to external ROM(EEPROM) or external controller(MCU) by 2-wire serial communication. Master device setting is needed when external ROM is used, slave device setting is needed when external controller is used. Master device or slave device can be selected by MS pin setting. Figure 8.8.1(a), (b) shows SDA data format in slave device. Figure 8.8.2 shows timing specification.

| MS pin       | SCL<br>Frequency | Description                                                                                                                                                                                                                                                                                                               |

|--------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L<br>(IOVSS) | 64<br>[kHz]      | RAA458100 is slave device for 2-wire serial communication. External controller can write / read the register of RAA458100. The slave address can be changed by ADDR pin. ADDR pin =L : 0001010, ADDR pin =H : 1101010                                                                                                     |

| H<br>(IOVDD) | 64<br>[kHz]      | RAA458100 is master device for 2-wire serial communication. RAA458100 can read register setting values from EEPROM in<br>Initial Mode. The communication between RAA458100 and EEPROM is read operation only.<br>The slave address of EEPROM can be selected by ADDR pin.<br>ADDR pin =L : 1010000, ADDR pin =H : 1010001 |

Figure 8.8.1(a) SDA data format (Slave, Write)

Figure 8.8.1(b) SDA data format (Slave, Read)

Figure 8.8.2 SCL and SDA timing specification of 2-wire serial communication (for reference)

#### 8.9 WPT Communication

#### 8.9.1 Outline

RAA458100 and RAA457100(Receiver IC) support a bidirectional communication by amplitude modulation on wireless power transmission carrier signal. In receiver to transmitter communication, RAA457100 changes transmitting antenna voltage by load modulation and then RAA458100 detects the voltage variation and demodulates data. In transmitter to receiver communication, RAA458100 changes rectified voltage of RAA457100 by changing transmission power and then RAA457100 detects the voltage variation and demodulates data.

#### 8.9.2 Packet Format in WPT Communication

The packet of WPT communication is consisted of fixed data length packet including Preamble, Header, Message1, Message2, Checksum showed in Figure 8.9.2. The Header, Message1, Message2 have 1 bit of odd parity bit respectively, and the check sum generated by exclusive OR is added to the last of the packet. When ATPC pin level of RAA458100 and RAA457100 is high, automatic transmission power control function is available (ATPC Mode). In ATPC Mode, the packet which includes a special header code (0x00 to 0x0F) is sent from RAA457100 to RAA458100 periodically, and RAA458100 adjusts transmission power based on the data included in packet.

| Preamble<br>(11bit) St Header<br>(8bit) | r Sp St | Message1<br>(8bit) Pr | Sp St | Message2<br>(8bit) | Pr | Sp | St Checksum<br>(8bit) | Pr | Sp |

|-----------------------------------------|---------|-----------------------|-------|--------------------|----|----|-----------------------|----|----|

|-----------------------------------------|---------|-----------------------|-------|--------------------|----|----|-----------------------|----|----|

St : Start bit(1bit), Pr : Parity bit(1bit), Sp : Stop bit(1bit)

#### Figure 8.9.2 Data packet format

#### Table 8.9.2 Header code

| Header code  | Explanation                                                      |

|--------------|------------------------------------------------------------------|

| 0x00 to 0x0F | Header code for automatic transmission power control (ATPC Mode) |

| 0x10 to 0xFF | Header code for any user purpose                                 |

#### 8.9.3 Data Transfer Function

The transmission power is modulated by changing bridge driver output pulse duty depending on packet data.

#### 8.9.4 Data Receive Function

A data packet described in Figure 8.9.2 sent from receiver is demodulated.

The voltage variation on transmitting antenna is detected and demodulated by a buffer amplifier (input : ASKIN pin, output : ASKOUT pin) and demodulation circuits.

#### 8.9.5 Communication Bit Rate

Table 8.9.5 shows communication bit rate. The transmission data rate is 125[bps], the reception data rate is 250[bps].

#### Table 8.9.5 Setting for communication rate

| Communication direction                     | Bit rate | Remark |  |  |

|---------------------------------------------|----------|--------|--|--|

| Data transmission (Transmitter to receiver) | 125bps   |        |  |  |

| Data reception (Receiver to transmitter)    | 250bps   |        |  |  |

9. Register Map (The values described in this chapter are reference values, not guaranteed values.)

9.1 Address 0x00 to 0x07 (\*1 Test Register : The same value as initial value (init) should be written here at write access to this address.)

|         |          | Register Name        | - |       | Description                                                                                                                               |

|---------|----------|----------------------|---|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| luurooo |          | drive_on             | 0 |       | Bridge driver ON/OFF control in MCU Control Mode. 0 : OFF 1 : ON                                                                          |

|         | D1       | drive_mode_on        | 0 | -     | The register to change operation mode when DUTY6,7,8 pin all are low level. 0 : Initial Mode 1 : Change to Drive Mode                     |

|         | D2       |                      | 0 | R/W   | *1                                                                                                                                        |

|         | D3       |                      | 0 | R/W   | *1                                                                                                                                        |

| 0x00    | D4       |                      | 0 | R/W   | *1                                                                                                                                        |

|         | D5       |                      | 0 | R/W   | *1                                                                                                                                        |

|         | D6       | auto_drive_on        | 0 | R     | Bridge driver ON/OFF notification in ATPC Mode and Stand Alone Mode. 0 : OFF 1 : ON                                                       |

|         | D7       | atpc_eep_end_mode    | 0 | R     | Data loading from ROM(EEPROM) completion notification in ATPC Mode. 0 : Not complete 1 : Completed                                        |

|         | D0       | alpc_eep_end_mode    | 0 | R/W   | Test register.                                                                                                                            |

|         | D0       |                      | 1 | R/W   | Write access is NOT allowed.                                                                                                              |

|         | D1<br>D2 |                      | 1 | R/W   |                                                                                                                                           |

|         | D2<br>D3 |                      | 1 | R/W   |                                                                                                                                           |

| 0x01    |          |                      | - |       |                                                                                                                                           |

|         | D4       |                      | 0 | R/W   |                                                                                                                                           |

|         | D5       |                      | 0 | R/W   |                                                                                                                                           |

|         | D6       |                      | 0 | R/W   |                                                                                                                                           |

|         | D7       |                      | 0 | R/W   |                                                                                                                                           |

|         | D0       |                      | 0 | R/W   | Test register.<br>Write access is NOT allowed.                                                                                            |

|         | D1       |                      | 0 | R/W   |                                                                                                                                           |

|         | D2       |                      | 0 | R/W   |                                                                                                                                           |

| 0x02    | D3       |                      | 0 | R/W   |                                                                                                                                           |

|         | D4       |                      | 0 | R/W   |                                                                                                                                           |

|         | D5       |                      | 0 | R/W   |                                                                                                                                           |

|         | D6       |                      | 0 | R/W   |                                                                                                                                           |

|         | D7       |                      | 0 | R/W   |                                                                                                                                           |

|         | D0       |                      | 0 |       | Test register.                                                                                                                            |

|         | D1       |                      | 0 | R/W   | Write access is NOT allowed.                                                                                                              |

|         | D2       |                      | 0 | R/W   |                                                                                                                                           |

| 0x03    | D3       |                      | 0 | R/W   |                                                                                                                                           |

| 0,00    | D4       |                      | 0 | R/W   |                                                                                                                                           |

|         | D5       |                      | 0 | R/W   |                                                                                                                                           |

|         | D6       |                      | 0 | R/W   |                                                                                                                                           |

|         | D7       |                      | 0 | R/W   |                                                                                                                                           |

|         | D0       | f_drive [0]          | 0 | R/W   | Frequency of bridge driver output pulse.                                                                                                  |

|         | D1       | f_drive [1]          | 0 | R/W   | Frequency F <sub>DRV</sub> = 1000 x (128 / f_drive[10:0]) [kHz].<br>This register value is applied when register 0x05 D[7] is set to "1". |

|         | D2       | f_drive [2]          | 0 | R/W   |                                                                                                                                           |

|         | D3       | f_drive [3]          | 0 | R/W   |                                                                                                                                           |

| 0x04    | D4       | f_drive [4]          | 0 | R/W   |                                                                                                                                           |

|         | D5       | f_drive [5]          | 0 | R/W   |                                                                                                                                           |

|         | D6       | f_drive [6]          | 0 | R/W   |                                                                                                                                           |

|         | D7       | f_drive [7]          | 0 | R/W   |                                                                                                                                           |

|         | D0       | f_drive [8]          | 0 | R/W   |                                                                                                                                           |

|         | D1       | f_drive [9]          | 0 | R/W   |                                                                                                                                           |

|         |          | f_drive [10]         | 1 | R/W   |                                                                                                                                           |

|         | D3       |                      | 0 | R/W   | *1                                                                                                                                        |

| 0x05    | D4       |                      | 0 | R/W   | *1                                                                                                                                        |

|         | D5       |                      | 0 | R/W   | *1                                                                                                                                        |

|         | D6       |                      | 0 | R/W   | *1                                                                                                                                        |

|         | D0       | f_drive_reg_update   | 0 | R/W   | 1 : The value of f_drive[10:0] is applied. (This register automatically returns to 0 after applying.)                                     |

|         |          | duty [0]             | 0 |       | Duty of bridge driver output pulse.                                                                                                       |

|         |          | duty [0]<br>duty [1] | 0 | R/W   | Duty = $100  x$ (duty[9:0] / f_drive[10:0] ) [%].                                                                                         |

|         |          | duty [1]<br>duty [2] | 0 | R/W   | This register value is applied when register 0x07 D[7] is set to "1".                                                                     |

|         |          |                      | 0 | R/W   |                                                                                                                                           |

| 0x06    |          | duty [3]             | 0 |       |                                                                                                                                           |

|         |          | duty [4]             | - | R/W   |                                                                                                                                           |

|         |          | duty [5]             | 0 | R/W   |                                                                                                                                           |

|         |          | duty [6]             | 0 | R/W   |                                                                                                                                           |

|         |          | duty [7]             | 0 | R/W   |                                                                                                                                           |

|         |          | duty [8]             | 0 | R/W   |                                                                                                                                           |

|         | D1       | duty [9]             | 0 | R/W   |                                                                                                                                           |

|         | D2       |                      | 0 | R/W   | *1                                                                                                                                        |

|         | D3       |                      | 0 | R/W   | *1                                                                                                                                        |

| 0x07    |          |                      | 0 | R/W   | *1                                                                                                                                        |