## **RAA457100GBM**

Wireless Charging System Receiver IC for Low Power Applications

R19DS0094EJ0100 Rev.1.00 2017.02.28

#### 1. Product Outline

## Description

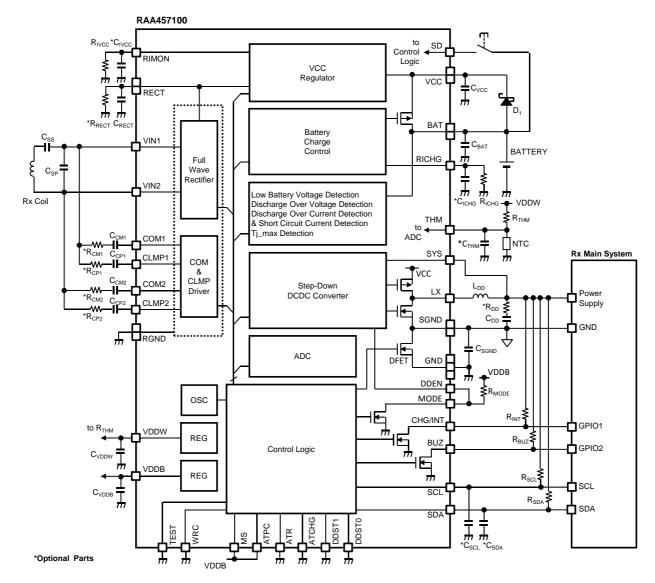

RAA457100 is a receiver IC for low power wireless charging system. RAA457100 performs battery charging by wireless transmission power and DC power supply to receiver application system from battery. When RAA458100 is used in a transmitter, a wireless charging system with bi-directional communication can be constructed.

#### **Features**

- Wireless battery charging

- DC power supply to application system by high efficiency DCDC converter

- Monitoring some pin voltages such as rectified output voltage, battery voltage by 12bit A/D converter

- Modulation/Demodulation function for bi-directional communication between transmitter and receiver

- Transmitter system(RAA458100) can read and write RAA457100 registers for setting charge control parameters

- Function which converts wireless communication to 2-wrie serial communication for communication between transmitter and receiver application system

- Battery protection, Low battery voltage detection

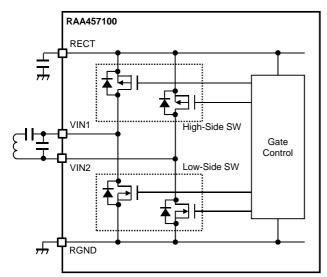

## 2. Block Diagram (Example for Application Circuit)

RAA457100GBM 3. Pin Functions

## 3. Pin Functions

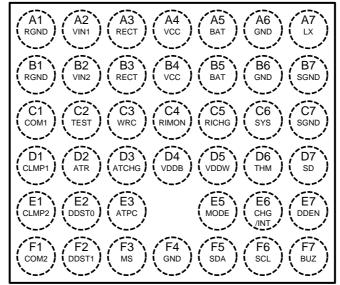

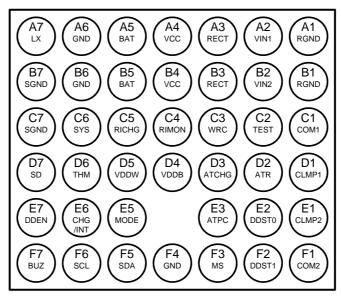

| Pin<br>No.    | Pin<br>Name | A/D<br>*1 | I/O<br>*2 | Function                                                                                      | Remark                                                                                                        |

|---------------|-------------|-----------|-----------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| A6,B6,F4      | GND         | -         | -         | Ground                                                                                        | Connect to minus terminal of battery                                                                          |

| A1,B1         | RGND        | -         | -         | Ground for Rectifier, Load modulation driver, Clamp driver                                    | Connect to minus terminal of battery                                                                          |

| B7,C7         | SGND        | -         | -         | Ground for DCDC converter, application system                                                 | Connected to discharge control FET on chip                                                                    |

| A5,B5         | BAT         | Α         | I/O       | Battery terminal                                                                              | Connect to plus terminal of battery                                                                           |

| A2            | VIN1        | Α         | I         | Input terminal 1 to rectifier                                                                 | -                                                                                                             |

| B2            | VIN2        | Α         | I         | Input terminal 2 to rectifier                                                                 | -                                                                                                             |

| A3,B3         | RECT        | Α         | I/O       | Rectified output terminal                                                                     | Connect C <sub>RECT</sub> between RECT and RGND                                                               |

| C1            | COM1        | Α         | 0         | Load modulation driver output terminal 1                                                      | Connect C <sub>CM1</sub> between COM1 and VIN1                                                                |

| F1            | COM2        | Α         | 0         | Load modulation driver output terminal 2                                                      | Connect C <sub>CM2</sub> between COM2 and VIN2                                                                |

| D1            | CLMP1       | Α         | 0         | Clamp driver output terminal 1                                                                | Connect C <sub>CP1</sub> between CLMP1 and VIN1                                                               |

| E1            | CLMP2       | Α         | 0         | Clamp driver output terminal 2                                                                | Connect C <sub>CP2</sub> between CLMP2 and VIN2                                                               |

| D4            | VDDB        | А         | 0         | Regulated 3.0V output (inside usage)                                                          | Connect C <sub>VDDB</sub> between VDDB and GND                                                                |

| D5            | VDDW        | А         | 0         | Regulated 2.7V output (inside usage, reference voltage for thermistor)                        | Connect C <sub>VDDW</sub> between VDDW and GND Connect to pull up resistor R <sub>THM</sub> of NTC thermistor |

| A4,B4         | VCC         | А         | 0         | VCC regulator output (Power supply for DCDC converter)                                        | Connect C <sub>VCC</sub> between VCC and GND                                                                  |

| C4            | RIMON       | А         | 0         | External resistor connection for output current limit Monitor of VCC regulator output current | Connect R <sub>IVCC</sub> between RIMON and GND                                                               |

| C5            | RICHG       | А         | 0         | External resistor connection for current setting of constant current charging                 | Connect R <sub>ICHG</sub> between RICHG and GND                                                               |

| D6            | ТНМ         | Α         | I         | Thermistor voltage input terminal                                                             | Divided VDDW voltage by R <sub>THM</sub> and NTC thermistor                                                   |

| A7            | LX          | Α         | 0         | DCDC converter switching output terminal                                                      | -                                                                                                             |

| C6            | SYS         | Α         | I         | DCDC converter output voltage feedback terminal                                               | -                                                                                                             |

| E7            | DDEN        | D         | ı         | DCDC converter enable control terminal                                                        | -                                                                                                             |

| D7            | SD          | D         | ı         | Shut down control terminal                                                                    | -                                                                                                             |

| E5            | MODE        | D         | 0         | Operation mode notification output                                                            | Open drain                                                                                                    |

| E6            | CHG/INT     | D         | 0         | Charging status notification output/<br>Interruption signal output for Rx application system  | Open drain                                                                                                    |

| F7            | BUZ         | D         | 0         | Low battery voltage notification                                                              | Open drain                                                                                                    |

| F3            | MS          | D         | ı         | Master or slave setting for 2-wire serial interface                                           | Connect to VDDB or GND                                                                                        |

| F6            | SCL         | D         | I/O       | Clock input or output for 2-wire serial interface                                             | Connect pullup resistor R <sub>SCL</sub>                                                                      |

| F5            | SDA         | D         | I/O       | Data input or output for 2-wire serial interface                                              | Connect pullup resistor R <sub>SDA</sub>                                                                      |

| E2            | DDST0       | D         | ı         | DCDC converter output voltage setting 1                                                       | Connect to VDDB or GND                                                                                        |

| F2            | DDST1       | D         | 1         | DCDC converter output voltage setting 2                                                       | Connect to VDDB or GND                                                                                        |

| D2            | ATR         | D         | ·<br>     | Enable automatic control of rectifier                                                         | Connect to VDDB or GND                                                                                        |

| D3            | ATCHG       | D         |           | Enable automatic start of battery charging                                                    | Connect to VDDB or GND                                                                                        |

| E3            | ATPC        | D         |           | Enable automatic transmission power control function                                          | Connect to VDDB or GND                                                                                        |

| C3            | WRC         | D         | <u> </u>  | Enable contact battery charging                                                               | Connect to GND in wireless charging system                                                                    |

| C2            | TEST        |           | '         | Test only                                                                                     | Connect to GND                                                                                                |

| <sup>02</sup> | IESI        |           |           | I est Offix                                                                                   | Connect to GND                                                                                                |

<sup>\*1</sup> A : Analog signal including power supply, D : Digital signal

\*2 I : Input terminal, O : Output terminal, I/O : Input and Output terminal

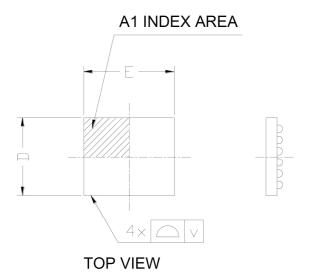

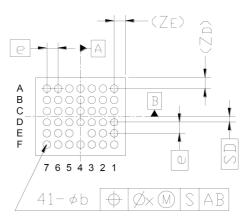

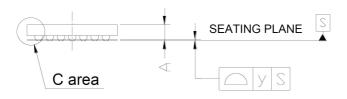

## 4. Pin Configuration

**Top View**

# Bottom View (Ball Side)

## 5. Absolute Maximum Ratings ( Tj=25[degC] unless otherwise noted. )

| Item                    | Symbol                                                                | Value              | Unit | Remark     |

|-------------------------|-----------------------------------------------------------------------|--------------------|------|------------|

|                         | VIN1, VIN2, CLMP1, CLMP2,<br>COM1, COM2, RECT                         | 18                 | V    |            |

| Dinyeltege              | BAT, VCC, SD, DDEN, CHG/INT,<br>MODE, SDA, SCL                        | -0.3 to 5          | V    |            |

| Pin voltage             | RIMON, RICHG, THM,<br>WRC, ATR, ATCHG, ATPC<br>DDST0, DDST1, MS, TEST | -0.3 to VDDB + 0.3 | V    |            |

|                         | SYS, BUZ                                                              | -0.3 to VCC + 0.3  | V    | 5V maximum |

| Operating temperature   | Та                                                                    | -20 to 50          | degC |            |

| Junction temperature Tj |                                                                       | -20 to 70          | degC |            |

| Storage temperature     | Tstg                                                                  | -20 to 70          | degC |            |

## 6. Recommended Operating Conditions

| Item             | Symbol            | Value       | Unit | Remark |

|------------------|-------------------|-------------|------|--------|

| RECT pin voltage | V <sub>RECT</sub> | 3.5 to 6.0  | ٧    |        |

| BAT pin voltage  | V <sub>BAT</sub>  | 3.2 to 4.35 | ٧    |        |

RAA457100GBM 7. Electrical Characteristics

## 7. Electrical Characteristics

Tj=25[degC] unless otherwise noted.

| Item                                                 | Symbol                  | Condition                                                                     | min                   | typ                                                    | max                        | Unit |

|------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------|----------------------------|------|

| Rectified output voltage detection                   |                         |                                                                               |                       |                                                        |                            |      |

| Rectified output voltage lower limit                 | V <sub>RECT_UVLO</sub>  | V <sub>RECT</sub> is raised (hysteresis voltage 100mV)                        | 2.9                   | 3.0                                                    | 3.1                        | V    |

| Rectified output voltage upper limit                 | V <sub>RECT_OVD</sub>   | V <sub>RECT</sub> is raised (hysteresis voltage 7V)                           | 13                    | 14                                                     | 15                         | ٧    |

| Circuit current                                      | •                       |                                                                               |                       |                                                        |                            |      |

| Current at charge mode                               | I <sub>RECT_CM</sub>    | V <sub>RECT</sub> =5V, V <sub>CC</sub> =no load                               | -                     | 1.0                                                    | 2.0                        | mA   |

| Current at discharge mode                            | I <sub>BAT_DM</sub>     | V <sub>RECT</sub> =0V, V <sub>BAT</sub> =3.8V, V <sub>CC</sub> =no load, MS=H | -                     | 25                                                     | -                          | uA   |

| Current at shut down mode                            | I <sub>BAT_SD</sub>     | V <sub>RECT</sub> =0V, V <sub>BAT</sub> =3.0V                                 | -                     | 1                                                      | -                          | uA   |

| Regulator for on chip circuit                        | •                       |                                                                               |                       |                                                        |                            | •    |

| 3.0V regulator output voltage                        | V <sub>DDB</sub>        | V <sub>RECT</sub> =5V, I <sub>SOURCE</sub> =1mA                               | 2.85                  | 3.00                                                   | 3.15                       | V    |

| 2.7V regulator output voltage                        | V <sub>DDW</sub>        | V <sub>RECT</sub> =5V, I <sub>SOURCE</sub> =30uA                              | 2.60                  | 2.70                                                   | 2.80                       | V    |

| VCC regulator                                        | •                       |                                                                               | •                     |                                                        |                            | •    |

| VCC regulator output voltage                         | V <sub>CC</sub>         | V <sub>RECT</sub> =V <sub>BAT</sub> +500mV, V <sub>BAT</sub> =3.8V            | V <sub>BAT</sub> +0.2 | V <sub>BAT</sub> +0.3                                  | V <sub>BAT</sub> +0.4      | V    |

| Output current                                       | I <sub>LIM</sub>        |                                                                               | -                     | -                                                      | 80                         | mA   |

| Battery charging                                     | •                       |                                                                               | •                     |                                                        | •                          |      |

| Charge start voltage                                 | V <sub>START</sub>      | V <sub>BAT</sub> is raised (hysteresis voltage 100mV)                         | -                     | 1.5                                                    | -                          | V    |

| Fast charge start voltage                            | V <sub>QCHGON</sub>     | V <sub>BAT</sub> is raised (hysteresis voltage 100mV)                         | -                     | 3.0                                                    | -                          | V    |

| Charge control voltage range                         | V <sub>CHG</sub>        |                                                                               | 4                     | .05, 4.20, 4.3                                         | 35                         | V    |

| Charge control voltage error                         | V <sub>CHG_ERR</sub>    | $I_{BAT}$ =0.2 x $I_{CHGR}$ , $R_{ICHG}$ =5.6kΩ                               | -50                   | -                                                      | +50                        | mV   |

| Trickle charge current                               | I <sub>PRECHG</sub>     |                                                                               |                       | 0.1 x I <sub>CHGR</sub>                                |                            | -    |

| Trickle charge current error                         | I <sub>PRECHG_ERR</sub> | $I_{BAT}$ =0.1 x $I_{CHGR}$ , $R_{ICHG}$ =5.6kΩ                               | -50                   | -                                                      | +50                        | %    |

| Fast charge current range                            | I <sub>CHG</sub>        |                                                                               | -                     | -                                                      | 70                         | mA   |

| Fast charge current error                            | I <sub>CHG_ERR</sub>    | $I_{BAT}$ =0.5 x $I_{CHGR}$ , $R_{ICHG}$ =5.6kΩ                               | -30                   | -                                                      | +30                        | %    |

| Charge complete current range                        | I <sub>FC</sub>         |                                                                               | 0.05 x<br>(0.         | I <sub>CHGR</sub> to 0.20<br>05 x I <sub>CHGR</sub> st | x I <sub>CHGR</sub><br>ep) | -    |

| Charge complete current error                        | I <sub>FC_ERR</sub>     | $I_{BAT}$ =0.2 x $I_{CHGR}$ , $R_{ICHG}$ =5.6k $\Omega$                       | -60                   | -                                                      | +60                        | %    |

| Trickle charge timer range                           | T <sub>DCHG</sub>       |                                                                               |                       | 60, 120, 180                                           |                            | min  |

| Trickle charge timer error                           | T <sub>DCHG_ERR</sub>   |                                                                               | -                     | 10                                                     | -                          | %    |

| Fast charge timer range                              | T <sub>CHG</sub>        |                                                                               | 18                    | 0, 240, 300, 3                                         | 360                        | min  |

| Fast charge timer error                              | T <sub>CHG_ERR</sub>    |                                                                               | -                     | 10                                                     | -                          | %    |

| Battery protection                                   | •                       |                                                                               |                       | •                                                      |                            |      |

| Charge overvoltage detection voltage *1              | V <sub>COVD</sub>       | BAT to GND differential voltage                                               | -                     | V <sub>CHG</sub> +0.1                                  | -                          | V    |

| Charge overvoltage detection delay time              | T <sub>COVD</sub>       |                                                                               | -                     | 256                                                    | -                          | ms   |

| Discharge short circuit current detection voltage    | V <sub>DSCD</sub>       | SGND to GND differential voltage                                              | -                     | 160                                                    | -                          | mV   |

| Discharge short circuit current detection delay time | T <sub>DSCD</sub>       |                                                                               | -                     | 250                                                    | -                          | us   |

| Discharge overcurrent detection voltage              | V <sub>DOCD</sub>       | SGND to GND differential voltage                                              | -                     | 80                                                     | -                          | mV   |

| Discharge overcurrent detection delay time           | T <sub>DOCD</sub>       |                                                                               | -                     | 4                                                      | -                          | ms   |

| Discharge overvoltage detection voltage              | V <sub>DOVD</sub>       | BAT to GND differential voltage                                               | -                     | 2.8                                                    | -                          | V    |

| Discharge overvoltage detection delay time           | T <sub>DOVD</sub>       |                                                                               | -                     | 32                                                     | -                          | ms   |

$<sup>^{\</sup>star}1\ \ \text{Detection voltage is set to suitable temperature charge control voltage} (V_{\text{CHG}}) + 0.1[V]\ \text{regardless of thermistor temperature}.$

RAA457100GBM 7. Electrical Characteristics

# 7. Electrical Characteristics (continued)

Tj=25[degC] unless otherwise noted.

| Item                                                | Symbol                 | Condition                                                            | min  | typ            | max  | Unit        |

|-----------------------------------------------------|------------------------|----------------------------------------------------------------------|------|----------------|------|-------------|

| Low battery voltage detection                       | •                      |                                                                      | •    |                |      |             |

|                                                     | .,                     | V <sub>SYS</sub> =1.2V,or 1.5V,or 1.8V                               | 3.10 | 3.20           | 3.30 | T ,,        |

| Low battery detection voltage H                     | V <sub>FGHD</sub>      | V <sub>SYS</sub> =3.0V                                               | 3.45 | 3.55           | 3.65 | _           |

| Landa Maria Lata di Santa Maria L                   | .,                     | V <sub>SYS</sub> =1.2V,or 1.5V,or 1.8V                               | 2.95 | 3.05           | 3.15 | <b>\</b> ,, |

| Low battery detection voltage L                     | $V_{FGLD}$             | V <sub>SYS</sub> =3.0V                                               | 3.25 | 3.35           | 3.45 | \ \         |

| Low battery voltage detection delay time            | T <sub>FGD</sub>       |                                                                      | -    | 256            | -    | ms          |

| DCDC converter                                      |                        |                                                                      |      |                |      |             |

| UVLO release voltage<br>(V <sub>CC</sub> is raised) | V                      | V <sub>SYS</sub> =1.2V,or 1.5V,or 1.8V<br>(hysteresis voltage 100mV) | 2.80 | 2.90           | 3.00 |             |

|                                                     | V <sub>DCDC_UVLO</sub> | V <sub>SYS</sub> =3.0V<br>(hysteresis voltage120mV)                  | 3.20 | 3.30           | 3.50 | v           |

| Output voltage range                                | V <sub>SYS</sub>       |                                                                      | 1.   | 2, 1.5, 1.8, 3 | 3.0  | V           |

| Output current range                                | I <sub>SYS</sub>       | Discharge mode                                                       | -    | -              | 100  | mA          |

| A/D converter                                       |                        |                                                                      |      |                |      |             |

| Resolution                                          | ADC <sub>RES</sub>     |                                                                      | -    | 12             | -    | bit         |

| WPT communication                                   |                        |                                                                      |      |                |      |             |

| Bit rate from RX to TX                              | BR <sub>RX2TX</sub>    |                                                                      | -    | 250            | -    | bps         |

| Bit rate from TX to RX                              | BR <sub>TX2RX</sub>    |                                                                      | -    | 125            | -    | bps         |

| COM, CLAMP driver                                   | •                      | •                                                                    | •    |                | •    |             |

| ON resistance                                       | R <sub>ON_DRV</sub>    |                                                                      | -    | 0.5            | -    | Ω           |

| Leak current                                        | I <sub>L_DRV</sub>     | Pin voltage=15V                                                      | -    | -              | 10   | uA          |

| Discharge control FET                               |                        |                                                                      |      |                |      |             |

| ON resistance                                       | R <sub>ON_DFET</sub>   |                                                                      | -    | 0.4            | -    | Ω           |

| Resistance between SGND and GND                     | R <sub>SG</sub>        | V <sub>DOCD</sub> or V <sub>DSCD</sub> detection condition           | -    | 5              | -    | kΩ          |

| SDA, SCL                                            | •                      |                                                                      |      |                | •    | •           |

| High level input voltage                            | V <sub>IH_I2C</sub>    |                                                                      | 1.0  | -              | -    | V           |

| Low level input voltage                             | V <sub>IL_I2C</sub>    |                                                                      | -    | -              | 0.3  | V           |

| Low level output voltage                            | V <sub>OL_I2C</sub>    | I <sub>SINK</sub> =2mA                                               | -    | -              | 0.2  | V           |

| MODE, CHG/INT, BUZ                                  | •                      |                                                                      | •    |                |      | •           |

| Low level output voltage                            | V <sub>OL_OD</sub>     | I <sub>SINK</sub> =2mA                                               | -    | -              | 0.2  | V           |

| Leak current                                        | I <sub>L_OD</sub>      | Pin voltage=3V                                                       | -    | -              | 5    | uA          |

| DDEN                                                | •                      | •                                                                    | •    | •              | •    | •           |

| High level input voltage                            | V <sub>IH_DDEN</sub>   |                                                                      | 1.0  | -              | -    | V           |

| Low level input voltage                             | V <sub>IL_DDEN</sub>   |                                                                      | -    | -              | 0.3  | V           |

| SD                                                  |                        | •                                                                    |      |                | •    | •           |

| High level input voltage                            | V <sub>IH_SD</sub>     |                                                                      | 2.6  | -              | -    | V           |

| Low level input voltage                             | V <sub>IL_SD</sub>     |                                                                      | -    | -              | 0.3  | V           |

8. Functions Description (The values described in this chapter are reference values, not guaranteed values.)

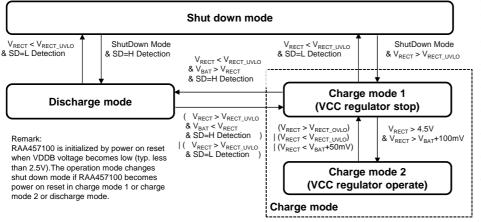

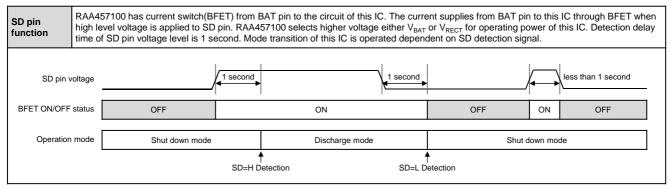

#### 8.1 Operation Mode and SD Pin Function

The RAA457100 have shut down mode and charge mode 1 and charge mode 2, and discharge mode. Table 8.1.1 shows outline of each operating mode, and Table 8.1.2 shows function of each operating mode. Figure 8.1.1 shows mode transition and SD pin function.

Table 8.1.1 Outline of each operation mode

| Operating mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shut down mode | Major functions stop in this mode. The conditions in this mode are no power feed by wireless power transmission and battery, or VDDB voltage is lower than 2.5V. In discharge mode, the current from BAT pin to the circuit of this IC is shut down when low level voltage longer than 1 second is input to SD pin. In this state, if V <sub>RECT</sub> is lower than V <sub>RECT_UVLO</sub> , the operating mode changes shut down mode.                                                                                                                                                                                  |

| Charge mode 1  | This IC operates by rectified voltage in this mode. In discharge mode if $V_{RECT}$ is higher than $V_{RECT\_UVLO}$ and $V_{RECT}$ is higher than $V_{RECT\_UVLO}$ , or in shut down mode if $V_{RECT}$ is higher than $V_{RECT\_UVLO}$ , the operating mode changes into charge mode 1.                                                                                                                                                                                                                                                                                                                                   |

| Charge mode 2  | In this mode, battery charging and WPT communication are available. In charge mode 1, if $V_{RECT}$ is higher than 4.5V, and $V_{RECT}$ is higher than $V_{BAT}$ +100mV, the operating mode changes charge mode 2. VCC regulator starts to operate. After VCC regulator starts, VCC regulator continues to operate in condition $V_{RECT} > V_{RECT}_{LUVLO}$ , $V_{RECT} < V_{RECT}_{LUVLO}$ , $V_{RECT} > V_{BAT}$ +50mV. The transmission power should be controlled so that the rectified voltage is 0.5V higher than battery voltage. It means that charge control circuit and receiver main system can operate well. |

| Discharge mode | In this mode, this IC operates by battery power. In shut down mode, if high level voltage longer than 1 second is input to SD pin, the operating mode changes into discharge mode. Or in charging mode 1, if V <sub>RECT</sub> is lower than V <sub>RECT_UVLO</sub> and V <sub>BAT</sub> is higher than V <sub>RECT</sub> , the operating mode changes into discharge mode.                                                                                                                                                                                                                                                |

Table 8.1.2 Function of each operation mode

| Operating mode | Battery Protection *1 | ADC , VDDW | VCC regulator | Charge control *2 | DCDC converter *3 |

|----------------|-----------------------|------------|---------------|-------------------|-------------------|

| Shut down mode |                       |            | stop          |                   |                   |

| Charge mode 1  | operate               | operate    | stop          | stop              | available         |

| Charge mode 2  | operate               | operate    | operate       | available         | available         |

| Discharge mode | operate               | stop       | stop          | stop              | available         |

<sup>\*1</sup> Discharge control FET (DFET) becomes off if battery protection level is detected.

<sup>\*2</sup> Battery charging is started automatically when operating mode become charge mode 2 if ATCHG pin level is high(VDDB).

Battery charging can be started by register setting (0x01 D[0]=1) if ATCHG pin level is low.

\*3 DCDC converter is started when DDEN pin is high level and V<sub>CC</sub> > V<sub>DCDC\_UVLO</sub>, and discharge control FET is on.

| Symbol                        | Description                                                 |  |  |

|-------------------------------|-------------------------------------------------------------|--|--|

| &                             | Logical AND                                                 |  |  |

| 1                             | Logical OR                                                  |  |  |

| V <sub>BAT</sub>              | Battery voltage<br>(BAT pin voltage)                        |  |  |

| V <sub>RECT</sub>             | Rectified voltage<br>(RECT pin voltage)                     |  |  |

| V <sub>RECT_UVLO</sub>        | Rectified output undervoltage detection voltage             |  |  |

| V <sub>RECT_OVLO</sub>        | Rectified output overvoltage detection voltage              |  |  |

| SD=H<br>Detection *1          | High level voltage longer than 1 second is input to SD pin. |  |  |

| SD=L<br>Detection *1          | Low level voltage longer than 1 second is input to SD pin.  |  |  |

| *4 *** 1 4 40 1 4 41 10 41 11 |                                                             |  |  |

\*1 This detection is operated in all operation mode.

Figure 8.1.1 Mode transition and SD pin function

#### 8.2 Rectifier

Rectified output (RECT pin) voltage rises in asynchronous rectifying operation by body diode of switch MOSFET. When rectified output voltage lower limit is detected ( $V_{RECT} > V_{RECT\_UVLO}$ ), the gate control circuit controls the high side switch depending on VIN1, VIN2, RECT pin voltages (half synchronous rectifying operation). When a current of the high side switch increases, the gate control circuit controls the low side switch too (full synchronous rectifying operation). A current of the high side switch depends on VCC regulator output current( $I_{VCC}$ ). When the voltage level of ATR pin and ATPC pin are high voltage, the operation function control depending on VCC regulator current are available in battery charge, such as rectifying operation (half synchronous, half or full synchronous automatically changed) and on-resistance of the high side switch. The settings of the rectifying operation and the on-resistance of the high side switch are five, and the current threshold of the VCC regulator output to change these settings can be set by register (show the register map). When ATR pin level is low voltage, the rectifying operation is half synchronous rectifying operation, and the on-resistance of the high side switch is  $1[\Omega]$ . When the settings of the current threshold is not appropriate, rectifying operation becomes unstable (a change of half synchronous rectifying operation and full synchronous rectifying operation becomes unstable), and then ripple voltage of rectified voltage is increased. If the settings of the appropriate current threshold is difficult, it is recommended to set ATR pin level to low voltage.

| Rectifier operation                | vcc                              | VCC output current thresho | old             |

|------------------------------------|----------------------------------|----------------------------|-----------------|

| /on-resistance of high side switch | regulator<br>current<br>changing | Register settings          | Initial<br>(mA) |

| Holf owneh/4[O]                    | i                                | -                          | -               |

| Half synch/1[Ω]                    | decreasing                       | 0x1B D[7:0]                | 3.868           |

| Full over the /OFO1                | increasing                       | 0x1B D[7:0] + 0x1F D[6:0]  | 7.736           |

| Full synch/8[Ω]                    | decreasing                       | 0x1C D[7:0]                | 8.087           |

| Full over the /4[O]                | increasing                       | 0x1C D[7:0] + 0x1F D[6:0]  | 11.96           |

| Full synch/4[Ω]                    | decreasing                       | 0x1D D[7:0]                | 16.17           |

| F. II h /0[0]                      | increasing                       | 0x1D D[7:0] + 0x1F D[6:0]  | 20.04           |

| Full synch/2[Ω]                    | decreasing                       | 0x1E D[7:0]                | 31.99           |

| Full oursels (410)                 | increasing                       | 0x1E D[7:0] + 0x1F D[6:0]  | 35.86           |

| Full synch/1[Ω]                    | -                                | -                          | -               |

Figure 8.2.1 Rectifier circuit, and Rectifier action on ATR pin and ATPC pin = high

### 8.3 A/D Converter

In charge mode, some pin voltages (RECT pin voltage, BAT pin voltage, etc) are monitored by 12bit A/D converter. Table 8.3.1 shows monitor items of A/D converter. These items are monitored in 4[ms] period. These items are used by calculating parameters for automatic transmission power control and charging control (battery temperature, battery voltage). 2-wire serial interface and WPT communication make it possible to read the A/D conversion results. A/D conversion results in register are not updated automatically. When 0x35 D[0] is 1, all registers of A/D conversion result are updated.

Table 8.3.1 Monitor items of A/D converter

| Item                                             | monitor point                        | Output code *1                                                                                                               | Input voltage range *2<br>(Actual voltage range) | Register(12bit)            |

|--------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------|

| Rectified output voltage                         | RECT pin voltage V <sub>RECT</sub>   | ( 4096 / 10.8 ) x V <sub>RECT</sub>                                                                                          | 0 to 10.8V<br>( 3.2 to 10 V )                    | 0x36 D[7:4]<br>0x37 D[7:0] |

| VCC regulator output current (I <sub>VCC</sub> ) | RIMON pin voltage V <sub>RIMON</sub> | $(4096/2.7) \times V_{RIMON}$<br>$(V_{RIMON} = (I_{VCC} \times R_{IVCC}) / K_{IVCC})$                                        | 0 to 2.7 V<br>( 0 to 1.2 V )                     | 0x38 D[7:4]<br>0x39 D[7:0] |

| Battery voltage                                  | BAT pin voltage<br>V <sub>BAT</sub>  | ( 4096 / 5.4 ) x V <sub>BAT</sub>                                                                                            | 0 to 5.0 V<br>( 0 to 4.35 V )                    | 0x3A D[7:4]<br>0x3B D[7:0] |

| Charging current (I <sub>CHG</sub> )             | RICHG pin voltage V <sub>RICHG</sub> | ( 4096 / 2.7 ) x V <sub>RICHG</sub><br>( V <sub>RICHG</sub> = ( I <sub>CHG</sub> x R <sub>ICHG</sub> ) / K <sub>ICHG</sub> ) | 0 to 2.7V<br>( 0 to 1.2 V )                      | 0x3C D[7:4]<br>0x3D D[7:0] |

| Thermistor temperature (Battery temperature)     | THM pin voltage<br>V <sub>THM</sub>  | ( 4096 / 2.7 ) x V <sub>THM</sub>                                                                                            | 0 to 2.7 V<br>( 0 to 2.7 V )                     | 0x3E D[7:4]<br>0x3F D[7:0] |

<sup>\*1</sup> Output code range is from 0 to 4095.

<sup>\*2</sup> Each inputted voltage should be within input voltage range to avoid miss converting.

The voltage range in the parenthesis shows a voltage range assumed in practical use.

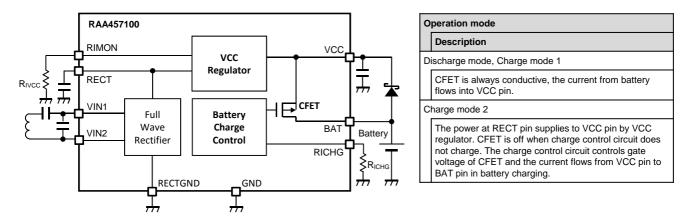

#### 8.4 Power Supply to VCC Pin

Figure 8.4.1 shows block diagram of VCC regulator and battery charge control and charge control FET(CFET). Charge control FET is conductive in discharge mode and charge mode 1, current from battery flows into VCC pin. VCC regulator operates in charge mode 2. Current from RECT pin flows into VCC pin. When battery charging does not operate, CFET is off. In battery charging, the battery charge control circuit controls the gate voltage of CFET, charging current from VCC pin flows into BAT pin. VCC regulator regulates the voltage which is 3.3V to 4.8V depending on BAT pin voltage. VCC regulator has current limit function showed in Table 8.4.1. VCC regulator output voltage is changed depending on current no limit state or current limit state when charge control operates (Table 8.4.2). If VCC regulator is in current limit state, battery charging current is adjusted depending on limiting current (load current dividing function of charge control circuit). To prevent the current limit by low RECT pin voltage, the transmission power has to maintain recommended RECT pin voltage showed in Table 8.4.2.

Figure 8.4.1 Block diagram of VCC regulator and battery charge control and charge control FET

Table 8.4.1 Current limit function of VCC regulator

| Item                                  | Description                                                                                                                                                                                                                                                                                                                                     |                                                                                                                          |  |  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Current limit by                      | The maximum output                                                                                                                                                                                                                                                                                                                              | The maximum output current of VCC regulator can be set by external resistor R <sub>IVCC</sub> between RIMON pin and GND. |  |  |  |  |  |

| R <sub>IVCC</sub>                     | The relation of R <sub>IVCC</sub> a                                                                                                                                                                                                                                                                                                             | and output limiting current                                                                                              |  |  |  |  |  |

|                                       | Limiting current                                                                                                                                                                                                                                                                                                                                | $I_{LIM} = K_{IVCC} x (1.2 / R_{IVCC})$                                                                                  |  |  |  |  |  |

|                                       | Parameter $K_{IVCC} = 80$<br>$R_{IVCC} = 1.2$ kΩ, or $2.4$ kΩ, or $4.8$ kΩ (prohibit using except recommended value <sup>-1</sup> )                                                                                                                                                                                                             |                                                                                                                          |  |  |  |  |  |

| Current limit by low RECT pin voltage | When the differential voltage between RECT pin and BAT pin is low, VCC regulator output current is limited. The output current starts to be limited on $V_{RECT} - V_{BAT} < 0.4V$ , the output current decreases depending on the differential voltage. The output current is limited so that $V_{RECT}$ does not decrease than below voltage. |                                                                                                                          |  |  |  |  |  |

|                                       | RECT pin voltage when output current of VCC regulator is 0mA.                                                                                                                                                                                                                                                                                   |                                                                                                                          |  |  |  |  |  |

|                                       | $V_{BAT} > 3.0V$ $V_{RECT} = V_{BAT} + 0.2V$                                                                                                                                                                                                                                                                                                    |                                                                                                                          |  |  |  |  |  |

|                                       | V <sub>BAT</sub> < 3.0V                                                                                                                                                                                                                                                                                                                         | $V_{RECT} = 3.2V$                                                                                                        |  |  |  |  |  |

<sup>\*1</sup>  $R_{\text{IVCC}}$  is detected before VCC regulator starts, the circuit works depending on detection result.  $R_{\text{IVCC}}$  value need to be 1.2k or 2.4k or 4.8k $\Omega$ .

## Table 8.4.2 VCC pin voltage

| BAT pin voltage (V <sub>BAT</sub> )                                  |                         | voltage<br>circuit operating | RECT pin recommended voltage(V <sub>RECT</sub> ) *1 |  |

|----------------------------------------------------------------------|-------------------------|------------------------------|-----------------------------------------------------|--|

|                                                                      | Current no limit state  | Current limit state          |                                                     |  |

| $3.0 \text{V} \leq \text{V}_{\text{BAT}} \leq \text{V}_{\text{CHG}}$ | V <sub>BAT</sub> + 0.3V | V <sub>BAT</sub> + 0.1V      | $V_{RECT} > V_{BAT} + 0.5V$                         |  |

| V <sub>BAT</sub> < 3.0V                                              | 3.3V                    | 3.1V                         | V <sub>RECT</sub> > 3.5V                            |  |

<sup>\*1</sup> This is the condition in order to avoid limiting the output current of VCC regulator by decreasing RECT pin voltage

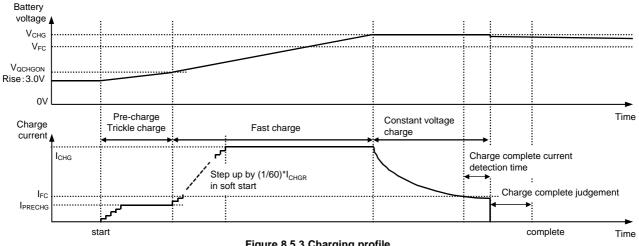

#### 8.5 Battery Charge Control

#### 8.5.1 Battery Charge Method

This IC has the charge function for Li-ion battery (constant current - constant voltage charge method). Some charge control parameters can be set by the registers.

## 8.5.2 Charge Start Voltage, Trickle to Fast Charge Transition Threshold Voltage and Charge Overvoltage Detection Voltage

Table 8.5.2 shows charge start voltage and trickle to fast charge transition threshold voltage and charge overvoltage detection voltage, and detection delay time. These voltages are judged by control circuit using A/D conversion result of BAT pin voltage.

Table 8.5.2 Charge start voltage, Trickle to fast charge transition threshold voltage, Charge overvoltage detection voltage

| Item                                                | Detection voltage                                  | Detection delay time |

|-----------------------------------------------------|----------------------------------------------------|----------------------|

| Charge start voltage*1                              | 1.5V (hysteresis voltage 100mV)                    | 256ms                |

| Trickle to fast charge transition threshold voltage | 3.0V (hysteresis voltage 100mV)                    | 256ms                |

| Charge overvoltage detection voltage*2              | Suitable temperature charge control voltage +100mV | 256ms                |

## 8.5.3 Charge Current, Charge Complete Current, Charge Control Voltage, Charge Timer

The maximum charge current is 70[mA]. Reference fast charge current  $I_{CHGR}$  is set by resistor  $R_{ICHG}$  between RICHG pin and GND. Pre-charge current and trickle charge current are set to one tenth(1/10) of reference fast charge current I<sub>CHGR</sub>. In soft start of fast charge, charging current increases stepped by (1/60)\*I<sub>CHGR</sub>. The transition time of 1 step can be set by register. The fast charge current and the charge control voltage can be set to 3 values in each battery temperature. Trickle charge timer and fast charge timer can be set by register. If the timer overflows, battery charge is stopped. Table 8.5.3 shows the parameters of charge current and charge complete current and charge control voltage, and charge timer.

Table 8.5.3 Charge control parameters

| Item                                                        | Symbol                | Value                                                                                                        | Unit | Remark                |

|-------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|------|-----------------------|

| Reference fast charge current                               | I <sub>CHGR</sub>     | 1.2 x K <sub>ICHG</sub> / R <sub>ICHG</sub>                                                                  | Α    | K <sub>ICHG</sub> =80 |

| Pre-charge current Trickle charge current                   | I <sub>PRECHG</sub>   | 0.1 x I <sub>CHGR</sub>                                                                                      | Α    | -                     |

| Fast charge current range *1                                | I <sub>CHG</sub>      | $I_{CHGR}$ , 0.5 x $I_{CHGR}$ , 0.25 x $I_{CHGR}$                                                            | Α    | Register 0x02 D[7:2]  |

| Charge current transition step in soft start of fast charge | I <sub>CHG_SOFT</sub> | (1 / 60) x I <sub>CHGR</sub>                                                                                 |      | -                     |

| Transition time of one step in soft start of fast charge    | T <sub>CHG_SOFT</sub> | 15.625, 7.8125, 3.125                                                                                        | ms   | Register 0x02 D[1:0]  |

| Charge control voltage *1                                   | V <sub>CHG</sub>      | 4.05 , 4.20 , 4.35                                                                                           | V    | Register 0x03 D[7:2]  |

| Charge complete current                                     | I <sub>FC</sub>       | 0.20 x I <sub>CHGR</sub> , 0.15 x I <sub>CHGR</sub> ,<br>0.10 x I <sub>CHGR</sub> , 0.05 x I <sub>CHGR</sub> |      | Register 0x03 D[1:0]  |

| Charge complete judgement voltage                           | V <sub>FC</sub>       | 3.8                                                                                                          | V    | -                     |

| Trickle charge timer                                        | T <sub>DCHG</sub>     | 60, 120, 180                                                                                                 | min  | Register 0x04 D[1:0]  |

| Fast charge timer                                           | T <sub>CHG</sub>      | 180, 240, 300, 360                                                                                           | min  | Register 0x04 D[3:2]  |

<sup>\*1</sup> It can be set in each battery temperature(low, suitable, high)

<sup>\*1</sup> RAA457100 can charge to zero V battery by setting register D[7] in address 0x04.

\*2 In low temperature and suitable temperature and high temperature, each charge control voltage can be set to 4.05V or 4.20V or 4.35V. (show section 8.5.3, 8.5.4)

#### 8.5.4 Battery Temperature Monitor

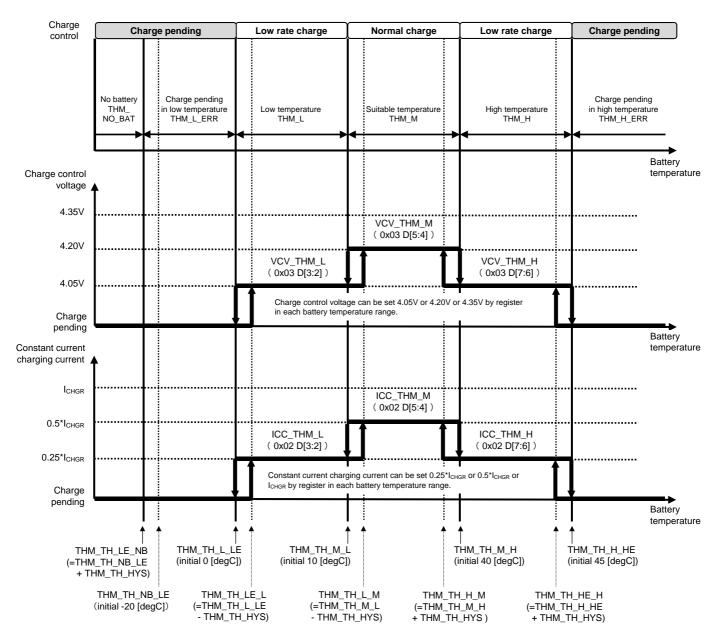

RAA457100 controls the fast charging current and the charge control voltage depending on battery temperature. The fast charging current and the charge control voltage can be set by registers in each temperature range. But the charge control voltage of low and high temperature range needs to be lower than the charge control voltage of suitable temperature range. The battery temperature range threshold can be set by registers that are THM\_TH\_NB\_LE(no battery and charge pending in low temperature threshold), THM\_TH\_L\_LE(low rate charge in low temperature and charge pending in low temperature threshold), THM\_TH\_M\_L(normal charge and low rate charge in low temperature threshold), THM\_TH\_M\_H(normal charge and low rate charge in high temperature and charge pending in high temperature threshold), THM\_TH\_HYS(hysteresis) in address 0x05 to 0x0A. THM\_TH\_LE\_NB(charge pending in low temperature and no battery threshold), THM\_TH\_LE\_L(charge pending in low temperature and low rate charge in low temperature threshold), THM\_TH\_LAM(low rate charge in low temperature and normal charge threshold), THM\_TH\_HAM(low rate charge in high temperature and normal charge threshold), THM\_TH\_HE\_H(charge pending in high temperature and low rate charge in high temperature threshold) are calculated by the registers described above. These registers are written initially by the value for NTC thermistor NCP03WF104F05RL, NCP15WF104F03RC (Murata Manufacturing) or an equivalent device. (refer to register map)

Figure 8.5.4 Battery temperature threshold, Charge control voltage, Constant current charge current

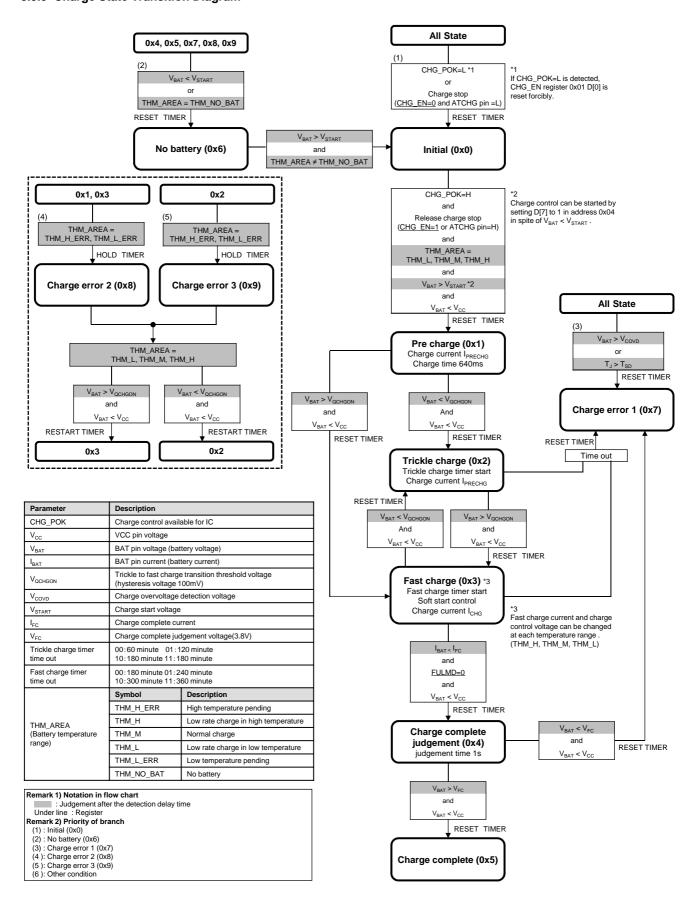

#### 8.5.5 Charge State Transition Diagram

## 8.6 Power Supply to Application System (Buck DCDC Converter, Battery Protection)

#### 8.6.1 Buck DCDC Converter

The buck DCDC converter supplies power to application system. The input voltage of DCDC converter is VCC pin voltage. DCDC converter starts when DDEN pin level is high. DCDC converter output voltage can be set by settings of DDST0 pin and DDST1 pin (show Table 8.6.1.1). Some status of DCDC converter can be monitored by registers. When 2-wire serial interface set into slave device by setting MS pin to low, an application system can read the registers by 2-wire serial interface. Table 8.6.1.2 shows registers related to DCDC converter. If the equivalent series resistance of output capacitor  $C_{DD}$  is small, the output ripple voltage might be increased. If the DCDC converter output is unstable, series resistance  $R_{DD}$  should be connected to output capacitor  $C_{DD}$  for improvement (Refer to Block Diagram).

Table 8.6.1.1 DCDC converter output voltage settings

| Voltage input | Enable pin  | DDST1 pin | DDST0 pin | Output voltage |

|---------------|-------------|-----------|-----------|----------------|

|               |             | L         | L         | 1.2V           |

| VCC           | VCC DDEN '1 | L         | Н         | 1.5V           |

| VCC           |             | Н         | L         | 1.8V           |

|               |             | Н         | Н         | 3.0V           |

<sup>\*1</sup> DCDC converter starts when DDEN pin level is high.

Table 8.6.1.2 Registers related to DCDC converter

| Item                                             | Register               | Description                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC pin voltage<br>detection<br>(UVLO detection) | 0x33 D[4]              | DCDC converter is controlled depending on VCC pin voltage level.  0 : Stop (UVLO detected)  V <sub>CC</sub> < 2.80V(Output voltage is 1.2V or 1.5V or 1.8V)  V <sub>CC</sub> < 3.18V(Output voltage is 3.0V)  1 : Start (UVLO release)  V <sub>CC</sub> > 2.90V(Output voltage is 1.2V or 1.5V or 1.8V)  V <sub>CC</sub> > 3.30V(Output voltage is 3.0V) |

| Start up complete                                | 0x33 D[5]              | DCDC converter confirms the completion of start up by monitoring SYS pin voltage. 0: Low voltage status of SYS pin ( $V_{SYS}$ < Setting output voltage x 0.831) 1: Start up complete ( $V_{SYS}$ > Setting output voltage x 0.875)                                                                                                                      |

| Overvoltage<br>detection of SYS<br>pin           | 0x33 D[6]              | DCDC converter stops switching MOSFET if overvoltage is detected at SYS pin.  0 : Not detected (V <sub>SYS</sub> < Setting output voltage x 1.207)  1 : Detected (V <sub>SYS</sub> > Setting output voltage x 1.250)                                                                                                                                     |

| Overcurrent detection *1                         | 0x33 D[7]<br>0x30 D[2] | If overcurrent condition of DCDC converter is detected continuously, the status register is 1(0x33 D[7]=1). The delay time of detection is 8ms.                                                                                                                                                                                                          |

<sup>\*1</sup> Interruption signal is output from CHG/INT pin when MS pin level is low and register 0x2F D[2] is 0.

#### 8.6.2 Battery Protection, Maximum Junction Temperature Protection

Battery protection functions are discharge overvoltage protection and discharge overcurrent protection and discharge short circuit current protection. Temperature protection is maximum junction temperature protection. Table 8.6.2 shows protection detection threshold and detection delay time and post-processing.

Table 8.6.2 Protection detection threshold, Detection delay time, Post-processing

|                                                        |                                    |                      | Post-processing *1          |                                        |                      |                                   |                   |  |  |  |  |  |

|--------------------------------------------------------|------------------------------------|----------------------|-----------------------------|----------------------------------------|----------------------|-----------------------------------|-------------------|--|--|--|--|--|

| Item<br>(Voltage for detection)                        | Detection voltage<br>/ temperature | Detection delay time | Discharge<br>control<br>FET | Resistor<br>between<br>SGND and<br>GND | DCDC<br>Converter *2 | Digital input /<br>output pins *3 | Charge<br>control |  |  |  |  |  |

| Discharge overvoltage (between BAT and GND)            | 2.8V                               | 2.8V 32ms            |                             | disconnect                             | suspend              | suspend                           | •                 |  |  |  |  |  |

| Discharge overcurrent (between SGND and GND)           | 80mV                               | 4ms                  | off connect                 |                                        | suspend              | suspend                           | -                 |  |  |  |  |  |

| Discharge short circuit current (between SGND and GND) |                                    |                      | off connect                 |                                        | suspend              | suspend                           | -                 |  |  |  |  |  |

| Maximum junction temperature 68 degree C               |                                    | 256ms                | off                         | disconnect                             | suspend              | suspend                           | suspend           |  |  |  |  |  |

<sup>\*1</sup> DCDC converter, discharge control FET and digital input/output pins restart automatically from suspend when each protection is released.

\*2 DCDC converter is also suspended when VCC pin voltage is lower than UVLO voltage(V<sub>DCDC\_UVLO</sub>).

If battery protection and junction temperature error and UVLO(V<sub>CC</sub> < V<sub>DCDC\_UVLO</sub>) is detected, DCDC converter is stopped.

<sup>\*3</sup> MODE, CHG/INT, BUZ, SCL and SDA pins are applicable.

#### 8.7 Battery Low Voltage Notification (BUZ pin)

Battery low voltage notification has two threshold voltages depending on DCDC converter output voltage. There are two ways of notice. BUZ pin (open drain output) outputs low level when battery low voltage H or battery low voltage L is detected and register 0x34 D[2] is 0. BUZ pin outputs specified pulse (show Table 8.7) when register 0x34 D[2] is 1. Battery low voltage detection result is also stored in register 0x34 D[1:0].

Table 8.7 Battery low voltage notification

| Item                                                        | DCDC converter   | Detection voltage | Detection                                                                | Post-processing                                    |                                                         |  |  |  |

|-------------------------------------------------------------|------------------|-------------------|--------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|--|--|--|

| Rem                                                         | output voltage   | Detection voltage | Detection delay time  256ms                                              | 0x34 D[2]=0                                        | 0x34 D[2]=1                                             |  |  |  |

| Battery low voltage                                         | 1.2V, 1.5V, 1.8V | 3.20V             | 3.55V When battery voltage becomes higher than detection voltage, BUZ pi | BUZ pin outputs low level.<br>When battery voltage | BUZ pin outputs pulse,<br>256[ms] low level pulse width |  |  |  |

| detection H<br>(between BAT and GND)                        | 3.0V             | 3.55V             |                                                                          | detection voltage, BUZ pin                         | in 2560[ms] period.                                     |  |  |  |

| Battery low voltage<br>detection L<br>(between BAT and GND) | 1.2V, 1.5V, 1.8V | 3.05V             | 2301115                                                                  | returns high level.                                | BUZ pin outputs pulse,<br>128[ms] low level pulse width |  |  |  |

|                                                             | 3.0V             | 3.35V             |                                                                          |                                                    | in 1280[ms] period.                                     |  |  |  |

## 8.8 Charge Status Notification / Interrupt Signal Output (CHG / INT pin)

CHG / INT pin(open drain output) function is changed by MS pin setting. Table 8.8.1 shows this function. CHG / INT pin outputs low level when interruption event showed in Table 8.8.2 occurs and MS pin is low level. These interruption events can be masked by setting mask register showed in Table 8.8.3.

#### Table 8.8.1 CHG / INT pin function description

| MS pin      | Description                                                                                                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L<br>(GND)  | CHG / INT pin outputs low level when interruption event occurs (refer to Table 8.8.2). Application system can confirm interruption event factor by reading factor register after receiving that CHG / INT pin is low level. |

| H<br>(VDDB) | CHG / INT pin outputs low level when charge control circuit status is pre-charge or trickle charge or fast charge.                                                                                                          |

#### Table 8.8.2 Interruption signal output event

| Item                                   | Factor register | Description                                                                                              |

|----------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------|

| WPT communication receive notification | 0x30 D[0]       | WPT communication data is received from transmitter. The register is clear after reading.                |

| Charge state transition notification   | 0x30 D[1]       | Charge state transition. (Refer to charge state transition diagram) The register is clear after reading. |

| DCDC converter overcurrent detection   | 0x30 D[2]       | DCDC converter detects overcurrent. This register is always set by 1 in overcurrent.                     |

| VCC regulator current limit detection  | 0x30 D[3]       | VCC regulator limits output current. This register is always set by 1 in limiting current.               |

## Table 8.8.3 Interruption signal output mask register

| Item                                           | Mask register | Description                                                                       |

|------------------------------------------------|---------------|-----------------------------------------------------------------------------------|

| WPT communication receive notification         | 0x2F D[0]     | 0 : Interruption output available, 1 : Interruption output unavailable            |

| Charge state transition notification 0x2F D[1] |               | If all mask register are set by 1, CHG / INT pin function is as same as MS pin=H. |

| DCDC converter overcurrent detection           | 0x2F D[2]     |                                                                                   |

| VCC regulator current limit detection          | 0x2F D[3]     |                                                                                   |

#### 8.9 Charge Mode or Discharge Mode Notification (MODE pin)

MODE pin level depends on charge mode or discharge mode.

### Table 8.9 MODE pin function description

| MODE pin | Description                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L        | MODE pin outputs low level in charge mode 1 or 2. If MODE pin connects to DDEN pin and DDEN connects VCC or VDDB via external resistor, DCDC converter stops in charge mode (Refer to block circuit). When register 0x00 D[0] is 1, MODE pin level is always high (Open drain output is off). |

| Н        | Mode pin outputs high level in discharge mode (Open drain output is off).                                                                                                                                                                                                                     |

#### 8.10 2-wire Serial Communication Interface (MS, SCL, SDA pin)

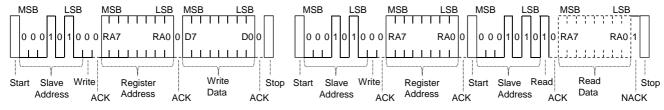

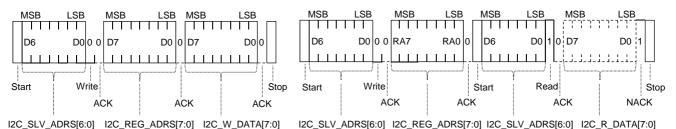

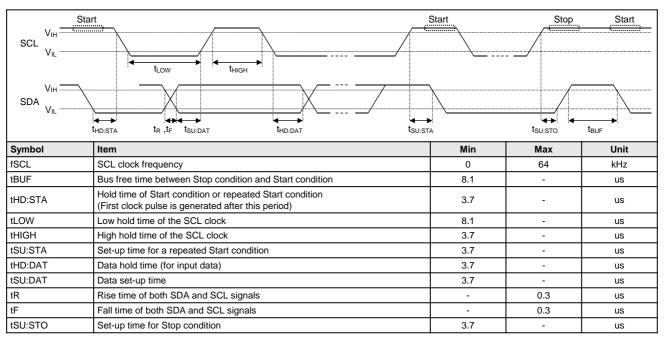

RAA457100 can communicate to application system by 2-wire serial interface. Master device or slave device can be selected by MS pin setting. Figure 8.10.1(a), (b) shows SDA data format in slave device, Figure 8.10.2(a), (b) shows SDA data format in master device. Figure 8.10.3 shows timing specification. High level input threshold voltage of SDA and SCL pins is low voltage (less than 1.0V). The communication may be affected adversely if noise voltage at pins is high. If communication error occurs, capacitor should be put between that pins and GND for filtering noise.

Table 8.10.1 2-wire serial interface outline

| MS pin      | SCL<br>frequency | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L<br>(GND)  | 64<br>[kHz]      | RAA457100 becomes slave device. The slave device address is 0x0A(0001010). Application system can read and write registers. 0x40 D[0] should be set to 1 for writing into the registers in address 0x00 to 0x0F.                                                                                                                                                                                          |

| H<br>(VDDB) | 64<br>[kHz]      | RAA457100 becomes master device. The transmitter system can write and read the register of receiver application system via WPT communication. When RAA457100 receives an access requirement (read or write register) from transmitter system to receiver application system, RAA457100 converts the access requirement to 2-wire serial interface format and communicates to receiver application system. |

Figure 8.10.1(a) SDA data format(Slave, Write)

Figure 8.10.1(b) SDA data format(Slave, Read)

Figure 8.10.2(a) SDA data format(Master, Write)

Figure 8.10.2(b) SDA data format(Master, Read)

Figure 8.10.3 2-wire serial interface SCL, SDA timing diagram (for reference)

## 8.11 WPT Communication and Rectified Output Overvoltage Protection

#### 8.11.1 **Outline**

RAA457100 and RAA458100(Transmitter IC) support a bidirectional communication by amplitude modulation on wireless power transmission carrier signal. In receiver to transmitter communication, RAA457100 changes transmitting antenna voltage by load modulation and then RAA458100 detects the voltage variation and demodulates data. In transmitter to receiver communication, RAA458100 changes rectified voltage of RAA457100 by changing transmission power and then RAA457100 detects the voltage variation and demodulates data.

#### 8.11.2 Packet Format in WPT Communication

The packet of WPT communication is consisted of fixed data length packet including Preamble, Header, Message1, Message2, Checksum showed in Figure 8.11.2. The Header, Message1, Message2 have 1 bit of odd parity bit respectively, and the check sum generated by exclusive OR is added to the last of the packet. When ATPC pin level of RAA458100 and RAA457100 is high, automatic transmission power control function is available (ATPC Mode). In ATPC Mode, the packet which includes a special header code (0x00 to 0x0F) is sent from RAA457100 to RAA458100 periodically, and RAA458100 adjusts transmission power based on the data included in packet.

| Preamble (11bit) St | Header<br>(8bit) Pr Sp | St | Message1<br>(8bit) | Pr : | Sp | St | Message2<br>(8bit) | Pr | Sp | St | Checksum<br>(8bit) | Pr | Sp |