### Application Note: SY6915 SMBus Controlled 1-4 Cell Battery Charger Controller Supporting Boost Mode

## **General Description**

The SY6915 is a high efficient, multi-cell battery charger controller supporting Boost mode. It allows the battery to discharge energy to the system when the system power demand is higher than the input capacity temporarily.

Three internal DACs are used as the reference of the charge voltage, the charge current, and the input current limit. They can be programmed by the system using SMBus.

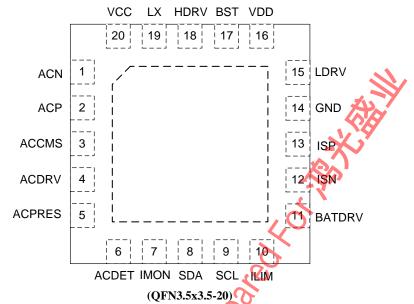

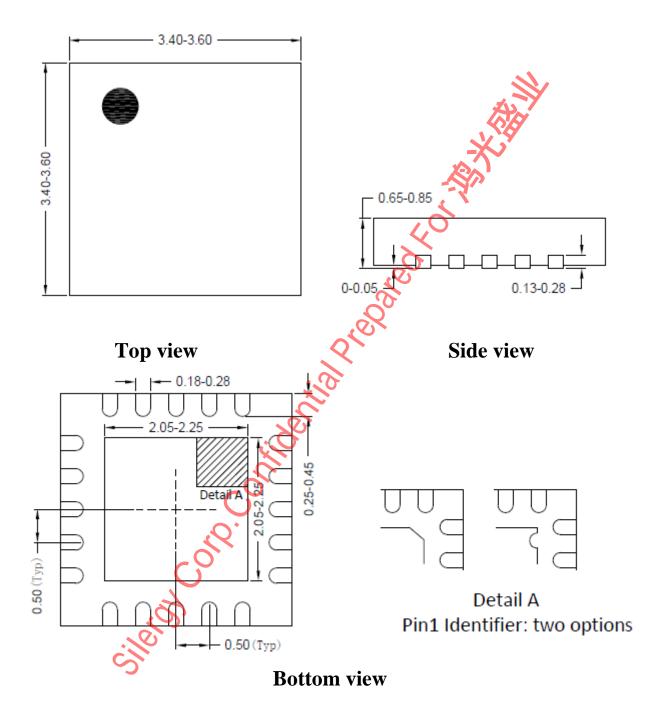

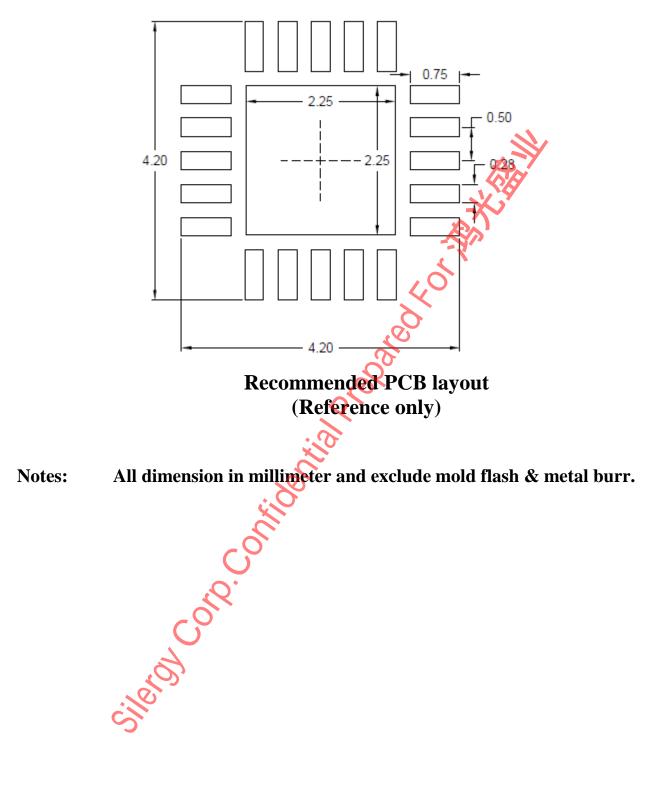

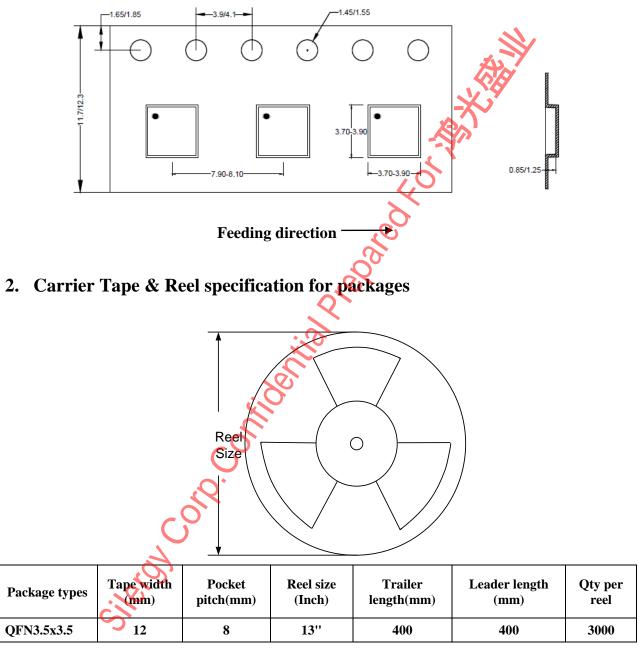

The SY6915 can charge 1, 2, 3 and 4 cells battery pack and is available in QFN3.5x3.5-20 package to allow the small PCB footprint.

## **Ordering Information**

| Ordering Number | Package type  | Note |

|-----------------|---------------|------|

| SY6915RBC       | QFN3.5x3.5-20 |      |

### Applications

- Notebook and Sub-notebook

- Battery Charger Cradle

- Portable Equipment with Rechargeable Battery

ileron

Battery Back-up Systems

### Features

- Input Voltage Range 4.5V to 25V

- SMBus Controlled Synchronous Buck Controller with 615kHz, 750kHz and 885kHz Programmable Switching Frequency

- SMBus Controls

- Battery Charge Voltage (1.024V 19.2V)

- Battery Charge Current (128mA 8.128A)

- Adapter Input Current Limit (128mA 8.064A)

- ±0.5% Battery Charge Voltage Accuracy

- ±3% Battery Charge Current Accuracy

- ±3% Adapter Input Current Limit Accuracy

- ±2% 20x Input Current or Charge Current Amplifier Output Accuracy

- Internal Charge Pumps for AC Blocking NFETs

and BAT NFET

- Integrated Loop Compensation

- Internal Soft Start

- Programmable Adapter Detection and Indicator Support Air-line Adapter

- Support 1, 2, 3 and 4 Cells Battery Pack

- Support Boost Mode

- Battery LEARN Function and Programmable Battery Depletion Threshold

- Cycle-by-cycle Peak Current Limit

- Battery Over Voltage Protection and Short Protection

- Inductor and MOSFET Short Circuit Protection

- Thermal Shutdown with Hysteresis

- 0.65mA(0.8mA Max) Adapter Standby Quiescent Current

- 5 µA Off-state Battery Discharge Current

- Package QFN 3.5x3.5-20

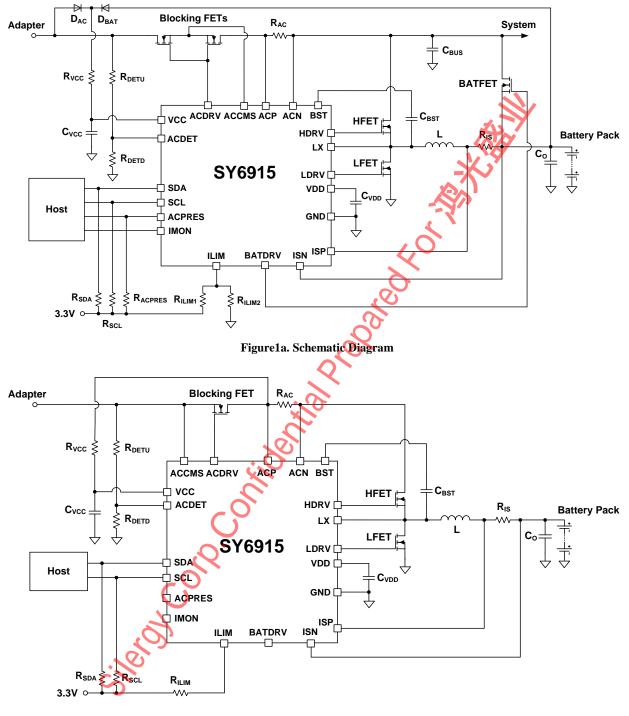

## **Typical Application**

Figure1b. Schematic Diagram

### **Pinout (top view)**

**Top Mark:** AUSxyz (device code: AUS, x=year code, y=week code, z= lot number code)

| Pin Name | Pin Number | Pin Description                                                                                                                                                                                                                                                                                                        |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACN      | 1          | Adapter current sense negative input.                                                                                                                                                                                                                                                                                  |

| ACP      | 2          | Adapter current sense positive input.                                                                                                                                                                                                                                                                                  |

| ACCMS    | 3          | Common source connection for N-channel MOSFET switches.                                                                                                                                                                                                                                                                |

| ACDRV    | 4          | N-channel blocking MOSFETs driver output.                                                                                                                                                                                                                                                                              |

| ACPRES   | 5          | AC adapter detection open-drain output. It's pulled high by an external pull-up resistor when<br>the ACDET voltage is above 1.8V and the VCC voltage is above UVLO threshold. High<br>ACPRES indicates a valid adapter (air mode or normal AC adapter) is present to start charge.                                     |

| ACDET    | 6          | Adapter detection input. Use the resistor divider from adapter output to set the detection voltage. When the ACDET voltage is above 0.6V and the VCC voltage is above UVLO threshold, the VDD will be present, ACPRES comparator and IMON will be active.                                                              |

| IMON     | 7          | Buffered input or charge current output, selectable with SMBus command. The IMON voltage is 20 times of the differential voltage across the sense resistor.                                                                                                                                                            |

| SDA      | 8          | SMBus data I/O. Open-drain output. Connect an external pull-up resistor according to the SMBus specification.                                                                                                                                                                                                          |

| SCL      | 9          | SMBus clock input. Connect an external pull-up resistor according to the SMBus specification.                                                                                                                                                                                                                          |

| ILIM     |            | Charge current limit input. Minimum of the ILIM voltage and DAC limit voltage sets charge current limit. Setting the ILIM voltage above 1.6V will disable this control. Once the voltage on ILIM pin falls below 75mV, charge will be disabled. Charge will be enabled when the voltage on ILIM pin rises above 105mV. |

| BATDRV   | 11         | Charge pump output to drive N-channel BAT MOSFET.                                                                                                                                                                                                                                                                      |

| ISN      | 12         | Battery charge current sense negative input.                                                                                                                                                                                                                                                                           |

| ISP      | 13         | Battery charge current sense positive input.                                                                                                                                                                                                                                                                           |

| GND      | 14         | IC ground.                                                                                                                                                                                                                                                                                                             |

AN\_SY6915 Rev0.9A © 2020 Silergy Corp. Silergy Corp. Confidential- Prepared for Customer Use Only 3 All Rights Reserved.

| LDRV | 15 | Low side MOSFET driver output.                                                                                                        |

|------|----|---------------------------------------------------------------------------------------------------------------------------------------|

| VDD  | 16 | LDO output for converter power MOSFETs driver. Connect a 1 µF ceramic capacitor at least to GND.                                      |

| BST  | 17 | High side power MOSFET driver power supply.                                                                                           |

| HDRV | 18 | High side MOSFET driver output.                                                                                                       |

| LX   | 19 | Inductor connecting point.                                                                                                            |

| VCC  | 20 | IC power supply input. Add a $10\Omega$ resistor and a 1 $\mu$ F capacitor to filter the inrush current and the high frequency noise. |

energy of the second se

### Absolute Maximum Ratings (Note 1)

| ACN, ACP, ACCMS, ACPRES, ISN, ISP, LX, VCC                   |

|--------------------------------------------------------------|

| ACDET, IMON, SDA, SCL, ILIM, LDRV, VDD                       |

| ACP-ACN, ISP-ISN                                             |

| ACDRV-ACCMS, BATDRV-ISN, BST-LX, BST-HDRV, HDRV-LX, VDD-LDRV |

| Package Thermal Resistance (Note 2)                          |

| QFN3.5×3.5-20, θ <sub>JA</sub> 46.8 ℃/W                      |

| QFN3.5 ×3.5-20, θ <sub>JC</sub> 56.9 ℃/W                     |

| Junction Temperature Range                                   |

| Operating Temperature Range                                  |

| Storage Temperature65 °C to 150 °C                           |

| Lead Temperature (Soldering, 10s) 300 °C                     |

### Recommended Operating Conditions (Note 3)

| ACN, ACP, ACCMS, ACPRES, ISN, ISP, LX, VCC<br>ACDRV, BATDRV, BST, HDRV<br>ACDET, IMON, SDA, SCL, ILIM, LDRV, VDD<br>ACP-ACN, ISP-ISN, | 0.3V to 5.5V<br>0.2V to 0.2V<br>40 °C to 125 °C |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| citeros                                                                                                                               |                                                 |

| sileron                                                                                                                               |                                                 |

AN\_SY6915 Rev0.9A © 2020 Silergy Corp.

## **Electrical Characteristics**

$(T_A = 25^{\circ}C, V_{VCC}=18V, V_{ISN}=12V, 10m\Omega$  sense resistor between ACP and ACN,  $10m\Omega$  sense resistor between ISP and ISN, unless otherwise noted)

| Parameter                               | Symbol                   | Test Conditions                             | Min    | Тур    | Max    | Unit |

|-----------------------------------------|--------------------------|---------------------------------------------|--------|--------|--------|------|

| Operating Condition                     |                          |                                             |        |        |        |      |

| VCC Input Voltage Range                 | V <sub>VCC_RNG</sub>     |                                             | 4.5    |        | 25     | V    |

| Regulation Range and Acc                | curacy                   |                                             | J.     | 4      |        |      |

| Charge Voltage Regulation<br>Range      | $V_{BAT\_REG\_RNG}$      | -                                           | 1.024  |        | 19.2   | V    |

|                                         |                          | Charge Voltage () = 0x4140                  | 16.716 | 16.8   | 16.884 | V    |

|                                         |                          | ChargeVoltage() = $0x41A0$                  | -0.5%  |        | 0.5%   |      |

|                                         |                          | ChargeVoltage() = $0x3130$                  | 12.529 | 12.592 | 12.655 | V    |

| Charge Voltage Regulation<br>Accuracy   | V                        | Charge voltage() = 0x3150                   | -0.5%  |        | 0.5%   |      |

|                                         | $V_{BAT\_REG\_ACC}$      | ChargeVoltage() = $0 \times 20 D0$          | 8.35   | 8.4    | 8.45   | V    |

|                                         |                          |                                             | -0.6%  |        | 0.6%   |      |

|                                         |                          | Charge Voltage() = $0 \times 1060$          | 4.163  | 4.192  | 4.221  | V    |

|                                         |                          |                                             | -0.7%  |        | 0.7%   |      |

| Charge Current<br>Regulation Range      | I <sub>CHG_REG_RNG</sub> | $V_{ISP-ISN}$ , $10m\Omega$ sense resistor  | 0      |        | 8128   | mA   |

|                                         |                          | ChargeCurrent() = 0x1000                    | 3973   | 4096   | 4219   | mA   |

|                                         |                          |                                             | -3%    |        | 3%     |      |

|                                         | $\sim$                   | ChargeCurrent() = 0x0800                    | 1946   | 2048   | 2150   | mA   |

|                                         |                          |                                             | -5%    |        | 5%     |      |

|                                         | R                        | Cl                                          | 430    | 512    | 594    | mA   |

| Charge Current Regulation               | <u> </u>                 | ChargeCurrent() = $0x0200$                  | -16%   |        | 16%    |      |

| Accuracy                                | ICHG_REG_ACC             | Charge Comment() 0=0100                     | 204.8  | 256    | 307.2  | mA   |

| , ć                                     | 2                        | ChargeCurrent() = $0x0100$                  | -20%   |        | 20%    |      |

| e e                                     |                          | ChargeCurrent() = 0x00C0                    | 147.8  | 192    | 236.2  | mA   |

|                                         |                          | ChargeCurrent() = 0x00C0                    | -23%   |        | 23%    |      |

|                                         |                          | Charge Current() = 0x0000                   | 64     | 128    | 192    | mA   |

|                                         |                          | ChargeCurrent() = 0x0080                    | -50%   |        | 50%    |      |

| Input Current Limit<br>Regulation Range | I <sub>AC_REG_RNG</sub>  | $V_{ACP-ACN}$ , 10m $\Omega$ sense resistor | 0      |        | 8064   | mA   |

|                                                 |                         | InputCurrent() = 0x1000                                                                                                       | 3973 | 4096 | 4219 | mA  |

|-------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----|

|                                                 |                         |                                                                                                                               | -3%  |      | 3%   |     |

|                                                 |                         | InputCurrent() = 0x0800                                                                                                       | 1946 | 2048 | 2150 | mA  |

| Input Current Limit                             | T                       | inputcurrent() = 0x0800                                                                                                       | -5%  |      | 5%   |     |

| Regulation Accuracy                             | I <sub>AC_REG_ACC</sub> | InputCurrent() = 0x0400                                                                                                       | 870  | 1024 | 1178 | mA  |

|                                                 |                         | $\operatorname{InputCurrent}() = 0x0400$                                                                                      | -15% |      | 15%  |     |

|                                                 |                         | InputCurrent() = 0x0200                                                                                                       | 384  | 512  | 640  | mA  |

|                                                 |                         | inputCurrent() = 0x0200                                                                                                       | -25% | 3    | 25%  |     |

| Current Sense Amplifier                         |                         |                                                                                                                               | R    |      |      |     |

| Current Sense Amplifier<br>Output Voltage Range | V <sub>IMON_RNG</sub>   | 4                                                                                                                             | 0    |      | 3.3  | V   |

| Current Sense Amplifier<br>Output Current Range | I <sub>IMON_RNG</sub>   | × ×                                                                                                                           | 0    |      | 1    | mA  |

| Current Sense Amplifier<br>Gain                 | A <sub>IMON</sub>       | V <sub>IMON</sub> /(V <sub>ISP</sub> -V <sub>ISN</sub> ) or (V <sub>ACP</sub> Y <sub>ACN</sub> )                              |      | 20   |      | V/V |

|                                                 |                         | V <sub>ACP</sub> -V <sub>ACN</sub> or V <sub>ISP</sub> -V <sub>ISN</sub> =40.96mV                                             | -2%  |      | 2%   |     |

|                                                 | V <sub>IMON_ACC</sub>   | V <sub>ACP</sub> -V <sub>ACN</sub> or V <sub>ISP</sub> -V <sub>ISN</sub> =20.48mV                                             | -4%  |      | 4%   |     |

| Current Sense Amplifier                         |                         | V <sub>ACP</sub> -V <sub>ACN</sub> or V <sub>ISP</sub> -V <sub>ISN</sub> =10.24mV                                             | -15% |      | 15%  |     |

| Gain Accuracy                                   |                         | VACP-VACN OF VISP-VISN=5.12mV                                                                                                 | -20% |      | 20%  |     |

|                                                 |                         | V <sub>ACP</sub> -V <sub>ACN</sub> or V <sub>ISP</sub> -V <sub>ISN</sub> =2.56mV                                              | -33% |      | 33%  |     |

|                                                 |                         | V <sub>ACP</sub> -V <sub>ACN</sub> or V <sub>ISP</sub> -V <sub>ISN</sub> =1.28mV                                              | -50% |      | 50%  |     |

| Buffer Capacitance Load                         | CIMON                   |                                                                                                                               | 0    |      | 100  | pF  |

| Comparator                                      |                         | <u>}</u>                                                                                                                      |      |      |      |     |

| VCC UVLO Comparator                             | V <sub>UVLO</sub>       | V <sub>VCC</sub> rising                                                                                                       | 3.5  | 3.75 | 4    | V   |

| VCC UVLO Hysteresis                             | $\Delta V_{UVLO}$       | V <sub>VCC</sub> falling                                                                                                      |      | 340  |      | mV  |

| ACPRES Rising<br>Threshold                      | VACPRES                 | V <sub>VCC</sub> >V <sub>UVLO</sub> , V <sub>ACDET</sub> rising                                                               | 1.78 | 1.80 | 1.82 | V   |

| ACPRES Falling<br>Hysteresis                    | VACPRES_HYS             | $V_{VCC} > V_{UVLO}, V_{ACDET}$ falling                                                                                       | 35   | 50   | 75   | mV  |

| ACPRES Rising Deglitch<br>Time                  | tacpres_deg             | V <sub>VCC</sub> >V <sub>UVLO</sub> , V <sub>ACDET</sub> rising above<br>2.4V, First time or ChargeOption()<br>bit [15]=0     | 110  | 160  | 210  | ms  |

|                                                 |                         | V <sub>VCC</sub> >V <sub>UVLO</sub> ,V <sub>ACDET</sub> rising above<br>2.4V, Not first time and<br>ChargeOption() bit [15]=1 | 0.9  | 1.3  | 1.7  | S   |

|                                                 |                         | V <sub>VCC</sub> >V <sub>UVLO</sub> , V <sub>ACDET</sub> rising above<br>1.8V and less than 2.4V, air mode                    | 0.6  | 1.0  | 1.7  | S   |

| WAKEUP Detect Rising                            | V <sub>WAKE_RISE</sub>  | V <sub>VCC</sub> > V <sub>UVLO</sub> , V <sub>ACDET</sub> rising                                                              |      | 0.6  | 0.8  | V   |

AN\_SY6915 Rev0.9A © 2020 Silergy Corp. Silergy Corp. Confidential- Prepared for Customer Use Only 7 All Rights Reserved.

| <u>SILEKUT</u>                                |                          |                                                                                 |               |      |      |      |                     |

|-----------------------------------------------|--------------------------|---------------------------------------------------------------------------------|---------------|------|------|------|---------------------|

| Threshold                                     |                          |                                                                                 |               |      |      |      |                     |

| WAKEUP Detect Falling<br>Threshold            | $V_{WAKE\_FALL}$         | $V_{VCC}$ > $V_{UVLO}$ , $V_{ACDET}$ fallin                                     | lg            | 0.3  | 0.5  |      | V                   |

| AC Over Voltage ACDET<br>Rising Threshold     | V <sub>ACOV</sub>        | V <sub>ACDET</sub> rising                                                       |               | 3.05 | 3.15 | 3.25 | V                   |

| AC Over Voltage ACDET<br>Falling Hysteresis   | V <sub>ACOV_HYS</sub>    | V <sub>ACDET</sub> falling                                                      |               | 50   | 75   | 100  | mV                  |

| VCC to ISN Comparator                         | V <sub>VCC_ISN</sub>     | $V_{VCC}$ - $V_{ISN}$ falling threshold                                         |               | 70   | 125  | 200  | mV                  |

| VCC to ISN Comparator<br>Hysteresis           | V <sub>VCC_ISN_HYS</sub> | $V_{VCC}$ - $V_{ISN}$ rising hysteresis                                         |               | 100  | 150  | 200  | mV                  |

| ACN to ISN Comparator                         | V <sub>ACN_ISN</sub>     | $V_{ACN}$ - $V_{ISN}$ falling threshold                                         |               | 120  | 200  | 280  | mV                  |

| ACN to ISN Comparator<br>Hysteresis           | V <sub>ACN_ISN_HYS</sub> | $V_{ACN}$ - $V_{ISN}$ rising hysteresis                                         | 0.            | 40   | 80   | 120  | mV                  |

| HFET_SC ACP to LX                             |                          | ChargeOption() bit [8] = 1                                                      | X             | 450  | 750  | 1200 |                     |

| Comparator Rising<br>Threshold                | V <sub>HFET_SC</sub>     | ChargeOption() bit [8] = 0<br>Disable function                                  |               |      |      |      | mV                  |

| LFET_SC LX to GND                             | V <sub>LFET_SC</sub>     | Buck<br>Mode                                                                    |               | 100  | 125  | 150  |                     |

|                                               |                          |                                                                                 | Boost<br>Mode | 120  | 150  | 180  | mV                  |

| Comparator Rising<br>Threshold                |                          |                                                                                 | Buck<br>Mode  | 200  | 250  | 300  | 111 V               |

|                                               |                          | ChargeOption() bit [7] = 1                                                      | Boost<br>Mode | 240  | 300  | 360  |                     |

| Cycle-by-cycle Peak                           |                          | ChargeCurrent() = 0x0xxxF                                                       | I             | 45   | 55   | 65   |                     |

| Current Limit during Buck<br>Mode, ISP to ISN | V <sub>PK_CHARGE</sub>   | ChargeCurrent() = 0x1000H–<br>0x17C0H                                           |               | 70   | 85   | 100  | mV                  |

| Comparator Rising<br>Threshold                | .Q.                      | ChargeCurrent() = 0x1800H–<br>0x1FC0H                                           |               | 90   | 105  | 120  |                     |

| Fast DPM Comparator<br>Threshold              | IDPM                     | Stop charging and enter Bo<br>mode threshold with respec<br>input current limit |               | 103% | 107% | 111% | I <sub>AC_REG</sub> |

| ACOC Comparator Rising<br>Threshold           | PACOC                    | ChargeOption() bit [1] = 1                                                      |               | 300% | 333% | 366% | I <sub>AC_REG</sub> |

| Min ACOC Clamped<br>Threshold                 | I <sub>ACOC_MIN</sub>    | $I_{ACOC}$ =333% × $I_{AC_REG}$                                                 |               | 4    | 4.5  | 5    | А                   |

| Max ACOC Clamped<br>Threshold                 | I <sub>ACOC_MAX</sub>    | $I_{ACOC}=333\% \times I_{AC\_REG}$                                             |               | 13.5 | 15   | 16.5 | А                   |

| ACOC Deglitch Time                            | t <sub>ACOC_DEG</sub>    | Voltage across input sense r<br>rising to disable charge                        | resistor      | 2.3  | 4.2  | 6.6  | ms                  |

| BAT OV Rising Threshold                       | V <sub>BATOV_RISE</sub>  | V <sub>ISN</sub> rising                                                         |               | 103% | 104% | 106% | $V_{BAT\_REG}$      |

AN\_SY6915 Rev0.9A © 2020 Silergy Corp. Silergy Corp. Confidential- Prepared for Customer Use Only 8 All Rights Reserved.

|                                               |                         | · · · · · · · · · · · · · · · · · · ·         |        |        |       |                      |

|-----------------------------------------------|-------------------------|-----------------------------------------------|--------|--------|-------|----------------------|

| BAT OV Falling<br>Threshold                   | VBATOV_FALL             | V <sub>ISN</sub> falling                      |        | 102%   |       | V <sub>BAT_REG</sub> |

|                                               |                         | ChargeOption() bit [12:11] = 00               | 55.53% | 59.19% | 63.5% |                      |

| Battery Depletion ISN                         | V                       | ChargeOption() bit [12:11] = 01               | 58.68% | 62.65% | 67.5% | V                    |

| Falling Threshold                             | VBATDEP                 | ChargeOption() bit [12:11] = 10               | 62.17% | 66.55% | 71.5% | V <sub>BAT_REG</sub> |

|                                               |                         | ChargeOption() bit [12:11] = 11               | 66.06% | 70.97% | 77%   |                      |

|                                               |                         | ChargeOption() bit [12:11] = 00               | 225    | 305    | 400   |                      |

| Battery Depletion ISN                         | V                       | ChargeOption() bit [12:11] = 01               | 240    | 325    | 430   | mV                   |

| Rising Hysteresis                             | V <sub>BATDEP_HYS</sub> | ChargeOption() bit [12:11] = 10               | 255    | 345    | 450   | III V                |

|                                               |                         | ChargeOption() bit [12:11] = 11               | 280    | 370    | 490   |                      |

| Battery Depletion ISN<br>Rising Deglitch Time | t <sub>BATDEP_DEG</sub> |                                               | N.     | 600    |       | ms                   |

| BAT UV Falling<br>Threshold                   | VBATUV                  | V <sub>ISN</sub> falling                      | 2.4    | 2.5    | 2.6   | v                    |

| BAT UV Rising Hysteresis                      | $V_{BATUV\_HYS}$        | V <sub>ISN</sub> rising                       |        | 200    |       | mV                   |

| ILIM Falling Threshold to Disable Charge      | V <sub>ILIM_DIS</sub>   | VILIM falling                                 | 60     | 75     | 90    | mV                   |

| ILIM Rising Threshold To<br>Enable Charge     | V <sub>ILIM_EN</sub>    | VILIM rising                                  | 90     | 105    | 120   | mV                   |

| Thermal Shutdown Rising<br>Threshold          | T <sub>SD</sub>         | Temperature rising                            |        | 150    |       | °C                   |

| Thermal Shutdown Falling<br>Hysteresis        | T <sub>SD_HYS</sub>     | Temperature falling                           |        | 20     |       | °C                   |

| Driver Capability                             |                         |                                               |        |        |       |                      |

| VDD LDO Voltage                               | V <sub>VDD</sub>        | Vvcc>6V,V <sub>ACDET</sub> >0.6V              | 5      | 5.5    | 6     | V                    |

| VDD Current Capacity                          | I <sub>VDD</sub>        | V <sub>VCC</sub> >6V,V <sub>ACDET</sub> >0.6V | 55     |        |       | mA                   |

| High Side Driver Turn-on<br>Resistance        | R <sub>H_ON</sub>       | V V SOV                                       |        | 3      |       | Ω                    |

| High Side Driver Turn-off<br>Resistance       | RH_OFF                  | $V_{BST}-V_{LX}=5.2V$                         |        | 0.5    |       | Ω                    |

| Low Side Driver Turn-on<br>Resistance         | RL_ON                   | N 55N                                         |        | 4      |       | Ω                    |

| Low Side Driver Turn-off<br>Resistance        | R <sub>L_OFF</sub>      | V <sub>VDD</sub> =5.5V                        |        | 0.5    |       | Ω                    |

| Dead Time from HDRV<br>Low to LDRV High       | t <sub>DEAD_LD</sub>    |                                               |        | 20     |       | ns                   |

| Dead Time from LDRV<br>Low to HDRV High       | t <sub>DEAD_HD</sub>    |                                               |        | 20     |       | ns                   |

| ACDRV Driver Voltage                          | VACPUMP                 | $V_{ACDRV}$ - $V_{ACCMS}$ when $V_{VCC}$ >6V  |        | 6      |       | V                    |

| ACDRV Driver Source<br>Current                | IACDRV_SOURCE           |                                               | 50     | 80     |       | μΑ                   |

AN\_SY6915 Rev0.9A © 2020 Silergy Corp. Silergy Corp. Confidential- Prepared for Customer Use Only 9 All Rights Reserved.

| 5/12/10/                                |                            |                                                                                                                     |      |      |      |     |

|-----------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-----|

| ACDRV Driver Sink<br>Current            | IACDRV_SINK                |                                                                                                                     | 1.75 |      |      | mA  |

| BATDRV Driver Voltage                   | VBATPUMP                   | V <sub>BATDRV</sub> -V <sub>ISN</sub> when V <sub>VCC</sub> >6V                                                     |      | 6    |      | V   |

| BATDRV Driver Source<br>Current         | I <sub>BATDRV_SOURCE</sub> |                                                                                                                     | 40   | 60   |      | μΑ  |

| BATDRV Driver Sink<br>Current           | IBATDRV_SINK               |                                                                                                                     |      | 1    |      | mA  |

| PWM Oscillator                          |                            |                                                                                                                     |      |      |      |     |

| PWM Switching<br>Frequency              | F <sub>SW</sub>            | ChargeOption() bit [9] = 0<br>(Default)                                                                             | 600  | 750  | 900  | kHz |

| PWM Increase Frequency                  | $F_{SW^+}$                 | ChargeOption() bit [10:9] = 11                                                                                      | 665  | 885  | 1100 | kHz |

| PWM Decrease Frequency                  | F <sub>SW-</sub>           | ChargeOption() bit [10:9] = 01                                                                                      | 465  | 615  | 765  | kHz |

| Logic I/O                               |                            | ~                                                                                                                   |      |      |      |     |

| SCL/SDA Input Low<br>Threshold          | V <sub>IN_LO</sub>         | 2<br>Z                                                                                                              |      |      | 0.8  | V   |

| SCL/SDA Input High<br>Threshold         | V <sub>IN_HI</sub>         | No.                                                                                                                 | 2.1  |      |      | V   |

| SDA/ACPRES Output<br>Saturation Voltage | V <sub>OUT_LO</sub>        | 5mA drain current                                                                                                   |      |      | 0.5  | V   |

| SDA/ACPRES Leakage<br>Current           | I <sub>OUT_LEAK</sub>      | V=7V                                                                                                                | -1   |      | 1    | μΑ  |

| Time                                    |                            |                                                                                                                     |      |      |      |     |

| Soft Start Current Step                 | I <sub>STEP</sub>          | 2                                                                                                                   |      | 64   |      | mA  |

| Soft Start Current Step<br>Time         | t <sub>STEP</sub>          | 10m current sensing resistor                                                                                        |      | 240  |      | μs  |

| Quiescent Current                       | ć                          | <b>C</b>                                                                                                            |      |      |      |     |

| Battery Current when<br>BATFET OFF      | IBAT_BATFET_OFF            | V <sub>ISN</sub> =16.8V, VCC disconnect from<br>battery, BATFET charge pump off,<br>BATFET turns off                |      |      | 5    | μΑ  |

| Battery Current when<br>BATFET ON       | IBAT_BATFET_ON             | V <sub>ISN</sub> =16.8V, VCC connect from<br>battery, BATFET charge pump on,<br>BATFET turns on                     |      |      | 25   | μΑ  |

| Standby Quiescent Current               | Istandby                   | Adapter present, $V_{VCC}$ > $V_{UVLO}$ , $V_{ACDET}$ >0.6V, charge disabled                                        |      | 0.65 | 0.8  | mA  |

| Adapter Current when No<br>Switching    | I <sub>AC_NOSW</sub>       | Adapter present, $V_{VCC}$ > $V_{UVLO}$ ,<br>2.4 $V$ < $V_{ACDET}$ <3.15 $V$ , charge<br>enabled, no switching      |      | 1.5  | 3    | mA  |

| Adapter Current when<br>Switching       | I <sub>AC_SW</sub>         | Adapter present, $V_{VCC}>V_{UVLO}$ ,<br>2.4V< $V_{ACDET}$ <3.15V, charge<br>enabled, switching, MOSFET<br>SiS412DN |      | 10   |      | mA  |

Note 1: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25 \text{ C}$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

Note 3: The device is not guaranteed to function outside its operating conditions.

AN\_SY6915 Rev0.9A © 2020 Silergy Corp.

### **SMBus Timing Specifications**

| Parameter                                                                  | Symbol                  | Test Conditions                 | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------|-------------------------|---------------------------------|-----|-----|-----|------|

| SMBus Frequency                                                            | F <sub>S(CLK)</sub>     |                                 | 10  |     | 100 | kHz  |

| SCL/SDA Rise Time                                                          | t <sub>RISE</sub>       |                                 |     |     | 1   | μs   |

| SCL/SDA Fall Time                                                          | t <sub>FALL</sub>       |                                 |     |     | 300 | ns   |

| SCL Pulse Width High                                                       | t <sub>W(HIGH)</sub>    |                                 | 4   |     | 50  | μs   |

| SCL Pulse Width Low                                                        | t <sub>W(LOW)</sub>     |                                 | 4.7 |     |     | μs   |

| Setup Time for START<br>Condition                                          | t <sub>SET(START)</sub> |                                 | 4,7 |     |     | μs   |

| START Condition Hold Time<br>after which First Clock Pulse is<br>Generated | thold(start)            |                                 | 4   |     |     | μs   |

| Data Setup Time                                                            | t <sub>SET(DAT)</sub>   | ر٥                              | 250 |     |     | ns   |

| Data Hold Time                                                             | t <sub>HOLD(DAT)</sub>  | ~                               | 300 |     |     | ns   |

| Setup Time for STOP Condition                                              | t <sub>SET(STOP)</sub>  | S<br>S                          | 4   |     |     | us   |

| Bus Free Time between START<br>and STOP Condition                          | t <sub>FREE(BUS)</sub>  | 03                              | 4.7 |     |     | us   |

| SMBus Bus Release Timeout                                                  | t <sub>TIMEOUT</sub>    |                                 |     | 30  |     | ms   |

| Deglitch for Watchdog Reset<br>Signal                                      | t <sub>boot</sub>       | 31                              | 10  |     |     | ms   |

|                                                                            |                         | ChargeOption() bit [14:13] = 11 | 140 | 175 | 210 | s    |

| Watchdog Timeout Period                                                    | t <sub>WATCHDOG</sub>   | ChargeOption() bit [14:13] = 10 | 70  | 88  | 105 | S    |

|                                                                            | Ç                       | ChargeOption() bit [14:13] = 01 | 35  | 44  | 53  | S    |

cileron cont

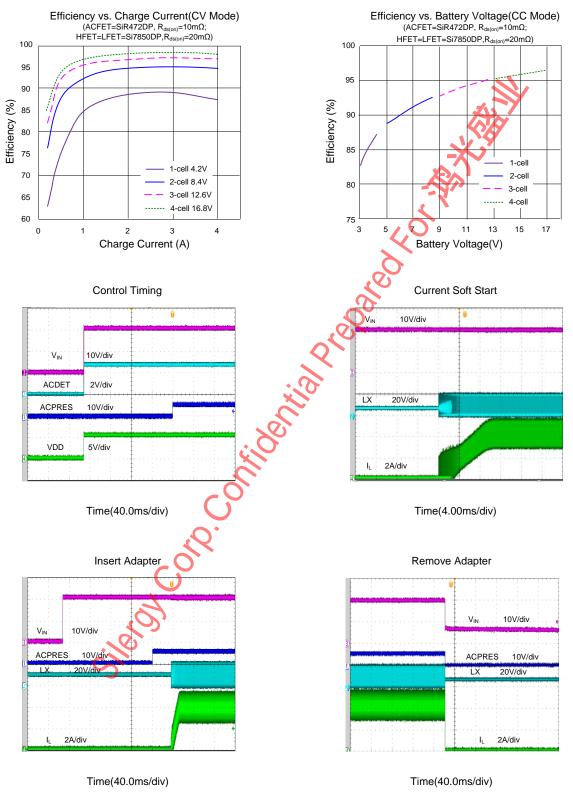

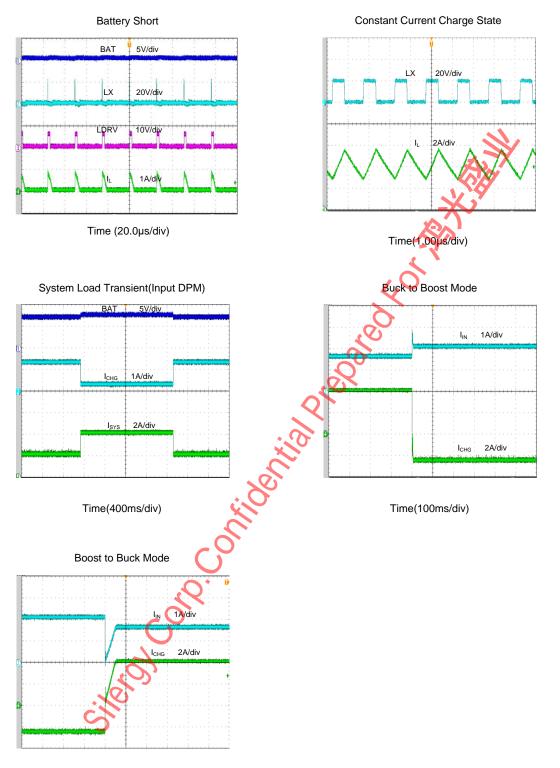

## **Typical Performance Characteristics**

T<sub>A</sub>=25 °C, V<sub>IN</sub>=19V, I<sub>CHG</sub>=4A, 2cell battery, L=4.7µH, unless otherwise specified.

Silergy Corp. Confidential- Prepared for Customer Use Only All Rights Reserved.

13

Time(20ms/div)

### **General Function Description**

The SY6915 is a high efficient, multi-cell battery charger controller supporting Boost mode. It allows the battery to discharge energy to the system when the system power demand is higher than the input capacity temporarily.

Three internal DACs are used as the reference of the charge voltage, the charge current, and the adapter input current limit. They can be programmed by system using SMBus.

#### Adapter Detect and Power up (ACPRES)

Pin ACDET detects the input voltage from the adapter or other DC source. The divider resistors should program the input voltage higher than the maximum battery voltage and lower than the maximum allowed adapter voltage.

ACPRES can be pulled to the external rail by the pull-up resistor after ACPRES deglitch time under the following conditions:

- V<sub>VCC</sub>>V<sub>UVLO</sub>, ensure the control circuits operate well;

- V<sub>ACDET</sub>>1.8V, the input voltage is within operation range;

The ACPRES rising deglitch time is 160ms for the first time after POR no matter what the charge option register value is. After one time the voltage on ACDET pin drops below 1.8V but above 0.6V the next ACPRES rising deglitch time will be forced to 1.3s.

#### <u>Battery Charge Voltage, Battery Charge Current,</u> and Adapter Input Current Limit Regulation

The battery charge voltage regulation is set by an 11bit DAC register, programmed by the host microcontroller through the SMBus interface.

The battery charge current regulation is set by a 7-bit DAC register. It is sensed by a resistor connected between the ISP and ISN pins. For a  $10m\Omega$  sense resistor, the maximum current is 8.128A. A larger resistor gives lower maximum current and higher regulation accuracy

The adapter input current limit is set by a 6-bit DAC register, sensed by the resistor between the ACP and ACN pins. For a  $10m\Omega$  sense resistor, the maximum current is 8.064A. A high accuracy amplifier provides an analog output voltage of 20x ACP-ACN at the IMON pin that can be used by the host system to monitor the adapter input current. If the adapter

current rises to the limit, the battery charge current will be reduced so that the charger will not reduce the current available to the system.

#### Dynamic Power Management (DPM, ACOC)

When the input current rises to adapter input current limit due to system load, the charge current will be decreased by the input current limit loop. It can prevent adapter overload.

The ACOC function can be enabled by charge option register. If the input current has increased to the ACOC set point for 4.2ms (t<sub>ACOC\_DEG</sub>), ACFETs will latch off. The latch status can't be cleared until adapter is removed.

#### **Boost Mode**

The SY6915 supports Boost mode. The system draws the battery power through Boost converter when the adapter is fully loaded. During Boost mode, battery energy is delivered to system when system power demand is temporarily higher than adapter maximum power level so that adapter will not overload. After POR, the charge option register bit[3] is 0 which disable Boost mode. To enable it, the charge option register bit[3] must be written to 1 by the host.

When input current is higher than the FAST\_DPM comparator threshold, if Boost mode is enabled, the IC will allow battery to discharge and the converter will change from Buck to Boost. During Boost mode the adapter current is regulated at input current limit level so that adapter will not overload. The battery discharge current depends on system current requirement and adapter input current limit register setting value. The SMBus timer can be enabled to prevent converter running at Boost mode for too long time.

#### Cycle-by-cycle Peak Current Limit

The SY6915 uses cycle-by-cycle peak current limit mode to prevent the switch from over current. The IC senses the voltage drop of resistor or switch as the current information. The peak current limit values of Buck and Boost are different.

#### MOSFET Short Circuit Protection (HFET\_SC, LFET\_SC)

When the MOSFET or inductor is shorten, the high voltage drop across the  $R_{DS(ON)}$  will trigger the HFET\_SC or LFET\_SC. When the counter receives the short circuit signal over 7 times within 90s, the IC will latch off the converter. Recycle the AC input will release the latch off status.

AN\_SY6915 Rev0.9A © 2020 Silergy Corp. Silergy Corp. Confidential- Prepared for Customer Use Only 15 All Rights Reserved.

#### **Battery Over Voltage Protection (BATOV)**

The converter will not switch when battery voltage exceeds 104% of the regulation voltage set point. Switching resumes when it is below 102%.

#### **Battery Short Protection (BATUV)**

A comparator monitors output battery voltage. If the voltage falls below 2.5V ( $V_{BATUV}$ ), the battery short status will be detected. The peak current will be clamped to a low value and the IC will decrease the switching frequency. The charge current will return to the set point when the battery voltage rises above 2.7V ( $V_{BATUV}+V_{BATUV}+W_{S}$ ).

#### **Thermal Shutdown Protection (T<sub>SD</sub>)**

When the junction temperature exceeds 150°C, the IC will shut down. Once the temperature drops below 130°C, switching will resume.

#### **Charge Timeout**

A timer will terminate charging if the charger does not receive a charge voltage or charge current command within 175s. If a timeout occurs, either charge voltage or charge current command must be sent to reenable charging.

#### **Battery LEARN**

A Battery LEARN cycle can be activated via SMBus command in the SY6915. Battery LEARN mode allows the battery to discharge in order to calibrate the battery gas gauge over a complete discharge/charge cycle. When entering into battery LEARN mode, the IC will turn off the converter and ACFETs first, and then will turn on BATFET to support the discharge mode. When exiting battery LEARN mode, the IC will recovery to normal mode if all conditions are ready.

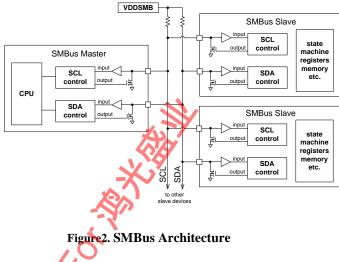

#### **SMBus Interface**

#### The System Management Bus

The System Management Bus (SMBus) is a 2 wire BUS that supports bidirectional communications. The protocol is described briefly here. More detail is available from www.smbus.org.

#### **General SMBus Architecture**

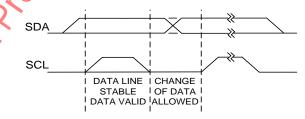

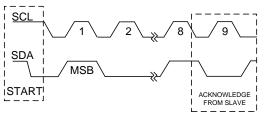

#### Data Validity

The data on the SDA line must be stable during the HIGH period of the SCL, unless generating a START or STOP condition. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. Refer to Figure 3.

#### Figure3. Data Validity

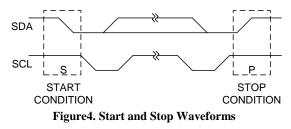

#### **START and STOP Conditions**

As shown in Figure4, START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH. A STOP condition must be sent before each START condition.

#### **Acknowledge**

Each address and data transmission uses 9 clock

AN\_SY6915 Rev0.9A © 2020 Silergy Corp. Silergy Corp. Confidential- Prepared for Customer Use Only 16 All Rights Reserved.

pulses. The ninth pulse is the acknowledge bit (ACK). After the START condition, the master sends 7 slave address bits and a R/W bit during the next 8 clock pulses. During the ninth clock pulse, the device that recognizes its own address holds the data line low to acknowledge. The acknowledge bit is also used by both the master and the slave to acknowledge receipt of register addresses and data as described below.

Figure 5. Acknowledge On the SMBus

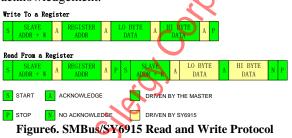

#### **SMBus Transactions**

All transactions start with a control byte sent from the SMBus master device. The control byte begins with a START condition, followed by 7-bits of slave address (0001001 for the SY6915) followed by the R/W bit. The R/W bit is 0 for a write or 1 for a read. If any slave devices on the SMBus recognize their address, they will acknowledge by pulling the serial data (SDA) line low for the last clock cycle in the control byte. If no slaves exist at that address or are not ready to communicate, the data line will be 1, indicating a not acknowledge condition. Once the control byte is sent, and the SY6915 acknowledgesit, the 2nd byte sent by the master must be a register address byte such as 0x14 for the charge current register. The register address byte tells the SY6915 which register the master will write or read. See Table 1 for details of the registers. Once the SY6915 receives a register address byte it responds with acknowledgement.

#### **Byte Format**

Every byte put on the SDA line must be eight bits long and must be followed by an acknowledge bit. Data is transferred with the most significant bit first (MSB) and the least significant bit last (LSB).

#### SY6915 and SMBus

The SY6915 receives control inputs from the SMBus interface. The serial interface complies with the SMBus protocols as documented in the system management BUS specification V1.1, which can be downloaded from www.smbus.org. The SY6915 uses the SMBus Read-Word and Write-Word protocols (Figure 6) to communicate with the smart battery. The SY6915 is a SMBus slave device and does not initiate communication on the bus. It responds to the 7-bit address 0b0001001X. Read address = 0b00010011 and Write address = 0b00010010.

In addition, the SY6915 has two identification (ID) registers: a 16-bit device ID register and a 16-bit manufacturer ID register.

The data (SDA) and clock (SCL) pins have schmitttrigger inputs that can accommodate slow edges. Choose pull-up resistors for SDA and SCL to achieve rise times according to the SMBus specifications. The SY6915 is controlled by the data written to the registers described in Table 1.

SMBus communication is enabled with the following conditions:

- V<sub>VCC</sub> is above V<sub>UVLO</sub> ;

- V<sub>ACDET</sub> is above 0.6V.

#### **Battery Charger Registers**

The SY6915 supports four battery charger registers that use either write-word or read-word protocols, as summarized in Table 1. Manufacturer ID and Device ID are "read only" registers and can be used for identifying SY6915. On SY6915, Manufacturer ID always returns 0x0053 (ASCII code for "SI" for Silergy) and Device ID always returns 0x0002.

AN\_SY6915 Rev0.9A © 2020 Silergy Corp.

| Register<br>Address | Register Name   | Read/Write    | Description                       | POR State |

|---------------------|-----------------|---------------|-----------------------------------|-----------|

| 0x12                | ChargeOption()  | Read or Write | 16-Bit Charge Option Control      | 0xF902    |

| 0x14                | ChargeCurrent() | Read or Write | 7-Bit Charge Current Setting      | 0x0000    |

| 0x15                | ChargeVoltage() | Read or Write | 11-Bit Charge Voltage Setting     | 0x0000    |

| 0x3F                | InputCurrent()  | Read or Write | 6-Bit Input Current Limit Setting | 0x1000    |

| 0xFE                | ManufactureID() | Read Only     | Manufacture ID                    | 0x0053    |

| 0xFF                | DeviceID()      | Read Only     | Device ID                         | 0x0002    |

#### Table1. Battery Charger Register Summary

#### **Enabling and Disabling Charge**

After applying power to the SY6915, the internal registers contain their POR values (see Table 1). The POR values for charge current and charge voltage are 0x0000. These values disable charge. To enable charge, the charge current register must be written with a number larger than 0x007F and the charge voltage register must be written with a number larger

than 0x03FF. Charge can be disabled by writing 0x0000 to either of the two registers.

### Charge Option Control

Charge option is set by writing a valid 16-bit number to the charge option register.

| D:4 | Bit     Bit Name     Description       |                                                                                                                                                                                                                                               |  |

|-----|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DIL | Dit Name                               | Description                                                                                                                                                                                                                                   |  |

| 0   | Charge Inhibit                         | 0: Enable Charge (POR default)<br>1: Inhibit Charge                                                                                                                                                                                           |  |

| 1   | ACOC Threshold Adjust                  | Set this bit 1 to limit the Input current when it is out of regulation.<br>The maximum input current limit is 15A typical with10mΩ sense<br>resistor.<br>0: Function is disabled<br>1: 3.33 x of input current regulation limit (POR default) |  |

| 2   | Boost Mode Indication<br>(Read Only)   | 0: Not in Boost mode (POR default)<br>1: In Boost mode.                                                                                                                                                                                       |  |

| 3   | Boost Mode Enable                      | 0: Disable Boost mode (POR default)<br>1: Enable Boost mode                                                                                                                                                                                   |  |

| 4   | AC Adapter Indication<br>(Read Only)   | 0: AC adapter is not present (V <sub>ACDET</sub> <2.4V) (POR default)<br>1: AC adapter is present (V <sub>ACDET</sub> >2.4V)                                                                                                                  |  |

| 5   | IMON Selection                         | <ul><li>0: IMON is the 20x input current amplifier output (POR default)</li><li>1: IMON is the 20x charge current amplifier output</li></ul>                                                                                                  |  |

| 6   | Battery LEARN Enable                   | 0: Disable LEARN (POR default)<br>1: Enable LEARN                                                                                                                                                                                             |  |

| 7   | LFET_SC Comparator Threshold<br>Adjust | Short circuit protection low side MOSFET voltage drop comparator<br>threshold. This is also used for cycle-by-cycle current limit<br>protection threshold during Boost mode.<br>0: 125mV (POR default)<br>1: 250mV                            |  |

#### Table2. Charge Option (Register 0x12)

AN\_SY6915 Rev0.9A © 2020 Silergy Corp.

| Bit   | Bit Name                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8     | HFET_SC Comparator Threshold<br>Adjust               | <ul><li>Short circuit protection high side MOSFET voltage drop comparator threshold.</li><li>0: Function is disabled.</li><li>1: 750mV (POR default).</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9     | EMI Switching Frequency Enable                       | <ul><li>0: Disable adjust PWM switching frequency (POR default).</li><li>1: Enable adjust PWM switching frequency</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10    | EMI Switching Frequency Adjust                       | Default frequency:750kHz<br>0: Reduce PWM switching frequency by 18% (POR default).<br>1: Increase PWM switching frequency by 18%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11    | BAT Depletion Comparator<br>Threshold Adjust [12:11] | See bit [12].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12    | BAT Depletion Comparator<br>Threshold Adjust [12:11] | Bit [12:11] is used for LEARN function and battery over discharge<br>protection during Boost mode. During LEARN cycle, when IC<br>detects battery voltage is below depletion voltage threshold, the IC<br>will turn off BATFET and turn on blocking FETs to power the<br>system from AC adapter instead of the battery. During Boost mode,<br>when the IC detects battery voltage is below depletion voltage<br>threshold, the IC will stop Boost mode. Set charge voltage register<br>value to 0V will disable this function.<br>00: Falling Threshold = 59.19% of voltage regulation limit<br>(~2.486V/cell)<br>01: Falling Threshold = 62.65% of voltage regulation limit<br>(~2.631V/cell)<br>10: Falling Threshold = 66.55% of voltage regulation limit<br>(~2.795V/cell)<br>11: Falling Threshold = 70.97% of voltage regulation limit<br>(~2.981V/cell) (POR default) |

| 14:13 | WATCHDOG Timer Adjust                                | Set maximum delay between consecutive SMBus Write charge<br>voltage or charge current command. The charge will be suspended if<br>the IC does not receive write charge voltage or write charge current<br>command within the watchdog time period and watchdog timer is<br>enabled.<br>The charge will be resumed after receive write charge voltage or<br>write charge current command when watchdog timer expires and<br>charge suspends. During Boost mode, the timer is fixed to 175s if it<br>is enabled.<br>00: Disable Watchdog Timer.<br>01: Enabled, 44 s.<br>10: Enabled, 88 s.<br>11: Enable Watchdog Timer (175s) (POR default).                                                                                                                                                                                                                                 |

| 15    | ACPRES Deglitch Time Adjust                          | Adjust ACPRES rising edge deglitch time. After POR, the first time<br>the adapter plug in occurs, the deglitch time is always 160ms no<br>matter if this bit is 0 or 1. This bit only sets the next ACPRES<br>deglitch time after ACFET turns off at least one time. To change<br>this option, the VCC voltage must above UVLO threshold and the<br>ACDET voltage must above 0.6V to enable the IC SMBus<br>communication.<br>0: ACPRES rising edge deglitch time is 160ms.<br>1: ACPRES rising edge deglitch time is 1.3s (POR default).                                                                                                                                                                                                                                                                                                                                    |

#### Setting Charge Voltage

Charge voltage is set by writing a valid 16-bit number to the charge voltage register. This 16-bit number translates to a 65.535V full-scale voltage. The SY6915 ignores the first 4 LSBs and uses the next 11 bits to set the voltage DAC. The charge voltage range of the SY6915 is 1.024V to 19.200V. All numbers requesting charge voltage below 1.024V or above 19.2V result in a voltage set point of zero, which terminates charging.

Upon initial power up or reset, the charge voltage and charge current registers are reset to 0 and the charger remains shut down until valid numbers are sent to the charge voltage and charge current registers. Use the Write-word protocol to write to the charge voltage register. The register address for charge voltage is 0x15. The 16-bit binary number formed by D15–D0 represents the charge voltage set point in mV. However, the resolution of the SY6915 is 16mV because the D0–D3 bits are ignored as shown in Table 3. The D15 bit is also ignored because it is not needed to span the 1.024V to 19.2V range. Table 3 shows the mapping between the charge voltage set point and the 16-bit number written to the charge voltage register. The charge voltage register can be read back to verify its contents.

| Bit | Bit Name                | Description                                                                         |

|-----|-------------------------|-------------------------------------------------------------------------------------|

| 0   |                         | Not used.                                                                           |

| 1   |                         | Not used.                                                                           |

| 2   |                         | Not used.                                                                           |

| 3   |                         | Not used.                                                                           |

| 4   | Charge Voltage, DACV 0  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 16mV of charge voltage.                 |

| 5   | Charge Voltage, DACV 1  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 32mV of charge voltage.                 |

| 6   | Charge Voltage, DACV 2  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 64mV of charge voltage.                 |

| 7   | Charge Voltage, DACV 3  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 128mV of charge voltage.                |

| 8   | Charge Voltage, DACV 4  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 256mV of charge voltage.                |

| 9   | Charge Voltage, DACV 5  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 512mV of charge voltage.                |

| 10  | Charge Voltage, DACV 6  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 1024mV of charge voltage.               |

| 11  | Charge Voltage, DACV 7  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 2048mV of charge voltage.               |

| 12  | Charge Voltage, DACV 8  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 4096mV of charge voltage.               |

| 13  | Charge Voltage, DACV 9  | 0 = Adds 0mV of charge voltage.<br>1 = Adds 8192mV of charge voltage.               |

| 14  | Charge Voltage, DACV 10 | 0 = Adds 0mV of charge voltage.<br>1 = Adds 16384mV of charge voltage, 19200mV max. |

| 15  |                         | Not used.                                                                           |

| Table3. | Charge | Voltage | (Register  | <b>0x15</b> ) |

|---------|--------|---------|------------|---------------|

| I asiee | Charge | , onege | (Itegister | UMIC)         |

#### Setting Charge Current

SY6915 has a 16-bit charge current register that sets the battery charge current. SY6915 controls the charge current by controlling the ISP-ISN voltage. The SY6915 ignores the first 6 LSBs and uses the next 7 bits to control the current DAC. The chargecurrent range of the SY6915 is 128mA to 8.128A (using a  $10m\Omega$  current-sense resistor). All numbers requesting charge current below 128mA or above 8.128A result in a current setting of 0mA and charging termination.

The default charge current setting at power on Reset (POR) is 0mA. To stop charging, set charge current to 0. Upon initial power up, the charge voltage and

charge current registers are reset to 0 and the charger is disabled. To start the charger, write valid numbers to the charge voltage and charge current registers. The charge current register uses the Write-word protocol. The register code for charge current is 0x14 (0b00010100). Table 4 shows the mapping between the charge current set point and the 16-bit number written to the charge current register. The charge current register can be read back to verify its contents.

The ILIM voltage also can limit the battery charge current. The limited charge current is given by the equation  $I_{CHG}=V_{ILIM}/(20xR_{1S})$  in Buck mode. The lower of the current set by ILIM and DAC is selected for internal charge current limit.

| Bit | Bit Name                  | Description                                                                           |

|-----|---------------------------|---------------------------------------------------------------------------------------|

| 0   |                           | Not used.                                                                             |

| 1   |                           | Not used.                                                                             |

| 2   |                           | Not used.                                                                             |

| 3   |                           | Not used,                                                                             |

| 4   |                           | Not used.                                                                             |

| 5   |                           | Not used.                                                                             |

| 6   | Charge Current, DACICHG 0 | <ul> <li>Adds 0mA of charge current.</li> <li>Adds 64mA of charge current.</li> </ul> |

| 7   | Charge Current, DACICHG 1 | 0 = Adds 0mA of charge current.<br>1 = Adds 128mA of charge current.                  |

| 8   | Charge Current, DACICHG 2 | 0 = Adds 0mA of charge current.<br>1 = Adds 256mA of charge current.                  |

| 9   | Charge Current, DACICHG 3 | 0 = Adds 0mA of charge current.<br>1 = Adds 512mA of charge current.                  |

| 10  | Charge Current, DACICHG 4 | 0 = Adds 0mA of charge current.<br>1 = Adds 1024mA of charge current.                 |

| 11  | Charge Current, DACICHG 5 | 0 = Adds 0mA of charge current.<br>1 = Adds 2048mA of charge current.                 |

| 12  | Charge Current, DACICHG 6 | 0 = Adds 0mA of charge current.<br>1 = Adds 4096mA of charge current, 8128mA max.     |

| 13  |                           | Not used.                                                                             |

| 14  | S                         | Not used.                                                                             |

| 15  |                           | Not used.                                                                             |

#### Table4. Charge Current (Register 0x14) (10mΩ Sense Resistor)

#### **Setting Input Current Limit**

The total power from an adapter is the sum of the power supplied to the system and the power into the charger and battery. When the input current exceeds the set input current limit, the SY6915 will decrease the charge current to provide priority to system load current. As the system load rises, the available charge current drops linearly to zero. Thereafter, all input current goes to system load and input current increases.

The internal amplifier compares the differential voltage between ACP and ACN to a scaled voltage set by the input current register. The total input current is the sum of the device supply current, the charger input current, and the system load current. The total input current can be estimated as follows:

$$I_{INPUT} = I_{SYSTEM} + \left[ \left( I_{CHG} \times V_{BATTERY} \right) / (V_{IN} \times \eta) \right]$$

where  $\eta$  is the efficiency of the DC/DC converter (typically 85% to 95%). To set the input current limit use the SMBus to write a 16-bit input current register using the data format listed in Table 5. The input

current register uses the Write-Word protocol. The register code for input current is 0x3F (0b0011111). The input current register can be read back to verify its contents.

The SY6915 ignores the first 6 LSBs and uses the next 6 bits to control the input current DAC. The input-current range of the SY6915 is from 128mA to 8.064A. All 16-bit numbers requesting input current below 128mA or above 8.064A will terminate charging. The default input current limit setting at POR is 4.096A. When choosing the current-sense resistor, carefully calculate its power rating. Take into account variations in the system's load current and the overall accuracy of the sense amplifier. Note that the voltage drop across this resistor contributes additional power loss, which reduces efficiency. System currents normally fluctuate as portions of the system are powered up or put to sleep. Without input current regulation, the input source must be able to deliver the maximum system current and the maximum charger-input current. By using the input current fimit circuit, the output-current capability of the AC wall adapter can be lowered, reducing system cost.

| Bit | Bit Name                      | Description                                                                     |

|-----|-------------------------------|---------------------------------------------------------------------------------|

| 0   |                               | Not used.                                                                       |

| 1   |                               | Not used.                                                                       |

| 2   |                               | Not used.                                                                       |

| 3   |                               | Not used.                                                                       |

| 4   | $\mathbf{\tilde{\mathbf{G}}}$ | Not used.                                                                       |

| 5   |                               | Not used.                                                                       |

| 6   |                               | Not used.                                                                       |

| 7   | Input Current, DACIIN 0       | 0 = Adds 0mA of input current.<br>1 = Adds 128mA of input current.              |

| 8   | Input Current, DACIIN 1       | 0 = Adds 0mA of input current.<br>1 = Adds 256mA of input current.              |

| 9   | Input Current, DACIIN 2       | 0 = Adds 0mA of input current.<br>1 = Adds 512mA of input current.              |

| 10  | Input Current, DACIIN 3       | 0 = Adds 0mA of input current.<br>1 = Adds 1024mA of input current.             |

| 11  | Input Current, DACIIN 4       | 0 = Adds 0mA of input current.<br>1 = Adds 2048mA of input current.             |

| 12  | Input Current, DACIIN 5       | 0 = Adds 0mA of input current.<br>1 = Adds 4096mA of input current, 8064mA max. |

| Table5. Input Current Limit (Register 0x3F) | $(10m\Omega$ Sense Resistor) |

|---------------------------------------------|------------------------------|

|---------------------------------------------|------------------------------|

| Bit | Bit Name | Description |

|-----|----------|-------------|

| 13  |          | Not used.   |

| 14  |          | Not used.   |

| 15  |          | Not used.   |

#### SY6915 Data Byte Order

Each register in SY6915 contains 16-bits or 2, 8 bit bytes. All data sent on the SMBus is in 8 bit bytes and 2 bytes must be written or read from each register in SY6915. The order in which these bytes

#### Writing to the Internal Registers

In order to set the charge current, charge voltage or input current, valid 16-bit numbers must be written to SY6915's internal registers via the SMBus.