## **MPQ5072**

5.5V, 1A Low R<sub>DS(ON)</sub> Load Switch with Programmable Current Limit, AEC-Q100 Qualified

#### DESCRIPTION

The MPQ5072 is a programmable load switch that provides 1A of load protection across a 0.5V to 5.5V voltage range. With low  $R_{DS(ON)}$  in a tiny package, the MPQ5072 provides a highly efficient, space-saving solution for notebooks, tablets, and other portable device applications.

The MPQ5072's soft start (SS) function avoids inrush current during circuit start-up. The MPQ5072 also provides a programmable soft-start time, output discharge functions, over-current protection (OCP), and thermal shutdown.

The maximum load at the output source is current-limited, which is accomplished by utilizing a sense FET topology.

The magnitude of the current limit is controlled by an external resistor from the ILIM pin to ground (GND).

An internal charge pump drives the power device gate, allowing a low on resistance DMOS power FET of  $50m\Omega$ .

The MPQ5072 is available in a tiny, space-saving QFN-12 (2mmx2mm) package.

#### **FEATURES**

- Guaranteed Industrial/Automotive Temperature Range Limits

- 0.5V to 5.5V V<sub>IN</sub> Range

- Shutdown Current < 5μA</li>

- Integrated 50mΩ Low R<sub>DS(ON)</sub> FETs

- 1A Load Current

- Push/Pull Power Good (PG) Indicator

- Adjustable Start-Up Slew Rate

- Output Discharge

- Short-Circuit Protection (SCP) < 200ns

- Thermal Shutdown Protection

- Available in a Space-Saving QFN-12 (2mmx2mm) Package

- Available in AEC-Q100 Grade 1

#### **APPLICATIONS**

- Notebook and Tablet Computers

- Portable Devices

- Solid State Drives (SSDs)

- Handheld Devices

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

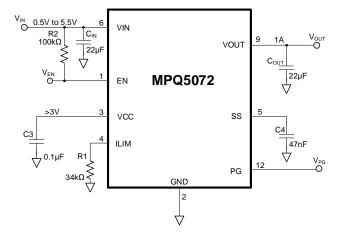

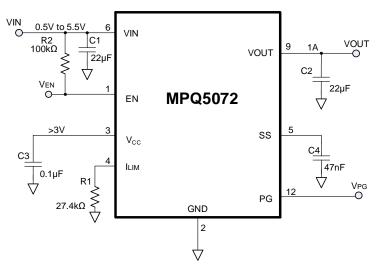

#### TYPICAL APPLICATION

## **ORDERING INFORMATION**

| Part Number*   | Package          | Top Marking | MSL Rating |

|----------------|------------------|-------------|------------|

| MPQ5072GG      | OEN 12 (2mmy2mm) | Coo Polow   | 1          |

| MPQ5072GG-AEC1 | QFN-12 (2mmx2mm) | See Below   | I          |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MPQ5072GG-AEC1–Z).

#### **TOP MARKING**

LRY

LLLL

LR: Product code of MPQ5072GG & MPQ5072GG-AEC1

Y: Year code LLLL: Lot number

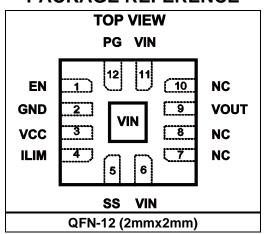

## **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin #                 | Name                             | Description                                                                                                                  |  |  |

|-----------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                     | EN                               | Enable input. Pull EN below the specified threshold to shut down the chip.                                                   |  |  |

| 2                     | GND                              | Ground.                                                                                                                      |  |  |

| 3                     | VCC                              | Supply voltage to the control circuitry.                                                                                     |  |  |

| 4                     | ILIM                             | Output current limit configuration. Place a resistor to GND to set the overload current limit level.                         |  |  |

| 5                     | SS                               | <b>Soft start.</b> An external capacitor connected to the SS pin sets the slew rate of the output voltage soft-start period. |  |  |

| 6, 11,<br>exposed pad | Input power supply.              |                                                                                                                              |  |  |

| 9                     | VOUT                             | Output to the load.                                                                                                          |  |  |

| 12                    | PG Power good. Push/pull output. |                                                                                                                              |  |  |

| 7, 8, 10              | NC                               | <b>Not connected.</b> It is recommended to connect this pin to VOUT to improve thermal performance.                          |  |  |

#### **ABSOLUTE MAXIMUM RATINGS (1)**

| V <sub>IN</sub>              | 0.3V to +6.5V           |

|------------------------------|-------------------------|

| V <sub>CC</sub>              | 0.3V to +6.5V           |

| V <sub>OUT</sub>             | 0.3V to +6.5V           |

| EN, SS, ILIM                 | -0.3V to $V_{CC}$ +0.3V |

| Junction temperature         | 150°C                   |

| Lead temperature             | 260°C                   |

| Continuous power dissipation | ) <sup>(2)</sup>        |

| QFN-12 (2mmx2mm)             | 1.6W                    |

#### ESD Ratings

| Human body model (HE   | 3M)±2k\     | / |

|------------------------|-------------|---|

| Charged device model ( | (CDM) ±750\ | / |

#### **Recommended Operating Conditions (3)**

| Supply voltage (V <sub>IN</sub> )         | 0.5V to 5.5V    |

|-------------------------------------------|-----------------|

| Supply voltage (V <sub>CC</sub> )         | 3V to 5.5V      |

| Output voltage (V <sub>OUT</sub> )        | 0.5V to 5.5V    |

| Operating junction temp (T <sub>J</sub> ) | -40°C to +125°C |

| Thermal Resistance | $e^{(4)}$ $\theta_{JA}$ | $oldsymbol{	heta}$ JC |       |

|--------------------|-------------------------|-----------------------|-------|

| QFN-12 (2mmx2mm)   | 80                      | 16                    | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the device may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 3.6V$ ,  $V_{CC} = 3.6V$ ,  $T_{J} = -40^{\circ}$ C to +125°C, typical values are  $T_{J} = 25^{\circ}$ C, unless otherwise noted.

| Parameters                                 | Symbol                | Condition                                                              | Min | Тур | Max  | Units |

|--------------------------------------------|-----------------------|------------------------------------------------------------------------|-----|-----|------|-------|

| Input and Supply Voltage Range             |                       |                                                                        |     |     |      |       |

| Input voltage                              | V <sub>IN</sub>       |                                                                        | 0.5 |     | 5.5  | V     |

| Supply voltage                             | Vcc                   |                                                                        | 3   |     | 5.5  | V     |

| Supply Current                             | _                     |                                                                        |     |     |      |       |

| Off state leakage assument                 |                       | $V_{IN} = 5V$ , $EN = 0$ , $T_J = 25$ °C                               |     |     | 1    | μΑ    |

| Off-state leakage current                  | loff                  | $V_{IN} = 5V$ , $EN = 0$ ,<br>-40°C < $T_J$ < +125°C                   |     |     | 5    | μΑ    |

|                                            |                       | Vcc = 5V, EN = 0                                                       |     | 0.1 | 1    |       |

| VCC standby current                        | I <sub>STBY</sub>     | Vcc = 5V, enable, no load,<br>T <sub>J</sub> = 25°C                    |     | 180 | 230  | μA    |

| ,                                          |                       | Vcc = 5V, enable, no load,<br>-40°C < T <sub>J</sub> < +125°C          |     | 180 | 250  |       |

| Power FET                                  |                       |                                                                        |     |     | 1    | I     |

|                                            |                       | Vcc = 5.0V, T <sub>J</sub> = 25°C                                      |     | 50  | 70   |       |

| On resistance                              | D-s/s/                | $V_{CC} = 5.0V, -40^{\circ}C < T_{J} < +125^{\circ}C$                  |     | 50  | 80   | mΩ    |

| On resistance                              | R <sub>DS(ON)</sub>   | Vcc = 3.3V, T <sub>J</sub> = 25°C                                      |     | 60  | 80   | 11122 |

|                                            |                       | $V_{CC} = 3.3V, -40^{\circ}C < T_{J} < +125^{\circ}C$                  |     | 60  | 90   |       |

| Thermal Shutdown and Recovery (5           | )                     |                                                                        |     |     |      |       |

| Shutdown temperature                       | T <sub>STD</sub>      |                                                                        |     | 150 |      | °C    |

| Hysteresis                                 | T <sub>HYS</sub>      |                                                                        |     | 30  |      | °C    |

| Under-Voltage Protection                   |                       |                                                                        |     |     |      |       |

| VCC under-voltage lockout (UVLO) threshold | Vcc_uvlo              | UVLO rising threshold                                                  |     | 2.6 | 2.95 | V     |

| UVLO hysteresis                            | V <sub>UVLO_HYS</sub> |                                                                        |     | 200 |      | mV    |

| Soft Start (SS)                            | •                     |                                                                        |     |     |      | •     |

| SS pull-up current                         | Iss                   | Fixed slew rate                                                        | 4   | 11  | 17   | μA    |

| Enable (EN)                                |                       |                                                                        |     |     | · L  |       |

| EN rising threshold                        | V <sub>ENH</sub>      |                                                                        | 1.3 | 1.5 | 1.7  | V     |

| EN hysteresis                              | V <sub>EN_HYS</sub>   |                                                                        |     | 200 |      | mV    |

| ILIM                                       | 1 2.1                 |                                                                        |     |     | II.  | 1     |

| Current limit                              | Іоит                  | $R_{LIM} = 24k\Omega$ , ramp $I_{OUT}$ record peak current limit value |     | 1.4 |      | Α     |

| Discharge Resistance                       |                       |                                                                        | •   |     |      | •     |

| Discharge resistance                       | R <sub>DIS</sub>      |                                                                        |     | 200 |      | Ω     |

| Power Good (PG)                            | <u>.</u>              |                                                                        | •   |     | •    | •     |

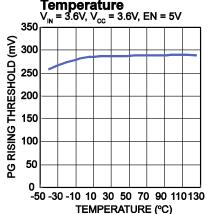

| PG rising threshold                        | V <sub>PG_R</sub>     | Voltage gap between V <sub>OUT</sub> and V <sub>IN</sub>               | 140 | 280 | 450  | mV    |

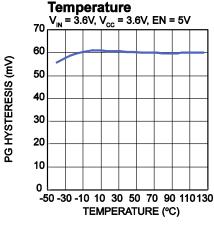

| PG threshold                               | V <sub>PG_HYS</sub>   |                                                                        |     | 60  |      | mV    |

| PG delay                                   | t <sub>PG_D</sub>     |                                                                        |     | 50  |      | μs    |

| PG high                                    | V <sub>PG_H</sub>     | V <sub>CC</sub> = 3.3V                                                 | 3.2 |     |      | V     |

| PG low                                     | VPG_L                 | Sink 1mA                                                               |     |     | 0.3  | V     |

#### Notes:

5) Guaranteed by design.

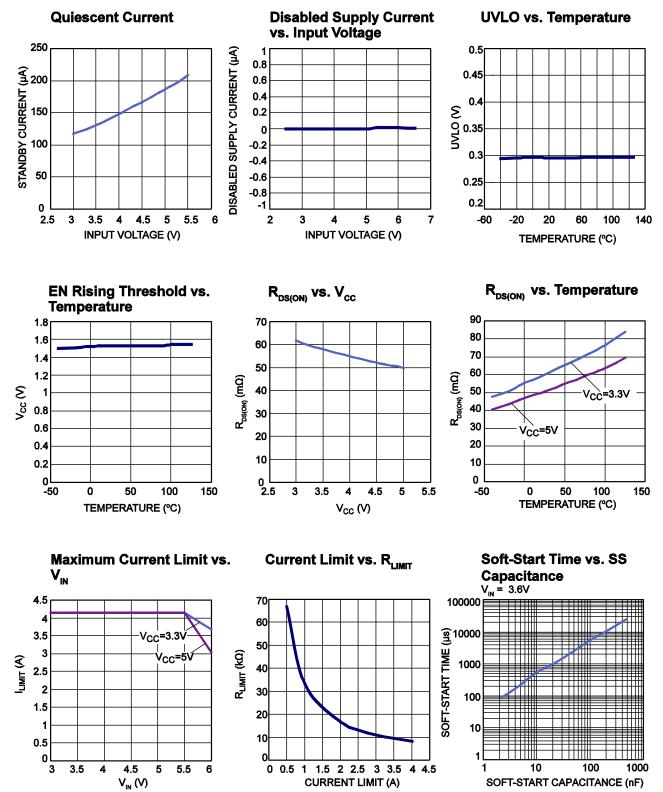

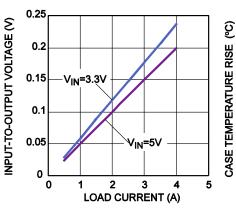

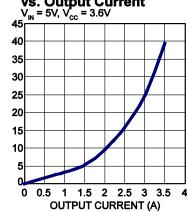

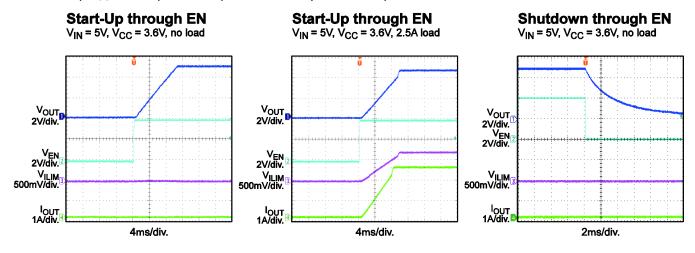

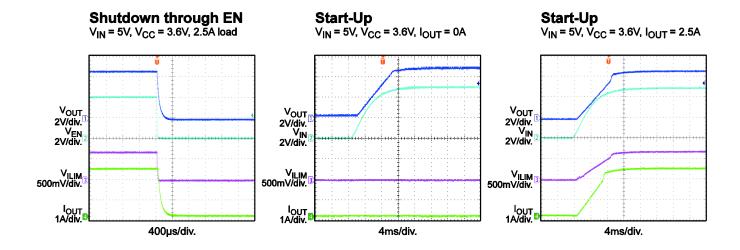

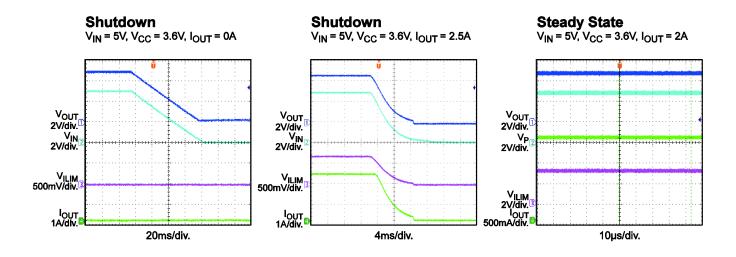

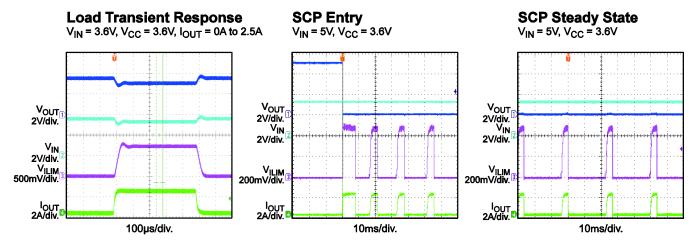

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 3.6V$ ,  $V_{CC} = 3.6V$ ,  $R_{ILIM} = 13k\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 3.6V$ ,  $V_{CC} = 3.6V$ ,  $R_{ILIM} = 13k\Omega$ ,  $T_A = 25$ °C, unless otherwise noted.

# Case Temperature Rise vs. Output Current

## PG Rising Threshold vs. Temperature

#### PG Hysteresis vs.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

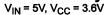

$V_{IN} = 3.6V$ ,  $V_{CC} = 3.6V$ , EN = 4V,  $R_{ILIM} = 13k\Omega$ ,  $T_A = 25$ °C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 3.6V$ ,  $V_{CC} = 3.6V$ , EN = 4V,  $R_{ILIM} = 13k\Omega$ ,  $T_A = 25$ °C, unless otherwise noted.

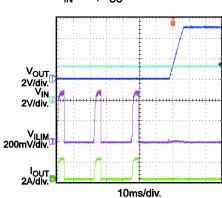

## **FUNCTIONAL BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

#### **OPERATION**

The MPQ5072 is designed to limit the inrush current to the load when a circuit card is inserted into a live backplane power source, limiting the backplane's voltage drop and the slew rate of the voltage to the load. The MPQ5072 provides an integrated solution that monitors the input voltage, output voltage, and output current — eliminating the need for an external current power MOSFET and current-sense device.

#### Enable (EN)

The MPQ5072 is enabled when the input voltage exceeds the under-voltage lockout (UVLO) threshold (typically 0.5V), and the enable (EN) pin is pulled above 1.5V. Pulling the voltage down to ground (GND) disables the MPQ5072.

#### **Current Limit**

The MPQ5072 provides a constant-current limit programmed by an external resistor. Once the device reaches its current limit threshold, the IC regulates the gate voltage to hold a constant current in the power FET. The typical response time is about 20µs. During this response time, a small overshoot in the output current may occur. The preset current limit value can be calculated with Equation (1):

$$I_{LIMIT} = (1 / R_{ILIM}) \times S$$

(1)

Where S is the current-sense ratio of the MPQ5072 (typically 33,000 if  $V_{IN} = 3.6V$ ).

If the current limit block starts regulating the output current, power loss in the power MOSFET causes the IC temperature to rise. Thermal shutdown occurs if the junction temperature is too high. After thermal shutdown, the output is disabled until the over-temperature (OT) fault is removed. The OT threshold is 150°C, and the hysteresis is 30°C.

#### Power Good (PG)

The power good (PG) pin is the push/pull of a MOSFET that can be pulled high to  $V_{CC}$ . The MOSFET turns on with the application of an input voltage so that the PG pin pulls to GND. Once the voltage gap between  $V_{IN}$  and  $V_{OUT}$  is less than 280mV, the PG pin is pulled high after a

50µs delay. When the voltage gap is greater than 340mV, the PG pin is pulled low.

#### **Short-Circuit Protection (SCP)**

If a short circuit causes the load current to rapidly increase, the current may exceed its limit threshold. If the current reaches the internal secondary limit (about 7A), a fast turn-off circuit shuts off the power FET, limiting the peak current through the switch and the input voltage drop. The total short circuit response time is about 200ns. If the fast turn-off succeeds, the power FET remains off for 80µs. After the 80µs, the power FET turns back on. If the short circuit remains, the MPQ5072 reduces and holds the current limit until the part is hot enough to trigger thermal shutdown. Once the short circuit condition is removed, the current limit will automatically recovers to the preset value.

#### **Output Discharge**

The MPQ5072 has an output discharge function. This function discharges  $V_{\text{OUT}}$  with an internal pull-down resistor when the IC is disabled and the load is very light.

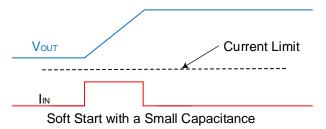

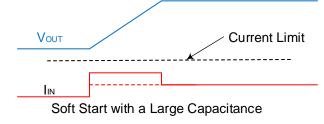

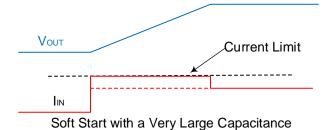

#### Soft Start (SS)

The capacitor connected to the SS pin determines the soft-start time. An internal,  $11\mu A$  constant-current source charges the SS capacitor and ramps up the voltage on the SS pin. The output voltage rises at five times the slew rate of the SS voltage.

The soft-start time can be calculated with Equation (2):

$$t_{SS}(ms) = \frac{1}{5} \times \frac{V_{OUT}(V) \times C_{SS}(nF)}{I_{SS}(\mu A)}$$

(2)

Where  $t_{SS}$  is the soft-start time,  $I_{SS}$  is the internal 11µA constant current, and  $C_{SS}$  is the external SS capacitor.

The suggested minimum capacitance should be greater than 4.7nF. If the SS pin is floating or the SS capacitor is too small, the  $V_{\text{OUT}}$  rise time is limited by the power MOSFET charge time.

#### APPLICATION INFORMATION

#### **ILIM Resistor Selection**

The current limit value is set by the ILIM resistor (R<sub>ILIM</sub>). The current limit can be calculated with Equation (1) on page 10.

The suggested current limit threshold should be 10% to 20% greater than the maximum load current. For example, if a system's full load is 1A, set the current limit to 1.1A.

#### **ILIM Capacitor Selection**

The internal, advanced, auto-zero comparator offers high-accuracy current monitoring, though it causes a small amount of jitter on the ILIM pin. To stabilize ILIM, mount a small ceramic capacitor between the ILIM pin and GND. It is recommended to use a capacitor that is less than 1nF.

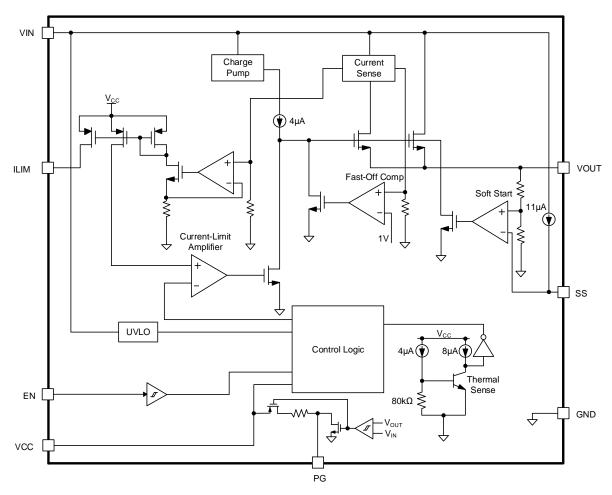

#### **SS Capacitor Selection**

An internal  $11\mu A$  constant-current source charges the SS capacitor, which ramps up the voltage on the SS pin. The output voltage follows the SS voltage slew rate as it rises.

If the inrush of the output current reaches the current limit during start-up (e.g. if there is a large output capacitor or a large load), the MPQ5072 limits the output current, and the soft-start time increases simultaneously (see Figure 2 and Figure 3).

#### **Component Selection**

Figure 2: Soft Start at Different Loads

Soft Start with Different Output Capacitances

Figure 3: Soft Start at Different Output Capacitances

#### **Design Example**

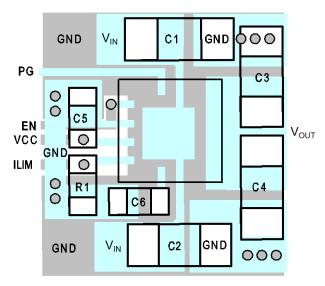

For design examples, see Table 1 and Figure 5.

Table 1: Recommended RLIM and Css Values

|     |     | Max Load R <sub>LIMIT</sub> SS Ca<br>Range (A) (kΩ) |    | SS Time<br>(ms) |

|-----|-----|-----------------------------------------------------|----|-----------------|

| 3.6 | 0.5 | 47                                                  | 22 | 1               |

| 3.6 | 1   | 27.4                                                | 47 | 2.4             |

#### **PCB Layout Guidelines**

PCB layout is critical for stable operation. For the best results, refer to Figure 4 and follow the guidelines below:

- 1. Place R<sub>ILIM</sub> close to the ILIM pin.

- 2. Place the input capacitor close to the VCC pin.

- 3. Place vias around the IC to improve thermal performance.

Figure 4: Recommended PCB Layout

## TYPICAL APPLICATION CIRCUIT

**Figure 5: Typical Application Circuit**

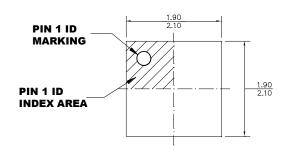

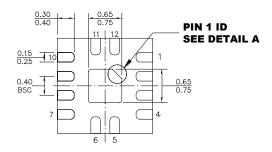

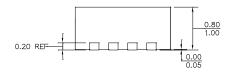

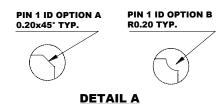

## **PACKAGE INFORMATION**

## QFN-12 (2mmx2mm)

#### **TOP VIEW**

#### **BOTTOM VIEW**

**SIDE VIEW**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

- 4) JEDEC REFERENCE IS MO-229.

- 5) DRAWING IS NOT TO SCALE.

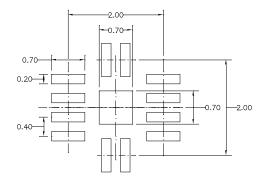

#### **RECOMMENDED LAND PATTERN**

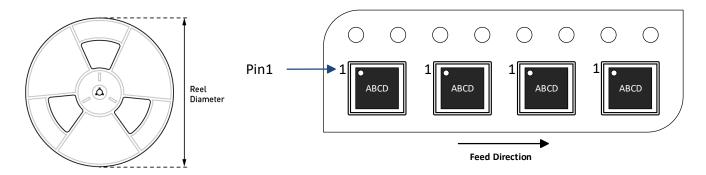

## **CARRIER INFORMATION**

| Part Number                         | Package Description |       | Quantity/<br>Tube | Quantity/<br>Tray | Reel<br>Diameter | Carrier<br>Tape Width | Carrier<br>Tape Pitch |

|-------------------------------------|---------------------|-------|-------------------|-------------------|------------------|-----------------------|-----------------------|

| MPQ5072GG-Z<br>MPQ5072GG-<br>AEC1-Z | QFN-12<br>(2mmx2mm) | 5,000 | N/A               | N/A               | 13in             | 12mm                  | 8mm                   |

## **Revision History**

| Revision # | Revision<br>Date | Description     | Pages<br>Updated |  |

|------------|------------------|-----------------|------------------|--|

| 1.0        | 10/16/2020       | Initial Release | -                |  |

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.