# CrM/DCM Multi-Mode PFC Controller with Second OVP

### **DESCRIPTION**

The MP44019 is a CrM/DCM multi-mode PFC controller that provides simple and high-performance active power factor correction using minimal external components.

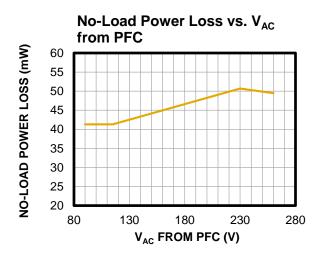

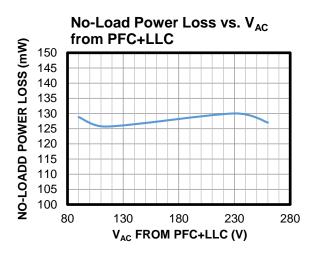

The device features a very low supply current. This allows the device to achieve low standby power loss. The typical no load power loss is below 50mW.

The MP44019 reduces the switching frequency using dead time extension technology under light loads. This improves light-load efficiency.

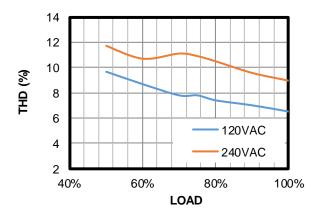

The device achieves lower total harmonic distortion (THD) due to variable on time control in discontinuous conduction mode (DCM), when compared to conventional constant on time (COT) control.

Multi-protection functionality largely enhances the safety and reliability of the system. The MP44019 feature over-voltage protection (OVP), second OVP (OVP2), an over-current limit (OCL), over-current protection (OCP), under-voltage protection (UVP), brown-in (BI) and brownout (BO), VCC under-voltage lockout (UVLO), and over-temperature protection (OTP).

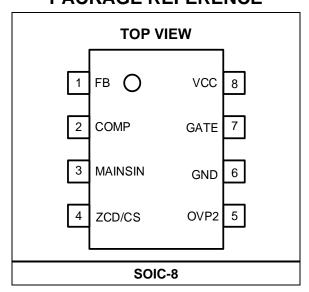

The MP44019 is available in an SOIC-8 package.

# **FEATURES**

- Valley Turn On for Minimum Switching Loss

- Frequency Reduction to Reduce Switching Loss Under Light-Load Conditions

- Low Supply Current in Burst Mode

- Soft-On/Off Burst for Low Audible Noise

- Mains Compensation

- Improved THD

- Under-Voltage Protection (UVP)

- Over-Current Limit (OCL)

- Over-Current Protection (OCP)

- Over-Voltage Protection (OVP)

- Second Over-Voltage Protection (OVP2)

- Brown-In (BI) and Brownout (BO)

- Over-Temperature Protection (OTP)

- Open/Short Pin Protection

- Soft Start-Up

- Enhanced Dynamic Response

- Available in an SOIC-8 Package

# **APPLICATIONS**

- LCD and OLED TVs

- Desktop PCs and Servers

- High-Power Supplies for Lighting

- AC/DC Adapters, Open-Frame SMPSs

- Video Game Consoles

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

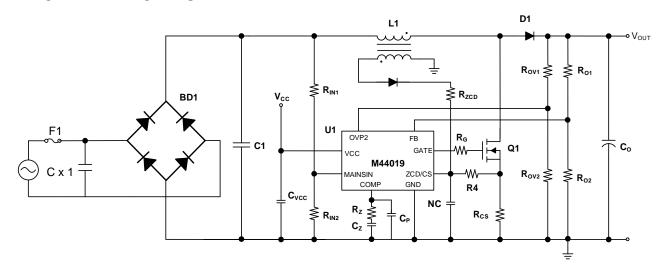

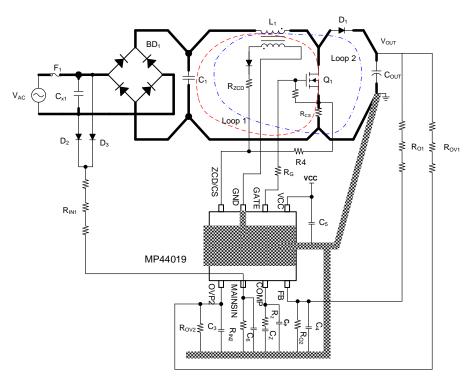

# **TYPICAL APPLICATION**

# **ORDERING INFORMATION**

| Part Number* | Package | Top Marking | MSL Rating |  |

|--------------|---------|-------------|------------|--|

| MP44019GS    | SOIC-8  | See Below   | 2          |  |

\*For Tape & Reel, add suffix –Z (e.g. MP44019GS–Z).

# **TOP MARKING**

MP44019 LLLLLLLL MPSYWW

MP44019: Part number LLLLLLL: Lot number MPS: MPS prefix Y: Year code WW: Week code

# **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| Pin# | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |           | <b>Output voltage sense.</b> The FB pin senses the output voltage through a resistor divider, and compares the sensed voltage to the reference voltage (V <sub>REF</sub> ) (typically 2.5V). This allows the output voltage to be regulated. FB also integrates under-voltage protection (UVP) and over-voltage protection (OVP), described below:                                                                                                                                                                                                           |

| 1    | FB        | $\underline{\text{UVP}}$ : Pull the FB pin below 0.36V for a blanking time ( $t_{\text{BL\_UVP}}$ ) of 55µs to shut down the IC, or pull COMP down for the IC to enter low-supply current mode.                                                                                                                                                                                                                                                                                                                                                              |

|      |           | $\underline{\text{OVP}}$ : If the FB voltage (V <sub>FB</sub> ) exceeds V <sub>FB_OVP</sub> (typically 2.7V) for a blanking time (t <sub>BL_OVP</sub> ) of 22µs, the IC stops switching. The IC resumes switching when V <sub>FB</sub> drops back to 2.62V.                                                                                                                                                                                                                                                                                                  |

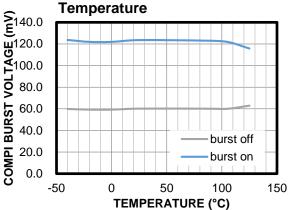

| 2    | СОМР      | <b>Error amplifier output.</b> The compensation network is connected between the COMP pin and GND. If the internal COMP voltage (V <sub>COMPI</sub> ) drops below V <sub>COMPI_BOFF</sub> (typically 60mV), switching stops with five soft-off pulses. As V <sub>COMPI</sub> ramps up to V <sub>COMPI_BON</sub> (typically 120mV), switching resumes after five soft-on pulses.                                                                                                                                                                              |

| 2    | MAINICINI | Mains voltage sense. MAINSIN is connected to the capacitor just after the rectifier bridge. The rectifier voltage is scaled down by a resistor divider connected to MAINSIN. The voltage on MAINSIN provides brown-in and brownout functions, and provides feed-forward compensation for the COMP voltage.                                                                                                                                                                                                                                                   |

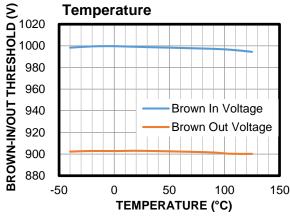

| 3    | MAINSIN   | If MAINSIN's peak voltage exceeds $V_{MAINS\_BI}$ (typically 1V), the device starts to switch with COMP soft start-up. If MAINSIN's peak voltage remains below $V_{MAINS\_BO}$ (typically 0.9V) for $t_{BO}$ (typically 50ms), a brownout condition is confirmed. Then the PFC stops switching, and COMP is pulled down to 0V.                                                                                                                                                                                                                               |

|      |           | Combined function with current sense and zero-current detection. The CS pin provides monitoring for over-current protection (OCP) and over-current limiting (OCL). A lead-edge blanking (LEB) time ensures that the CS pin does not mistrigger OCP or OCL. OCP and OCL are described in greater detail below:                                                                                                                                                                                                                                                |

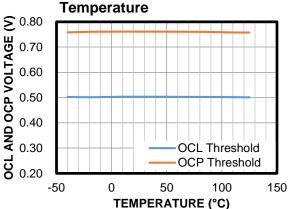

|      |           | OCL: If CS exceeds V <sub>OCL</sub> (typically 0.5V) for an LEB time (t <sub>OCL_LEB</sub> ) of 300ns, the IC stops switching. OCL is cycle-by-cycle current limited.                                                                                                                                                                                                                                                                                                                                                                                        |

| 4    | ZCD/CS    | $\underline{\text{OCP}}$ : If the CS voltage exceeds V <sub>OCP</sub> (typically 0.75V) for two consecutive 180µs restart switching cycles, the OCP flag is triggered, and the IC stops switching. OCP is reset by an auto-recovery timer (tocp_R) of 80ms, or by a brown-in, brownout, or VCC under-voltage lockout (UVLO) event.                                                                                                                                                                                                                           |

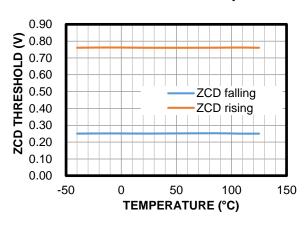

|      |           | A leading-edge blanking time ( $t_{ZCD\_LEB}$ ) of 0.3µs is inserted to filter out the noise ringing on ZCD after the gate turns off. The positive voltage on ZCD must exceed $V_{ZCD\_H}$ (typically 0.75V), then drop below $V_{ZCD\_L}$ (typically 0.25V) for the next stroke. The valley switch must wait for the end of the minimum period limit time or dead time extension control. The restart timer generates a signal to turn on the MOSFET when ZCD is not detected for $t_{ZCD\_TO}$ (typically 180µs) which starts to count when switching off. |

| 5    | OVP2      | <b>Second OVP function.</b> If OVP2 exceeds $V_{FB\_OVP2}$ (typically 2.7V) for a blanking time of $t_{BL\_OVP2}$ (typically 22µs), the IC stops switching. The IC resumes switching when OVP2 drops to $V_{FB\_OVP2}$ - $V_{FB\_OVP2\_HYS}$ (typically 2.6V).                                                                                                                                                                                                                                                                                               |

| 6    | GND       | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7    | GATE      | <b>Gate driver output.</b> The high output current of the gate driver can drive the power MOSFET. If GATE is supplied with a high $V_{\rm CC}$ , the high-level voltage of GATE is clamped to 13V.                                                                                                                                                                                                                                                                                                                                                           |

| 8    | VCC       | <b>Supply voltage.</b> VCC supplies power to the IC's signal path and the gate driver. Connect a bypass capacitor from VCC to ground to reduce noise.                                                                                                                                                                                                                                                                                                                                                                                                        |

| ABSOLUTE MAXIM                                                           | UM RATINGS (1)     |

|--------------------------------------------------------------------------|--------------------|

| Supply voltage (V <sub>CC</sub> )<br>FB, COMP, MAINSIN, CS.              |                    |

| GATE                                                                     | 0.3V to +14V       |

| ZCDZCD current                                                           |                    |

| Continuous power dissipati SOIC-8                                        |                    |

| Junction temperature<br>Lead temperature (solder)                        | 150°C<br>260°C     |

| Storage temperature <b>ESD Ratings</b>                                   | 55°C to +150°C     |

| Human body model (HBM)<br>Charged device model (CD                       |                    |

| Recommended Operation                                                    | ing Conditions (3) |

| Supply voltage (V <sub>CC</sub> )<br>MAINSIN<br>Maximum junction temp (T | 0V to 4V           |

| Thermal Resistance (4) | $oldsymbol{	heta}$ JA | $oldsymbol{	heta}$ JC |      |

|------------------------|-----------------------|-----------------------|------|

| SOIC-8                 | 90                    | 45                    | °C/W |

#### Notes:

- Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the maximum junction temperature, T\_J (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA},$  and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by D (MAX) =  $(T_J (MAX) - T_A) / \theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

5

Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS (5)**

$V_{CC}$  = 20V,  $T_A$  =  $T_J$ = -40°C to +125°C, min and max values are guaranteed by characterization, typical values are tested under 25°C, unless otherwise noted.

| Parameter                               | Symbol                      | Condition                                  | Min      | Тур  | Max   | Units |

|-----------------------------------------|-----------------------------|--------------------------------------------|----------|------|-------|-------|

| Supply Voltage (VCC)                    |                             |                                            | <u> </u> |      |       |       |

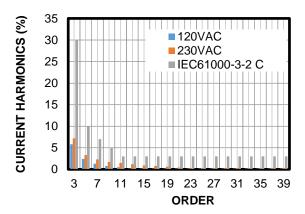

| Turn-on threshold                       | Vcc_on                      |                                            | 10.2     | 10.7 | 11.2  | V     |

| Turn-off threshold                      | V <sub>CC_OFF</sub>         |                                            | 8.1      | 8.6  | 9.1   | V     |

| Hysteresis                              | Vcc_hys                     |                                            | 1.8      | 2.1  | 2.4   | V     |

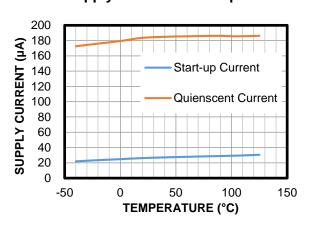

| Supply Current                          |                             |                                            |          |      |       |       |

| Start-up current                        | ISTARTUP                    | Vcc = 9.5V                                 |          | 25   | 40    | μΑ    |

| Quiescent current                       | lα                          | No switch                                  |          | 0.18 | 0.25  | mA    |

| Operating current                       | Icc                         | fsw = 70kHz, C <sub>LOAD</sub> = 1nF       |          | 2.1  | 3     | mA    |

| Mains Voltage Sensing (                 | (MAINSIN)                   |                                            |          |      |       |       |

| Brown-in voltage                        | V <sub>MAINS_BI</sub>       |                                            | 0.95     | 1    | 1.05  | V     |

| Brownout voltage                        | V <sub>MAINS_BO</sub>       |                                            | 0.85     | 0.9  | 0.95  | V     |

| Brownout comparator hysteresis          | V <sub>BO(HYS)</sub>        |                                            | 0.05     | 0.1  | 0.14  | V     |

| Brownout timer                          | t <sub>BO</sub>             |                                            |          | 50   |       | ms    |

| Protection current for MAINSIN open     | I <sub>MAINSIN_BIAS</sub>   |                                            |          | 20   |       | nA    |

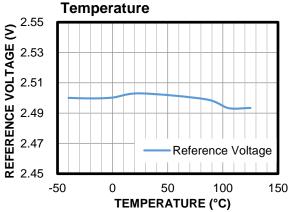

| Error Amplifier                         | 1                           |                                            | <u>'</u> |      |       |       |

| Reference voltage                       | $V_R$                       |                                            | 2.463    | 2.5  | 2.538 | V     |

|                                         | G <sub>м1</sub>             | V <sub>FB</sub> = 2.45V                    | 80       | 105  | 125   | μS    |

| Transconductance                        | G <sub>M2</sub>             | V <sub>FB</sub> = 2.2V to 2.3V             | 160      | 280  | 400   | μS    |

|                                         | G <sub>мз</sub>             | V <sub>FB</sub> = 2.65V to 2.75V           | 660      | 780  | 940   | μS    |

| Course ourrent                          | I <sub>SOURCE1</sub> (COMP) | $V_{FB} = V_{REF} - 0.3V$                  | 40       | 70   | 100   | μΑ    |

| Source current                          | ISOURCE2(COMP)              | V <sub>FB</sub> = V <sub>REF</sub> - 0.05V | 3        | 5    | 7     | μΑ    |

| Ciple ourrent                           | Isink1(COMP)                | V <sub>FB</sub> = V <sub>REF</sub> + 0.05V | -2.5     | -4.5 | -6.5  | μΑ    |

| Sink current                            | I <sub>SINK2(COMP)</sub>    | $V_{FB} = V_{REF} + 0.15V$                 | -25      | -50  | -75   | μA    |

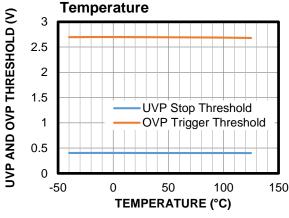

| Feedback Inverter Pin (F                | B)                          |                                            |          |      |       |       |

| UVP stop threshold                      | V <sub>FB_UVP</sub>         |                                            | 0.35     | 0.4  | 0.45  | V     |

| UVP hysteresis                          | V <sub>FB_UVP_HYS</sub>     |                                            |          | 0.04 |       | V     |

| UVP blanking time                       | t <sub>BL_UVP</sub>         |                                            | 35       | 55   | 75    | μs    |

| FB start G <sub>M3</sub> (5)            | V <sub>FB_SGM3</sub>        |                                            | 2.56     | 2.6  | 2.64  | V     |

| FB start G <sub>M2</sub> (5)            | V <sub>FB_SGM2</sub>        |                                            | 2.36     | 2.4  | 2.44  | V     |

| OVP trigger threshold                   | $V_{FB\_OVP}$               |                                            | 2.66     | 2.7  | 2.73  | V     |

| OVP hysteresis                          | V <sub>FB_OVP_HYS</sub>     |                                            |          | 0.08 |       | V     |

| OVP blanking time                       | t <sub>BL_OVP</sub>         |                                            | 15       | 22   | 32    | μs    |

| Protection current for an FB open fault | I <sub>FB_BIAS</sub>        | V <sub>FB</sub> = 2V                       |          | 20   |       | nA    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{CC}$  = 20V,  $T_A$  =  $T_J$  = -40°C to +125°C, min and max values are guaranteed by characterization, typical values are tested under 25°C, unless otherwise noted.

| Parameter                                                    | Symbol                 | Condition                | Min | Тур  | Max  | Units |

|--------------------------------------------------------------|------------------------|--------------------------|-----|------|------|-------|

| Current Sense (ZCD/CS)                                       |                        |                          |     |      |      |       |

| Protection current for ZCD/CS open fault                     | Ics_bias               |                          |     | 60   |      | nA    |

| Over-current limit threshold                                 | Vocl                   |                          | 460 | 500  | 530  | mV    |

| LEB time for OCL                                             | tocl_leb               |                          |     | 300  |      | ns    |

| Driver delay time                                            | tcs_delay              |                          |     | 100  |      | ns    |

| Over-current protection threshold                            | Vocp                   |                          | 600 | 750  | 1000 | mV    |

| Voltage difference between OCP and OCL                       | Vocp_ocl               |                          | 100 | 200  | 500  | mV    |

| LEB time for OCP                                             | tocp_leb               |                          |     | 250  |      | ns    |

| OCP recovery time                                            | tocp_r                 |                          |     | 80   |      | ms    |

| <b>Zero-Current Detection (ZC</b>                            | D/CS)                  |                          |     |      |      |       |

| Upper clamp voltage                                          | Vzcd_clamp             | $I_{ZCD} = 3mA$          | 7.2 | 7.8  |      | V     |

| Zero-current sensing                                         | V <sub>ZCD_</sub> H    | V <sub>ZCD</sub> rising  | 0.6 | 0.75 | 0.9  | V     |

| threshold                                                    | $V_{ZCD\_L}$           | V <sub>ZCD</sub> falling | 0.2 | 0.25 | 0.3  | V     |

| Turn-on delay after ZCD is detected                          | tzcd_delay             |                          |     | 150  |      | ns    |

| ZCD timeout                                                  | t <sub>ZCD_TO</sub>    |                          | 130 | 180  | 250  | μs    |

| ZCD leading-edge blanking time <sup>(5)</sup>                | tzcd_leb               |                          |     | 0.3  |      | μs    |

| Minimum off time                                             | toff_mini              |                          | 1   | 1.4  | 1.9  | μs    |

| Error Amplifier Output (CO                                   | MP)                    |                          |     |      | •    | •     |

| Comp voltage at max on time (5)                              | V <sub>COMP_H</sub>    |                          |     | 3.8  |      | V     |

| Comp voltage at zero on time <sup>(5)</sup>                  | Vcomp_l                |                          |     | 0.8  |      | V     |

| Internal COMP voltage transient from CrM to DCM (5)          | V <sub>COMPI_C2D</sub> |                          |     | 0.38 |      | V     |

| Internal COMP voltage to enter burst-off mode <sup>(6)</sup> | VCOMPI_BOFF            |                          | 30  | 60   | 90   | mV    |

| Internal COMP voltage to enter burst-on mode                 | V <sub>COMPI_BON</sub> |                          | 95  | 120  | 150  | mV    |

| Burst hysteresis                                             | V <sub>BURST_HYS</sub> |                          | 30  | 60   | 95   | mV    |

| Soft-off burst pulse counter (5)                             | Nsoftoff               |                          |     | 5    |      |       |

| Soft-on burst pulse counter (5)                              | Nsofton                |                          |     | 5    |      |       |

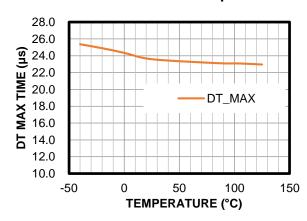

| Maximum dead time                                            | tdead_max              |                          | 19  | 23.5 | 29   | μs    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{CC}$  = 20V,  $T_A$  =  $T_J$  = -40°C to +125°C, min and max values are guaranteed by characterization, typical values are tested under 25°C, unless otherwise noted.

| Parameter                              | Symbol                   | Condition                                                                     | Min  | Тур  | Max | Units |

|----------------------------------------|--------------------------|-------------------------------------------------------------------------------|------|------|-----|-------|

| Mains Compensation                     |                          |                                                                               |      |      |     |       |

| On time                                | t <sub>ON_LL</sub>       | VCOMP = 3.8V, MAINSIN = 1.0V                                                  | 20   | 24   | 29  | μs    |

| On time                                | ton_hl                   | VCOMP = 3.8V, MAINSIN = 3.38V                                                 | 1.6  | 2.1  | 2.8 | μs    |

| Gate Driver (GATE)                     |                          |                                                                               |      |      |     |       |

| Drop voltage                           | Rон                      | Igdsource = 20mA                                                              |      | 10   | 16  | Ω     |

| Drop voltage                           | R <sub>OL</sub>          | I <sub>GDSINK</sub> = 20mA                                                    |      | 2.5  | 6   | Ω     |

| Voltage falling time                   | $t_{F}$                  |                                                                               |      | 20   |     | ns    |

| Voltage rising time                    | t <sub>R</sub>           |                                                                               |      | 120  |     | ns    |

| Max output drive voltage               | V <sub>GATE_MAX</sub>    |                                                                               | 11.5 | 13   | 15  | V     |

| Source current capability (5)          | IGATE_SOURCE             |                                                                               |      | -600 |     | mA    |

| Sink current capability (5)            | IGATE_SINK               |                                                                               |      | 1    |     | Α     |

| UVLO saturation voltage                | VSATURATION              | V <sub>CC</sub> = 0V to V <sub>CC_ON</sub> ,<br>I <sub>GATE_SINK</sub> = 10mA |      |      | 1.5 | V     |

| Second OVP (OVP2)                      |                          |                                                                               |      |      |     |       |

| OVP2 trigger threshold                 | V <sub>FB_OVP2</sub>     |                                                                               | 2.6  | 2.7  | 2.8 | V     |

| OVP2 hysteresis                        | V <sub>FB_OVP2_HYS</sub> |                                                                               |      | 0.08 |     | V     |

| Protection current for OVP2 open fault | I <sub>FB2_BIAS</sub>    |                                                                               |      | -100 |     | nA    |

| OVP2 blanking time                     | t <sub>BL_OVP2</sub>     |                                                                               | 17   | 23   | 32  | μs    |

| Internal OTP                           |                          |                                                                               |      |      |     |       |

| OTP threshold (5)                      | Тотр                     |                                                                               |      | 150  |     | °C    |

| OTP hysteresis (5)                     | T <sub>OTP_HYS</sub>     |                                                                               |      | 40   |     | °C    |

#### Notes:

- 5) Guaranteed by design.

- 6)  $V_{COMPI} = (V_{COMP} V_{COMP\_L}) / 3$ .

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 85V_{AC}$  to  $265V_{AC}$ ,  $V_{OUT} = 400V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

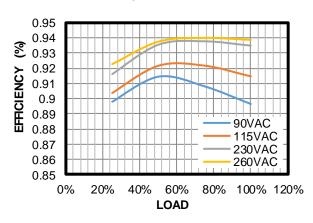

### Efficiency vs. Load

#### Power Factor vs. Load

#### THD vs. Load

# **Current Harmonics vs. Order**

$V_{IN} = 85V_{AC}$  to  $265V_{AC}$ ,  $V_{OUT} = 400V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### Supply Voltage vs. Temperature

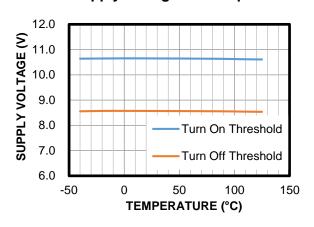

#### Supply Current vs. Temperature

Brown-In/Out Threshold vs.

Reference Voltage vs.

# UVP and OVP Threshold vs.

OCL and OCP Voltage vs.

$V_{IN} = 85V_{AC}$  to  $265V_{AC}$ ,  $V_{OUT} = 400V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

### **ZCD Threshold vs. Temperature**

# COMPI Burst Voltage vs.

### **DT Max Time vs. Temperature**

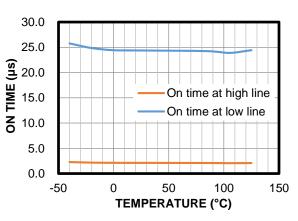

# On Time vs. Temperature

### **OVP2 Voltage vs. Temperature**

© 2021 MPS. All Rights Reserved.

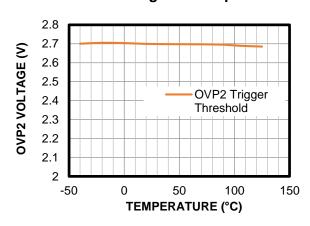

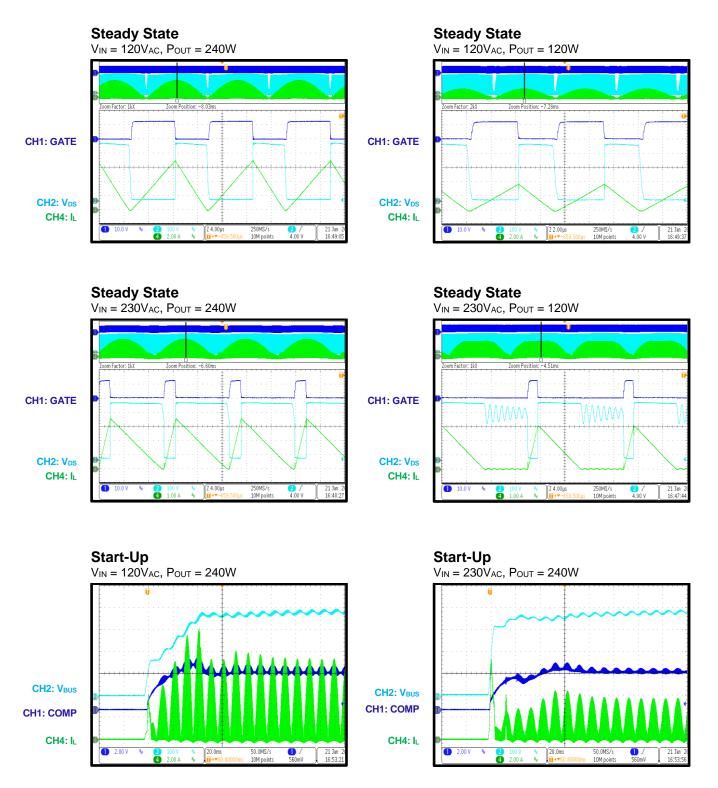

$V_{IN} = 85V_{AC}$  to  $265V_{AC}$ ,  $V_{OUT} = 400V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

$V_{IN} = 85V_{AC}$  to 265 $V_{AC}$ ,  $V_{OUT} = 400V$ ,  $T_A = 25$ °C, unless otherwise noted.

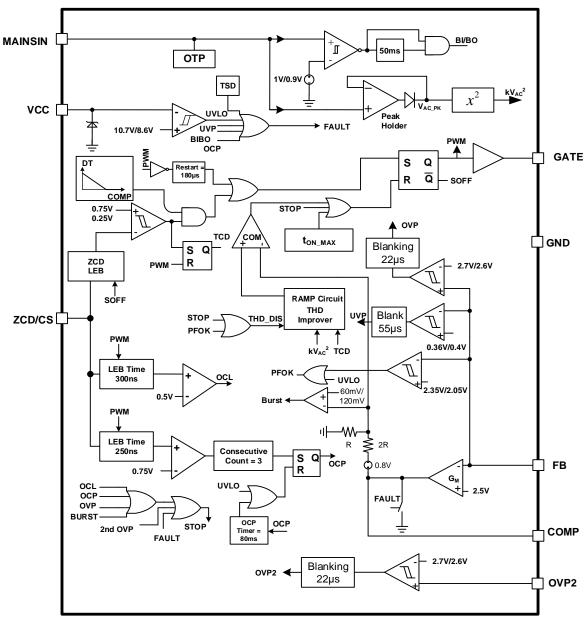

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

# **OPERATION**

The MP44019 is designed to provide simple, high-performance active power factor correction (PFC) using minimal external components. CrM/DCM multi-mode allows the MP44019 to operate in transitional modes under heavy loads. Multi-mode allows the device to convert seamlessly into discontinuous conduction mode (DCM) under light loads, which maximizes operating efficiency.

The MP44019 features a very low supply current, which meets typical standby power requirements. The no-load power loss is usually below 50mW.

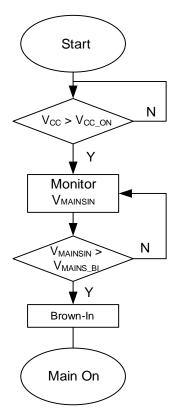

#### Start-Up and Brown-In

Figure 2 shows the typical start-up timing diagram.

As  $V_{CC}$  gradually builds up and reaches  $V_{CC\_ON}$  (typically 10.7V) at t1, the IC is enabled. Then the IC starts to sense the brown-in condition through MAINSIN. When the sampled peak voltage exceeds  $V_{MAINS\_BI}$  (typically 1V), the device starts to switch at t2. The MP44019 implements a COMP soft start-up, and the bus voltage achieves its regulation voltage at t3.

Figure 2: Start-Up and Brown-In/Brownout

#### **Brownout Function**

The AC peak voltage is continuously sensed by MAINSIN. Because the AC peak voltage falls below  $V_{\text{MAINS\_BO}}$  (typically 0.9V) at t4, the device continues switching until the brownout timer

(typically 50ms) ends at t5. Then the IC confirms the brownout condition.

At this point, the PFC stops switching and COMP is pulled down to 0V. The device restarts with a COMP soft start if the peak MAINSIN voltage exceeds V<sub>MAINS\_BI</sub> (typically 1V).

# **Enhanced Dynamic Response**

The boost PFC output voltage is sensed on FB, and is compared with the internal reference ( $V_{REF}$ , typically 2.5V) (see Figure 13 on page 19).  $R_{O1}$  is recommended to be  $10M\Omega$  to minimize power consumption.  $R_{O2}$  can be calculated with Equation (1):

$$R_{O2} = \frac{R_{O1} \times V_R}{V_{OUT} - V_R} \tag{1}$$

The voltage compensation tank is connected from COMP to GND. Proportional integral (PI) control with a high-frequency pole is typically used for compensation.

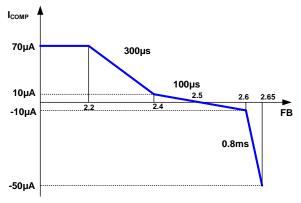

Figure 3 shows a nonlinear  $G_M$ , which achieves both excellent loop regulation in steady state and enhanced dynamic response during load transient. If the output voltage is detected with an undershoot of 4%, the gain increases to four times the normal gain. A higher gain can pull up COMP quickly and reduce the voltage drop during the load step.

Figure 3: Nonlinear G<sub>M</sub>

If the output voltage is above or below the normal voltage with an overshoot of 4%, the gain increases to eight times the normal gain. This ensures that COMP is quickly pulled down to avoid triggering over-voltage protection (OVP).

#### **Valley Switching**

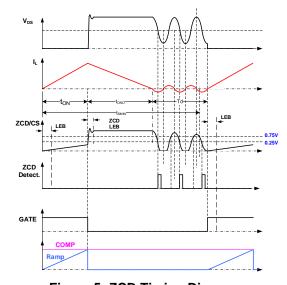

To minimize the switching loss, the MP44019 always achieves valley switching through zero-current detection (ZCD) under any condition, regardless of DCM or CRM. A leading edge blanking time ( $t_{\text{ZCD\_LEB}}$ , typically 0.3 $\mu$ s) is inserted to filter out the noise on ZCD after the gate turns off

The positive voltage on ZCD must exceed  $V_{ZCD\_H}$  (typically 0.75V) then drop below  $V_{ZCD\_L}$  (typically 0.25V) for the next trigger condition. Besides the ZCD trigger condition, the actual turn-on action should also wait for the end of the dead time extension (DTE) signal (see the Frequency Reduction function below for more details). When the DTE signal ends, and the conditions to trigger ZCD are fulfilled, the controller switches on the MOSFET after a delay time ( $t_{ZCD\_DELAY}$ , typically 150ns) at the minimum drain-source voltage.

The auxiliary winding turn ratio is determined by a sufficient positive voltage. V<sub>AUX\_MIN</sub> can be estimated with Equation (2):

$$V_{AUX\_MIN} = \frac{1}{2} \times \left( \frac{V_{OUT} - \sqrt{2} \times V_{AC\_MAX}}{N} - V_F \right) \ge V_{\text{ZCD\_H}}$$

(2)

Where  $V_F$  is the forward voltage of  $D_Z$  (typically 0.7V). The winding ratio (N) can then be calculated with Equation (3):

$$N \le \frac{V_{OUT} - \sqrt{2} \times V_{AC\_MAX}}{2 \times V_{ZCD\ H} + V_F} \tag{3}$$

Where  $V_{AC\_MAX}$  is the input's maximum RMS voltage.

A restart timer-out ( $t_{ZCD\_TO}$ , typically 180µs) generates a signal to turn on the MOSFET after it switches off. This allows the MOSFET to turn on during start-up, since no valley signal can be detected on ZCD.

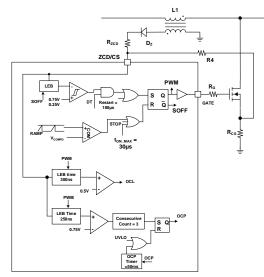

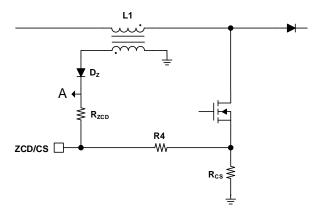

Figure 4 shows the internal function block, as well as its peripheral circuit.

Figure 4: ZCD Functional Block

Figure 5 shows the ZCD timing diagram.

Figure 5: ZCD Timing Diagram

# **Frequency Reduction Function**

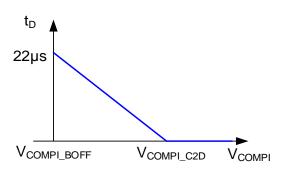

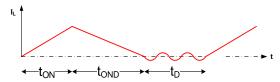

The MP44019 reduces the switching frequency with DTE technology under light loads. The MP44019 works in CrM under heavy loads. In CrM, the PFC's frequency increases as the load is decreased, which means the switching loss becomes dominant. The MP44019 gradually inserts a dead time  $(t_{\text{D}})$  as the load becomes lighter.

Figure 6 shows how the dead time is extended when the COMP voltage drops.

Figure 6: Dead Time Extension

The maximum dead time ( $t_{DEAD\_MAX}$ ) is 23µs. During this time, COMP reaches its minimum voltage and linearly approaches 0V as the internal COMP ( $V_{COMPI}$ ) reaches its threshold ( $V_{COMP\_C2D}$ , typically 0.38V).

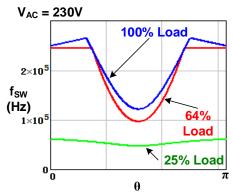

With this control scheme, the system smoothly alternates between CrM and DCM as the load is gradually reduced. This means the switching frequency is automatically reduced for maximum efficiency. Figure 7 shows how the switching frequency changes in a line cycle.

Figure 7: Switching Frequency in a Line Cycle

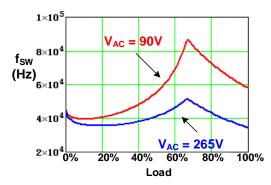

Figure 8 shows the relationship between the switching frequency and the load.

Figure 8: Switching Frequency vs. Load

#### **Burst Mode Operation**

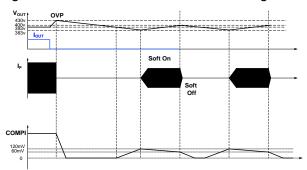

Figure 9 shows a burst mode control diagram.

Figure 9: Burst Mode Control

Depending on how the COMP voltage indicates the load information, the device enters DCM. The device only enters burst mode under certain loads to improve light-load efficiency and reduce standby power loss.

As the load decreases, COMP gradually drops. When  $V_{\text{COMPI}}$  drops below  $V_{\text{COMPI}}$  (typically 60mV), switching stops with five soft-off pulses. As  $V_{\text{COMPI}}$  ramps up to  $V_{\text{COMPI}}$  bon (typically 120mV), switching resumes with five soft-on pulses. This soft-on/off control avoids abrupt inductor current changes, and attenuates the acoustic noise accordingly.

During the burst-off period, the IC shuts down most of internal block to ensure that the supply current is below  $I_Q$  (typically 180µA).

#### Improved THD

Under heavy loads, the MP44019 works in CrM. The average input current in one cycle can be estimated with Equation (4):

$$I_{IN}(\theta) = \frac{V_{AC}(\theta)}{2 \times L} \times t_{ON}(\theta) = \frac{V_{AC}(\theta)}{R_{EQ1}}$$

(4)

Where  $V_{AC}$  is the RMS of the line voltage, calculated with Equation (5):

$$V_{AC}(\theta) = \sqrt{2} \times V_{AC} \times \sin(\theta)$$

(5)

And  $R_{EQ1}$  is the equivalent input resistor, which can be can be calculated with Equation (6):

$$R_{EQ1} = \frac{2 \times L}{t_{ON}(\theta)}$$

(6)

Where  $t_{ON}(\theta)$  is the on time.

Since  $t_{ON}$  ( $\theta$ ) is generated by an internal ramp current that is compared to the COMP voltage,  $t_{ON}$  ( $\theta$ ) stays constant throughout one AC line cycle. Meanwhile,  $R_{EQ}$  behaves like a resistor load. This means the average input current is proportional to  $V_{AC}$  ( $\theta$ ).

Along with reducing the load, the MP44019 gradually works from CrM to DCM to reduce the switching loss under light loads.

Figure 10: DCM

The average input current in one cycle can be estimated with Equation (7):

$$I_{IN}(\theta) = \frac{v_{AC}(\theta)}{2 \times L} \times t_{ON}(\theta) \times D_{C}(\theta) = \frac{v_{AC}(\theta)}{R_{EO2}}$$

(7)

Where R<sub>EQ2</sub> can be estimated with Equation (8):

$$R_{EQ2} = \frac{2 \times L}{t_{ON}(\theta) \times D_{C}(\theta)}$$

(8)

And D<sub>C</sub> can be estimated with Equation (9):

$$D_{C}(\theta) = \frac{t_{ON} + t_{OND}}{t_{ON} + t_{OND} + t_{D}}$$

(9)

A dedicated, variable on time control circuit is integrated into the device.  $t_{ON}$  can be calculated with Equation (10):

$$t_{ON}(\theta) = \frac{\varepsilon}{D_{C}(\theta)}$$

(10)

Where  $\varepsilon$  is a constant defined by the internal parameters.  $R_{EQ2}$  can be estimated with Equation (11):

$$R_{EQ2} = \frac{2 \times L}{\varepsilon}$$

(11)

$R_{EQ2}$  also behaves like a resistor load, and the input average current is proportional to  $V_{AC}$  ( $\theta$ ).

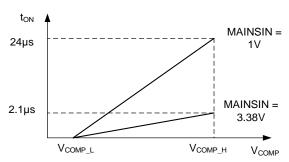

#### **Mains Compensation**

The input power for the boost PFC converter can be calculated with Equation (12):

$$P_{IN} = \frac{V_{AC}^2}{2 \times L} \times t_{ON}$$

(12)

This means that the AC transient response is suboptimal due to the square of the mains input voltage.

The COMP voltage ( $V_{COMP}$ ) can be estimated with Equation (13):

$$V_{COMP} \approx \frac{1}{V_{AC}^2}$$

(13)

$V_{\text{COMP}}$  varies between low-line and high-line. For general designs, the burst mode load is determined by  $V_{\text{COMP}}$ . In high-line, the converter enters burst mode even under heavy loads. The audible noise is created accordingly.

To compensate for the mains input voltage influence, the MP44019 contains a square of  $V_{AC}$  compensation circuits. The AC peak voltage is sensed at MAINSIN, and is fed to the generation of the internal ramp current.

The internal COMP voltage can be estimated with Equation (14):

$$V_{COMPI} = 4 \times L \times P_{IN} \times \frac{K_{MAIN}^{2}}{K_{RAMP}}$$

(14)

Where  $K_{MAIN}$  is the voltage divider ratio of MAINSIN, and  $K_{RAMP}$  is equal to  $t_{ON\_LL}$  (typically  $24\mu s/V$ ).

Figure 11 shows the relationship between  $t_{\text{ON}}$  and COMP.

Figure 11: ton vs. COMP

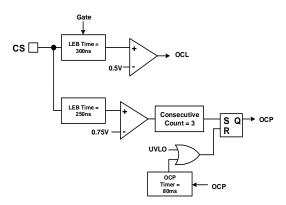

#### Over-Current Limit (OCL)

Figure 12 shows the block diagram for overcurrent limit (OCL) and over-current protection (OCP). The current is sensed by the CS pin. The device can limit the current cycle by cycle when CS exceeds  $V_{\rm OCL}$  (0.5V).

An LEB time (t<sub>OCL LEB</sub>) of 300ns is applied during OCL to avoid mistriggering OCL due to a spike current raised by discharging the drain-source capacitor of the MOSFET.

Figure 12: OCL and OCP

### **Over-Current Protection (OCP)**

A second over-current protection (OCP) is also integrated in the CS pin with a shorter LEB time (t<sub>OCP LEB</sub>) of 250ns. If the CS voltage exceeds V<sub>OCP</sub> (typically 0.75V) for two consecutive 180µs restart switching cycles, the OCP flag is triggered, and the IC stops switching. OCP is reset by an auto-recovery timer (t<sub>OCP R</sub>) of 80ms, as well as the following events: brownin, brownout, and V<sub>CC</sub> UVLO. OCP only protects the device from certain faults, such as an inductor short or a bypass diode short.

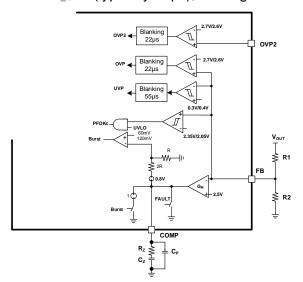

# Under-Voltage Protection (UVP) and Over-**Voltage Protection (OVP)**

The scaled-down voltage is connected to FB, which is the input of the under-voltage protection (UVP) and over-voltage protection (OVP) comparators, as well as the error amplifier.

Figure 13 shows that if the FB voltage (V<sub>FB</sub>) exceeds the OVP trigger threshold (typically 2.7V), the OVP comparator shuts down the output of the gate drive circuit after a blanking time (t<sub>BL OVP</sub>) of 22µs. Switching resumes when V<sub>FB</sub> drops to 2.62V.

The UVP comparator shuts down if V<sub>FB</sub> drops below 0.36V for a blanking time (t<sub>BL\_UVP</sub>) of 55µs. The UVP comparator's hysteresis is 40mV.

If UVP is triggered, COMP is discharged to zero, and the device's supply current is reduced to a minimum.

The UVP function can disable switching if FB is open, or if the FB feedback loop is open.

The UVP and OVP comparators values are described below:

- OVP: V<sub>FB</sub> rises above 108% of V<sub>REF</sub>. Normal operation resumes when V<sub>FB</sub> drops below 104% of V<sub>REF</sub>.

- UVP: V<sub>FB</sub> falls below 12% of V<sub>REF</sub>. Normal operation resumes when V<sub>FB</sub> rises above 16% of VRFF.

# Second Over-Voltage Protection (OVP2)

The scaled-down voltage is connected to the OVP2 pin. A second over-voltage protection (OVP2) is used for applications with a high ripple, or for a redundant protection for open loops on the FB pin. The comparator's threshold for OVP2 is 108% of V<sub>REF</sub>, with a hysteresis of 4%.

The second OVP comparator shuts down the output of the gate drive circuit after a blanking time of t<sub>BL\_OVP2</sub> (typically 23µs), see Figure 13.

Figure 13: FB Functional Block

#### **Gate Driver**

The IC includes a push-pull gate driver that can directly drive the MOSFET. The peak source current is 600mA, and the peak sink current capability is 1A.

### APPLICATION INFORMATION

#### **Design Requirements**

Table 1 lists recommended design requirements.

**Table 1: Recommended Designs**

| Parameter                    | Symbol          | Value                                   |

|------------------------------|-----------------|-----------------------------------------|

| Input AC RMS voltage         | V <sub>AC</sub> | 85V <sub>AC</sub> to 265V <sub>AC</sub> |

| Input AC voltage             | fune            | 47Hz to                                 |

| frequency                    | ·LINE           | 63Hz                                    |

| Output voltage               | Vout            | 400V                                    |

| Output voltage ripple        | Vo_ripple       | ≤3% V <sub>OUT</sub>                    |

| Output voltage OVP threshold | ΔOVP            | 40V                                     |

| Output power                 | Роит            | 240W                                    |

| Efficiency                   | η               | ≥93%                                    |

# Power Stage Design

# Selecting the Bridge

The diode bridge should withstand the maximum reverse input AC voltage and the maximum input current. When selecting a diode bridge, consider the maximum instantaneous voltage (the peak voltage of the line voltage) and the maximum input RMS current (the input RMS current at low-line). In addition, the package size and thermal performance should also be considered. To handle the line frequency current, use a standard, low-cost diode bridge with a slow recovery.

In this case, the maximum input RMS current can be calculated with Equation (15):

$$I_{AC\_MAX} = \frac{P_{OUT}}{\eta_{MIN} \times V_{AC\_MIN}} = 3.04(A)$$

(15)

The maximum instantaneous voltage can be estimated with Equation (16):

$$V_{IN MAX} = \sqrt{2} \times V_{AC MAX} = 375(V)$$

(16)

A standard 600V/8A bridge can be selected to provide enough margin.

## Selecting the Input Capacitor

The input capacitor that is placed before the boost inductor provides a bypass path for the high switching frequency current and minimizes fluctuation on the rectified sinusoidal input voltage. In general, a voltage drop up to 10% on the input capacitor may be expected. The worst-case condition occurs when the input voltage is below its minimum threshold voltage due to a

large current ripple.

The input capacitor  $(C_{IN})$  can be calculated with Equation (17):

$$C_{IN} = \frac{I_{AC\_MAX}}{2\pi \times f_{SW} \times r \times V_{AC\_MIN}}$$

(17)

Where r is the coefficient (0.01 to 0.1), and  $f_{SW}$  is the switching frequency at the peak of the minimum input AC voltage.

Select a capacitor with good high-frequency performance, such as a film capacitor. For example, assume a minimum  $f_{SW}$  (e.g. 40kHz) and set r to be 0.05. Then the input capacitance can be calculated with Equation (18):

$$C_{IN} = \frac{I_{AC\_MAX}}{2\pi \times f_{SW} \times r \times V_{AC\_MIN}} = 2.85 \mu F \quad (18)$$

Two 1µF film capacitors with a 450V voltage rating are recommended to act as the input capacitors because they provide high-frequency energy during the switching cycle.

# **Boost Inductor Design**

The boost inductance value (L<sub>MAX</sub>), which is required to ensure that the maximum load can be delivered from the minimum input voltage, can be estimated with Equation (19):

$$L_{MAX} = \frac{V_{AC\_MIN}^2 \times \eta \times t_{ON\_MAX}}{2 \times P_{OUT}}$$

(19)

The boost inductance value should be below  $L_{\text{MAX}}$ . A normal inductance is recommended to use a 60% to 70% ratio for  $L_{\text{MAX}}$  to avoid  $t_{\text{ON}}$  being close to  $t_{\text{ON}}$  MAX.

If the ratio is selected to be 60%, the actual inductance can be calculated with Equation (20):

$$L_{ACTUAL} = \frac{V_{AC\_MIN}^2 \times \eta \times t_{ON\_MAX} \times Ratio}{2 \times P_{OUT}} = 182 \mu H \qquad (20)$$

The boost inductance value should exceed  $L_{\text{MIN}}$ . To avoiding triggering over-current protection (OCP) when triggering the over-current limit (OCL), there is a delay time ( $t_{\text{CS\_DELAY}}$ ) of 100ns, as well as a MOSFET turn-off delay.

The minimum boost inductance can be estimated with Equation (21):

$$L_{MIN} = \frac{\sqrt{2}V_{AC\_MAX} \times 300ns}{V_{OCP\ OCL}} \times R_{CS} = 37.5 \mu H (21)$$

# Selecting the Boost MOSFET

The voltage rating of the MOSFET is determined by the output voltage, over-voltage protection (OVP) threshold, and a margin, such that  $V_{DS} > V_O + \Delta V_{OVP}$ . The current rating of the MOSFET is determined by the RMS value of the current flowing through the MOSFET.

V<sub>DS</sub> can be calculated with Equation (22):

$$V_{DS} > V_{OUT} + \Delta V_{OVP} = 440V \tag{22}$$

The RMS current of MOSFET can be estimated with Equation (23):

$$I_{QRMS} = 2\sqrt{2} \times I_{AC\_MAX} \times \sqrt{\frac{1}{6} - \frac{4\sqrt{2}}{9\pi}} \times \frac{V_{AC\_MIN}}{V_{OUT}} = 3A$$

(23)

In addition, the MOSFET pulse-drain current should exceed the peak inductor current, calculated with Equation (24):

$$I_{D \text{ PULSE}} > I_{LPK \text{ MAX}} = 2\sqrt{2} \times I_{AC \text{ MAX}} = 8.6A$$

(24)

#### Selecting the Boost Diode

The boost diode should have the same voltage rating as the boost MOSFET.

The average current of the output diode is the same as the output current of the PFC regulator, calculated with Equation (25):

$$I_{DAVG} = I_{OUT} = 0.6A \tag{25}$$

To estimate the power consumption of the diode, the RMS current can be calculated with Equation (26):

$$I_{DRMS} = 2\sqrt{2} \times I_{AC\_MAX} \times \sqrt{\frac{4\sqrt{2}}{9\pi}} \times \frac{V_{AC\_MIN}}{V_{OUT}} = 1.82A (26)$$

The boost diode must have an average and RMS current ratings that exceed  $I_{\text{DAVG}}$  and  $I_{\text{DRMS}},$  respectively.

Diodes are available with a range of different speed and recovery charges. Fast diodes typically have higher conduction loss but lower switching loss. Slow diodes typically have lower conduction loss but higher switching loss. Maximum efficiency is achieved when the diode speed rating matches the application. In this case, a boost diode with a fast recovery is

recommended.

#### Selecting the Output Capacitor

When selecting an output capacitor, consider the output voltage ripple ( $V_{O\_RIPPLE}$ ), ripple current rating, and hold-up time.

The output ripple is a function of the effective series resistance (ESR) of the capacitor, the output voltage, and the line frequency (f<sub>LINE</sub>). The output ripple can be estimated with Equation (27):

$$V_{O\_RIPPLE} = 2x \frac{P_{OUT}}{V_{OUT}} x \sqrt{\frac{1}{(2\pi \times 2f_{LINE} \times C_{OUT})^2} + ESR^2} (27)$$

In this case, the calculated ripple with the selected capacitor should be below 3% of the output voltage, and the ESR of the output capacitor is assumed to be  $1\Omega$ .  $C_{OUT}$  can be calculated with Equation (28):

$$C_{OUT} \ge \frac{1}{2\pi x 2 f_{LINE} \sqrt{\left(\frac{3\% \times V_{OUT}^2}{2x P_{OUT}}\right)^2 - ESR^2}} = 160 \mu F$$

(28)

To ensure that the error amplifier's nonlinear gain is not activated by the extremes of the output voltage ripple, the output voltage ripple amplitude should satisfy the condition calculated with Equation (29):

$$\frac{V_{O\_RIPPLE}}{V_{OUT}} \le \frac{2x100mV}{V_R} = 8\%$$

(29)

The maximum RMS ripple current flowing in the output capacitor can be estimated with Equation (30):

$$I_{O\_RIPPLE\_MAX} = \sqrt{I_{DRMS}^2 - \left(\frac{P_{OUT}}{V_{OUT}}\right)^2} = 1.72A$$

(30)

This current flowing into the output capacitor is made up of a switching frequency component (50Hz) and a twice-line frequency ripple component (100kHz), calculated with Equation (31) and Equation (32), respectively:

$$I_{O\_RIPPLE\_50Hz} = \frac{1}{\sqrt{2}} x \frac{P_{OUT}}{V_{OUT}} = 0.424A$$

(31)

$$I_{O\_RIPPLE\_100KHz} = \sqrt{I_{DRMS}^2 - \frac{3}{2} x \left(\frac{P_{OUT}}{V_{OUT}}\right)^2} = 1.67A$$

(32)

The capacitor should be chosen so that the holdup time satisfies the relationship calculated with Equation (33):

$$C_{OUT} = \frac{2 \cdot P_{OUT} \times t_{HOLDUP}}{\eta \times (V_{OUT}^2 \cdot V_{O}^2 + HOLDUP)}$$

(33)

Where  $V_{\text{OUT}}$  is the minimum output voltage under all normal operating conditions, and  $V_{\text{O\_HOLDUP}}$  is the required minimum operating output voltage to supply the downstream DC/DC converter when the line voltage is shut down. The maximum voltage at the output is a combination of the output voltage, output voltage ripple, and OVP threshold. Therefore, the voltage rating of the capacitor must exceed this maximum output voltage under the worst-case conditions.

In this example design, an aluminum electrolytic capacitor with a specification of  $450V/180\mu F$  is recommended.

# **Control Circuit Design**

#### The VCC Pin

If an external VCC power supply is not used, initiate start-up by connecting a start-up resistor to the input AC voltage. As the VCC capacitor's charge rises above the turn-on threshold through the start-up resistor, the IC begins to work.

The MP44019 requires a minimum 40µA start-up current when VCC is 9.5V. The start-up resistance can be calculated with Equation (34):

$$R_{STARTUP} \le \frac{\sqrt{2x}V_{AC\_MIN}-9.5}{I_{STARTUP}} = 2.9M\Omega$$

(34)

Since the start-up resistor causes a voltage drop between the input AC voltage and the supply voltage of the chip, use a resistor with a higher resistance to minimize the power consumption.

#### The FB Pin

V<sub>OUT</sub> can be set by connecting resistors to the FB pin. Output voltage regulation accuracy degrades with higher-value resistors due to the effect of the FB bias current. Ensure that the FB bias current degrades the output voltage regulation by less than 1%. Calculate the upper voltage resistor divider value with Equation (35):

$$R_{O\_UPPER} \le 1\%x \frac{V_{OUT}}{I_{O\_BIAS}} = 40M\Omega$$

(35)

Considering the power consumption, it is recommended to use three  $3.3M\Omega$  resistors in series for the FB upper voltage resistor divider.

The lower voltage resistor divider value can be calculated with Equation (36):

$$R_{O\_LOWER} = \frac{V_R}{V_{O_{II}} - V_R} x R_{O\_UPPER} = 62.3 k\Omega \qquad (36)$$

#### The MAINSIN Pin

The MAINSIN voltage range (as related to the  $V_{AC}$  range) is between 1V and 3.38V. In this case, a voltage of  $85V_{AC}$  can be set as the brown-in voltage. The MAINSIN voltage divider can be calculated with Equation (37):

$$\frac{R_{I\_LOWER}}{R_{I\_LOWER} + R_{I\_UPPER}} = \frac{V_{MAINS\_BI}}{V_{AC\_MIN}} = \frac{1}{120}$$

(37)

Considering the power consumption, a higher-value resistor is recommended. In this scenario, it is recommended to place three  $3.3 M\Omega$  resistors in series for the MAINSIN upper voltage resistor divider.

The lower voltage resistor divider value can be calculated with Equation (38):

$$R_{I\_LOWER} = \frac{R_{I\_UPPER}}{120-1} = 83.2k\Omega$$

(38)

#### The ZCD/CS Pin

The ZCD/CS pin provides a current-sense function as well as zero-current detection (ZCD). Figure 14 shows the ZCD/CS pin connection.

Figure 14: ZCD/CS connection

CS is used for OCP and OCL. The current flowing through the MOSFET should be below the over-current limit threshold. The current-sense resistor on the CS pin can be calculated with Equation (39):

$$R_{CS} \le \frac{V_{OCL}}{2 \times \sqrt{2} \times I_{AC MAX}} = 58 \text{m}\Omega$$

(39)

In this case, it is recommended to place two  $100m\Omega$  2512 SMT resistors in parallel.

To enhance the anti-interference ability, a  $1k\Omega$  resistor is connected in series to CS. In addition, to pass the surge test, ZCD winding is connected to the ZCD/CS pin through a diode, and  $R_{ZCD}$  can be used to obtain the valley signal of the drain voltage. Generally,  $R_{ZCD}$  is designed to be equal to R4 (for example,  $R_{ZCD} = R4 = 4.7k\Omega$ ).

A leading edge blanking time of  $t_{ZCD\_LEB}$  (typically 0.3µs) is inserted to filter out the noise ringing on ZCD winding just after gate turns off.

The auxiliary winding turn ratio can be calculated with Equation (40):

$$N \leqslant \frac{V_{\text{OUT}} - \sqrt{2} \times V_{\text{AC}}}{2 \times V_{\text{ZCD}}} = 9.6 \tag{40}$$

Where  $V_{AC\_MAX}$  is 265 $V_{AC}$ .

In this scenario, 26:3 is selected as the winding ratio.

If the reflected voltage on ZCD winding is below  $V_{ZCD\_L}$  (typically 0.25V) after the gate turns off, the AC input voltage can be estimated with Equation (41):

$$V_{AC\_LIMIT} \geqslant \frac{V_{OUT} - N \times (2 \times V_{ZCD\_L} + V_F)}{\sqrt{2}} = 273 \qquad (41)$$

Erratic switching may occur if the AC source is tuned above  $V_{\text{AC\_LIMIT}}$ . In this scenario, a voltage spike exceeding 0.75V may be generated when the gate turns off. If this spike lasts for longer than  $t_{\text{ZCD\_LEB}}$  (typically 0.3 $\mu$ s), this means that the turn-on condition is a result of this spike. The device immediately starts to counter the timer for a dead time extension while ignoring the turn-off time. Finally, this switching cycle becomes shorter than a normal cycle.

There are three recommendations to attenuate the spike. This first recommendation is to use a lower resistance for  $R_{ZCD}$  and R4 (e.g. a  $3k\Omega$  resistor with a 1206 package).

A second solution is to choose a FET with a shorter turn-off delay time and turn-off time. The final recommendation is to increase the BUS voltage.

## The OVP2 Pin

The second OVP voltage ( $V_{OVP2} = V_{OUT} + \Delta OVP$ ) can be set by the OVP2 resistors.

Normally, it is recommended to use three  $3.3M\Omega$

resistors in series for the upper voltage resistor dividers of OVP2.

The lower voltage resistor divider can be estimated with Equation (42):

$$R_{OV2} = \frac{V_{OVP2} \times V_{FB\_OVP2}}{V_{OVP2} \cdot V_{FB\_OVP2}} \times R_{OV1} = 61 \text{k}\Omega \quad (42)$$

#### The COMP Pin

Based on the small signal model, the control to output voltage transfer function (resistive load) can be estimated with Equation (43):

$$G_{VC}(s) = \frac{\kappa_{RAMP}}{3 \times \kappa_{MAIN}^2} x \frac{1}{2 \times V_{OUT} \times C_{OUT} \times L} x \frac{1}{\frac{2}{R_O \times C_{OUT}} + s}$$

(43)

Where  $K_{MAIN}$  is the MAINSIN voltage divider ratio, and  $K_{RAMP}$  is equal to  $t_{ON\_LL}$ .

In this scenario,  $G_{VC}$  can be calculated with Equation (44):

$$G_{VC}(s) = \frac{4706.67}{s+16.67}$$

(44)

In addition, the voltage error amplifier is a transconductance amplifier. The voltage compensation tank is connected from COMP to GND. A Type-II compensation network is recommended. The transfer function of the transconductance amplifier can be calculated with Equation (45):

$$G_{EA}(s) = K_{FB}xG_{M1}x\frac{1}{C_{P}xs}x\frac{\frac{1}{C_{Z}\times R_{Z}}+s}{\frac{C_{Z}+C_{P}}{C_{Z}\times C_{P}\times R_{Z}}+s}$$

(45)

Where  $K_{FB}$  is the FB voltage divider ratio, and  $G_{M1}$  is the transconductance value (typically 105 $\mu$ s).

The open voltage loop transfer function can be calculated with Equation (46):

$$G(s) = G_{VC}(s)xG_{FA}(s)$$

(46)

In this scenario, to design a high-stability voltage loop, it is recommended to make the crossover frequency 12Hz, as the phase margin must exceed 45°. 5Hz is the recommended zero value, and 50Hz should be selected as the pole with high frequency.

The value of the compensation network can be calculated with Equation (47):

$$R_Z = \frac{1}{K_{FB} \times G_{M1}} \times 10^{\frac{-\Phi_{VC}(12)}{20}} = 28.5 \text{k}\Omega$$

(47)

Where  $C_Z$  can be estimated with Equation (48):

$$C_Z = \frac{1}{2\pi x 5 x R_Z} = 1.1 \mu F$$

(48)

And C<sub>P</sub> can be estimated with Equation (49):

$$C_P = \frac{1}{2\pi x 50 x R_7} = 0.1 \mu F$$

(49)

For this compensation network, it is recommended for  $R_Z=30k\Omega,\ C_Z=1\mu F,$  and  $C_P=220pF$

# **PCB Layout Guidelines**

PCB layout is critical for stable operation and EMI performance, as the device can malfunction due to noise coupling. For the best results, refer to Figure 15 and follow the guidelines below:

- 1. Make power loop 1 and power loop 2 as small as possible.

- 2. Do not place the IC in power loop 1 or power loop 2.

- Make the areas of high dV/dt junctions (e.g. the drain of the external primary MOSFET) as small as possible. Place the IC and control circuits far away from these areas.

- Separate the reference ground of the IC and control signals circuit from the ground of the power loop. Then connect this signal ground to the ground of the output capacitor with a single-point junction.

- 5. Connect the VCC-to-GND capacitor close to IC.

- 6. Connect the FB-to-GND and OVP2-to-GND capacitors close to the IC.

- Connect the MAINS-to-GND capacitor close to the IC. Ensure that the CS wiring does not cross MAINSIN. Otherwise, the CS noise may couple to MAINSIN and impact peak voltage sensing.

- If the PFC stage is connected to a cascade DC/DC stage, separate both GNDs with an output capacitor, so that GND noises do not interfere with one another.

Figure 15: Recommended PCB Layout

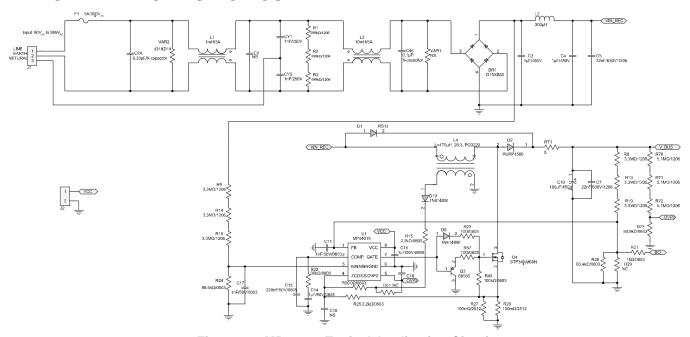

# **TYPICAL APPLICATION CIRCUIT**

Figure 16: MP44019 Typical Application Circuit

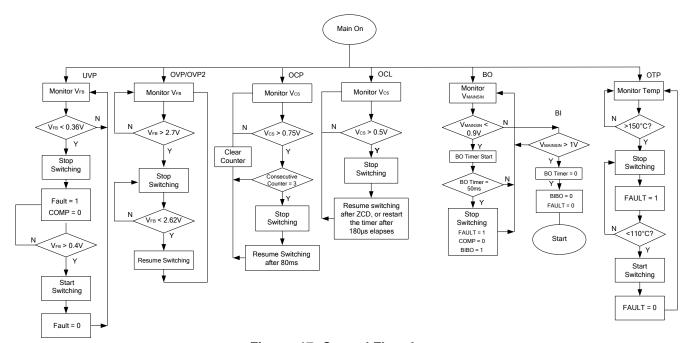

# **CONTROL FLOWCHART**

Figure 16: Start-Up Flowchart

Figure: 17: Control Flowchart

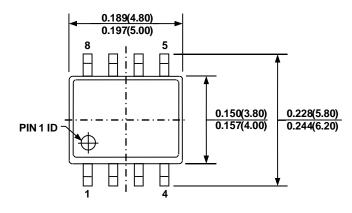

# **PACKAGE INFORMATION**

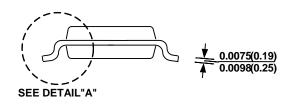

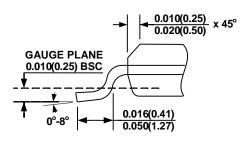

#### **SOIC-8**

#### TOP VIEW

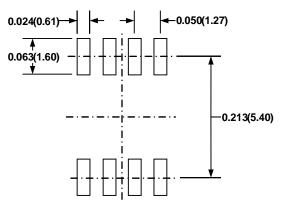

RECOMMENDED LAND PATTERN

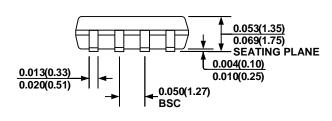

**FRONT VIEW**

**SIDE VIEW**

DETAIL "A"

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION, OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.04" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC M612, VARIATION AA

- 6) DRAWING IS NOT TO SCALE.

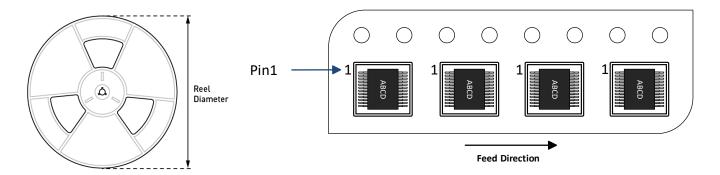

# **CARRIER INFORMATION**

| Part Number | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Quantity/<br>Tray | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|-------------|------------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|

| MP44019GS-Z | SOIC-8                 | 2500              | 100               | N/A               | 13in             | 12mm                     | 8mm                      |

# **REVISION HISTORY**

| Revision # | Revision Date | Description     | Pages Updated |

|------------|---------------|-----------------|---------------|

| 1.0        | 4/30/2021     | Initial Release | -             |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.