### **General Description**

The MAX4473 PA power control IC is intended for closed-loop bias control of GSM power amplifiers. The device facilitates accurate control of the current delivered to the power amplifier (PA) through a control voltage. The error amplifier senses the voltage drop across an external current-sense resistor placed between the supply and the PA. The output of the error amplifier adjusts the PA gain until the current is proportional to the power control voltage applied to the MAX4473. This unique topology is useful in time-division-multipleaccess (TDMA) systems, such as GSM, where accurate transmit burst shaping and power control is required. User-selectable current sensing and gain setting resistors maximize flexibility.

The MAX4473 operates from a single 2.7V to 6.5V supply and typically draws 1.2mA of supply current. The error amplifier has a common-mode range that extends from 1V to Vcc. The power control input and error amplifier outputs swing Rail-to-Rail®. A low-power shutdown mode reduces supply current to less than 1µA and activates an on-board active pull-down at the error amplifier output. Fast enable/disable times of 0.9µs reduce average power consumption without compromising dynamic performance. The MAX4473 is available in a space-saving 8-pin QFN package.

#### **Applications**

**GSM Cellular Phones Cordless Phones** Precision Current Control High-Frequency Servo Loops

#### **Features**

- **♦ Optimized for GSM Timing Requirements**

- ♦ 2.7V to 6.5V Single-Supply Operation

- ♦ 1.2mA Supply Current

- ♦ ≤1µA Supply Current in Shutdown Mode

- ♦ Guaranteed 1.5µs Enable/Disable Times

- ♦ Active Output Pull-Down in Shutdown Mode

- ♦ Rail-to-Rail Error Amplifier Output

- ♦ Rail-to-Rail Power Control Input

- ♦ Output Drive Capability—500Ω and 300pF Loads

- ♦ 1V to Vcc Current Sense Input Common-Mode Voltage Range

- ♦ No Phase-Reversal for Common-Mode Voltage from 0 to Vcc

- ♦ External Current Sensing and Gain Setting **Resistors Maximize Flexibility**

- ♦ Available in a Space-Saving 8-Pin QFN

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX4473EUA | -40°C to +85°C | 8 µMAX      |

| MAX4473ETA | -40°C to +85°C | 8 QFN       |

| MAX4473ESA | -40°C to +85°C | 8 SO        |

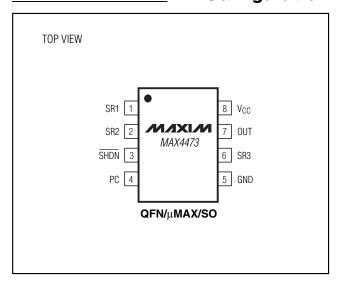

Pin Configuration appears at end of data sheet.

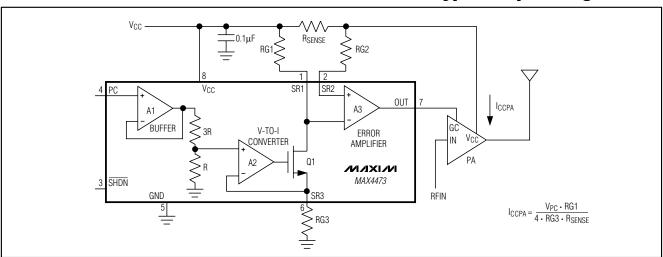

## Typical Operating Circuit

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

MIXIM

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND             | 7V                        |

|------------------------------------|---------------------------|

| SR1, SR2, SR3, PC, SHDN,           |                           |

| OUT to GND                         | 0.3V to $(V_{CC} + 0.3V)$ |

| SR1 to SR3                         | 0 to V <sub>CC</sub>      |

| OUT and SR3 Short-Circuit Duration |                           |

| to V <sub>CC</sub> or GND          | Continuous                |

| Current into Any Pin               | ±50mA                     |

|                                    |                           |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                |

|-------------------------------------------------------|----------------|

| 8-Pin µMAX (derate 4.10mW/°C above +70°C              | C)330mW        |

| 8-Pin QFN (derate 24.4mW/°C above +70°C)              | )1951mW        |

| 8-Pin SO (derate 5.88mW/°C above +70°C).              | 471mW          |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC}=2.7V\ to\ 6.5V,\ \overline{SHDN}>2.4V,\ MAX4473\ test\ circuit,\ RG1=RG2=1k\Omega\ \pm1\%,\ RG3=2.5k\Omega\ \pm1\%,\ R_{SENSE}=100\Omega\ \pm1\%,\ R_L=10k\Omega,\ C_L=300pF,\ T_A=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=6.0V,\ V_{PC}=1.0V,\ T_A=+25^{\circ}C.$ ) (Note 1)

| PARAMETER                                   |                                                              | COND                 | ITIONS                                                 | MIN      | TYP      | MAX       | UNITS   |

|---------------------------------------------|--------------------------------------------------------------|----------------------|--------------------------------------------------------|----------|----------|-----------|---------|

| GENERAL                                     |                                                              |                      |                                                        |          |          | · ·       |         |

| Supply Voltage                              |                                                              |                      |                                                        | 2.7      |          | 6.5       | V       |

| Supply Current                              | $V_{PC} = 0$                                                 |                      |                                                        |          | 1.2      | 2         | mA      |

| Shutdown Supply Current                     | SHDN < 0.4V, RL                                              | = 10kΩ               |                                                        |          | 0.03     | 1         | μΑ      |

| SHDN Input High Voltage                     |                                                              |                      |                                                        | 2.4      |          |           | V       |

| SHDN Input Low Voltage                      |                                                              |                      |                                                        |          |          | 0.4       | V       |

| SHDN Input Current                          | SHDN = 0 to V <sub>CC</sub>                                  |                      |                                                        |          |          | ±0.5      | μΑ      |

| ERROR AMPLIFIER                             |                                                              |                      |                                                        |          |          |           |         |

| CD1 CD0 Invest Offset Voltage               | 1V < V <sub>SR1</sub> , V <sub>SR2</sub> <                   | : V <sub>C</sub> C   |                                                        |          | ±0.5     | ±2        |         |

| SR1, SR2 Input Offset Voltage               | 1V < V <sub>SR1</sub> , V <sub>SR2</sub> <                   | V <sub>CC</sub> at   | : +25°C                                                |          | ±0.5     | ±1        | mV      |

| SR1, SR2 Input Offset Voltage Drift         | 1V < VSR1, VSR2 <                                            | : Vcc                |                                                        |          | 10       |           | μV/°C   |

| SR1, SR2 Input Common-Mode<br>Voltage Range | Inferred from CMF                                            | RR test;             | V <sub>PC</sub> = GND (Note 2)                         | 1        |          | Vcc       | V       |

| SR1, SR2 Input Bias Current                 | 1V < V <sub>SR1</sub> , V <sub>SR2</sub> < SR3 = unconnected |                      | PC = GND,                                              |          | ±0.04    | ±1        | μΑ      |

| SR1, SR2 Input Bias Offset Current          | 1V < V <sub>SR1</sub> , V <sub>SR2</sub> < SR3 = unconnected |                      | PC = GND,                                              |          | ±0.001   | ±0.2      | μΑ      |

| SR1, SR2 Shutdown Leakage Current           | SHDN < 0.4V, V <sub>SF</sub>                                 | R1 = VSF             | R2 = VCC                                               |          | ±0.001   | ±0.5      | μΑ      |

| Common-Mode Rejection Ratio                 | 1V < VSR1, VSR2 <<br>VPC = GND                               | VCC,                 | V <sub>CC</sub> = 2.7V<br>V <sub>CC</sub> = 6.5V       | 65<br>75 | 85<br>95 |           | dB      |

| Power-Supply Rejection Ratio                | 2.7V < V <sub>CC</sub> < 6.5V                                | /, V <sub>PC</sub> = |                                                        | 80       | 90       |           | dB      |

| 1.13                                        | $R_L = 10k\Omega$                                            |                      | = 6.5V, 0.3V < V <sub>OUT</sub> < 6V                   | 80       | 130      |           |         |

| Lorgo Cignal Cain                           | to Vcc / 2                                                   | Vcc                  | V <sub>CC</sub> = 2.7V, 0.3V < V <sub>OUT</sub> < 2.4V |          | 125      |           | dB      |

| Large-Signal Gain                           | $R_L = 500\Omega$                                            | Vcc                  | V <sub>CC</sub> = 6.5V, 0.7V < V <sub>OUT</sub> < 5.5V |          | 130      |           |         |

|                                             | to $V_{CC} / 2$ $V_{CC} = 2$                                 |                      | = 2.7V, 0.7V < V <sub>OUT</sub> < 2.2V                 | 80       | 120      |           |         |

| Output Voltage Swing                        | $R_L = 10k\Omega$ to $V_{CC}/2$                              |                      |                                                        | 0.15     |          | CC - 0.15 | V       |

|                                             | $R_L = 500\Omega$ to $V_{CC}$                                | /2                   |                                                        | 0.5      |          | CC - 0.5  |         |

| Output Current Limit                        | Vout = Vcc / 2                                               |                      |                                                        |          | 20       |           | mA      |

| Gain-Bandwidth Product                      | $R_L = 10k\Omega$ , $C_L = 3$                                |                      | o = 10kHz                                              |          | 2        |           | MHz     |

| Phase Margin                                | $R_L = 10k\Omega$ , $C_L = 3$                                | 300pF                |                                                        |          | 60       |           | degrees |

| Slew Rate                                   | Measured from 30 C <sub>L</sub> = 300pF                      | % to 70              | 0% of $V_{OUT}$ , $R_L = 10k\Omega$ ,                  |          | 1.8      |           | V/µs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VCC = 2.7V to 6.5V,  $\overline{\text{SHDN}}$  > 2.4V, MAX4473 test circuit, RG1 = RG2 = 1k $\Omega$  ±1%, RG3 = 2.5k $\Omega$  ±1%, RSENSE = 100 $\Omega$  ±1%, RL = 10k $\Omega$ , CL = 300pF, TA = TMIN to TMAX, unless otherwise noted. Typical values are at VCC = 6.0V, VPC = 1.0V, TA = +25°C.) (Note 1)

| PARAMETER                 | CONDITIONS                                                          | MIN   | TYP   | MAX   | UNITS |

|---------------------------|---------------------------------------------------------------------|-------|-------|-------|-------|

| Capacitive-Load Stability | No sustained oscillations (Note 3)                                  | 0     |       | 300   | pF    |

| Enable/Disable Time       | From 50% of SHDN edge to Vout = 1V, Vpc = 2V                        |       | 0.9   | 1.5   | μs    |

| GAIN CONTROL BUFFER AND   | V-TO-I CONVERTER                                                    |       |       |       |       |

| PC Input Bias Current     | GND < V <sub>PC</sub> < V <sub>CC</sub> - 0.15V                     |       | ±0.04 | ±1    | μΑ    |

| SR3 Output Current Limit  | V <sub>PC</sub> = 2.55V, SR1 = SR2 = V <sub>CC</sub>                | 0.750 | 4     |       | mA    |

| VPC to VRG1 Ratio         | Measure voltage across RG1, 0.3V < V <sub>PC</sub> < 2.55V (Note 4) | 0.095 | 0.1   | 0.105 | V/V   |

| PC Input Bandwidth        | Bandwidth from V <sub>PC</sub> to V <sub>RG1</sub>                  |       | 2     |       | MHz   |

Note 1: Limits over temperature are guaranteed by design.

**Note 2:** No output phase-reversal for input common-mode voltage range from GND to V<sub>CC</sub>. Common-mode range limited by voltage drop across Q1 and RG3.

Note 3: Guaranteed by design.

Note 4: Error dependent on tolerance of RG1, RG2, and RG3. Specified with 0.1% tolerance resistors.

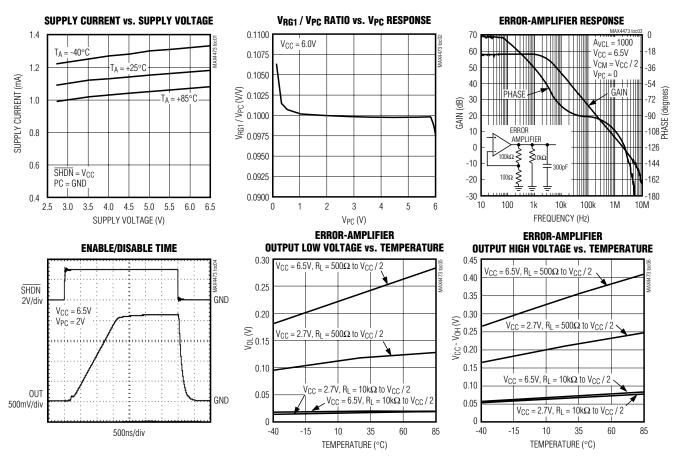

### Typical Operating Characteristics

(See *Test Circuit*, T<sub>A</sub> = +25°C, unless otherwise noted.)

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                          |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SR1  | Inverting Input of Error Amplifier and Drain of V-to-I FET, Q1. Connect to supply side of current-sense resistor, RSENSE, through gain resistor RG1.                                                                                              |

| 2   | SR2  | Noninverting Input of Error Amplifier. Connect to load side of current-sense resistor, R <sub>SENSE</sub> , through gain resistor RG2. Set RG2 equal to RG1.                                                                                      |

| 3   | SHDN | Shutdown Input. Drive SHDN low to disable all amplifiers, pull OUT to GND, set the gate-to-source voltage of the V-to-I FET (Q1) to 0, and reduce supply current to less than 1µA. Drive high or connect to V <sub>CC</sub> for normal operation. |

| 4   | PC   | Power Control Input. Apply a voltage to PC to set a DC current through the sense resistor to control PA bias.                                                                                                                                     |

| 5   | GND  | Ground                                                                                                                                                                                                                                            |

| 6   | SR3  | Inverting Input of V-to-I Converter and Source of V-to-I FET, Q1. Connect to ground through gain resistor RG3.                                                                                                                                    |

| 7   | OUT  | Output of Error Amplifier. Connect to gain control pin of power amplifier in bias control applications.                                                                                                                                           |

| 8   | Vcc  | +2.7V to +6.5V Voltage Supply Input. Bypass to ground with a 0.1µF capacitor.                                                                                                                                                                     |

### Detailed Description

The MAX4473 is a voltage-controlled, unidirectional, high-side current setting amplifier for applications where accurate control of PA supply current is desired. This device is intended for wireless TDMA based systems (GSM, DECT), where tight restrictions over the PA's transmit burst and output power require closed-loop control over the PA's output power. When used with a PA, the MAX4473 functions as a voltage-controlled constant current source, accurately setting PA supply current by varying the gain of the PA. If you know the output power versus supply current profile for the PA, you can set the PA's output power by controlling the amount of supply current delivered to the PA.

The MAX4473 is composed of an input buffer (A1), a voltage-to-current converting amplifier (A2), and a rail-to-rail output error amplifier (A3) (see *Typical Operating Circuit*). External gain and sense resistors allow programmability for a wide range of applications.

In the *Typical Operating Circuit*, PA supply current flows from the system supply, through the external current-sense resistor (RSENSE), to the PA. The rail-to-rail outputs of the error amplifier, A3, adjust the gain of the PA until the voltage drop across RSENSE equals the voltage drop across external gain resistor, RG1. The voltage drop across RG1 sets the voltage drop across RSENSE, with a larger voltage drop resulting in more current delivered to the PA. The voltage drop across RG1 is set by A1, A2, and the V-to-I FET, Q1. A voltage applied to the PC input of the input buffer is divided by

four by a resistor-divider network. A2 forces its inverting input and the source of Q1 to VPC / 4, thus setting a voltage across RG3. The resulting current through RG3 sets the current through RG1. This unique architecture allows the supply current to be set independent of supply voltage. Set PA supply current according to the following equation:

$ICCPA = (VPC \cdot RG1) / (4 \cdot RSENSE \cdot RG3)$

#### **Shutdown Mode**

When  $\overline{SHDN}$  is a logic-level low ( $\overline{SHDN}$  < 0.4V), amplifiers A1, A2, and A3 are off, Q1 is turned off, and the output of A3 is actively pulled to ground with an N-channel FET. Supply current is reduced to less than 1µA in shutdown mode. Typical power-up time is 0.9µs and typical power-down time is 0.3µs, using the MAX4473 test circuit.

## **Applications Information**

# Gain Resistor Selection (RG1, RG2, RG3)

For proper operation, do not make the value of external gain resistors RG1 and RG2 larger than twice the value of RG3. In most practical applications, choose RG1 smaller than RG3 to limit the voltage drop over RG1 and RSENSE. A large voltage drop over RSENSE substantially reduces the voltage applied to the PA, thus reducing PA output power. Set RG2 equal to RG1 to compensate for the input bias currents of A3. Recommended values for RG3 are between  $1 \mathrm{k} \Omega$  and  $10 \mathrm{k} \Omega$

#### Sense Resistor Selection (RSENSE)

Choose RSENSE based on the following criteria:

- **Voltage Loss:** A high R<sub>SENSE</sub> value causes the power-source voltage to degrade through IR loss. For minimal voltage loss, use low R<sub>SENSE</sub> values.

- Accuracy: A high RSENSE value allows lower currents to be measured more accurately because input offset voltages become less significant when the sense voltage is larger. For best performance, select RSENSE to provide approximately 100mV of sense voltage for the full-scale current in each application.

- Efficiency and Power Dissipation: At high current levels, the I<sup>2</sup>R losses in R<sub>SENSE</sub> are significant. Take this into consideration when choosing the resistor value and its power dissipation (wattage) rating. Also, the sense resistor's value may drift if it is allowed to heat up excessively.

#### **Test Circuit**

#### RSFNSF $V_{CC}$ 100Ω RG1 RG2 0.1μF $\underset{1\%}{\overset{\text{huz}}{\leqslant}} 1k\Omega$ 0.1% 1kO 1% SR1 SR2 MIXIM PC 2N3904 OUT MAX4473 SHDN SR3 GND $R_{\mathsf{F}}$ $750\Omega$ RG3 $2.5k\Omega$

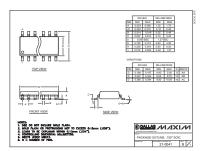

#### **Pin Configuration**

**Chip Information**

TRANSISTOR COUNT: 348

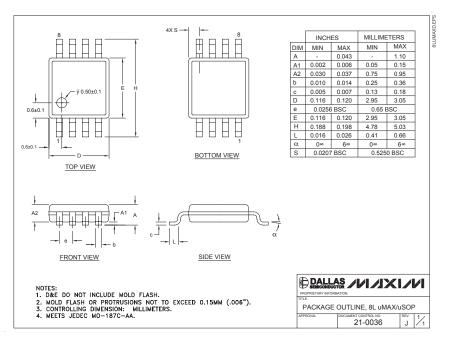

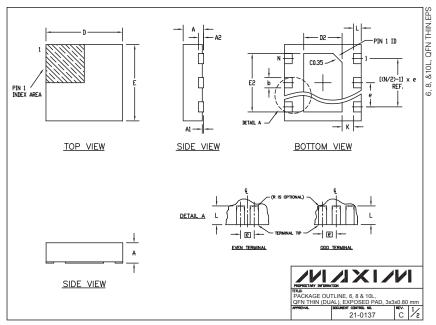

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

| COMMO               | N DIMEN | NSIONS          |                              |                           |                                      |                             |                                       |  |

|---------------------|---------|-----------------|------------------------------|---------------------------|--------------------------------------|-----------------------------|---------------------------------------|--|

| SYMBOL              | MIN.    | MAX.            |                              |                           |                                      |                             |                                       |  |

| Α                   | 0.70    | 0.80            |                              |                           |                                      |                             |                                       |  |

| D                   | 2.90    | 3.10            |                              |                           |                                      |                             |                                       |  |

| E                   | 2.90    | 3.10            |                              |                           |                                      |                             |                                       |  |

| A1                  | 0.00    | 0.05            |                              |                           |                                      |                             |                                       |  |

| L                   | 0.20    | 0.40            |                              |                           |                                      |                             |                                       |  |

| k                   | _       | 25 MIN          |                              |                           |                                      |                             |                                       |  |

| A2                  | 0.2     | 0 REF.          |                              |                           |                                      |                             |                                       |  |

| PACKAGE VAR         | N       | D2              | E2                           | е                         | JEDEC SPEC                           | b                           | [(N/2)-1] x e                         |  |

| PKG. CODE           | N       | D2              |                              | _                         |                                      | _                           | ** / /                                |  |

|                     |         |                 | E2<br>2.30±0.10<br>2.30±0.10 | e<br>0.95 BSC<br>0.65 BSC | JEDEC SPEC MO229 / WEEA MO229 / WEEC | b<br>0.40±0.05<br>0.30±0.05 | [(N/2)-1] x e<br>1.90 REF<br>1.95 REF |  |

| PKG. CODE<br>T633-1 | N<br>6  | D2<br>1.50±0.10 | 2.30±0.10                    | 0.95 BSC                  | MO229 / WEEA                         | 0.40±0.05                   | 1.90 REF                              |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.