# Data Sheet ZJC2103-14

# Precision, 14-bit 8-Channel 300 kSPS SAR ADC

### **Features**

- 14-bit resolution with no missing codes

- Throughput: 300 kSPS

- INL: ± 0.2 LSB

- DNL: ± 0.15 LSB

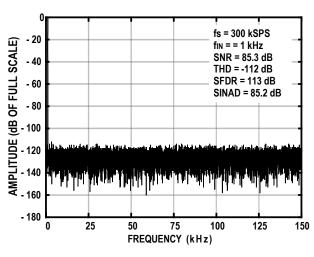

- Dynamic Range: 85.5 dB

- SNR: 85 dB

- THD: 103 dB

- Single-ended or Pseudo Differential Range: 0 V ~ VREF

- Pseudo Differential Bipolar Range: ±V<sub>REF</sub>/2

- No pipeline delay

- Single supply: 2.3 V ~ 5 V

- Logic interface: 1.8 V / 2.5 V / 3 V / 5 V

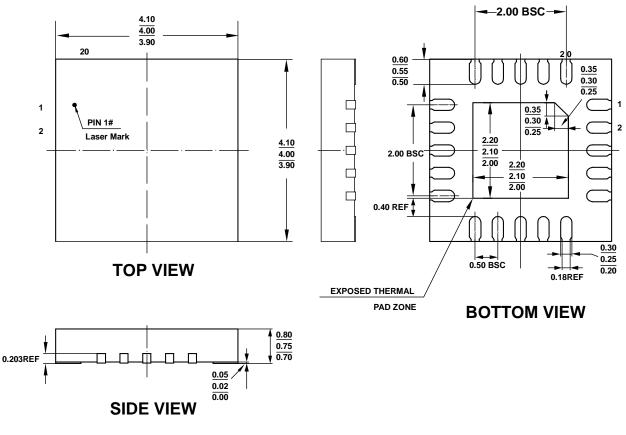

- Package: QFN-20

- Operating temp range: 40 °C to + 85 °C

## Applications

- Relay protection

- Precision data acquisition

- Automated testing

- Battery test

- Optical communication

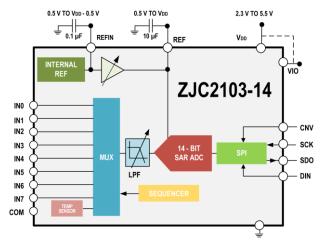

# **Block Diagram**

Figure 1. Block Diagram

### **General Description**

The ZJC2103-14 is an 8-channel, 14-bit, SAR analog-to-digital converter (ADC). It operates up to 300 kSPS from a single power supply.

The ZJC2103-14 contains a 14-bit SAR ADC with no missing codes, an 8-channel, low crosstalk multiplexer to configure the inputs as single-ended, pseudo differential unipolar or bipolar; an internal low drift reference (selectable 2.5 V or 4.096 V) and reference driver; a temperature sensor; a selectable one-pole filter; and a digital sequencer which is useful for channels being continuously scanned in order.

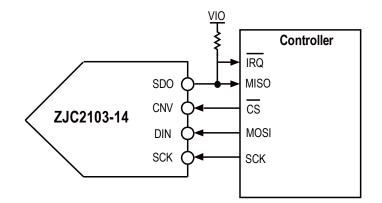

The ZJC2103-14 uses a SPI interface for writing configuration register and receiving conversion codes. The digital interface uses a separate supply, VIO, which should be set to the host logic level.

ZJC2103-14 is available in 20-lead QFN packages. It is pin compatible with industry standard parts.

## **Typical Characteristics**

# **Table of Contents**

| Features1                                     |

|-----------------------------------------------|

| Applications1                                 |

| General Description1                          |

| Block Diagram1                                |

| Typical Characteristics1                      |

| Table of Contents2                            |

| Version (Release C)                           |

| Revision History3                             |

| Pin Configurations and Function Descriptions4 |

| Absolute Maximum Ratings6                     |

| Thermal Resistance6                           |

| Specifications7                               |

| Timing Specifications10                       |

| Timing Specifications Continued11             |

| Typical Performance Characteristics           |

| Theory of Operation16                         |

| Circuit Structure16                           |

| Convertor Operation16                         |

| Transfer Function17                           |

| Typical Connection19                          |

| Fully Differential to Single-ended Driver20   |

| Input Configurations                    |

|-----------------------------------------|

| Internal Reference / Temperature        |

| External Reference and Internal Buffer  |

| External Reference 22                   |

| Power Supply                            |

| Digital Interface                       |

| Reading / Writing During Conversion     |

| Reading / Writing After Conversion      |

| Reading / Writing Spanning Conversion   |

| Configuration Register                  |

| General Timing Without a Busy Indicator |

| General Timing with a Busy Indicator    |

| Channel Sequencer                       |

| RAC Without a Busy Indicator            |

| RAC with a Busy Indicator 31            |

| Layout Guidelines                       |

| Outline Dimensions                      |

| Ordering Guide                          |

| Product Order Model                     |

| Related Parts                           |

### Version (Release C)<sup>1</sup>

#### **Revision History**

#### November 2023 ——Release C

a few parameters updated

#### October2023 — Release B

English version

Figure1、 Digital Output parameter、 Figure4、 Related Parts updating

November 2022 ——Release A

<sup>&</sup>lt;sup>1</sup> Information furnished by ZJW Microelectronics is believed to be accurate and reliable. However, no responsibility is assumed by ZJW Microelectronics for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of ZJW Microelectronics. Trademarks and registered trademarks are the property of their respective owners.

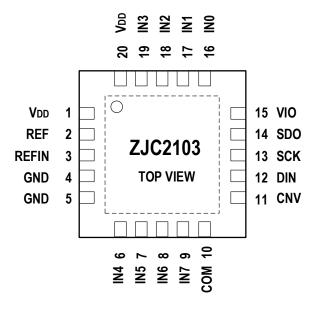

# **Pin Configurations and Function Descriptions**

Figure 3. ZJC2103-14 Pin Configuration

Note: The exposed pad has no internal connection. Connect the pad to GND.

| Mnemonic        | Pin No. | Pin Type               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|---------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 1, 20   | Power Supply           | Power Supply. Nominally 2.3 V to 5.5 V when using an external reference<br>and decoupled with 10 $\mu$ F and 100 nF capacitors.<br>For internal reference 2.5 V output, the minimum V <sub>DD</sub> should be 3.0 V.<br>For internal reference 4.096 V output, the minimum V <sub>DD</sub> should be 4.5 V.                                                                                                                                          |

| REF             | 2       | Analog Input or Output | External Reference Input or Internal Reference Buffer Output.<br>When the internal reference is enabled, it outputs a selectable reference<br>2.5 V or 4.096 V. When the internal reference is disabled and the buffer<br>is enabled, REF produces a buffered reference voltage of the REFIN pin<br>(4.096 V maximum).<br>This pin needs decoupling with an external 10 $\mu$ F capacitor close to REF<br>pin. See the Reference Decoupling section. |

| REFIN           | 3       | Analog Input or Output | Internal Reference Output or External Reference Buffer Input.<br>When using the internal reference, the internal un-buffered bandgap<br>reference voltage is present. It needs decoupling with a 0.1 $\mu$ F capacitor.<br>When using the internal reference buffer, apply an external reference<br>between 0.5 V and 4.096 V which is buffered to the REF pin.                                                                                      |

| GND             | 4, 5    | Ground                 | Power Supply Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IN4             | 6       | Analog Input           | ZJC2103-14: Analog Input Channel 4.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IN5             | 7       | Analog Input           | ZJC2103-14: Analog Input Channel 5.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IN6             | 8       | Analog Input           | ZJC2103-14: Analog Input Channel 6.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IN7             | 9       | Analog Input           | ZJC2103-14: Analog Input Channel 7.                                                                                                                                                                                                                                                                                                                                                                                                                  |

# **Data Sheet**

| СОМ              | 10          | Analog Input         | Common Channel Input. All input channels, IN [7:0], can be referenced     |

|------------------|-------------|----------------------|---------------------------------------------------------------------------|

| COM              | 10          | Analog Input         | to a common-mode point of 0 V or V <sub>REF</sub> / 2.                    |

| CNV              | 11          | Digital Input        | Convert Input. On the rising edge, CNV initiates the conversion. During   |

| CINV             | 11          |                      | conversion, if CNV is high, the busy indictor is enabled.                 |

| DIN              | 12          | Digital Input        | Serial Data Input. This data input is used for writing to the 14-bit      |

|                  | 12          | Digital input        | configuration register.                                                   |

| SCK              | 13          | Digital Input        | Serial Clock Input. This clock input is used to clock out the data on SDO |

| OOK              | 10          | Digital input        | and clock in data on DIN in an MSB first fashion.                         |

|                  |             |                      | Serial Data Output. The conversion codes are output on this pin by SCK.   |

| SDO 14           |             | Digital Output       | In unipolar modes, conversion codes are straight binary; in bipolar       |

|                  |             |                      | modes, conversion codes are twos complement.                              |

| VIO              | 15          | Digital Power Supply | Digital Interface Power Supply. Nominally at the same supply as the host  |

| VIO              | 15          |                      | interface.                                                                |

| IN0              | 16          | Analog Input         | ZJC2103-14: Analog Input Channel 0.                                       |

| IN1              | 17          | Analog Input         | ZJC2103-14: Analog Input Channel 1.                                       |

| IN2              | 18          | Analog Input         | ZJC2103-14: Analog Input Channel 2.                                       |

| IN3              | 19          | Analog Input         | ZJC2103-14: Analog Input Channel 3.                                       |

| EPAD             | Exposed Pad | NC                   | The exposed pad is not connected internally. Recommended connecting       |

| EPAD Exposed Pad |             |                      | the pad to the ground plane.                                              |

### Absolute Maximum Ratings<sup>1</sup>

#### Thermal Resistance <sup>6</sup>

| Parameter                                   | Rating                            | Package | θја | θις | Unit |

|---------------------------------------------|-----------------------------------|---------|-----|-----|------|

| V <sub>DD</sub> , REF, VIO to GND           | - 0.3 V ~ 6 V                     | QFN-20  | 51  | 27  | °C/W |

| REF, VIO to V <sub>DD</sub>                 | - 6 V ~ V <sub>DD</sub> + 0.3 V   |         |     |     |      |

| Analog Input Range (INx to GND)             | - 0.3 V ~ V <sub>DD</sub> + 0.3 V |         |     |     |      |

| Digital Input to GND                        | - 0.3 V ~ VIO + 0.3 V             |         |     |     |      |

| Digital Output to GND                       | - 0.3 V ~ VIO + 0.3 V             |         |     |     |      |

| Storage Temperature Range                   | - 65 °C to 150 °C                 |         |     |     |      |

| Junction Temperature Range                  | 150 °C                            |         |     |     |      |

| Lead Temperature<br>(Soldering, 10 seconds) | 300 °C                            |         |     |     |      |

| Maximum Reflow Temperature <sup>2</sup>     | 260 °C                            |         |     |     |      |

| Electrostatic Discharge (ESD) 3             |                                   |         |     |     |      |

| Human Body Model (HBM) 4                    | 1.5 kV                            |         |     |     |      |

| Charged Device Model (CDM) 5                | 1 kV                              |         |     |     |      |

Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

- <sup>4</sup> ANSI/ESDA/JEDEC JS-001 Compliant.

- <sup>5</sup> ANSI/ESDA/JEDEC JS-002Compliant.

<sup>&</sup>lt;sup>1</sup> These ratings apply at 25 °C, unless otherwise noted.

Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

<sup>&</sup>lt;sup>2</sup> IPC/JEDECJ-STD-020 Compliant.

<sup>&</sup>lt;sup>3</sup> Charged devices and circuit boards can discharge without detection.

<sup>&</sup>lt;sup>6</sup> O<sub>JA</sub> addresses the conditions for soldering devices onto circuit boards to achieve surface mount packaging.

# **Specifications**

The • denotes the full temperature range for specified performance. Unless otherwise noted,  $V_{DD}$  = 4.5 V ~ 5.5 V,  $V_{REF}$  =  $V_{DD}$ , T<sub>A</sub>= 25 °C.

| Parameter                    | Symbol Conditions                          |                                  | Min | Тур                     | Мах   | Unit                    |                  |

|------------------------------|--------------------------------------------|----------------------------------|-----|-------------------------|-------|-------------------------|------------------|

| Resolution                   |                                            |                                  |     | 14                      |       |                         |                  |

| Input Characteristics        |                                            |                                  |     |                         |       |                         |                  |

| Vellere Denre                |                                            | Unipolar                         | •   | 0                       |       | V <sub>REF</sub>        | V                |

| Voltage Range                |                                            | Bipolar                          | •   | - V <sub>REF</sub> /2   |       | + V <sub>REF</sub> /2   |                  |

|                              |                                            | INx+ to GND                      | •   | - 0.1                   |       | V <sub>REF</sub> + 0.1  | V                |

| Absolute input voltage       |                                            | INx- or COM, Unipolar            | •   | - 0.1                   |       | +0.1                    | V                |

|                              |                                            | INx- or COM, Bipolar             | •   | V <sub>REF</sub> /2-0.1 |       | V <sub>REF</sub> /2+0.1 | V                |

| Common Mode Rejection Ratio  | CMRR                                       | f <sub>IN</sub> = 230 kHz        |     |                         | 67    |                         | dB               |

| Leakage Current              |                                            | Acquisition Phase                |     |                         | 1     |                         | nA               |

| Input Impedance 1            |                                            |                                  |     |                         |       |                         |                  |

| Throughput                   |                                            |                                  |     |                         |       |                         |                  |

| Full Bandwidth               |                                            | V <sub>DD</sub> = 4.5 V to 5.5 V | •   | 0                       |       | 300                     | - kSPS           |

|                              |                                            | V <sub>DD</sub> = 2.3 V to 4.5 V | •   | 0                       |       | 200                     |                  |

|                              |                                            | V <sub>DD</sub> = 4.5 V to 5.5 V | •   | 0                       |       | 75                      |                  |

| 1/4 Bandwidth                | $V_{DD} = 2.3 \text{ V to } 4.5 \text{ V}$ |                                  | •   | 0                       |       | 50                      |                  |

| Transient Response           |                                            | Full - scale step                | •   |                         |       | 1967                    | ns               |

| DC Accuracy                  |                                            |                                  |     |                         |       |                         |                  |

| No Missing Codes             |                                            |                                  | •   | 14                      |       |                         | bits             |

| Integral Nonlinear Error     | INL                                        |                                  | •   | - 0.75                  | ±0.2  | +0.75                   | LSB <sup>2</sup> |

| Differential Nonlinear Error | DNL                                        |                                  | •   | - 0.5                   | ±0.15 | + 0.5                   | LSB              |

| Transition Noise             |                                            | $REF = V_{DD} = 5 V$             |     |                         | 0.3   |                         | LSB              |

| Gain Error                   | GE                                         | Single-ended                     | •   | - 5                     | ±1    | +5                      | LSB              |

| Gain Error Matching          |                                            |                                  |     |                         | ±0.5  |                         | LSB              |

| Gain Error Temperature Drift |                                            |                                  |     |                         | ±0.5  |                         | ppm/°C           |

| Zero Error                   | ZE                                         | Single-ended                     | •   | - 4                     | ±1    | +4                      | LSB              |

| Zero Error Matching          |                                            |                                  |     |                         | ±0.25 |                         | LSB              |

| Zero Error Temperature Drift |                                            |                                  |     |                         | ±0.3  |                         | ppm/°C           |

| Power Supply Sensitivity     |                                            | V <sub>DD</sub> = 5 V ± 5 %      |     |                         | ±0.2  |                         | LSB              |

1

See the Analog Inputs section. LSB means least significant bit. 1 LSB = 305.2  $\mu V$  for 5 V input range. 2

# ZJC2103-14

| Parameter                      | Parameter Symbol Conditions |                                                                 | Min | Тур   | Мах   | Unit                  |                 |  |

|--------------------------------|-----------------------------|-----------------------------------------------------------------|-----|-------|-------|-----------------------|-----------------|--|

| AC Accuracy                    |                             |                                                                 |     |       |       |                       |                 |  |

| Dynamic Range                  | DR                          | V <sub>REF</sub> = 5 V                                          | •   | 84.5  | 85.5  |                       | dB <sup>3</sup> |  |

|                                |                             | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 5 V                 | •   | 84    | 85.3  |                       |                 |  |

| SNR                            | SNR                         | $f_{IN}$ = 1 kHz, $V_{REF}$ = 4.096 V, internal ref             | •   | 83.5  | 84.5  |                       | dB              |  |

|                                |                             | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 2.5 V, internal ref | •   | 82    | 83.1  |                       |                 |  |

|                                |                             | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 5 V                 | •   | 84    | 85.2  |                       |                 |  |

| Signal-to (Noise + Distortion) | SINAD                       | $f_{IN}$ = 1 kHz, $V_{REF}$ = 4.096 V, internal ref             | •   | 83.4  | 84.4  |                       | dB              |  |

|                                |                             | $f_{IN}$ = 1 kHz, $V_{REF}$ = 2.5 V, internal ref               | •   | 82    | 83    |                       |                 |  |

| Spurious-Free Dynamic          | SFDR                        | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 5 V                 |     |       | 106   |                       | dB              |  |

| Total Harmonic Distortion      | THD                         | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 5 V                 |     |       | - 105 |                       | dB              |  |

| Channel Crosstalk              |                             | f <sub>IN</sub> = 1 kHz, V <sub>REF</sub> = 5 V                 |     |       | - 120 |                       | dB              |  |

| External Reference Input       |                             |                                                                 |     |       |       |                       |                 |  |

|                                |                             | REF Input                                                       | •   | 0.5   |       | V <sub>DD</sub> + 0.3 |                 |  |

| Voltage Range                  |                             | REFIN Input (Buffer Enabled)                                    | •   | 0.5   |       | V <sub>DD</sub> - 0.5 | - V             |  |

| Load Current                   |                             | Sinewave Input                                                  |     |       | 70    |                       | μA              |  |

| Internal Reference Output      |                             |                                                                 |     |       |       |                       |                 |  |

|                                |                             | 4.096 V, @ 25 °C                                                | •   | 4.092 | 4.096 | 4.100                 | V               |  |

| REFOutput Voltage              |                             | 2.5 V, @ 25 °C                                                  | •   | 2.495 | 2.5   | 2.505                 | - V             |  |

|                                |                             | REF = 4.096 V, @ 25 °C                                          |     |       | 2.42  |                       |                 |  |

| REFIN Output Voltage           |                             | REF = 2.5 V, @ 25 °C                                            |     |       | 1.21  |                       | - V             |  |

| REFOutput Current              |                             |                                                                 |     |       | 300   |                       | μA              |  |

| Tamarahan Di'tt                | -                           | - 40 °C to +85 °C                                               | •   |       | 6     | 12                    | ppm/°C          |  |

| Temperature Drift              | Tc                          | 0 °C to +85 °C                                                  |     |       | 2     |                       | ppm/°C          |  |

| Line Regulation                |                             | V <sub>DD</sub> = 5 V ± 5 %                                     |     |       | 20    |                       | ppm/V           |  |

| Turn-On Settling Time          |                             | Crefin = 0.1 μF, Cref = 10 μF                                   |     |       | 10    |                       | ms              |  |

| SamplingDynamics               |                             |                                                                 |     |       |       |                       |                 |  |

|                                |                             | V <sub>DD</sub> = 5 V, Full Bandwidth                           |     |       | 6     |                       | MHz             |  |

| -3dBAnalog Input Bandwidth     |                             | V <sub>DD</sub> = 5 V, 1/4 Bandwidth                            |     |       | 1.5   |                       |                 |  |

| Aperture Delay                 |                             | V <sub>DD</sub> = 5 V                                           |     |       | 3     |                       | ns              |  |

| Temperature Sensor             |                             |                                                                 |     |       |       |                       |                 |  |

| Output Voltage                 |                             | @ 25 °C                                                         |     |       | 300   |                       | mV              |  |

| Temperature Sensitivity        |                             |                                                                 |     |       | 1     |                       | mV/°C           |  |

<sup>&</sup>lt;sup>3</sup> Unless otherwise noted, all specifications expressed in decibels (dB) are referenced to full-scale input FSR and are tested with an input signal 0.5 dB below full-scale.

# **Data Sheet**

| Parameter             | Parameter Symbol Conditions |                                               | Min       | Тур       | Max         | Unit                 |    |

|-----------------------|-----------------------------|-----------------------------------------------|-----------|-----------|-------------|----------------------|----|

| Digital Input         |                             |                                               |           |           |             |                      |    |

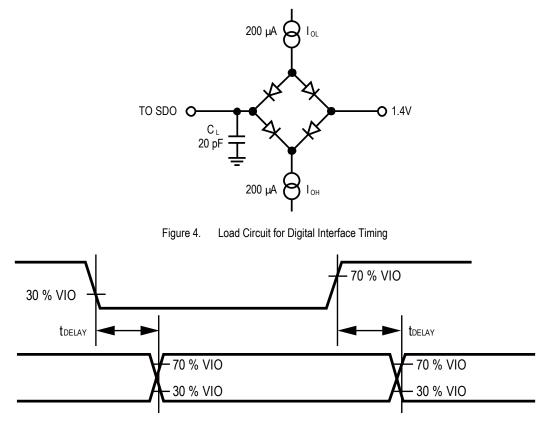

| Levie Level           | VIL                         |                                               | •         | - 0.3     |             | 0.3 x VIO            | V  |

| Logic Level           | Vih                         |                                               | •         | 0.7 x VIO |             | VIO + 0.3            |    |

|                       | lı∟                         |                                               | •         | - 1       |             | +1                   |    |

| Input Current         | Ін                          |                                               | •         | - 1       |             | +1                   | μA |

| Digital Output        |                             |                                               |           |           |             |                      |    |

| Data Format           |                             | Single-ended, or Pseudo Diff Unipolar         |           | Serial 14 | -bit, strai | ght binary           |    |

| Data Format           |                             | Pseudo Diff Bipolar                           | Serial 14 |           | -bit, twos  |                      |    |

| Logic Low Voltage     | V <sub>OL</sub>             | I <sub>OUT</sub> = +200 μA                    | •         |           |             | 0.4                  | V  |

| Logic High Voltage    | Vон                         | Ιουτ = - 200 μΑ                               | •         | VIO - 0.3 |             |                      | V  |

| Power Supplies        |                             |                                               |           |           |             |                      |    |

| V <sub>DD</sub>       |                             | Specified performance                         |           | 4.5       |             | 5.5                  | V  |

| V <sub>DD</sub>       |                             | Operating Range                               |           | 2.3       |             | 5.5                  | V  |

| VIO                   |                             | Specified performance                         |           | 1.8       |             | V <sub>DD</sub> +0.3 | V  |

| Power-downCurrent 4,5 |                             | V <sub>DD</sub> and VIO = 5 V, @25 °C         |           |           | 50          |                      | nA |

|                       |                             | V <sub>DD</sub> = 5 V, 1 kSPS                 | •         |           | 32          | 36                   | μW |

|                       |                             | V <sub>DD</sub> = 5 V, 100 kSPS               | •         |           | 3.4         | 3.8                  | mW |

| Power Consumption     |                             | V <sub>DD</sub> = 5 V, 300 kSPS               | •         |           | 9.3         | 10.4                 | mW |

|                       |                             | V <sub>DD</sub> = 5 V, 300 kSPS, internal ref | •         |           | 13.7        | 15.8                 | mW |

| Temperature Range     |                             |                                               |           |           |             |                      |    |

| SpecifiedPerformance  |                             | TMIN to TMAX                                  |           | - 40      |             | +85                  | °C |

<sup>4</sup>

In the acquisition phase. All digital inputs are forced to VIO or GND as required. 5

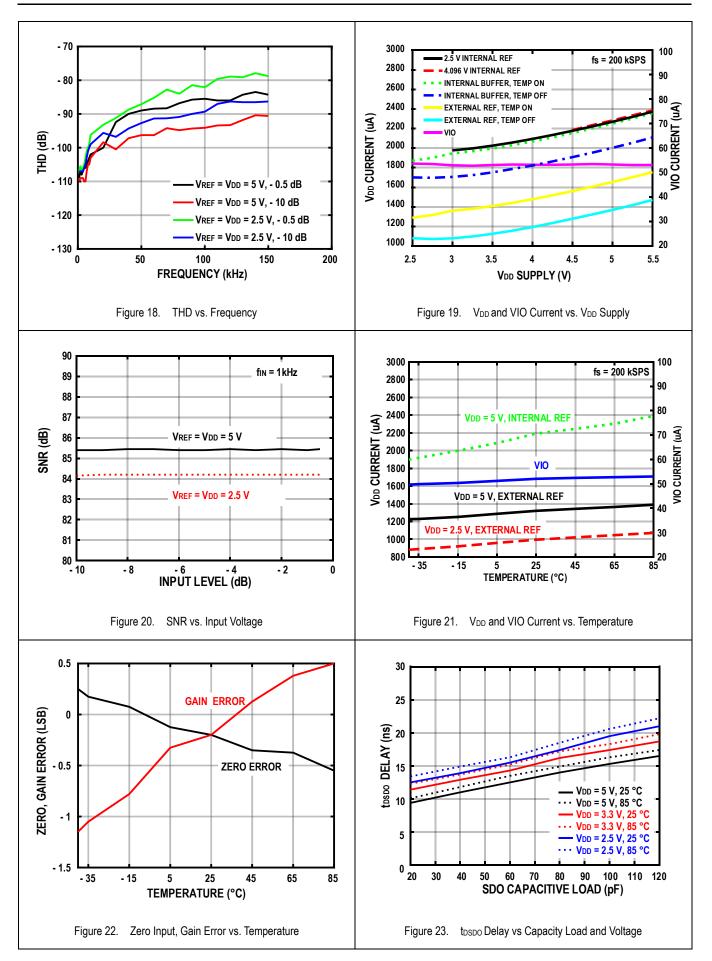

# **Timing Specifications**

The • denotes the full temperature range for specified performance. Unless otherwise specified,  $V_{DD}$  = 4.5 V ~ 5.5 V,  $V_{REF}$  =  $V_{DD}$ , VIO = 1.8 V ~  $V_{DD}$ ,  $T_A$  = 25 °C.

| Parameter                                               | Symbol            |   | Min   | Тур | Мах   | Unit |

|---------------------------------------------------------|-------------------|---|-------|-----|-------|------|

| Conversion Time: CNV Rising Edge to Data Available      | tсолу             | • |       |     | 1.366 | μs   |

| AcquisitionTime                                         | tacq              | • | 1.967 |     |       | μs   |

| Time Between Conversions                                | tcyc              | • | 3.333 |     |       | μs   |

| Data Write/Read During Conversion                       | <b>t</b> DATA     | • |       |     | 0.8   | μs   |

| CNV Pulse Width                                         | t <sub>CNVH</sub> | • | 10    |     |       | ns   |

| SCK Period (VIO > 3.3 V)                                | tscк              | • | 15    |     |       | ns   |

| VIO above 2.7 V                                         |                   | • | 20    |     |       | ns   |

| VIO above 2.3 V                                         |                   | • | 25    |     |       | ns   |

| VIO above 1.8 V                                         |                   | • | 40    |     |       | ns   |

| SCK Low Time (VIO > 3.3 V)                              | <b>t</b> SCKL     | • | 7.5   |     |       | ns   |

| SCK High Time (VIO > 3.3 V)                             | tscкн             | • | 7.5   |     |       | ns   |

| SCK Falling Edge to Data Remain Valid                   | <b>t</b> HSDO     | • | 4     |     |       | ns   |

| SCK Falling Edge to Data Valid Delay                    | tosdo             |   |       |     |       |      |

| VIO above 2.7 V                                         |                   | • |       |     | 17    | ns   |

| VIO above 2.3 V                                         |                   | • |       |     | 18    | ns   |

| VIO above 1.8 V                                         |                   | • |       |     | 21    | ns   |

| CNVLow to SDO MSB Valid                                 | t <sub>EN</sub>   |   |       |     |       |      |

| VIO above 2.7 V                                         |                   | • |       |     | 22    | ns   |

| VIO above 2.3 V                                         |                   | • |       |     | 25    | ns   |

| VIO above 1.8 V                                         |                   | • |       |     | 28    | ns   |

| CNV High or Last SCK Falling Edge to SDO High Impedance | e tois            |   |       |     | 25    | ns   |

| CNV Low to SCK Rising Edge                              | <b>t</b> CLCLK    | • | 10    |     |       | ns   |

| Last SCLK Falling Edge to CNV Rising Edge Delay         |                   | • | 100   |     |       | ns   |

| DIN Valid Setup Time from SCK Rising Edge               | t <sub>SDIN</sub> | • | 5     |     |       | ns   |

| DIN Valid Hold Time from SCK Rising Edge                | thdin             | • | 5     |     |       | ns   |

# **Timing Specifications Continued**

The • denotes the full temperature range for specified performance. Unless otherwise specified,  $V_{DD}$  = 2.3 V ~ 4.5 V,  $V_{REF}$  =  $V_{DD}$ , VIO = 1.8 V ~  $V_{DD}$ ,  $T_A$  = 25 °C.

| Parameter                                               | Symbol            |   | Min   | Тур | Мах   | Unit |

|---------------------------------------------------------|-------------------|---|-------|-----|-------|------|

| Conversion Time: CNV Rising Edge to Data Available      | tсолу             | • |       |     | 2.633 | μs   |

| AcquisitionTime                                         | tacq              | • | 2.367 |     |       | μs   |

| Time Between Conversions                                | tcyc              | • | 5     |     |       | μs   |

| Data Write/Read During Conversion                       | <b>t</b> DATA     | • |       |     | 0.8   | μs   |

| CNV Pulse Width                                         | t <sub>CNVH</sub> | • | 10    |     |       | ns   |

| SCK Period (VIO > 3.3V)                                 | tscк              | • | 15    |     |       | ns   |

| VIO above 2.7 V                                         |                   | • | 20    |     |       | ns   |

| VIO above 2.3 V                                         |                   | • | 25    |     |       | ns   |

| VIO above 1.8 V                                         |                   | • | 40    |     |       | ns   |

| SCK Low Time (VIO > 3.3 V)                              | <b>t</b> SCKL     | • | 7.5   |     |       | ns   |

| SCK High Time (VIO > 3.3 V)                             | tscкн             | • | 7.5   |     |       | ns   |

| SCK Falling Edge to Data Remain Valid                   | thsdo             | • | 4     |     |       | ns   |

| SCK Falling Edge to Data Valid Delay                    | tosdo             |   |       |     |       |      |

| VIO above 2.7 V                                         |                   | • |       |     | 17    | ns   |

| VIO above 2.3 V                                         |                   | • |       |     | 18    | ns   |

| VIO above 1.8 V                                         |                   | • |       |     | 21    | ns   |

| CNVLow to SDO MSB Valid                                 | t <sub>EN</sub>   |   |       |     |       |      |

| VIO above 2.7 V                                         |                   | • |       |     | 22    | ns   |

| VIO above 2.3 V                                         |                   | • |       |     | 25    | ns   |

| VIO above 1.8 V                                         |                   | • |       |     | 28    | ns   |

| CNV High or Last SCK Falling Edge to SDO High Impedance | tDIS              |   |       |     | 25    | ns   |

| CNV Low to SCK Rising Edge                              | <b>t</b> CLCLK    | • | 10    |     |       | ns   |

| Last SCLK Falling Edge to CNV Rising Edge Delay         |                   | • | 150   |     |       | ns   |

| DIN Valid Setup Time from SCK Rising Edge               | t <sub>SDIN</sub> | • | 5     |     |       | ns   |

| DIN Valid Hold Time from SCK Rising Edge                | thdin             | • | 5     |     |       | ns   |

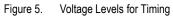

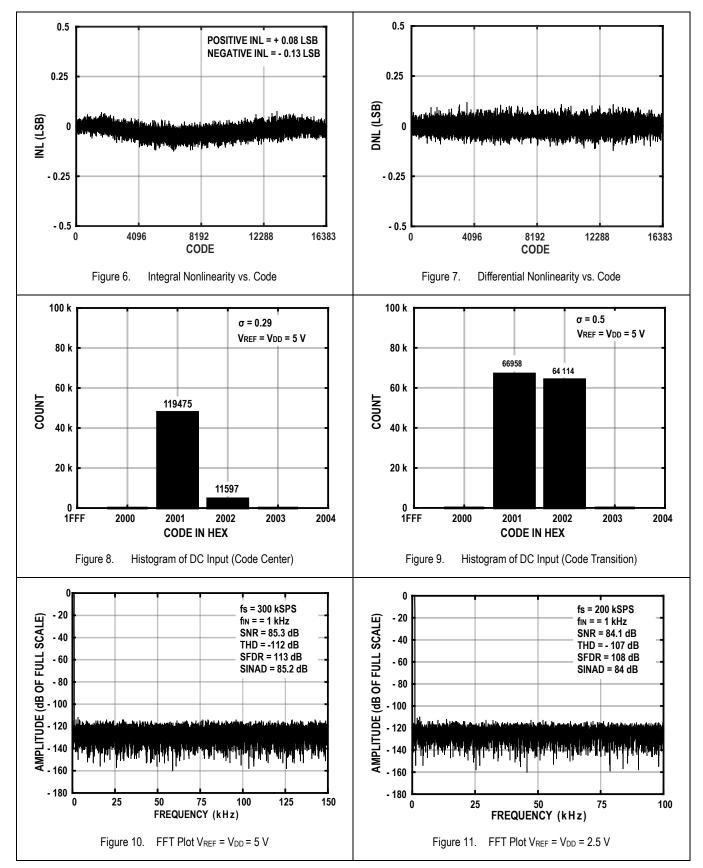

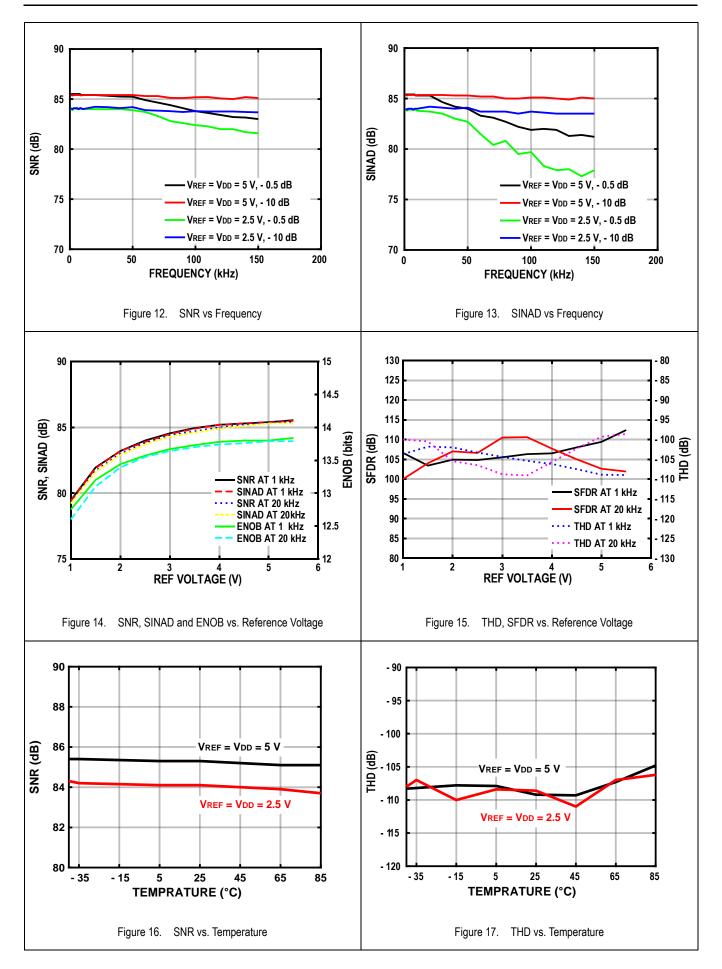

# **Typical Performance Characteristics**

Unless otherwise noted,  $V_{DD}$  = 5.0 V, REF = 5.0 V, VIO = 3.3 V, T<sub>A</sub> = 25 °C.

# ZJC2103-14

# **Data Sheet**

# ZJC2103-14

# **Theory of Operation**

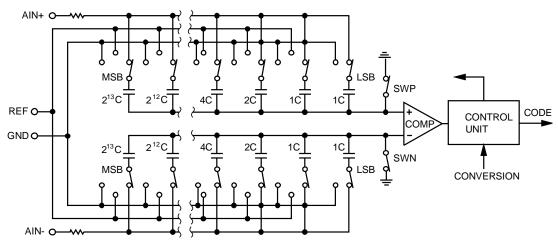

Figure 24. ADC Simplified Circuit Diagram

#### **Circuit Structure**

The ZJC2103-14 is an 8-channel, 14-bit, charge redistribution successive approximation register analog-to-digital converter. The ZJC2103-14 is capable of running up to 300 kSPS and powers down between conversions.

The ZJC2103-14 contains a 14-bit SAR ADC, an 8-channel, low crosstalk multiplexer to configure the inputs as single-ended, pseudo differential unipolar or bipolar; an internal low drift reference (selectable 2.5 V or 4.096 V) and reference driver; a temperature sensor; a selectable one-pole filter; and a digital sequencer which is useful for channels being continuously scanned in order.

#### **Convertor Operation**

Figure 24 is a simplified circuit diagram of ZJC2103-14.

In the acquisition phase, the array node connected to the input of the comparator is short connect to GND via the SW+and SW-. All individual switches are connected to analog inputs. When the acquisition phase is complete and a rising edge occurs on the CNV input, the conversion phase is initiated. When the conversion phase begins, the SW+ and SW-disconnect first. The two capacitor arrays are then disconnected from the input and connected to the GND input. By switching the elements of the capacitor array between GND and REF, the comparator input will vary in binary weighted voltage steps (V<sub>REF</sub>/2<sup>1</sup>, V<sub>REF</sub>/2<sup>2</sup>,...,V<sub>REF</sub>/2<sup>13</sup>). The control logic toggles these switches in sequence starting with the MSB, and the comparator is brought back into balance each time. After this phase is complete, the device returns to the acquisition phase, and the control logic generates the ADC output code.

## **Transfer Function**

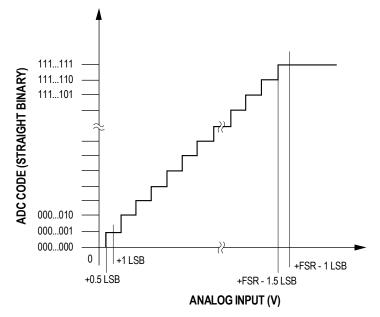

When configured as singled-ended or pseudo differential unipolar (single-ended INx to GND, COM to GND, temperature sensor, INto GND), the code is straight binary. The ideal transfer characteristic is shown below:

Singled-ended or Pseudo Differential Unipolar Output Codes and Ideal Input Voltages

| Description      | Analog Input V <sub>REF</sub> = 5 V | Digital Output (Hex) |

|------------------|-------------------------------------|----------------------|

| FSR - 1 LSB      | 4.999695 V                          | 0x3FFF <sup>1</sup>  |

| Midscale + 1 LSB | 2.500305 V                          | 0x2001               |

| Midscale         | 2.5 V                               | 0x2000               |

| Midscale - 1 LSB | 2.499695 V                          | 0x1FFF               |

| - FSR + 1 LSB    | 305.2 µV                            | 0x0001               |

| - FSR            | 0 V                                 | 0x0000 <sup>2</sup>  |

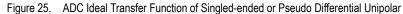

When configured as pseudo differential bipolar (COM = VREF/2 or INx- = VREF/2), the code is twos complement.

<sup>&</sup>lt;sup>1</sup> This is also the code for an overranged analog input ((INx+) – (INx-), or COM, above V<sub>REF</sub> – GND).

<sup>&</sup>lt;sup>2</sup> This is also the code for an underranged analog input ((INx+) - (INx-), or COM, below GND).

| Description      | Analog Input V <sub>REF</sub> = 5 V | Digital Output (Hex)  |

|------------------|-------------------------------------|-----------------------|

| FSR - 1 LSB      | +2.499695 V                         | 0b01 1111 1111 1111 1 |

| Midscale + 1 LSB | + 305.2 µV                          | 0b00 0000 0000 0001   |

| Midscale         | 0 V                                 | 0P00 0000 0000 0000   |

| Midscale - 1 LSB | - 305.2 μV                          | 0b11 1111 1111 1111   |

| - FSR + 1 LSB    | - 2.499695 V                        | 0b10 0000 0000 0001   |

| - FSR            | - 2.5 V                             | 0b10 0000 0000 0000 2 |

This is also the code for an overranged analog input ((INx+) – (INx–), or COM, above V<sub>REF</sub> – GND). This is also the code for an underranged analog input ((INx+) – (INx–), or COM, below GND). 1

<sup>2</sup>

### **Typical Connection**

5 V 1.8 V TO VDD VREF 100 nF 100 nl 100 nF 10 u REF REFIN Vdd VIO 0 V TO VREF IN0 ZJC2103-14 DIN MOSI ) IN1 SCK SCK SDO MISO 0 V TO VREF CS CNV 0 V or V<sub>REF</sub>/2 O COM GND

Figure 27 is a suggested connection for the ZJC2103-14 when multiple power supplies are used.

Figure 27. Application Circuits Using Multiple Power Supplies

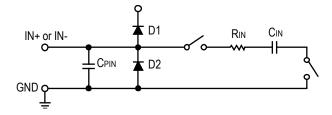

Figure 28 shows the equivalent circuit of the ZJC2103-14 input structure.

Figure 28. Two Diodes D1 and D2 Provide ESD Protection for the Analog Inputs

The voltage of the analog input signal cannot be higher than the supply voltage ( $V_{DD}$ ) by more than 0.3 V. If the voltage of the analog input signal exceeds  $V_{DD}$  + 0.3 V, the diode will be forward biased and start conducting current. These two diodes can handle forward bias currents up to 50 mA. If the supply voltage of the input driver is higher than  $V_{DD}$  the voltage of the analog input signal may be more than 0.3 V higher than the supply voltage. The two diodes D1 and D2 provide ESD protection for analog input IN+ and IN-.

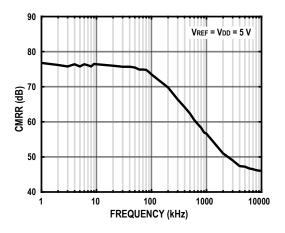

Figure 29. Analog Input CMRR vs. Frequency

In the acquisition phase, the impedance of the analog inputs can be modeled as a parallel combination of the capacitor,  $C_{PIN}$ , and the network formed by the series connection of  $R_{IN}$  and  $C_{IN}$ .  $C_{PIN}$  is primarily the pin capacitance.  $R_{IN}$  is typically 700  $\Omega$  and is a lumped component composed of serial resistors and the on resistance of the switches.  $C_{IN}$  is typically 30 pF and is mainly the ADC sampling capacitor.

#### **Fully Differential to Single-ended Driver**

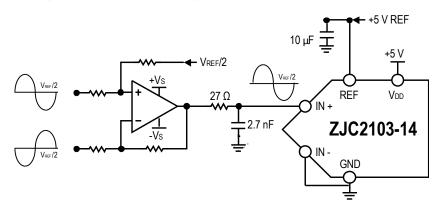

For applications using fully differential analog signals (bipolar or unipolar), an op amp driver can provide pseudo differential unipolar input to the ZJC2103-14, see Figure 30 for the schematic diagram.

Figure 30. Fully Differential to Single-ended Conversion with an Op Amp

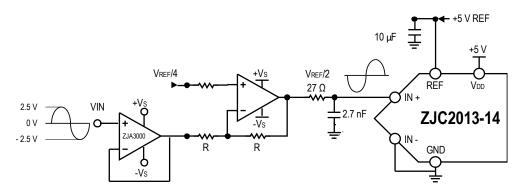

Singled-ended bipolar signal can be converted to pseudo differential unipolar signal with two amplifiers for ZJC2103-14.

Figure 31. Single-ended Bipolar to Pseudo Differential Unipolar

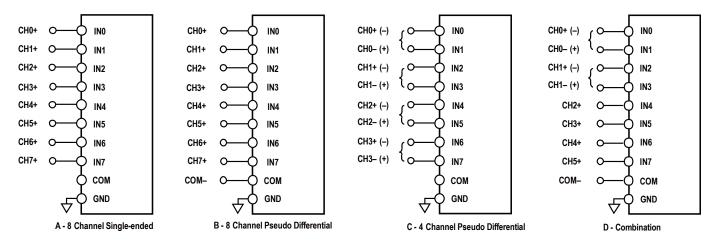

### **Input Configurations**

Figure 32 shows configuring the analog inputs with the configuration register CFG [12:10].

The analog inputs can be configured as:

- Figure 32A, all single-ended INx inputs referenced to ground; CFG [12:10] = 111. In this configuration, all inputs (IN [7:0]) have a range of GND to V<sub>REF</sub>.

- Figure 32B, pseudo differential bipolar with a common reference point; COM = V<sub>REF</sub>/2; CFG [12:10] = 010. Pseudo differential unipolar with COM = 0 V; CFG [12:10] = 110. All inputs IN [7:0] referred to GND have a range of GND to V<sub>REF</sub>.

- Figure 32C, pseudo differential bipolar pairs with the negative input channel referenced to V<sub>REF</sub>/2; CFG [12:10] = 00X.Pseudo differential unipolar pairs with the negative input channel referenced to a ground sense; CFG [12:10] = 10X. In these configurations, the positive input channels have the range of GND to V<sub>REF</sub>. The negative input channels are senses referred to V<sub>REF</sub>/2 for bipolar pairs, or GND for unipolar pairs. If CFG [9:7] is even, then IN0, IN2, IN4, and IN6 are used as positive inputs. If CFG [9:7] is odd, then IN1, IN3, IN5, and IN7 are used as positive inputs. Note that for the sequencer, the positive channels are always IN0, IN2, IN4, and IN6.

- Figure 32D, inputs configured in any of the combinations above.

Figure 32. Multiplexed Analog Input Configurations

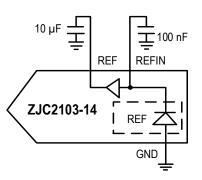

#### **Internal Reference / Temperature**

The ZJC2103-14 internal precision reference, can be set for either a 2.5 V or a 4.096 V on REF pin. When the internal reference is enabled, the band gap voltage is present on the REFIN pin. Because the current output of REFIN is limited, it can be used as a source if followed by a suitable buffer, such as the ZJA3000. Note that the voltage of REFIN changes depending on the 2.5 V or 4.096 V internal reference.

Enabling the reference also enables the internal temperature sensor, which measures the internal temperature of the ZJC2103-14. Note that, when using the temperature sensor, the output is straight binary referenced ZJC2103-14 GND pin.

The internal reference is trimmed to provide a typical drift of ±6 ppm/°C. Figure 33 shows the internal reference connection.

Figure 33. 2.5 V or 4.096 V Internal Reference Connection

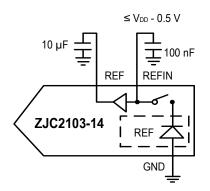

#### **External Reference and Internal Buffer**

For improved drift performance, an external reference can be used with the internal buffer, as shown in Figure 34. The external source is connected to REFIN, the input to the on-chip unity gain buffer, and the output is produced on the REF pin to drive the ADC core. An external reference can be used with the internal buffer with or without the temperature sensor enabled.

Figure 34. External Reference Using Internal Buffer

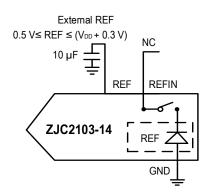

#### **External Reference**

For improved drift or noise performance, an external reference can be connected directly on the REF pin as shown in Figure 34. The reference buffer must be powered down, and the internal reference can be disabled for lower power consumption.

Figure 35. External Reference (internal buffer disabled)

For precision ADC applications, a precision voltage reference is an essential device. Generally, the reference source needs to have low initial error, low noise, and low temperature drift. The ZJC2103-14 reference voltage REF has a dynamic input impedance, so it should be driven with a low impedance source. The REF and GND pins should be effectively decoupled as described in the PCB

# **Data Sheet**

Layout Guidelines section. Figure 36 shows an example of a specific voltage reference and driver design. The ZJR100X series of high-precision voltage references can just meet these requirements.

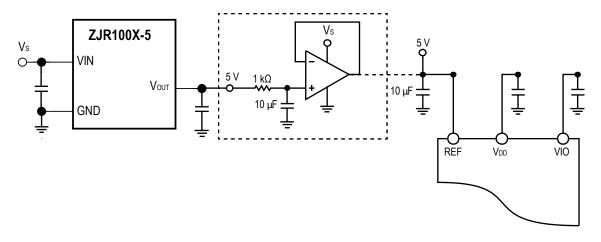

Figure 36. External Reference Drive

# **Power Supply**

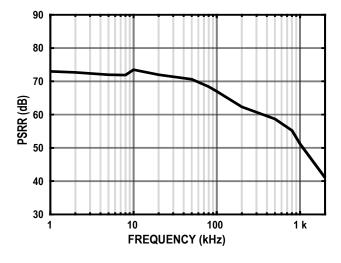

ZJC2103-14 uses two power supply pins: core power supply ( $V_{DD}$ ) and digital input/output interface power supply VIO. VIO can directly interface with any logic from 1.8 V to  $V_{DD}$ . To reduce the number of power supplies required, the VIO and  $V_{DD}$  pins can be tied together via resistors or ferrite beads. The PSRR curve is shown in Figure 37.

Figure 37. PSRRvs. Frequency

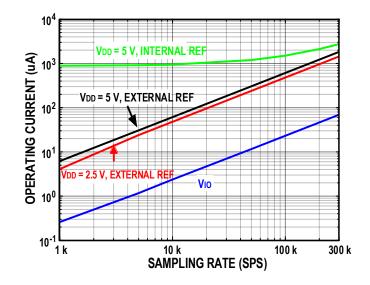

The ZJC2103-14 automatically enters power-down mode at the end of each conversion stage, so the power consumption is approximately linearly proportional to the sampling rate. This makes the device suitable for low sampling rate and low power consumptionapplications. As shown Figure 38.

Figure 38. Operating Current vs. Sampling Rate

Release C

### **Digital Interface**

ZJC2103-14 has 4-wire SPI digital interface which uses CNV, DIN, SCK and SDO. A 14-bit register, CFG [13:0], is used to configure the ADC for the channel to be converted, the reference selection, and other components.

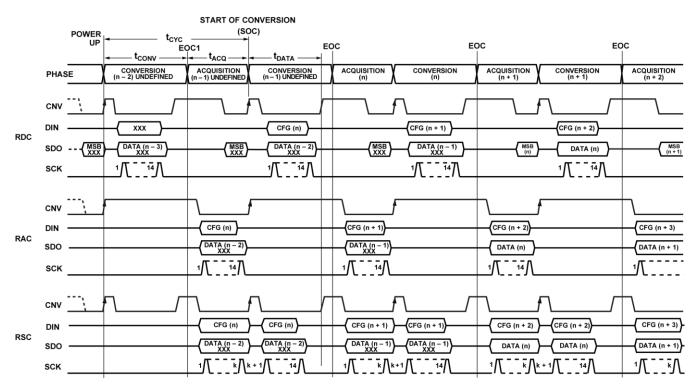

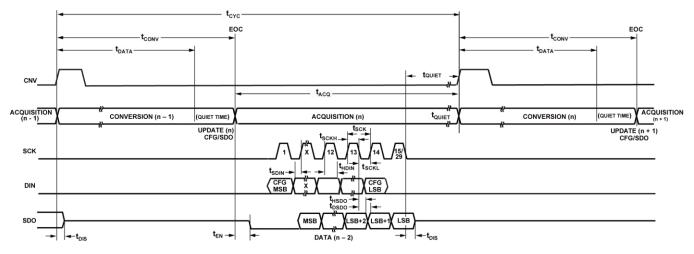

When CNV is low (works like chip select), reading/writing can occur during conversion, acquisition, and spanning conversion (acquisition plus conversion), as detailed in the following sections. The CFG word is updated on the first 14 SCK rising edges, and conversion codes are output on the first 13 (or 14 if busy indicator is selected) SCK falling edges. If the CFG readback is enabled, an additional 14 SCK falling edges are required to output the CFG word following the conversion code with the CFG MSB following the LSB of the conversion code.

#### **Reading / Writing During Conversion**

When reading or writing during conversion (n), conversion results are for the previous (n - 1) conversion, and writing the CFG register is for the next (n + 1) acquisition and conversion. After the CNV is brought high to initiate conversion, it must be brought low again to allow reading or writing during conversion. Reading or writing should only occur up to t<sub>DATA</sub>.

The SCK frequency required is calculated by

$$f_{SCK} \ge \frac{\text{Number} \_ SCK \_ Edges}{t_{DATA}}$$

The time between t<sub>DATA</sub> and t<sub>CONV</sub> is a quiet time when digital activity should not occur, or sensitive bit decisions may be corrupted.

#### **Reading / Writing After Conversion**

When reading or writing after conversion, or during acquisition (n), conversion results are for the previous (n - 1) conversion, and writing is for the (n + 1) acquisition. The reading or writing takes place during the  $t_{ACQ}$  (minimum) time.

#### **Reading / Writing Spanning Conversion**

When reading or writing spanning conversion, the data access starts at the current acquisition (n) and spans into the conversion (n). Conversion results are for the previous (n - 1) conversion, and writing the CFG register is for the next (n + 1) acquisition and conversion.

#### **Configuration Register**

The ZJC2103-14 uses a 14-bit configuration register (CFG [13:0]) to configure the analog inputs, the channel to be converted, the one-pole filter bandwidth, the reference, and the channel sequencer. The CFG register is latched (MSB first) on DIN with 14 SCK rising edges.

The register can be written to during conversion, during acquisition, or spanning acquisition/conversion, and is updated at the end of conversion. There is always a one deep delay when writing the CFG register. Note that, at power-up, the CFG register is undefined and two dummy conversions are required to update the register. To preload the CFG register with a factory setting, hold DIN high for two conversions. Thus CFG [13:0] = 0x3FFF. This sets the ZJC2103-14 for the following:

# ZJC2103-14

- IN [7:0] unipolar referenced to GND, sequenced in order

- Full bandwidth

- Internal reference and temperature sensor disabled, buffer enabled

- internal sequencer enabled

- No readback of the CFG register

| 13  | 12   | 11   | 10   | 9   | 8   | 7   | 6  | 5   | 4   | 3   | 2   | 1   | 0  |

|-----|------|------|------|-----|-----|-----|----|-----|-----|-----|-----|-----|----|

| CFG | INCC | INCC | INCC | INX | INX | INX | BW | REF | REF | REF | SEQ | SEQ | RB |

Configuration Register Description:

| Bit     | Name | Description                                                                                                |         |     |                                                                                   |  |  |  |

|---------|------|------------------------------------------------------------------------------------------------------------|---------|-----|-----------------------------------------------------------------------------------|--|--|--|

|         |      | Configuration update.                                                                                      |         |     |                                                                                   |  |  |  |

| [13]    | CFG  | 0 = write invalid, keep current configuration settings.                                                    |         |     |                                                                                   |  |  |  |

|         |      | 1 = write enabled, overwrite contents of register.                                                         |         |     |                                                                                   |  |  |  |

|         |      | Input channel configuration. Selection of pseudo differential bipolar, pseudo differential unipolar pairs, |         |     |                                                                                   |  |  |  |

|         |      | single-ended, or temperature sensor.                                                                       |         |     |                                                                                   |  |  |  |

|         |      | 12                                                                                                         | 11      | 10  | Function                                                                          |  |  |  |

|         |      | 0                                                                                                          | 0       | X 1 | Pseudo differential bipolar pairs; INx- input is VREF/2 $\pm$ 0.1 V.              |  |  |  |

| [12:10] | INCC | 0                                                                                                          | 1       | 0   | Pseudo differential bipolar pairs; INx- is COM = $V_{REF}/2 \pm 0.1$ V.           |  |  |  |

|         |      | 0                                                                                                          | 1       | 1   | Temperature sensor.                                                               |  |  |  |

|         |      | 1                                                                                                          | 0       | Х   | Pseudo differential unipolar pairs; INx- input is GND $\pm$ 0.1 V.                |  |  |  |

|         |      | 1                                                                                                          | 1       | 0   | Pseudo differential unipolar pairs; INx- is COM = GND $\pm$ 0.1 V.                |  |  |  |

|         |      | 1                                                                                                          | 1       | 1   | Singled-ended; INx referenced to GND.                                             |  |  |  |

|         |      | Input channel selection.                                                                                   |         |     |                                                                                   |  |  |  |

|         |      | 9                                                                                                          | 8       | 7   | Channel selected.                                                                 |  |  |  |

| 10, 71  | INx  | 0                                                                                                          | 0       | 0   | INO                                                                               |  |  |  |

| [9 :7]  |      | 0                                                                                                          | 0       | 1   | IN1                                                                               |  |  |  |

|         |      |                                                                                                            |         |     |                                                                                   |  |  |  |

|         |      | 1                                                                                                          | 1       | 1   | IN7                                                                               |  |  |  |

|         |      | Selection of bandwidth for low-pass filter.                                                                |         |     |                                                                                   |  |  |  |

| [6]     | BW   | 0 = ¼ BW, an additional internal series resistor to limit the noise. Maximum throughput must be            |         |     |                                                                                   |  |  |  |

| [6]     | DVV  | reduced to 1/4.                                                                                            |         |     |                                                                                   |  |  |  |

|         |      | 1 = Full bandwidth.                                                                                        |         |     |                                                                                   |  |  |  |

|         | REF  | Reference or buffer selection. Selection of internal, external, external buffered, and enabling of the     |         |     |                                                                                   |  |  |  |

|         |      |                                                                                                            | tempera |     |                                                                                   |  |  |  |

| 15 01   |      | 5                                                                                                          | 4       | 3   | Function                                                                          |  |  |  |

| [5 : 3] |      | 0                                                                                                          | 0       | 0   | Internal reference and temperature sensor enabled. REF = 2.5 V buffered           |  |  |  |

|         |      |                                                                                                            |         |     | output.                                                                           |  |  |  |

|         |      | 0                                                                                                          | 0       | 1   | Internal reference and temperature sensor enabled. REF = 4.096 V buffered output. |  |  |  |

|         |      |                                                                                                            |         |     |                                                                                   |  |  |  |

# **Data Sheet**

|         |     | 0                                                                              | 1 | 0                                                          | Use external reference on REF. Temperature sensor enabled. Internal buffer disabled.                                  |  |  |  |

|---------|-----|--------------------------------------------------------------------------------|---|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

|         |     | 0                                                                              | 1 | 1                                                          | Use external reference on REFIN. Temperature sensor enabled. Internal buffer enabled.                                 |  |  |  |

|         |     | 1                                                                              | 0 | 0                                                          | Invalid.                                                                                                              |  |  |  |

|         |     | 1                                                                              | 0 | 1                                                          | Invalid.                                                                                                              |  |  |  |

|         |     | 1                                                                              | 1 | 0                                                          | Use external reference on REF. Temperature sensor disable, internal reference disabled and internal buffer disabled.  |  |  |  |

|         |     | 1                                                                              | 1 | 1                                                          | Use external reference on REFIN. Temperature sensor disable, internal reference disabled and internal buffer enabled. |  |  |  |

|         | SEQ | Channel sequencer. Allows for scanning channels in an IN0 to IN [7:0] fashion. |   |                                                            |                                                                                                                       |  |  |  |

|         |     | 2                                                                              | 1 | Function                                                   |                                                                                                                       |  |  |  |

| [2 : 1] |     | 0                                                                              | 0 | Disable sequencer.                                         |                                                                                                                       |  |  |  |

| [2.1]   |     | 0                                                                              | 1 | No effect.                                                 |                                                                                                                       |  |  |  |

|         |     | 1                                                                              | 0 | Scan IN0 to IN [7:0] (set in CFG [9:7]), then temperature. |                                                                                                                       |  |  |  |

|         |     | 1                                                                              | 1 | Scan II                                                    | N0 to IN [7:0] (set in CFG [9:7])                                                                                     |  |  |  |

|         | RB  | Read back the CFG register.                                                    |   |                                                            |                                                                                                                       |  |  |  |

| [0]     |     | 0 = Read back current configuration at end of code.                            |   |                                                            |                                                                                                                       |  |  |  |

|         |     | 1 = Do not read back current configuration at end of code.                     |   |                                                            |                                                                                                                       |  |  |  |

#### **General Timing Without a Busy Indicator**

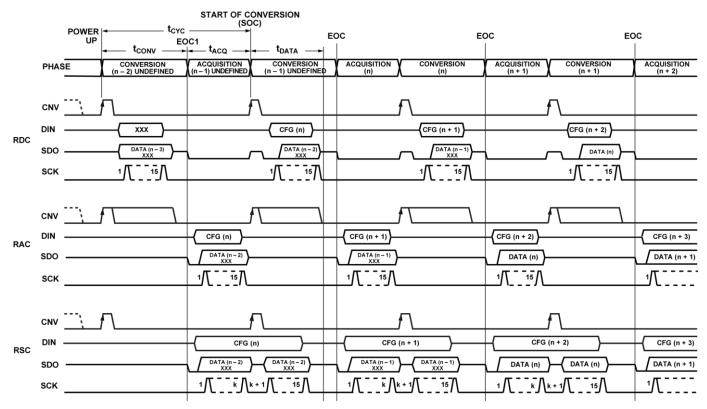

Figure 39 details the timing for all three modes: read/write during conversion (RDC), read/write after conversion (RAC), and read/write spanning conversion (RSC). Note that the gating item for both CFG and code readback is at the end of conversion (EOC). Make sure CNV is high at EOC, so the busy indicator is disabled.

The data access should happen during the safe data reading/writing time,  $t_{DATA}$ . If the full CFG word was not written to before EOC, it is discarded and the current configuration remains. If the conversion result is not read out fully prior to EOC, it is lost as the ADC updates SDO with the MSB of the current conversion. When CNV is brought low after EOC, SDO is driven from high impedance to the MSB. Falling SCK edges clock out bits starting with MSB -1. The SCK can idle high or low.

From power-up, in any read/write mode, the first three conversion results are undefined because a valid CFG does not take place until the 2nd EOC; thus two dummy conversions are required. Also, if the state machine writes the CFG during the power-up state (RDC shown), the CFG register needs to be rewritten again at the next phase. Note that the first valid data occurs in Phase (n + 1) when the CFG register is written during Phase (n - 1).

Note: n =14 for no readback of CFG; n = 28 for readback of CFG Figure 39. General Interface Timing for the ZJC2103-14 Without a Busy Indicator

#### **General Timing with a Busy Indicator**

Figure 40 details the timing for all three modes: read/write during conversion (RDC), read/write after conversion (RAC), and read/write spanning conversion (RSC). If CNV is low at EOC, the busy indicator is enabled. In addition, to generate the busy indicator properly, the host must provide a minimum of 15 SCK falling edges to return SDO to high impedance because the last bit on SDO remains active.

From power-up, in any read/write mode, the first three conversion results are undefined because a valid CFG does not take place until

the 2nd EOC; thus two dummy conversions are required. If the host writes the CFG during the power-up state (RDC shown), the CFG register needs to be rewritten again at the next phase. Note that the first valid data occurs in Phase (n + 1) when the CFG register is written during Phase (n - 1).

Note: n = 15 for no readback of CFG; n = 29 for readback of CFG Figure 40. General Interface Timing for the ZJC2103-14 With a Busy Indicator

#### **Channel Sequencer**

ZJC2103-14 channels can be scanned as singles or pairs, with or without the temperature sensor.

The sequencer starts with IN0 and ends with IN [7:0] set in CFG [9:7]. For paired channels, the channels are paired depending on the last channel set in CFG [9:7]. Note that in sequencer mode, the channels are always paired with the positive input on the even channels (IN0, IN2, IN4, IN6), and with the negative input on the odd channels (IN1, IN3, IN5, IN7).

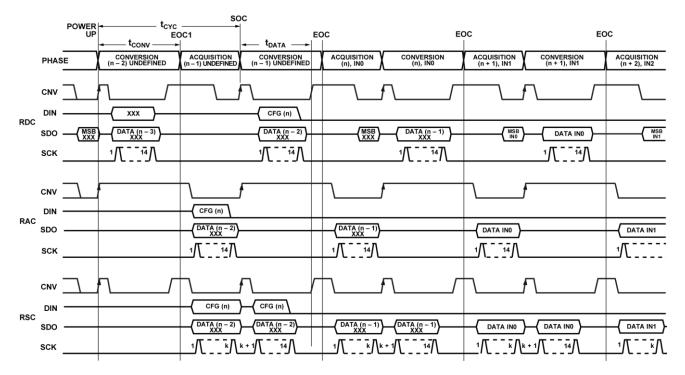

Figure 41 shows the timing for all three modes without a busy indicator. The sequencer can also be used with the busy indicator.

For sequencer operation, the CFG register should be set during the (n - 1) phase. On phase (n), the sequencer setting takes place and acquires IN0. The first valid conversion code is available at phase (n + 1). After the last channel set in CFG [9:7] is converted, the internal temperature sensor data is output (if enabled), followed by acquisition of IN0.

# ZJC2103-14

Figure 41. General Channel Sequencer Timing Without a Busy Indicator

#### **RAC Without a Busy Indicator**

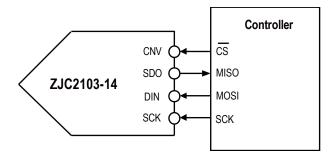

ZJC2103-14 connects to the host as shown in Figure 42, and the timing is shown is Figure 43.

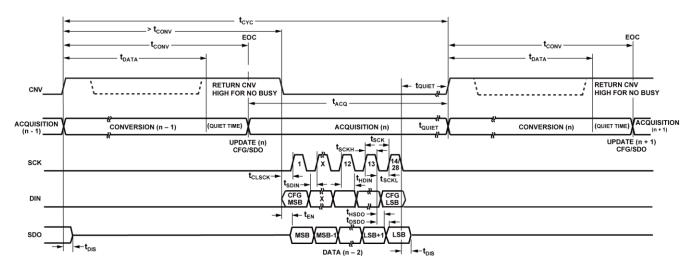

A rising edge on CNV initiates a conversion, pushes SDO to high impedance, and ignores data present on DIN. After a conversion is initiated, it continues until completion independent of the state of CNV. CNV must be returned high before the t<sub>DATA</sub> elapses, and then held high beyond the conversion time t<sub>CONV</sub>, to avoid the busy indicatorgeneration.

After the conversion is complete, the ZJC2103-14 enters the acquisition phase and powers down. While CNV is low, both a CFG update and a data readback take place. The first 14 SCK rising edges are used to update the CFG, and the first 13 SCK falling edges clock out the conversion results starting with MSB - 1. All 14 bits of CFG [13:0] must be written, otherwise they are ignored.

After the 14th (or 28th) SCK falling edge, or when CNV goes high (whichever happens first), SDO returns to high impedance.

Figure 42. Connection without a Busy Indicator

Figure 43. Timing of RACwithout a Busy Indicator

#### **RAC** with a Busy Indicator

ZJC2103-14 connects to the host as shown in Figure 44, and the timing is shown is Figure 45.

A rising edge on CNV initiates a conversion, pushes SDO to high impedance, and ignores data present on DIN. After a conversion is initiated, it continues until completion independent of the state of CNV. CNV must be returned low before the t<sub>DATA</sub> elapses, and then held low beyond the conversion time t<sub>CONV</sub>, to generate the busy indicator.

After the conversion is complete, the ZJC2103-14 enters the acquisition phase and powers down. While CNV is low, both a CFG update and a data readback take place. The first 14 SCK rising edges are used to update the CFG, and the first 14 SCK falling edges clock out the conversion results. All 14 bits of CFG [13:0] must be written, otherwise they are ignored.

After the 15th (or 29th) SCK falling edge, or when CNV goes high (whichever happens first), SDO returns to high impedance.

Figure 44. Connection with a Busy Indicator

Figure 45. Timing of RAC with a Busy Indicator

# **Layout Guidelines**

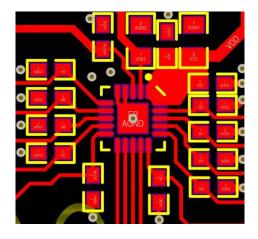

For optimum performance of the device, good PCB layout practices are recommended, including:

- Avoid running digital lines under the device, which may couple noise onto the die, unless a ground plane under the ZJC2103-14 is used as a shield. Fast switching signals such as CNV or clocks should not be placed close to the analog signal path. Crossover of digital and analog signals should be avoided.

- At least one ground plane should be used. It can be common or split between the digital and analog sections. In the latter case, the planes should be joined close to the ZJC2103-14.

- The ZJC2103-14 external voltage reference input, REF, has a dynamic input impedance and should be decoupled with 10 µF ceramic capacitors to minimize parasitic inductances. This is done by placing the reference decoupling ceramic capacitor close to, ideally right up against, the REF and GND pins and connecting them with wide, low impedance trace.

• The power supply  $V_{DD}$  of ZJC2103-14 should be decoupled with 10  $\mu$ F and 100 nF ceramic capacitors, placed close to the ZJC2103-14 and connected using short, wide traces to provide low impedance paths and to reduce the effect of noises on the power supply lines.

Figure 46 is an example of the guidance.

Figure 46. Example Layout and Routing of ZJC2103-14

### **Outline Dimensions**

### **Ordering Guide**

|   | Model      | Package | Orderable Device | Resolution (bit) | Supply Voltage (V) | Temperature<br>Range(°C) | ExternalPackage |

|---|------------|---------|------------------|------------------|--------------------|--------------------------|-----------------|

| _ | ZJC2103-14 | QFN-20  | ZJC2103-14ATPER  | 14               | 2.3 to 5.5         | - 40 to + 85             | 13" Reel        |

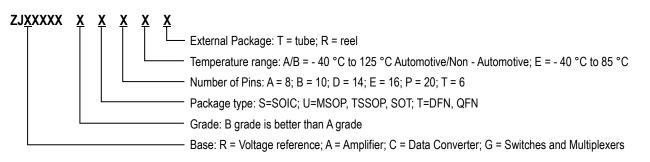

## **Product Order Model**

# **Related Parts**

| Part Number                          | Description                                                             | Comments                                                                                                                                             |  |  |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| ADC                                  |                                                                         |                                                                                                                                                      |  |  |  |  |  |  |

| ZJC2000/2010                         | 18-bit 400 kSPS/200 kSPS SAR ADC                                        | Fully differential input, SINAD 99.3 dB, THD - 113 dB                                                                                                |  |  |  |  |  |  |

| ZJC2001/2011                         | 16-bit 500 kSPS/250 kSPS SAR ADC                                        | Fully differential input, SINAD 95.3 dB, THD - 113 dB                                                                                                |  |  |  |  |  |  |

| ZJC2002/2012                         |                                                                         | Pseudo-differential unipolar input, SINAD 91.7 dB, THD - 105 dB                                                                                      |  |  |  |  |  |  |

| ZJC2003/2013                         | 16-bit 500 kSPS/250 kSPS SAR ADC                                        | Pseudo-differential bipolar input, SINAD 91.7 dB, THD - 105 dB                                                                                       |  |  |  |  |  |  |

| ZJC2004/2014                         | 18-bit 400 kSPS/200 kSPS SAR ADC                                        | Pseudo-differential unipolar input, SINAD 94.2 dB, THD - 105 dB                                                                                      |  |  |  |  |  |  |

| ZJC2005/2015                         | 10-01 400 KSF 3/200 KSF 3 SAN ADC                                       | Pseudo-differential bipolar input, SINAD 94.2 dB, THD - 105 dB                                                                                       |  |  |  |  |  |  |

| ZJC2007/2017                         | 14-bit 600 kSPS/300 kSPS SAR ADC                                        | Pseudo-differential unipolar input, SINAD 85 dB, THD - 105 dB                                                                                        |  |  |  |  |  |  |

| ZJC2008/2018                         |                                                                         | Pseudo-differential bipolar input, SINAD 85 dB, THD - 105 dB                                                                                         |  |  |  |  |  |  |

| ZJC2100/1-18                         | 18-bit 400 kSPS/200 kSPS 4-ch differential SAR A                        |                                                                                                                                                      |  |  |  |  |  |  |

| ZJC2100/1-16                         | 16-bit 500 kSPS/250 kSPS 4-ch differential SAR A                        |                                                                                                                                                      |  |  |  |  |  |  |

| ZJC2102/3-18                         | 18-bit 400 kSPS/200 kSPS 8-ch pseudo-differentia                        |                                                                                                                                                      |  |  |  |  |  |  |

| ZJC2102/3-16                         | 16-bit 500 kSPS/250 kSPS 8-ch pseudo-differentia                        |                                                                                                                                                      |  |  |  |  |  |  |

| ZJC2102/3-14                         | 14-bit 600 kSPS/300 kSPS 8-ch pseudo-differentia                        |                                                                                                                                                      |  |  |  |  |  |  |