# 具有开漏和推挽输出的 LMV7235 和 LMV7239 75ns、超低功耗、低压、轨至轨输入比较器

# 特性

● V<sub>S</sub> = 5V, T<sub>A</sub> = 25°C (典型值,除非另有说明)

● 传播延迟: 75ns

● 低电源电流: 65µA

● 轨至轨输入

● 开漏和推挽输出

● 非常适合 2.7V 和 5V 单电源 应用

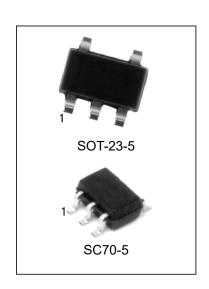

● 采用节省空间的封装: SOT-23-5 和 SC70-5 封装

# 产品订购信息

| 产品名称         | 封装       | 打印名称       | 包装 | 包装数量     |

|--------------|----------|------------|----|----------|

| LMV7235M5/TR | SOT-23-5 | V7235,C21A | 编带 | 3000 只/盒 |

| LMV7235M7/TR | SC70-5   | V7235,C21  | 编带 | 3000 只/盘 |

| LMV7239M5/TR | SOT-23-5 | V7239,C20A | 编带 | 3000 只/盒 |

| LMV7239M7/TR | SC70-5   | V7239,C20  | 编带 | 3000 只/盘 |

#### 说明

LMV7235 和 LMV7239 是 75ns 超低功耗低压比较器。这些器件可在 2.7V 至 5.5V 的完整电源电压范围内正常运行。这些器件可实现 75ns 的传播延迟,而在 5V 电压下仅消耗 65μA 的电源电流。

LMV7235 和 LMV7239 具有更大的轨至轨共模电压范围。输入共模电压范围可基于地电压向下扩展 200mV 并基于电源电压向上扩展 200mV,从而允许接地感应和电源感应。

LMV7235 具有开漏输出。通过连接一个外部电阻器,该比较器的输出可以用作电平转换器。LMV7239 具有推挽式输出级。凭借此特性,器件无需外部上拉电阻器即可运行。

LMV7235 和 LMV7239 采用 5 引脚 SC70 和 5 引脚 SOT-23 封装, 因此非常适合需要小尺寸和低功耗特性的系统。

### 应用

- 便携式和电池供电类系统

- 机顶盒

- 高速差分线路接收器

- 窗口比较器

- 过零检测器

- 高速采样电路

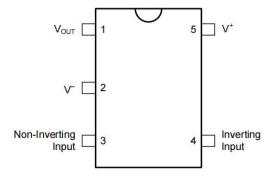

# 引脚配置和功能

SOT23-5/SC70-5

| P   | IN               | I/O | DESCRIPTION        |  |  |  |  |

|-----|------------------|-----|--------------------|--|--|--|--|

| NO. | NAME             | 1/0 | DESCRIPTION        |  |  |  |  |

| 1   | V <sub>OUT</sub> | 0   | Output             |  |  |  |  |

| 2   | V-               | Р   | Negative Supply    |  |  |  |  |

| 3   | IN <sup>+</sup>  | I   | Noninverting Input |  |  |  |  |

| 4   | IN-              | I   | Inverting Input    |  |  |  |  |

| 5   | V <sup>+</sup>   | Р   | Positive Supply    |  |  |  |  |

# **Absolute Maximum Ratings**

Over operating free-air temperature range (unless otherwise noted)(1)

| Paramete                         | Parameter              |                        |                  |      |  |  |

|----------------------------------|------------------------|------------------------|------------------|------|--|--|

| Differential Input Voltage       |                        |                        | ± Supply Voltage | V    |  |  |

| Output Short Circuit Duration    |                        |                        | See (2)          |      |  |  |

| Supply Voltage (V+ - V−)         |                        | 6                      | V                |      |  |  |

| Voltage at Input/Output Pins     | (V <sup>-</sup> )-0.3  | (V <sup>+</sup> ) +0.3 | V                |      |  |  |

| Current at Input Pin (3)         |                        | ±10                    | mA               |      |  |  |

| Storage Temperature, Tstg        | <b>–</b> 65            | 150                    | °C               |      |  |  |

| Junction Temperature,TJ          |                        |                        | 150              | °C   |  |  |

| Lead Temperature (Soldering, 10  | seconds)               | -                      | 245              | °C   |  |  |

|                                  | Human-body model (HBM) |                        | ±1000            | \/   |  |  |

| Electrostatic discharge          | Machine model (MM)     |                        | ±100             | V    |  |  |

| Junction-to-ambient thermal SC70 |                        |                        | 478              | °C/W |  |  |

| resistance R <sub>θJA</sub>      | SOT-23                 |                        | 265              | °C/W |  |  |

<sup>1.</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Parameter                                          | Min | Max | Unit |

|----------------------------------------------------|-----|-----|------|

| Supply Voltages (V <sup>+</sup> - V <sup>-</sup> ) | 2.7 | 5.5 | V    |

| Temperature Range <sup>(1)</sup>                   | -40 | 85  | °C   |

<sup>(1)</sup> The maximum power dissipation is a function of  $TJ_{(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PCB.

<sup>2.</sup> Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of ±30mA over long term may adversely affect reliability.

<sup>3、</sup>Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings.

#### **Electrical Characteristics, 2.7 V**

Unless otherwise specified, all limits ensured for  $T_A = 25$ °C,  $V_{CM} = V + /2$ , V + = 2.7 V, V - = 0 V - 10 V

| Symbol               | Parameter                             | Test Co                                           | onditions                                     | Min                 | Тур         | Max            | Unit |

|----------------------|---------------------------------------|---------------------------------------------------|-----------------------------------------------|---------------------|-------------|----------------|------|

|                      | liament Officet Voltage               |                                                   |                                               | -6                  | ±0.8        | +6             | \/   |

| Vos                  | Input Offset Voltage                  | At temp extremes                                  |                                               | -8                  |             | +8             | mV   |

| I <sub>B</sub>       | Input Bias Current                    |                                                   |                                               |                     | 30          | 400            | nA   |

| IB                   | Input bias Current                    | At temp extremes                                  |                                               |                     |             | 600            | IIA  |

| los                  | Input Offset Current                  |                                                   |                                               |                     | 5           | 200            | nA   |

| 108                  | input Onset Ourrent                   | At temp extremes                                  |                                               |                     |             | 400            | 11/1 |

| CMRR                 | Common-Mode Rejection Ratio           | $0 \text{ V} < V_{CM} < 2.7 \text{ V}^{(1)}$      |                                               | 52                  | 62          |                | dB   |

| PSRR                 | Power Supply Rejection Ratio          | V+ = 2.7 V to 5 V                                 |                                               | 65                  | 85          |                | dB   |

| $V_{CM}$             | Input Common-Mode Voltage             | CMRR > 50 dB                                      |                                               | V <sup>-</sup> -0.1 | -0.2 to 2.9 | V+ +0.1        | V    |

| V CM                 | Range                                 | CIVIL(1 > 50 db                                   | At temp extremes                              | V-                  |             | V <sup>+</sup> | v    |

|                      | Output Swing High (LMV7239            | I <sub>L</sub> = 4 mA, V <sub>ID</sub> = 500      | mV                                            | V+ -0.35            | V+ -0.26    |                | V    |

|                      | only)                                 | $I_L = 0.4 \text{ mA}, V_{ID} = 50$               |                                               | V+ -0.02            |             | V              |      |

| Vo                   |                                       | $I_L = -4 \text{ mA}, V_{ID} = -50$               |                                               | 230                 | 350         | mV             |      |

|                      | Output Swing Low                      | At temp extremes                                  |                                               |                     | 450         |                |      |

|                      |                                       | $I_L = -0.4 \text{ mA}, V_{ID} = -0.4 \text{ mA}$ | -500 mV                                       |                     | 15          |                | mV   |

|                      |                                       | Sourcing, Vo = 0 V (                              | Sourcing, V <sub>0</sub> = 0 V (LMV7239 only) |                     | 15          |                | mA   |

| Isc                  | Output Short Circuit Current          | Sinking, V <sub>0</sub> = 2.7 V                   | (LMV7235, R <sub>L</sub> = 10 k)              |                     | 20          |                | mA   |

|                      | 0 10 1                                | No load                                           |                                               |                     | 52          | 85             |      |

| Is                   | Supply Current                        | At temp extremes                                  |                                               |                     |             | 100            | μA   |

|                      |                                       | Overdrive = 20 mV (                               | C <sub>LOAD</sub> = 15 pF <sup>(2)</sup>      |                     | 96          |                | ns   |

| $t_{PD}$             | Propagation Delay                     | Overdrive = 50 mV (                               |                                               |                     | 87          |                | ns   |

|                      |                                       | Overdrive = 100 mV                                | C <sub>LOAD</sub> = 15 pF <sup>(2)</sup>      |                     | 85          |                | ns   |

| t <sub>SKEW</sub>    | Propagation Delay Skew (LMV7239 only) | Overdrive = 20 mV (                               |                                               | 2                   |             | ns             |      |

|                      | a                                     | LMV7239 10% to 90%                                |                                               |                     | 1.7         |                | ns   |

| t <sub>r</sub>       | Output Rise Time                      | LMV7235 10% to 90                                 |                                               | 112                 |             | ns             |      |

| t <sub>f</sub>       | Output Fall Time                      | 90% to 10%                                        |                                               | 1.7                 |             | ns             |      |

| I <sub>LEAKAGE</sub> | Output Leakage Current (LMV7235 only) |                                                   |                                               |                     | 3           |                | nA   |

<sup>(1)</sup> CMRR is not linear over the common mode range. Limits are guaranteed over the worst case from 0 to  $V_{\text{CC/2}}$  or  $V_{\text{CC/2}}$  to  $V_{\text{CC}}$ .

<sup>(2)</sup> A 10k pullup resistor was used when measuring the LMV7235. The rise time of the LMV7235 is a function of the R-C time constant.

<sup>(3)</sup> Propagation Delay Skew is defined as the absolute value of the difference between tpdlh and tpdhl.

# **Electrical Characteristics, 5 V**

Unless otherwise specified, all limits ensured for  $T_A$  = 25°C,  $V_{CM}$  = V + /2, V + = 5 V, V - = 0 V.

| Symbol            | Parameter                             | Test Cor                                       | nditions                                 | Min      | Тур         | Max            | Unit |

|-------------------|---------------------------------------|------------------------------------------------|------------------------------------------|----------|-------------|----------------|------|

|                   | In t Off t \ / -  t                   |                                                |                                          | -6       | ±1          | +6             | \/   |

| Vos               | Input Offset Voltage                  | At temp extremes                               |                                          | -8       |             | +8             | mV   |

|                   | In and Ding Comment                   |                                                |                                          |          | 30          | 400            | A    |

| l <sub>Β</sub>    | Input Bias Current                    | At temp extremes                               |                                          |          |             | 600            | nA   |

| 1                 | Innuit Officet Current                |                                                |                                          |          | 5           | 200            | nΛ   |

| los               | Input Offset Current                  | At temp extremes                               |                                          | 400      |             |                | nA   |

| CMRR              | Common-Mode Rejection Ratio           | 0 V < V <sub>CM</sub> < 5 V                    | 52                                       | 67       |             | dB             |      |

| PSRR              | Power Supply Rejection Ratio          | V+ = 2.7 V to 5 V                              |                                          | 65       | 85          |                | dB   |

|                   | Input Common-Mode                     |                                                |                                          | V⁻ −0.1  | -0.2 to 5.2 | V+ +0.1        | .,   |

| $V_{CM}$          | Voltage Range                         | CMRR > 50dB At temp extremes                   |                                          | V-       |             | V <sup>+</sup> | V    |

|                   | Output Swing High                     | I <sub>L</sub> = 4 mA, V <sub>ID</sub> = 500 n | V+ -0.25                                 | V+ -0.15 |             | V              |      |

|                   | (LMV7239 only)                        | I <sub>L</sub> = 0.4 mA, V <sub>ID</sub> = 500 |                                          |          | V+ -0.01    |                | V    |

| Vo                |                                       | I <sub>L</sub> = −4 mA,                        |                                          |          | 230         | 350            | .,   |

|                   | Output Swing Low                      | V <sub>ID</sub> = −500 mV                      | = -500 mV At temp extremes               |          |             | 450            | mV   |

|                   |                                       | $I_L = -0.4 \text{ mA}, V_{ID} = -5$           | 500 mV                                   |          | 10          |                | mV   |

|                   |                                       | Sourcing, V <sub>0</sub> = 0 V                 |                                          | 25       | 55          |                | A    |

| L                 | Output Chart Circuit Current          | (LMV7239 only)                                 | At temp extremes                         | 15       |             |                | mA   |

| Isc               | Output Short Circuit Current          | Sinking, V <sub>0</sub> = 5 V                  |                                          | 30       | 60          |                | mA   |

|                   |                                       | (LMV7235, R <sub>L</sub> = 10k)                | At temp extremes                         | 20       |             |                | mA   |

| I.                | Supply Current                        | No load                                        |                                          |          | 65          | 95             |      |

| ls                | Supply Current                        | NO IOAU                                        | At temp extremes                         |          |             | 110            | μA   |

|                   |                                       | Overdrive = 20 mV C                            | <sub>LOAD</sub> = 15 pF <sup>(1)</sup>   |          | 89          |                | ns   |

| t <sub>PD</sub>   | Propagation Delay                     | Overdrive = 50 mV C                            | <sub>LOAD</sub> = 15 pF <sup>(1)</sup>   |          | 82          |                | ns   |

|                   |                                       | Overdrive = 100 mV                             | C <sub>LOAD</sub> = 15 pF <sup>(1)</sup> |          | 75          |                | ns   |

| t <sub>skew</sub> | Propagation Delay Skew (LMV7239 only) | Overdrive = 20 mV <sup>(2)</sup>               |                                          | 1        |             | ns             |      |

|                   |                                       | LMV7239 10% to 90%                             |                                          |          | 1.2         |                | ns   |

| t <sub>r</sub>    | Output Rise Time                      | LMV7235 10% to 90%                             |                                          | 100      |             | ns             |      |

| t <sub>f</sub>    | Output Fall Time                      | 90% to 10%                                     |                                          |          | 1.2         |                | ns   |

| ILEAKAGE          | Output Leakage Current (LMV7235 only) |                                                |                                          |          | 3           |                | nA   |

<sup>(1)</sup> A 10k pullup resistor was used when measuring the LMV7235. The rise time of the LMV7235 is a function of the R-C time constant.

<sup>(2)</sup> Propagation Delay Skew is defined as the absolute value of the difference between tpdlh and tpdhl.

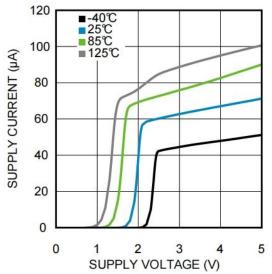

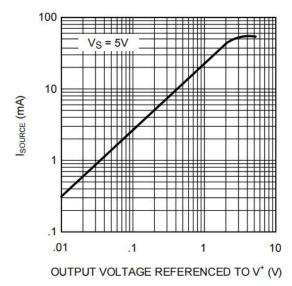

# **Typical Characteristics**

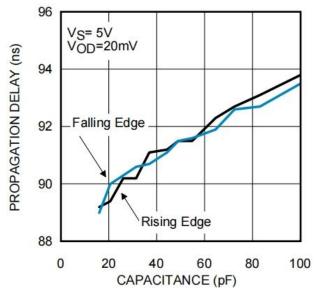

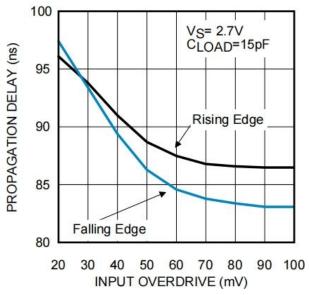

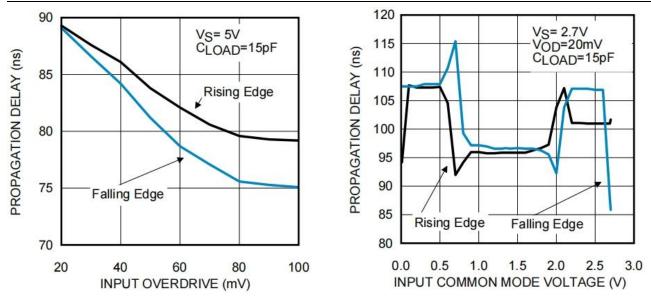

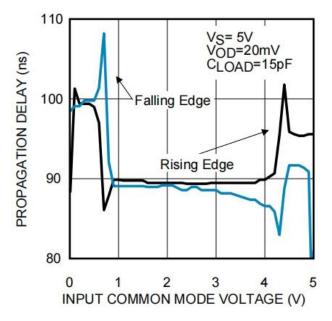

(Unless otherwise specified,  $V_S = 5V$ ,  $C_L = 10pF$ ,  $T_A = 25$ °C).

Figure 1. Supply Current vs. Supply Voltage

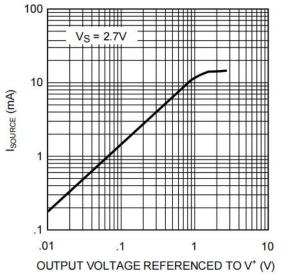

Figure 2. Sourcing Current vs. Output Voltage

Figure 3. Sourcing Current vs. Output Voltage

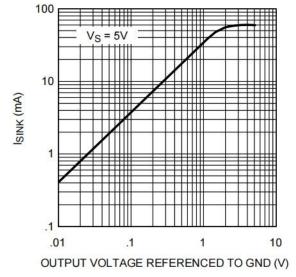

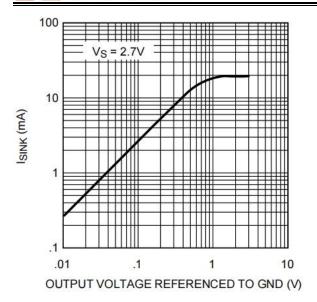

Figure 4. Sinking Current vs. Output Voltage

Figure 5. Sinking Current vs. Output Voltage

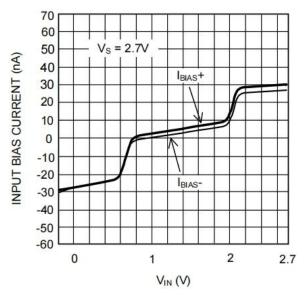

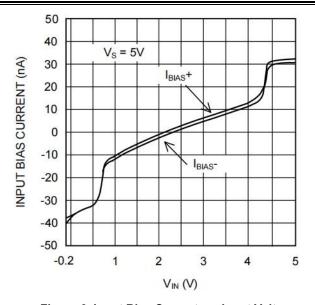

Figure 7. Input Bias Current vs. Input Voltage

Figure 6. Input Bias Current vs. Input Voltage

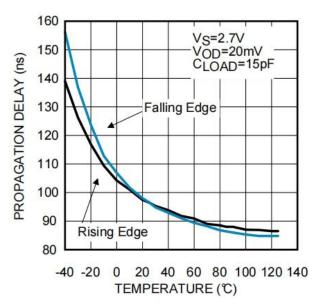

Figure 8. Propagation Delay vs. Temperature

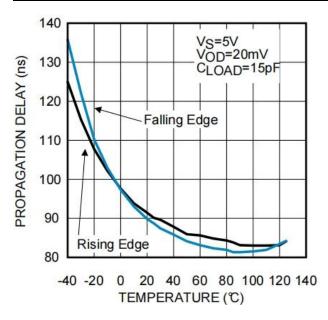

Figure 9. Propagation Delay vs. Temperature

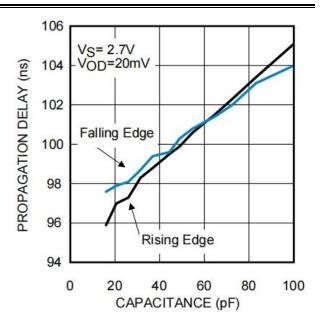

Figure 10. Propagation Delay vs. Capacitive Load

Figure 11. Propagation Delay vs. Capacitive Load

Figure 12. Propagation Delay vs. Input Overdrive

Figure 13. Propagation Delay vs. Input Overdrive

Figure 14. Propagation Delay vs. Common-Mode Voltage

Figure 15. Propagation Delay vs. Common-Mode Voltage

## **Detailed Description**

The LMV7235 and LMV7239 are ultra low power, low voltage, 75-ns comparators. They are ensured to operate over the full supply voltage range of 2.7 V to 5.5 V. These devices achieve a 75-ns propagation delay while consuming only 65  $\mu$ A of supply current at 5 V.

The LMV7235 and LMV7239 have a greater than rail-to-rail common-mode voltage range. The input commonmode voltage range extends 200 mV below ground and 200 mV above supply, allowing both ground and supply sensing.

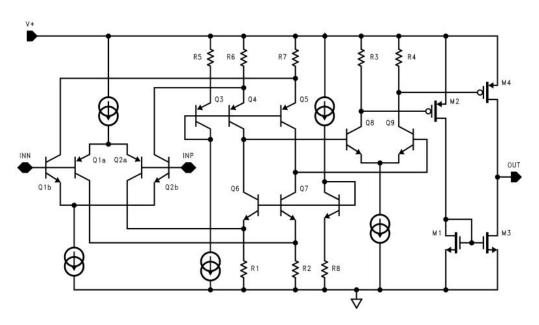

#### **Functional Block Diagram**

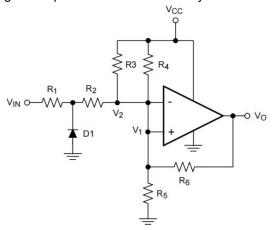

Figure 16. Simplified Schematic of LMV7239

# **Feature Description**

#### Input Stage

The LMV7235 and LMV7239 are rail-to-rail input and output. The typical input common-mode voltage range of -0.2 V below the ground to 0.2 V above the supply. The LMV7235 and LMV7239 use a complimentary PNP and NPN input stage in which the PNP stage senses common-mode voltage near V - and the NPN stage senses common-mode voltage near V  $\cdot$  . If either of the input signals falls below the negative common mode limit, the parasitic PN junction formed by the substrate and the base of the PNP will turn on resulting in an increase of input bias current.

If one of the inputs goes above the positive common mode limit, the output will still maintain the correct logic level as long as the other input stays within the common mode range. However, the propagation delay will increase. When both inputs are outside the common-mode voltage range, current saturation occurs in the input stage, and the output becomes unpredictable.

The propagation delay does not increase significantly with large differential input voltages. However, large differential voltages greater than the supply voltage should be avoided to prevent damage to the input stage.

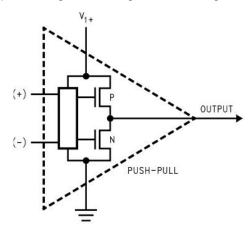

#### Output Stage: LMV7239

The LMV7239 has a push-pull output. When the output switches, there is a low resistance path between  $V_{CC}$  and ground, causing high output sinking or sourcing current during the transition.

Figure 17. LMV7239 Push-Pull Output Stage

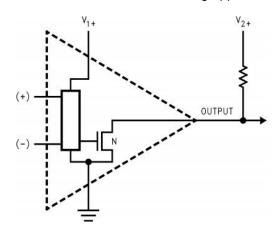

#### Output Stage: LMV7235

The LMV7235 has an open drain that requires a pull-up resistor to a positive supply voltage for the output to switch properly. The internal circuitry is identical to the LMV7239 except that the upper P channel output device M4 is absent in the Functional Block Diagram above. When the internal output transistor is off, the output voltage will be pulled up to the external positive voltage by the external pull-up resistor. This allows the output to be OR'ed with other open drain outputs on the same bus. The output pull-up resistor can be connected to any voltage level between V- and V+ for level shifting applications.

Figure 18. LMV7235 Open Drain Output

#### **Device Functional Modes**

#### **Capacitive and Resistive Loads**

The propagation delay on the rising edge of the LMV7235 depends on the load resistance and capacitance values.

#### **Noise**

Most comparators have rather low gain. This allows the output to spend time between high and low when the input signal changes slowly. The result is the output may oscillate between high and low when the differential input is near zero. The high gain of this comparator eliminates this problem. Less than 1  $\mu$ V of change on the input will drive the output from one rail to the other rail. If the input signal is noisy, the output cannot ignore the noise unless some hysteresis is provided by positive feedback. (See Hysteresis.)

#### **Hysteresis**

To improve propagation delay when low overdrive is needed hysteresis can be added.

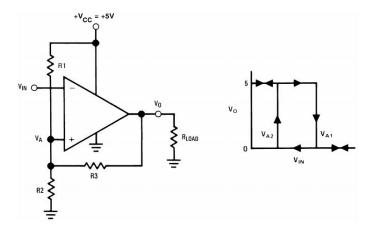

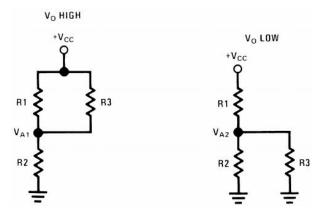

#### **Inverting Comparator With Hysteresis**

The inverting comparator with hysteresis requires a three resistor network that is referenced to the supply voltage V  $^+$  of the comparator as shown in Figure 19. When  $V_{IN}$  at the inverting input is less than  $V_A$ , the voltage at the noninverting node of the comparator ( $V_{IN} < V_A$ ), the output voltage is high (for simplicity assume VO switches as high as V  $^+$ ). The three network resistors can be represented as  $R_1$  // $R_3$  in series with  $R_2$ .

Figure 19. Inverting Comparator With Hysteresis

The lower input trip voltage VA1 is defined as:

$$V_{A1} = V_{CC}R_2 / [(R_1 // R_3) + R_2)]$$

(1)

When VIN is greater than VA, the output voltage is low or very close to ground. In this case the three network resistors can be presented as  $R_2 /\!\!/ R_3$  in series with  $R_1$ .

The upper trip voltage VA2 is defined as:

$$V_{A2} = V_{CC} (R_2 /\!/ R_3) / [(R_1) + (R_2 /\!/ R_3)]$$

(2)

The total hysteresis provided by the network is defined as  $\Delta V_A = V_{A1} - V_{A2}$ .

$$\Delta V_{A} = \frac{+V_{CC}R_{1}R_{2}}{R_{1}R_{2} + R_{1}R_{3} + R_{2}R_{3}}$$

(3)

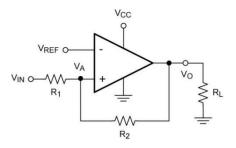

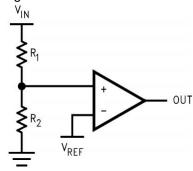

#### **Non-Inverting Comparator With Hysteresis**

A noninverting comparator with hysteresis requires a two resistor network, and a voltage reference ( $V_{REF}$ ) at the inverting input. When  $V_{IN}$  is low, the output is also low. For the output to switch from low to high,  $V_{IN}$  must rise up to  $V_{IN1}$  where  $V_{IN1}$  is calculated by:

$$\Delta V_{IN1} = \frac{V_{REF}(R_1 + R_2)}{R_2} \tag{4}$$

As soon as V<sub>O</sub> switches to V<sub>CC</sub>, V<sub>A</sub> steps to a value greater than V<sub>REF</sub> which is given by:

$$V_{A} = V_{1N} \frac{(V_{CC} - V_{IN1})R_{1}}{R_{1} + R_{2}}$$

(5)

To make the comparator switch back to its low state,  $V_{IN}$  must equal  $V_{REF}$  before  $V_A$  will again equal  $V_{REF}$ .  $V_{IN2}$  can be calculated by:

$$V_{IN2} = \frac{V_{REF}(R_1 + R_2) - V_{CC}R_1}{R_2}$$

(6)

The hysteresis of this circuit is the difference between V<sub>IN1</sub> and V<sub>IN2</sub>.

$$\Delta V_{IN} = V_{CC}R_1 / R_2. \tag{7}$$

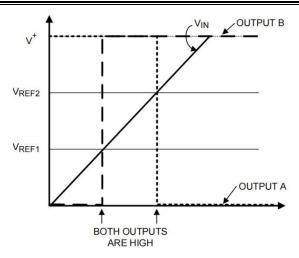

Figure 20. Noninverting Comparator With Hysteresis

Figure 21. Noninverting Comparator Thresholds

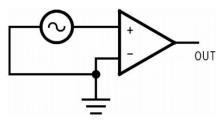

#### **Zero Crossing Detector**

In a zero crossing detector circuit, the inverting input is connected to ground and the noninverting input is connected to a 100 mV $_{PP}$  A $_{C}$  signal. As the signal at the noninverting input crosses 0V, the comparator's output changes state.

Figure 22. Simple Zero Crossing Detector

## **Zero Crossing Detector With Hysteresis**

To improve switching times and centering the input threshold to ground a small amount of positive feedback is added to the circuit. Voltage divider  $R_4$  and  $R_5$  establishes a reference voltage,  $V_1$ , at the positive input. By making the series resistance,  $R_1$  plus  $R_2$  equal to  $R_5$ , the switching condition,  $V_1 = V_2$ , will be satisfied when  $V_{IN} = 0$ .

The positive feedback resistor,  $R_6$ , is made very large with respect to  $R_5 \parallel R_6$  = 2000  $R_5$ ). The resultant hysteresis established by this network is very small ( $\Delta V_1$  < 10 mV) but it is sufficient to insure rapid output voltage transitions.

Diode  $D_1$  is used to ensure that the inverting input terminal of the comparator never goes below approximately -100 mV. As the input terminal goes negative,  $D_1$  will forward bias, clamping the node between  $R_1$  and  $R_2$  to approximately -700 mV. This sets up a voltage divider with  $R_2$  and  $R_3$  preventing  $V_2$  from going below ground. The maximum negative input overdrive is limited by the current handling ability of  $D_1$ .

Figure 23. Zero Crossing Detector With Hysteresis

#### **Threshold Detector**

Instead of tying the inverting input to 0 V, the inverting input can be tied to a reference voltage. As the input on the noninverting input passes the  $V_{REF}$  threshold, the comparator's output changes state. It is important to use a stable reference voltage to ensure a consistent switching point.

Figure 24. Threshold Detector

# **Application Information**

The LMV7235 and LMV7239 are single supply comparators with 75 ns of propagation delay and only 65  $\mu$ A of supply current.

#### **Typical Applications**

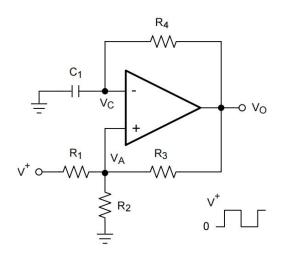

Figure 25. Square Wave Oscillator

#### **Design Requirements**

A typical application for a comparator is as a square wave oscillator. The circuit in Figure 25 generates a square wave whose period is set by the RC time constant of the capacitor  $C_1$  and resistor  $R_4$ .

#### **Detailed Design Procedure**

The maximum frequency is limited by the large signal propagation delay of the comparator and by the capacitive loading at the output, which limits the output slew rate.

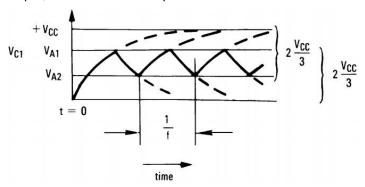

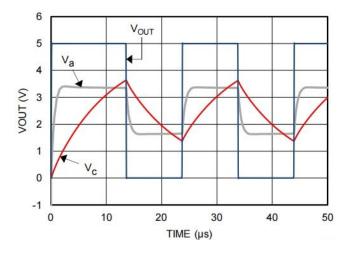

Figure 26. Square Wave Oscillator Timing Thresholds

Consider the output of Figure 25 to be high to analyze the circuit. That implies that the inverted input  $(V_C)$  is lower than the noninverting input  $(V_A)$ . This causes the C1 to be charged through R4 , and the voltage  $V_C$  increases until it is equal to the noninverting input. The value of VA at this point is:

$$V_{A1} = \frac{V_{CC} \bullet R_2}{R2 + R_1 II R_3}$$

(8)

If  $R_1 = R_2 = R_3$ , then  $V_{A1} = 2 \text{ Vcc/3}$

At this point the comparator switches pulling down the output to the negative rail. The value of V<sub>A</sub> at this point is:

$$V_{A2} = \frac{V_{CC}(R_2 IIR_3)}{R_1 + (R_2 IIR_3)}$$

(9)

If

$$R_1 = R_2 = R_3$$

, then  $V_{A2} = V_{CC}/3$ .

The capacitor  $C_1$  now discharges through R4 , and the voltage  $V_C$  decreases until it is equal to  $V_{A2}$ , at which point the comparator switches again, bringing it back to the initial stage. The time period is equal to twice the time it takes to discharge  $C_1$  from  $2V_{CC}/3$  to  $V_{CC}/3$ , which is given by  $R_4C_1 \cdot ln2$ . Hence the formula for the frequency is:

$$F = 1/(2 \cdot R_4 \cdot C_1 \cdot ln2) \tag{10}$$

The LMV7239 should be used for a symmetrical output. The LMV7235 will require a pullup resistor on the output to function, and will have a slightly asymmetrical output due to the reduced sourcing current.

#### **Application Curves**

Figure 27 shows the simulated results of an oscillator using the following values:

- 1.  $R_1 = R_2 = R_3 = R_4 = 100 \text{ k}\Omega$

- 2.  $C_1 = 100 pF$ ,  $C_L = 20 pF$

- 3. V + = 5 V, V = GND

- 4. C<sub>STRAY</sub> (not shown) from Va to GND = 10 pF

Figure 27. Square Wave Oscillator Output Waveform

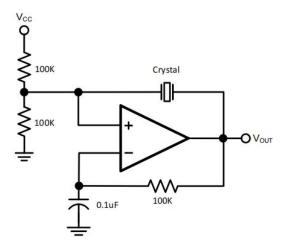

#### **Crystal Oscillator**

A simple crystal oscillator using the LMV7235 or LMV7239 is shown in Figure 28. Resistors R1 and  $R_2$  set the bias point at the comparator's noninverting input. Resistors,  $R_3$  and  $R_4$  and capacitor  $C_1$  set the inverting input node at an appropriate DC average level based on the output. The crystal's path provides resonant positive feedback and stable oscillation occurs. The output duty cycle for this circuit is roughly 50%, but it is affected by resistor tolerances and to a lesser extent by the comparator

Figure 28. Crystal Oscillator

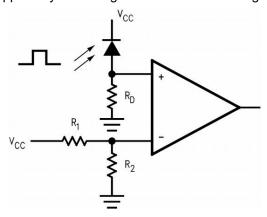

#### Infrared (IR) Receiver

The LMV7235 and LMV7239 can also be used as an infrared receiver. The infrared photo diode creates a current relative to the amount of infrared light present. The current creates a voltage across RD. When this voltage level cross the voltage applied by the voltage divider to the inverting input, the output transitions.

Figure 29. IR Receiver

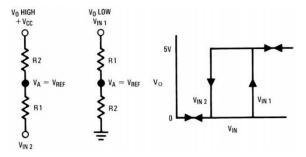

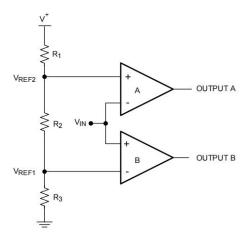

#### **Window Detector**

Figure 30. Window Detector

A window detector monitors the input signal to determine if it falls between two voltage levels. Both outputs are true (high) when  $V_{REF1} < V_{IN} < V_{REF2}$

Figure 31. Window Detector Output Signal

The comparator outputs A and B are high only when  $V_{REF1} < V_{IN} < V_{REF2}$ , or "within the window", where these are defined as:

$$V_{REF1} = R_3 / R_1 + R_2 + R_3 ) \times V +$$

(11)

$$V_{REF2} = R_2 + R_3 / R_1 + R_2 + R_3 / X + V +$$

(12)

To determine if the input signal falls outside of the two voltage levels, both inputs on each comparators can be reversed to invert the logic.

The LMV7235 with an open drain output should be used if the outputs are to be tied together for a common logic output.

Other names for window detectors are: threshold detector, level detector, and amplitude trigger or detector.

# **Power Supply Recommendations**

To minimize supply noise, power supplies should be decoupled by a  $0.01-\mu F$  ceramic capacitor in parallel with a  $10-\mu F$  capacitor.

Due to the nanosecond edges on the output transition, peak supply currents will be drawn during the time the output is transitioning. Peak current depends on the capacitive loading on the output. The output transition can cause transients on poorly bypassed power supplies. These transients can cause a poorly bypassed power supply to "ring" due to trace inductance and low self-resonance frequency of high ESR bypass capacitors.

Treat the LMV7235 and LMV7239 as high-speed devices. Keep the ground paths short and place small (low ESR ceramic) bypass capacitors directly between the V+ and V- pins.

Output capacitive loading and output toggle rate will cause the average supply current to rise over the quiescent current.

# **Physical Dimensions**

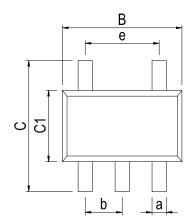

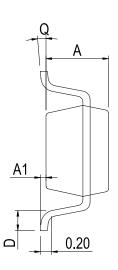

# SOT23-5

| Dimensions In Millimeters(SOT23-5) |      |      |      |      |      |      |    |      |          |          |

|------------------------------------|------|------|------|------|------|------|----|------|----------|----------|

| Symbol:                            | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        | е        |

| Min:                               | 1.05 | 0.00 | 2.82 | 2.65 | 1.50 | 0.30 | 0° | 0.30 | 0.05 BCC | 1 00 BCC |

| Max:                               | 1.15 | 0.15 | 3.02 | 2.95 | 1.70 | 0.60 | 8° | 0.40 | 0.95 BSC | 1.90 BSC |

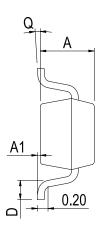

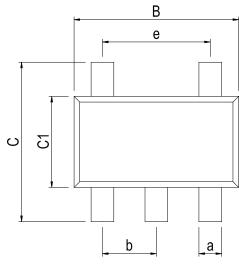

# SC70-5

| Dimensions In Millimeters(SC70-5) |      |      |      |      |      |      |    |      |      |          |

|-----------------------------------|------|------|------|------|------|------|----|------|------|----------|

| Symbol:                           | A    | A1   | В    | С    | C1   | D    | Q  | а    | b    | е        |

| Min:                              | 0.90 | 0.00 | 2.00 | 2.15 | 1.15 | 0.26 | 0° | 0.15 | 0.65 | 1.30 BSC |

| Max:                              | 1.00 | 0.15 | 2.20 | 2.45 | 1.35 | 0.46 | 8° | 0.35 | BSC  | 1.30 BSC |

20 / 22

# **Revision History**

| DATE       | REVISION                                                | PAGE    |

|------------|---------------------------------------------------------|---------|

| 2015-3-17  | New                                                     | 1-23    |

| 2023-10-31 | Document Reformatting、Update SC70-5 Physical Dimensions | 1-22、20 |

# LMV7235/LMV7239

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.