## **Regulating Pulse Width Modulators**

#### FEATURES

- 8 to 35V Operation

- 5.1V Buried Zener Reference Trimmed to ±0.75%

- 100Hz to 500kHz Oscillator Range

- Separate Oscillator Sync Terminal

- Adjustable Deadtime Control

- Internal Soft-Start

- Pulse-by-Pulse Shutdown

- Input Undervoltage Lockout with Hysteresis

- Latching PWM to Prevent Multiple Pulses

- Dual Source/Sink Output Drivers

- Low Cross Conduction Output

Stage

- Tighter Reference Specifications

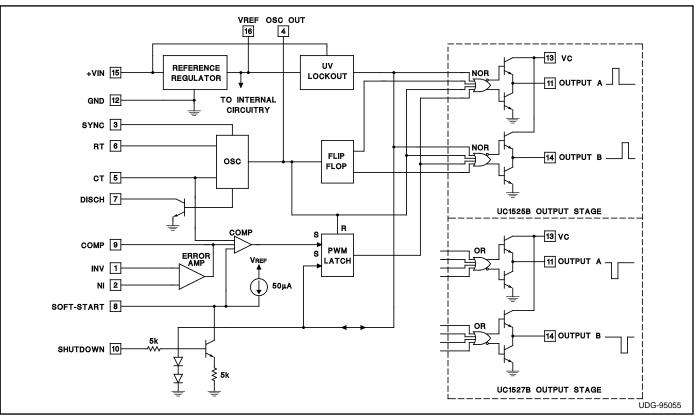

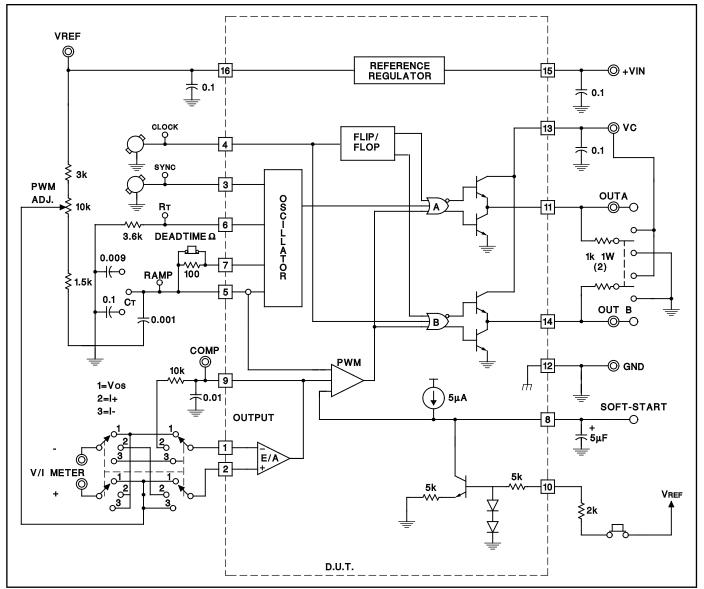

#### **BLOCK DIAGRAM**

#### DESCRIPTION

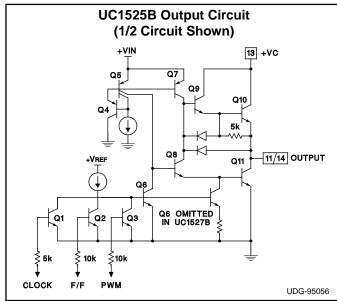

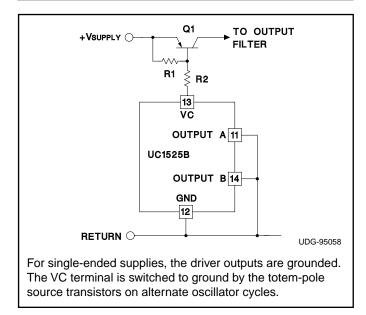

The UC1525B/1527B series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip +5.1V buried zener reference is trimmed to ±0.75% and the input common-mode range of the error amplifier includes the reference voltage, eliminating external resistors. A sync input to the oscillator allows multiple units to be slaved or a single unit to be synchronized to an external system clock. A single resistor between the CT and the discharge terminals provide a wide range of dead time adjustment. These devices also feature built-in soft-start circuitry with only an external timing capacitor required. A shutdown terminal controls both the soft-start circuitry and the output stages, providing instantaneous turn off through the PWM latch with pulsed shutdown, as well as soft-start recycle with longer shutdown commands. These functions are also controlled by an undervoltage lockout which keeps the outputs off and the soft-start capacitor discharged for sub-normal input voltages. This lockout circuitry includes approximately 500mV of hysteresis for jitter-free operation. Another feature of these PWM circuits is a latch following the comparator. Once a PWM pulse has been terminated for any reason, the outputs will remain off for the duration of the period. The latch is reset with each clock pulse. The output stages are totem-pole designs capable of sourcing or sinking in excess of 200mA. The UC1525B output stage features NOR logic, giving a LOW output for an OFF state. The UC1527B utilizes OR logic which results in a HIGH output level when OFF.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, (+VIN)                              | +40V                |

|-----------------------------------------------------|---------------------|

| Collector Supply Voltage (VC)                       | +40V                |

| Logic Inputs                                        | –0.3V to +5.5V      |

| Analog Inputs                                       | –0.3V to VIN        |

| Output Current, Source or Sink                      |                     |

| Reference Output Current                            |                     |

| Oscillator Charging Current                         |                     |

| Power Dissipation at TA = +25°C                     | 1000mW              |

| Power Dissipation at Tc = +25°C                     |                     |

| Operating Junction Temperature                      | –55°C to +150°C     |

| Storage Temperature Range                           | –65°C to +150°C     |

| Lead Temperature (Soldering, 10 sec.)               | +300°С              |

| All currents are positive into, negative out of the | specified terminal. |

| Consult Packaging Section of Databook for the       | ermal limitations   |

| and considerations of packages.                     |                     |

|                                                     |                     |

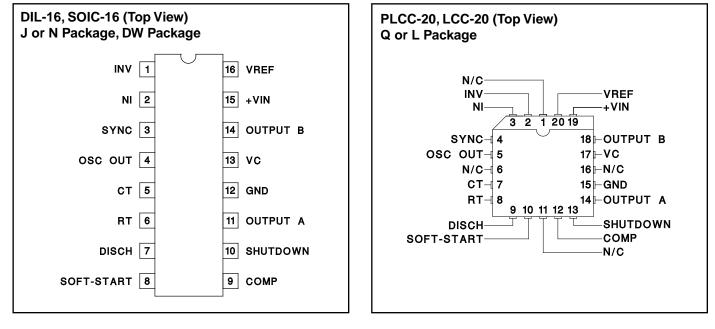

#### **CONNECTION DIAGRAMS**

#### **RECOMMENDED OPERATING CONDITIONS**

| (Note 1) | (N | lote | 1) |  |

|----------|----|------|----|--|

|----------|----|------|----|--|

| Input Voltage (+VIN)+8V to +35V                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| Collector Supply Voltage (VC)+4.5V to +35V                                                                                                     |

| Sink/Source Load Current (steady state)                                                                                                        |

| Sink/Source Load Current (peak)                                                                                                                |

| Reference Load Current                                                                                                                         |

| Oscillator Frequency Range                                                                                                                     |

| Oscillator Timing Resistor $\dots \dots \dots$ |

| Oscillator Timing Capacitor                                                                                                                    |

| Dead Time Resistor Range $\dots \dots \dots$   |

| Note 1: Range over which the device is functional and parame-                                                                                  |

| ter limits are guaranteed.                                                                                                                     |

**ELECTRICAL CHARACTERISTICS** Unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  for the UC1525B and UC1527B;  $-40^{\circ}C$  to  $+85^{\circ}C$  for the UC2525B and UC2527B;  $0^{\circ}C$  to  $+70^{\circ}C$  for the UC3525B and UC3527B; +VIN = 20V,  $T_A = T_J$ .

|                                |                                             |       | 25B/UC<br>27B/UC |       |       | JC3525<br>JC3527 | _     |       |

|--------------------------------|---------------------------------------------|-------|------------------|-------|-------|------------------|-------|-------|

| PARAMETER                      | TEST CONDITIONS                             | MIN   | TYP              | MAX   | MIN   | TYP              | MAX   | UNIT  |

| Reference Section              |                                             |       |                  |       | -     |                  |       |       |

| Output Voltage                 | $T_J = 25^{\circ}C$                         | 5.062 | 5.10             | 5.138 | 5.036 | 5.10             | 5.164 | V     |

| Line Regulation                | VIN = 8V to $35V$                           |       | 5                | 10    |       | 5                | 10    | mV    |

| Load Regulation                | I∟ = 0mA to 20mA                            |       | 7                | 15    |       | 7                | 15    | mV    |

| Temperature Stability (Note 2) | Over Operating Range                        |       | 10               | 50    |       | 10               | 50    | mV    |

| Total Output Variation         | Line, Load, and Temperature                 | 5.036 |                  | 5.164 | 5.024 |                  | 5.176 | V     |

| Short Circuit Current          | VREF = 0, TJ =25°C                          |       | 80               | 100   |       | 80               | 100   | mA    |

| Output Noise Voltage (Note 2)  | $10Hz \le f \le 10kHz$ , TJ = $25^{\circ}C$ |       | 40               | 200   |       | 40               | 200   | μVrms |

| Long Term Stability (Note 2)   | TJ = 125°C, 1000 Hrs.                       |       | 3                | 10    |       | 3                | 10    | mV    |

**ELECTRICAL CHARACTERISTICS (cont.)** Unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  for the UC1525B and UC1527B;  $-40^{\circ}C$  to  $+85^{\circ}C$  for the UC2525B and UC2527B;  $0^{\circ}C$  to  $+70^{\circ}C$  for the UC3525B and UC3527B; +VIN = 20V,  $T_A = T_J$ .

|                                     |                                            | UC1525B/UC2525B<br>UC1527B/UC2527B |      |     | UC3525B<br>UC2527B |      |     |      |

|-------------------------------------|--------------------------------------------|------------------------------------|------|-----|--------------------|------|-----|------|

| PARAMETER                           | TEST CONDITIONS                            | MIN                                | TYP  | MAX | MIN                | TYP  | MAX | UNIT |

| Oscillator Section (Note 3)         |                                            | •                                  |      |     |                    |      |     | •    |

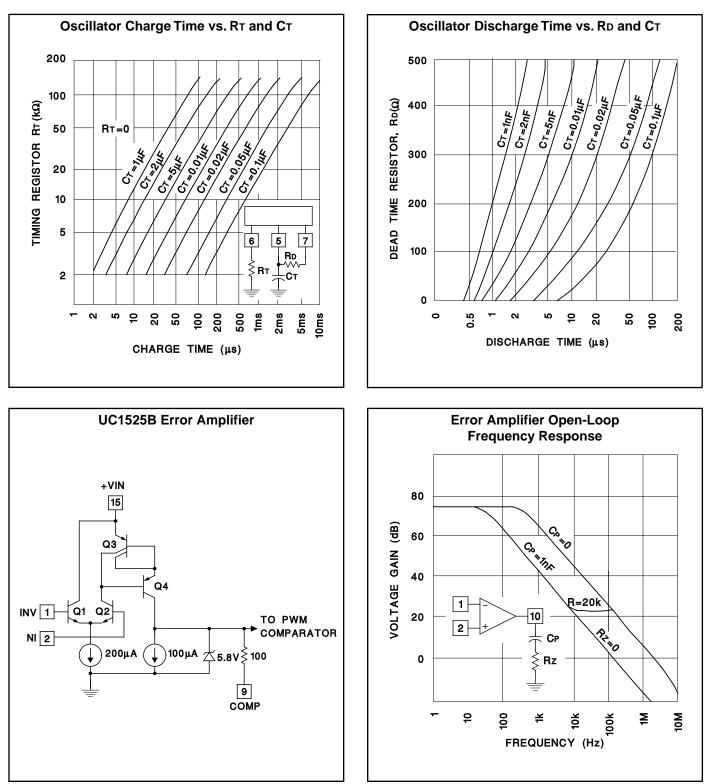

| Initial Accuracy (Notes 2 & 3)      | TJ = 25°C                                  |                                    | ±2   | ±6  |                    | ±2   | ±6  | %    |

| Voltage Stability (Notes 2 & 3)     | VIN = 8V to 35V                            |                                    | ±0.3 | ±1  |                    | ±1   | ±2  | %    |

| Temperature Stability (Note 2)      | Over Operating Range                       |                                    | ±3   | ±6  |                    | ±3   | ±6  | %    |

| Minimum Frequency                   | $RT = 200k\Omega$ , $CT = 0.1\mu F$        |                                    |      | 120 |                    |      | 120 | Hz   |

| Maximum Frequency                   | $RT = 2k\Omega$ , $CT = 470pF$             | 400                                |      |     | 400                |      |     | kHz  |

| Current Mirror                      | IRT = 2mA                                  | 1.7                                | 2.0  | 2.2 | 1.7                | 2.0  | 2.2 | mA   |

| Clock Amplitude (Notes 2 & 3)       |                                            | 3.0                                | 3.5  |     | 3.0                | 3.5  |     | V    |

| Clock Width (Notes 2 & 3)           | TJ = 25°C                                  | 0.3                                | 0.5  | 1.0 | 0.3                | 0.5  | 1.0 | μs   |

| Sync Threshold                      |                                            | 1.2                                | 2.0  | 2.8 | 1.2                | 2.0  | 2.8 | V    |

| Sync Input Current                  | Sync Voltage = 3.5V                        |                                    | 1.0  | 2.5 |                    | 1.0  | 2.5 | mA   |

| Error Amplifier Section (VCM = 5.1) | /)                                         | •                                  |      |     |                    |      |     |      |

| Input Offset Voltage                |                                            |                                    | 0.5  | 5   |                    | 2    | 10  | mV   |

| Input Bias Current                  |                                            |                                    | 1    | 10  |                    | 1    | 10  | μA   |

| Input Offset Current                |                                            |                                    |      | 1   |                    |      | 1   | μA   |

| DC Open Loop Gain                   | $RL \ge 10 Meg\Omega$                      | 60                                 | 75   |     | 60                 | 75   |     | dB   |

| Gain-Bandwidth Product (Note 2)     | $Av = 0dB, TJ = 25^{\circ}C$               | 1                                  | 2    |     | 1                  | 2    |     | MHz  |

| Output Low Level                    |                                            |                                    | 0.2  | 0.5 |                    | 0.2  | 0.5 | V    |

| Output High Level                   |                                            | 3.8                                | 5.6  |     | 3.8                | 5.6  |     | V    |

| Common Mode Rejection               | Vcm = 1.5V to 5.2V                         | 60                                 | 75   |     | 60                 | 75   |     | dB   |

| Supply Voltage Rejection            | VIN = 8V to 35V                            | 50                                 | 60   |     | 50                 | 60   |     | dB   |

| PWM Comparator                      | •                                          |                                    |      | •   | •                  | i.   |     | •    |

| Minimum Duty Cycle                  |                                            |                                    |      | 0   |                    |      | 0   | %    |

| Maximum Duty Cycle                  |                                            | 45                                 | 49   |     | 45                 | 49   |     | %    |

| Input Threshold (Note 3)            | Zero Duty Cycle                            | 0.7                                | 0.9  |     | 0.7                | 0.9  |     | V    |

| Input Threshold (Note3)             | Maximum Duty Cycle                         |                                    | 3.3  | 3.6 |                    | 3.3  | 3.6 | V    |

| Input Bias Current (Note 2)         |                                            |                                    | 0.05 | 1.0 |                    | 0.05 | 1.0 | μA   |

| Shutdown Section                    |                                            |                                    |      |     |                    |      |     |      |

| Soft Start Current                  | Vshutdown = 0V,<br>Vsoftstart = 0V         | 25                                 | 50   | 80  | 25                 | 50   | 80  | μA   |

| Soft Start Low Level                | VSHUTDOWN = 2.5V                           |                                    | 0.4  | 0.7 |                    | 0.4  | 0.7 | V    |

| Shutdown Threshold                  | To outputs, VSOFTSTART = 5.1V,<br>TJ =25°C | 0.6                                | 0.8  | 1.0 | 0.6                | 0.8  | 1.0 | V    |

| Shutdown Input Current              | VSHUTDOWN = 2.5V                           |                                    | 0.4  | 1.0 |                    | 0.4  | 1.0 | mA   |

| Shutdown Delay (Note 2)             | VSHUTDOWN = 2.5V, TJ = 25°C                |                                    | 0.2  | 0.5 |                    | 0.2  | 0.5 | μs   |

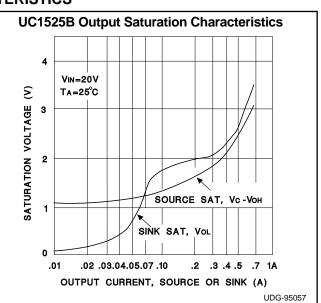

| Output Drivers (Each Output) (VC =  | 20V)                                       | •                                  |      |     | •                  |      |     | •    |

| Output Low Level                    | Isink = 20mA                               |                                    | 0.2  | 0.4 |                    | 0.2  | 0.4 | V    |

|                                     | Isinк = 100mA                              |                                    | 1.0  | 2.0 |                    | 1.0  | 2.0 | V    |

| Output High Level                   | ISOURCE = 20mA                             | 18                                 | 19   |     | 18                 | 19   |     | V    |

|                                     | ISOURCE = 100mA                            | 17                                 | 18   |     | 17                 | 18   |     | V    |

| Undervoltage Lockout                | VCOMP and VSOFTSTART = High                | 6                                  | 7    | 8   | 6                  | 7    | 8   | V    |

| Collector Leakage                   | VC = 35V                                   |                                    |      | 200 |                    |      | 200 | μA   |

**ELECTRICAL CHARACTERISTICS (cont.)** Unless otherwise stated, these specifications apply for  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  for the UC1525B and UC1527B;  $-40^{\circ}C$  to  $+85^{\circ}C$  for the UC2525B and UC2527B;  $0^{\circ}C$  to  $+70^{\circ}C$  for the UC3525B and UC3527B; +VIN = 20V,  $T_A = T_J$ .

|                                |                      | UC1525B/UC2525B<br>UC1527B/UC2527B |     | UC3525B<br>UC2527B |     |     |     |      |

|--------------------------------|----------------------|------------------------------------|-----|--------------------|-----|-----|-----|------|

| PARAMETER                      | TEST CONDITIONS      | MIN                                | TYP | MAX                | MIN | TYP | MAX | UNIT |

| Output Drivers (Each Output) ( | VC = 20V) (cont.)    |                                    |     |                    |     |     |     |      |

| Rise Time (Note 2)             | C∟ = 1nF, TJ = 25°C  |                                    | 100 | 600                |     | 100 | 600 | ns   |

| Fall Time (Note 2)             | C∟ = 1nF, TJ = 25°C  |                                    | 50  | 300                |     | 50  | 300 | ns   |

| Cross conduction charge        | Per cycle, TJ = 25°C |                                    | 30  |                    |     | 30  |     | nc   |

| Total Standby Current          |                      | •                                  |     |                    | •   |     |     |      |

| Supply Current                 | VIN = 35V            |                                    | 14  | 20                 |     | 14  | 20  | mA   |

Note 2: Guaranteed by design. Not 100% tested in production.

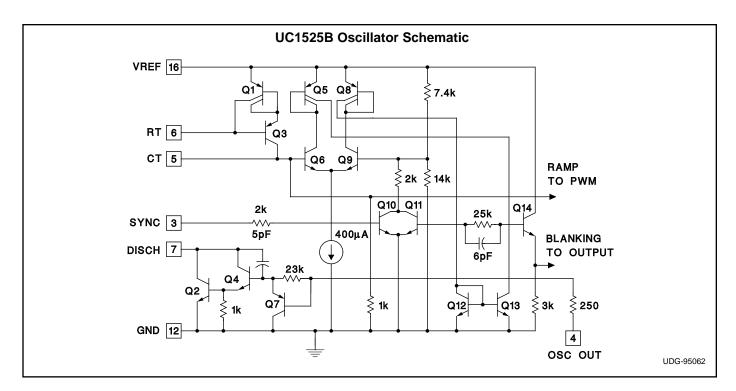

Note 3. Tested at fosc= 40kHz ( $R\tau = 3.6\Omega$ ,  $C\tau = 0.01\mu F$ ,  $RD = 0\Omega$ ). Approximate oscillator frequency is defined by:

$$f = \frac{1}{CT \bullet (0.7 \bullet RT + 3RD)}$$

#### PRINCIPLES OF OPERATION AND TYPICAL CHARACTERISTICS

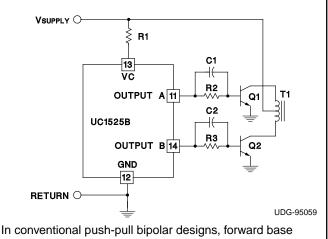

drive is controlled by R1-R3. Rapid turn-off times for the power devices are achieved with speed-up capacitors C, and C2.

# PRINCIPLES OF OPERATION AND TYPICAL CHARACTERISTICS

#### Shutdown Options (See Block Diagram)

Since both the compensation and soft-start terminals (Pins 9 and 8) have current source pull-ups, either can readily accept a pull-down signal which only has to sink a maximum of  $100\mu$ A to turn off the outputs. This is subject to the added requirement of discharging whatever external capacitance may be attached to these pins.

An alternate approach is the use of the shutdown circuitry of Pin 10 which has been improved to enhance the available shutdown options. Activating this circuit by

applying a positive signal on Pin 10 performs two functions: the PWM latch is immediately set providing the fastest turn-off signal to the external soft-start capacitor. If the shutdown command is short, the PWM signal is terminated without significant discharge of the soft-start capacitor, thus, allowing, for example, a convenient implementation of pulse-by-pulse current limiting. Holding Pin 10 high for a longer duration, however, will ultimately discharge this external capacitor, recycling slow turn-on upon release.

Pin 10 should not be left floating as noise pickup could conceivably interrupt normal operation.

#### LAB TEST FIXTURE

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

| TEXAS I | NSTRUMENTS   |          |                              |              |

|---------|--------------|----------|------------------------------|--------------|

| Search  | Tech Support | Comments | <ul> <li>Site Map</li> </ul> | • TI&ME      |

| PRO     | DUCTS        | DEVELOPI | VIENT TOOLS                  | APPLICATIONS |

|         |              |          |                              |              |

>> Semiconductor Home > Products > Analog & Mixed-Signal > Power Management > Switching Power Supply Controllers > Voltage Mode >

### UC1525B, REGULATING PULSE WIDTH MODULATORS

**Device Status: Active**

- > Description

- > Features

- > Datasheets

- > <a href="Pricing/Samples/Availability">Pricing/Samples/Availability</a>

- > <u>Application Notes</u>

- > Development Tools

- > Applications

| Parameter Name                | UC1525B                      |

|-------------------------------|------------------------------|

| Shutdown                      | Yes                          |

| Pulse - by - Pulse Isense     | No                           |

| Vsupply Operating Range (V)   | 8 - 35                       |

| Output Type                   | Dual Alternating, Totem Pole |

| Output Current (mA)           | 200                          |

| Frequency (max) (kHz)         | 500                          |

| Reference Voltage (V)         | 5.1                          |

| Vref tol (%)                  | 0.75                         |

| Duty Cycle (max) (%)          | 50/50                        |

| Undervoltage Lockout          | Yes                          |

| On-board Amplifiers           | 1                            |

| Output Mode Fixed Push - Pull | Yes                          |

| Output Mode Single - Ended    | No                           |

| Programmable Outputs          | No                           |

| Dead Time Control             | Yes                          |

### Description

| P |  |

|---|--|

The UC1525B/1527B series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip +5.1V buried zener reference is trimmed to  $\pm 0.75\%$  and the input common-mode range of the error amplifier includes the reference voltage, eliminating external resistors. A sync input to the oscillator allows multiple units to be slaved or a single unit to be synchronized to an external system clock. A single resistor between the CT and the discharge terminals provide a wide range of dead time adjustment. These devices also feature built-in soft-start circuitry with only an external timing capacitor required. A shutdown terminal controls both the soft-start circuitry and the output stages, providing instantaneous turn off through the PWM latch with pulsed shutdown, as well as soft-start recycle with longer shutdown commands. These functions are also controlled by an undervoltage lockout which keeps the outputs off and the soft-start capacitor discharged for subnormal input voltages. This lockout circuitry includes approximately 500mV of hysteresis for jitter-free operation. Another feature of these PWM circuits is a latch following the comparator. Once a PWM pulse has been terminated for any reason, the outputs will remain off for the duration of the period. The latch is reset with each clock pulse. The output stages are totem-pole designs capable of sourcing or sinking in excess of 200mA. The UC1525B output stage features NOR logic, giving a LOW output for an OFF state. The UC1527B utilizes OR logic which results in a HIGH output level when OFF.

### Features

- 8 to 35V Operation

- 5.1V Buried Zener Reference Trimmed to ±0.75%

- 100Hz to 500kHz Oscillator Range

- Separate Oscillator Sync Terminal

- Adjustable Deadtime Control

- Internal Soft-Start

- Pulse-by-Pulse Shutdown

- Input Undervoltage Lockout with Hysteresis

- Latching PWM to Prevent Multiple Pulses

- Dual Source/Sink Output Drivers

- Low Cross Conduction Output Stage

- Tighter Reference Specifications

To view the following documents, <u>Acrobat Reader 3.x</u> is required. To download a document to your hard drive, right-click on the link and choose 'Save'.

### Datasheets

Full datasheet in Acrobat PDF: slus376.pdf (530 KB)

### **Pricing/Samples/Availability**

| Orderable Device | Package    | Pins | <u>Temp</u><br>(°C) | <u>Status</u> | Price/unit<br>USD (100-999) | <u>Pack</u><br><u>Qty</u> | DSCC<br>Number | <u>Availability /</u><br><u>Samples</u> |

|------------------|------------|------|---------------------|---------------|-----------------------------|---------------------------|----------------|-----------------------------------------|

| UC1525BJ         | <u>UTR</u> | 16   | -55 TO<br>125       | ACTIVE        | 15.75                       | 1                         |                | Check stock or order                    |

| UC1525BJ883B     | <u>UTR</u> | 16   | -55 TO<br>125       | ACTIVE        | 20.36                       | 1                         |                | Check stock or order                    |

### **Application Reports**

- ANALOG APPLICATIONS JOURNAL, FEBRUARY 2000 (SLYT012A Updated: 03/23/2000)

- ANALOG APPLICATIONS JOURNAL, NOVEMBER 1999 (SLYT010A Updated: 03/23/2000)

- DN-36 UC1525B/UC1527B DEVICES COMPARISON SUMMARY TO UC1525A/27A DEVICES (SLUA170 -Updated: 11/04/1999)

- <u>ELECTROSTATIC DISCHARGE APPLICATION NOTE</u> (SSYA008 Updated: 05/05/1999)

- THERMAL CHARACTERISTICS OF LINEAR AND LOGIC PACKAGES USING JEDEC PCB DESIGNS (SZZA017A - Updated: 09/15/1999)

#### Table Data Updated on: 6/8/2000

| Search        | Tech Support      | Comments       | <ul> <li>Site Map</li> </ul> | ● TI&ME      | Home |

|---------------|-------------------|----------------|------------------------------|--------------|------|

| (c) Copyright | 2000 Texas Instri | uments Incorpo | orated. All right            | 's reserved. |      |

|               |                   |                |                              |              |      |

Trademarks, Important Notice!, Privacy Policy

| 🖗 Texas I | NSTRUMENTS   |          |                              |         |       |

|-----------|--------------|----------|------------------------------|---------|-------|

| Search    | Tech Support | Comments | <ul> <li>Site Map</li> </ul> | • TI&ME |       |

| PRO       | DUCTS        | DEVELOPM | ENT TOOLS                    | APPLICA | TIONS |

|           | 1            |          |                              |         |       |

>> Semiconductor Home > Products > Analog & Mixed-Signal > Power Management > Switching Power Supply Controllers > Voltage Mode >

### UC1526A, REGULATING PULSE WIDTH MODULATORS

**Device Status: Active**

- > Description

- > Features

- > Datasheets

- > <a href="Pricing/Samples/Availability">Pricing/Samples/Availability</a>

- > <u>Application Notes</u>

- > Development Tools

- > <u>Applications</u>

| Parameter Name                | UC1526A                      |  |  |  |

|-------------------------------|------------------------------|--|--|--|

| Shutdown                      | Yes                          |  |  |  |

| Pulse - by - Pulse Isense     | No                           |  |  |  |

| Vsupply Operating Range (V)   | 7 - 35                       |  |  |  |

| Output Type                   | Dual Alternating, Totem Pole |  |  |  |

| Output Current (mA)           | 200                          |  |  |  |

| Frequency (max) (kHz)         | 600                          |  |  |  |

| Reference Voltage (V)         | 5                            |  |  |  |

| Vref tol (%)                  | 1                            |  |  |  |

| Duty Cycle (max) (%)          | 50/50                        |  |  |  |

| Undervoltage Lockout          | Yes                          |  |  |  |

| On-board Amplifiers           | 1                            |  |  |  |

| Output Mode Fixed Push - Pull | Yes                          |  |  |  |

| Output Mode Single - Ended    | No                           |  |  |  |

| Programmable Outputs          | No                           |  |  |  |

| Current - Sense Amplifiers    | 1                            |  |  |  |

| Dead Time Control             | Yes                          |  |  |  |

### Description

```

P

```

The UC1526A Series are improved-performance pulse-width modulator circuits intended for direct replacement of equivalent non- "A" versions in all applications. Higher frequency operation has been enhanced by several significant improvements including: a more accurate oscillator with less minimum dead time, reduced circuit delays (particularly in current limiting), and an improved output stage with negligible cross-conduction current. Additional improvements include the incorporation of a precision, band-gap reference generator, reduced overall supply current, and the addition of thermal shutdown protection.

Along with these improvements, the UC1526A Series retains the protective features of under-voltage lockout, soft-start, digital current limiting, double pulse suppression logic, and adjustable deadtime. For ease of interfacing, all digital control ports are TTL compatible with active low logic.

Five volt (5V) operation is possible for "logic level" applications by connecting  $V_{IN}$ ,  $V_{C}$  and  $V_{REF}$  to a precision 5V input supply. Consult factory for additional information.

### Features

- Reduced Supply Current

- Oscillator Frequency to 600kHz

- Precision Band-Gap Reference

- 7 to 35V Operation

- Dual 200mA Source/Sink Outputs

- Minimum Output Cross-Conduction

- Double-Pulse Suppression Logic

- Under-Voltage Lockout

- Programmable Soft-Start

- Thermal Shutdown

- TTL/CMOS Compatible Logic Ports

- 5 Volt Operation ( $V_{IN} = V_C = V_{REF} = 5.0V$ )

To view the following documents, <u>Acrobat Reader 3.x</u> is required.

To download a document to your hard drive, right-click on the link and choose 'Save'.

### Datasheets

Full datasheet in Acrobat PDF: slus187.pdf (575 KB)

### Pricing/Samples/Availability

| Orderable Device | Package    | <u>Pins</u> | <u>Temp</u><br>(°C) | <u>Status</u> | Price/unit<br>USD (100-999) | Pack<br>Qty | DSCC Number    | <u>Availability /</u><br><u>Samples</u> |

|------------------|------------|-------------|---------------------|---------------|-----------------------------|-------------|----------------|-----------------------------------------|

| 85515022A        | L          | 20          | -55 TO<br>125       | ACTIVE        | 44.76                       | 1           |                | <u>Check stock or</u><br>order          |

| 8551502VA        | Ī          | 18          | -55 TO<br>125       | ACTIVE        | 19.06                       | 1           |                | <u>Check stock or</u><br>order          |

| UC1526AJ         | <u>UTR</u> | 18          | -55 TO<br>125       | ACTIVE        | 13.28                       | 1           |                | <u>Check stock or</u><br>order          |

| UC1526AJ883B     | <u>UTR</u> | 18          | -55 TO<br>125       | ACTIVE        | 19.06                       | 1           | 5962-8992002VA | <u>Check stock or</u><br>order          |

| UC1526AL         | <u>UTR</u> | 20          | -55 TO<br>125       | ACTIVE        | 29.29                       | 1           |                | <u>Check stock or</u><br>order          |

| UC1526AL883B     | UTR        | 20          | -55 TO<br>125       | ACTIVE        | 44.76                       | 1           | 5962-8670406XA | <u>Check stock or</u><br>order          |

### **Application Reports**

- ANALOG APPLICATIONS JOURNAL, FEBRUARY 2000 (SLYT012A Updated: 03/23/2000)

- ANALOG APPLICATIONS JOURNAL, NOVEMBER 1999 (SLYT010A Updated: 03/23/2000)

- ELECTROSTATIC DISCHARGE APPLICATION NOTE (SSYA008 Updated: 05/05/1999)

- THERMAL CHARACTERISTICS OF LINEAR AND LOGIC PACKAGES USING JEDEC PCB DESIGNS (SZZA017A - Updated: 09/15/1999)

#### Table Data Updated on: 6/11/2000

• Search • Tech Support • Comments • Site Map • TI&ME • Home (c) Copyright 2000 Texas Instruments Incorporated. All rights reserved. <u>Trademarks</u>, <u>Important Notice!</u>, <u>Privacy Policy</u>