## 67401 67401A 67402 67402A

Advanced Micro Devices

First-In First-Out (FIFO) 64x4 64x5 Standalone Memory

### DISTINCTIVE CHARACTERISTICS

- · Choice of 15 and 10 MHz shift-out/shift-in rates

- · Choice of 4-bit or 5-bit data width

- · TTL inputs and outputs

- · Readily expandable in word dimension only

- Structured pinouts. Output pins directly opposite corresponding input pins

- · Asynchronous operation

### ORDERING INFORMATION

| Part<br>Number | Package              | Temp | Description      |

|----------------|----------------------|------|------------------|

| 67401          | CD 016,PD 016,PL 020 | Com  | 10 MHz 64x4 FIFO |

| 67402          | CD 018,PD 018,PL 020 | Com  | 10 MHz 64x5 FIFO |

| 67401A         | CD 016,PD 016,PL 020 | Com  | 15 MHz 64x4 FIFO |

| 67402A         | CD 018,PD 018,PL 020 | Com  | 15MHz 64x5 FIFO  |

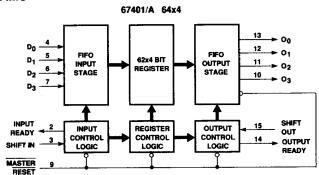

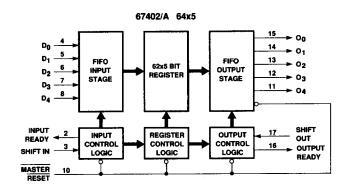

### **GENERAL DESCRIPTION**

The 67401/1A/2/2A are "fall-through" high-speed First-In First-Out (FIFO) memories organized 64 words by 4 bits and 64 words by 5 bits respectively. A 15 MHz data rate

allows usage in high speed tape or disc controllers and communication buffer applications. Word length is expandable; FIFO depth is not expandable.

### **BLOCK DIAGRAMS**

Publication # Rev. Amendment 10676 B /0 Issue Date: February 1989

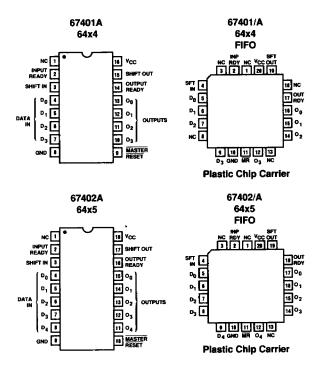

### **CONNECTION DIAGRAMS**

### LOGIC SYMBOL

### **PIN DESCRIPTION**

Data Input D<sub>0</sub> - D<sub>3/4</sub> O<sub>0</sub> - O<sub>3/4</sub> Data Output INP RDY Input Ready OUT RDY **Output Ready** SFT IN Shift In SFT OUT Shift Out MR Master Reset  $V_{CC}$ 5 V Power Supply GND Ground

### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage, V<sub>CC</sub>

-1.5 V to +7.0 V

Input voltage

-1.5 V to +7.0 V

Off-state output voltage

-0.5 V to +5.5 V

Storage temperature

-65°C to +150°C

### **OPERATING CONDITIONS**

| Symbol             |                                |        | 67401A/2A |     |      | 67401/2 |     |        |      |

|--------------------|--------------------------------|--------|-----------|-----|------|---------|-----|--------|------|

|                    | Parameter                      | Figure | Min       | Тур | Max  | Min     | Тур | Max    | Unit |

| v <sub>cc</sub>    | Supply Voltage                 |        | 4.75      | 5   | 5.25 | 4.75    | 5   | 5.25   | ٧    |

| T <sub>A</sub>     | Operating Free-Air Temperature |        | 0         |     | 75   | 0       |     | 75<br> | °C   |

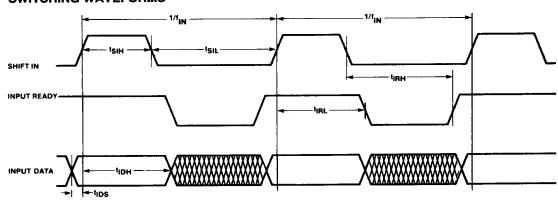

| t <sub>SIH</sub> † | Shift-In HIGH Time             | 1      | 23        |     | 28†  | 35      |     |        | ns   |

| t <sub>SIL</sub>   | Shift-In LOW Time              | 1      | 25        |     |      | 35      |     |        | ns   |

| t <sub>IDS</sub>   | Input Data Setup               | 1      | 5         |     |      | 5       |     |        | ns   |

| t <sub>IDH</sub>   | Input Data Hold Time           | 1      | 40        |     |      | 45      |     |        | ns   |

| t <sub>son</sub> † | Shift-Out HIGH Time            | 5      | 23        |     |      | 35      |     |        | ns   |

| t <sub>SOL</sub>   | Shift-Out LOW Time             | 5      | 25        |     |      | 35      |     |        | ns   |

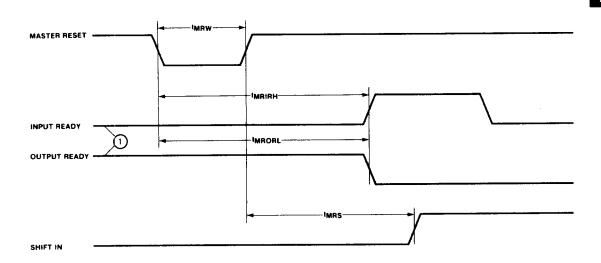

| t <sub>MRW</sub>   | Master Reset Pulse             | 10     | 35        |     |      | 35      |     |        | ns   |

| t <sub>MRS</sub>   | Master Reset to SI             | 10     | 35        |     |      | 35      |     |        | ns   |

### **SWITCHING CHARACTERISTICS** Over Operating Conditions

|                    |                                   |        | 67401A/2A |     |     | 67401/2 |     |     |      |

|--------------------|-----------------------------------|--------|-----------|-----|-----|---------|-----|-----|------|

| Symbol             | Parameter                         | Figure | Min       | Тур | Max | Min     | Тур | Max | Unit |

| f <sub>IN</sub>    | Shift-In Rate                     | 1      | 15        |     |     | 10      |     |     | MHz  |

| t <sub>IRL</sub> † | Shift In to Input Ready LOW       | 1      |           |     | 40  |         |     | 45  | ns   |

| t <sub>IRH</sub> † | Shift In to Input Ready HIGH      | 1      |           |     | 40  |         |     | 45  | ns   |

| f <sub>out</sub> † | Shift-Out Rate                    | 5      | 15        |     |     | 10      |     |     | MHz  |

| t <sub>ORL</sub> † | Shift Out to Output Ready LOW     | 5      |           |     | 45  |         |     | 55  | ns   |

| t <sub>ORH</sub> † | Shift Out to Output Ready HIGH    | 5      |           |     | 50  |         |     | 60  | ns   |

| t <sub>ODH</sub>   | Output Data Hold (previous word)  | 5      | 10        |     |     | 10      |     | _   | ns   |

| t <sub>ops</sub>   | Output Data Shift (next word)     | 5      |           |     | 45  |         |     | 55  | ns   |

| t <sub>PT</sub>    | Data Throughput or "Fall Through" | 4, 8   |           |     | 1.6 |         |     | 3   | μs   |

| t <sub>MRORL</sub> | Master Reset to OR LOW            | 10     |           |     | 60  |         |     | 60  | ns   |

| t <sub>MRIRH</sub> | Master Reset to IR HIGH           | 10     |           |     | 60  |         | ·   | 60  | ns   |

| t <sub>IPH</sub> * | Input Ready Pulse HIGH            | 4      | 23        |     |     | 23      |     |     | ns   |

| t <sub>OPH</sub> * | Output Ready Pulse HIGH           | 8      | 23        |     |     | 23      |     |     | ns   |

<sup>†</sup> See AC test and high speed application note.

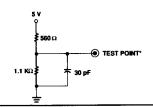

### **TEST LOAD**

\* The "TEST POINT" is driven by the output under test and observed by instrumentation.

Input Pulse 0 to 3 V

Input Rise and Fall Time (10% - 90%)

5 ns minimum

Measurements made at 1.5 V

### DC CHARACTERISTICS Over Operating Conditions

| Symbol            | Parameter                    | Test Cond                           | Min                               | Тур Мах                   | Unit |      |    |

|-------------------|------------------------------|-------------------------------------|-----------------------------------|---------------------------|------|------|----|

| V <sub>IL</sub>   | Low-level input voltage      |                                     |                                   |                           |      | 0.8† | V  |

| V <sub>IH</sub>   | High-level input voltage     |                                     |                                   |                           | 2†   |      | V  |

| V <sub>IC</sub>   | Input Clamp Voltage          |                                     | V <sub>CC</sub> = MIN             | I <sub>I</sub> = -18 mA   |      | -1.5 | V  |

| I <sub>IL</sub> 1 | Low-Level Input Current      | D <sub>0</sub> -D <sub>n</sub> , MR | V <sub>CC</sub> = MAX             | V <sub>I</sub> = 0.45 V   |      | -0.8 | mA |

| I <sub>IL</sub> 2 |                              | SI, SO                              |                                   |                           |      | -1.6 | mA |

| I <sub>IH</sub>   | High-Level Input Current     | 1                                   | V <sub>CC</sub> = MAX             | V <sub>I</sub> = 2.4 V    |      | 50   | μА |

|                   | Maximum Input Current        |                                     | V <sub>CC</sub> = MAX             | V <sub>i</sub> = 5.5 V    |      | 1    | mA |

| V <sub>OL</sub>   | Low-Level Output Voltage     |                                     | V <sub>CC</sub> = MIN             | I <sub>OL</sub> = 8 mA    |      | 0.5  | ٧  |

| V <sub>OH</sub>   | High-Level Output Voltage    |                                     | V <sub>CC</sub> = MIN             | I <sub>OH</sub> = -0.9 mA | 2.4  | -    | ٧  |

| los               | Output Short-Circuit Current |                                     | V <sub>CC</sub> = MAX             | V <sub>O</sub> = 0 V      | -20  | -90  | mA |

| l <sub>cc</sub>   | Supply Current               |                                     |                                   | 67401                     | -    | 160  |    |

|                   |                              |                                     | V <sub>CC</sub> = MAX             | 67402                     |      | 180  |    |

|                   |                              |                                     | All inputs low. All outputs open. | 67401A                    |      | 170  |    |

|                   |                              |                                     | 67402A                            |                           | 190  |      |    |

No more than one output should be shorted at a time, and duration of the short circuit should not exceed one second.

# FUNCTIONAL DESCRIPTION Data Input

After power up the Master Reset is pulsed low (Fig. 10) to prepare the FIFO to accept data in the first location. When Input Ready (IR) is HIGH, the location is ready to accept data from the  $D_{\rm x}$  inputs. Data then present at the data inputs is entered into the first location when the Shift In (SI) is brought HIGH. An SI HIGH signal causes the IR to go LOW. Data remains at the first location until SI is brought LOW. When SI is brought LOW and the FIFO is not full, IR will go HIGH, indicating that more room is available. Simultaneously, data will propagate to the second location and continue shifting until it reaches the output stage or a full location. The first word is present at the outputs before a shift out is applied. If the memory is full, IR will remain LOW.

### Data Transfer

Once data is entered into the second cell, the transfer of any full cell to the adjacent (downstream) empty cell is automatic, activated by an on-chip control. Thus data will stack up at the end of the device while empty locations will "bubble" to the front.  $t_{\rm p\,T}$  defines the time required for the first data to travel from input to the output of a previously empty device.

### **Data Output**

Data is read from the O, outputs. When data is shifted to the output stage, Output Ready (ÔR) goes HIGH, indicating the presence of valid data. When the OR is HIGH, data may be shifted out by bringing the Shift Out (SO) HIGH. A HIGH signal at SO causes the OR to go LOW. Valid data is maintained while the SO is HIGH. When SO is brought LOW the upstream data, provided that stage has valid data, is shifted to the output stage. When new valid data

is shifted to the output stage, OR goes HIGH. If the FIFO is emptied, OR stays LOW, and  $O_x$  remains as before (i.e., data does not change if FIFO is empty).

Input Ready and Output Ready may also be used as status signals indicating that the FIFO is completely full (Input Ready stays LOW for at least  $t_{\rm pT}$ ) or completely empty (Output Ready stays LOW for at least  $t_{\rm pT}$ ).

### AC TEST AND HIGH SPEED APP. NOTES

Since the FIFO is a very-high-speed device, care must be exercised in the design of the hardware and the timing utilized withing the design. The internal shift rate of the FIFO typically exceeds 20 MHz in operation. Device grounding and decoupling is crucial to correct operation as the FIFO will respond to very small glitches due to long reflective lines, high capacitance and/or poor supply decoupling and grounding. We recommend a monolithic ceramic capacitor of 0.1  $\mu\text{F}$  directly between  $V_{cc}$  and GND with very short lead length. In addition, care must be exercised in how the timing is set up and how the parameters are measured. For example, since an AND gate function is associated with both the Shift In-Input Ready combination, as well as the Shift Out-Output Ready combination, timing measurements may be misleading; i.e., rising edge of the Shift-In pulse is not recognized until Input-Ready is High. If Input-Ready is not high due to too high a frequency or FIFO being full or affected by Master Reset, the Shift-In activity will be ignored. This will affect the device from a functional standpoint, and will also cause the "effective" timing of Input Data Time (tidh) and the next activity of Input Ready (t,RL) to be extended relative to Shift-In going High. This same type of problem is also related to t<sub>IBH</sub>, t<sub>OBL</sub> and t<sub>OBH</sub> as related to Shift-Out.

<sup>†</sup> These are absolute voltages with respect to GND (PIN 8 or 9) and includes all overshoots due to system or tester noise.

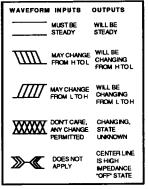

### KEY TO SWITCHING WAVEFORMS

08125-040A

Figure 1. Input Timing

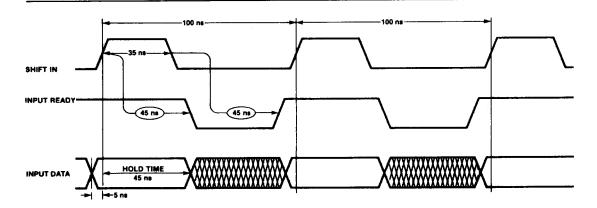

Figure 2. Typical Waveforms for 10-MHz Shift In Data Rate (67401/2)

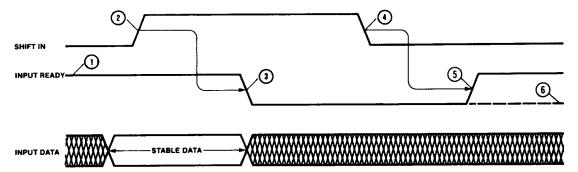

- ① Input Ready HIGH indicates space is available and a Shift-In pulse may be applied.

- ② Input Data is loaded into the first word.

- ③ Input Ready goes LOW indicating the first word is full.

- The Data from the first word is released for "fall-through" to second word.

- ⑤ The Data from the first word is transferred to second word. The first word is now empty as indicated by Input Ready HIGH.

- If the second word is already full, then the data remains at the first word. Since the FIFO is now full, Input Ready remains low. NOTE: Shift-In pulses applied while Input Ready is LOW will be ignored (See Figure 3).

SHIFT OUT

SHIFT IN

INPUT DATA

STABLE DATA

Figure 3. The Mechanism of Shifting Data Into the FIFO

- ① FIFO is initially full.

- ② Shift Out pulse is applied. An empty location sarts "bubbling" to the front.

- 3 Shift In is held HIGH.

- As soon as Input Ready becomes HIGH the Input Data is loaded into the first word.

- ⑤ The Data from the first word is released for "fall through" to second word.

Figure 4. Data is Shifted in Whenever Shift in and Input Ready Are Both HIGH

- ① The diagram assumes that at this time, words 63, 62, and 61 are loaded with A, B, and C Data, respectively.

- ② Data is shifted out when Shift Out makes a HIGH-to-LOW transition.

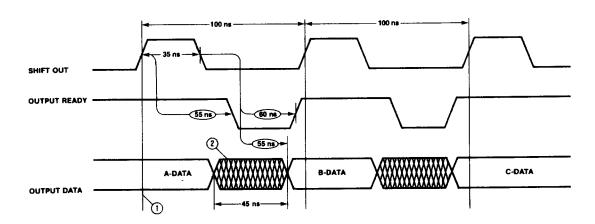

Figure 5. Ouput Timing

- ① The diagram assumes that at this time words 63, 62, and 61 are loaded with A, B, and C Data respectively.

- 2 Data in the crosshatched region may be A or B Data.

Figure 6. Typical Waveforms for 10-MHz Shift Out Data Rate (67401/2)

- ① Output Ready HIGH indicates that data is available and a Shift-Out pulse may be applied.

- ② Shift-Out goes HIGH causing the next step.

- 3 Output Ready goes LOW.

- ④ Contents of word 62 (B-DATA) to be released for "fall-through" to word 63.

- ⑤ Output Ready goes HIGH indicating that new data (B) is now available at the FIFO outputs.

- If the FIFO has only one word loaded (A-DATA) then Output Ready stays LOW and the A-DATA remains unchanged at the outputs. NOTE: Shift Out pulses applied when Output Ready is LOW will be ignored.

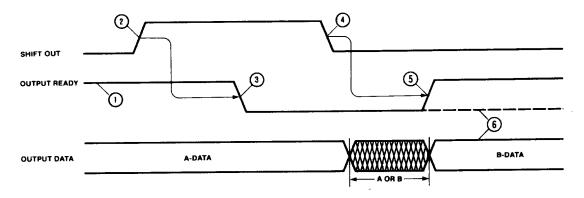

Figure 7. The Mechanism of Shifting Data Out of the FIFO

- ① FIFO is initially empty.

- ② Shift Out held HIGH.

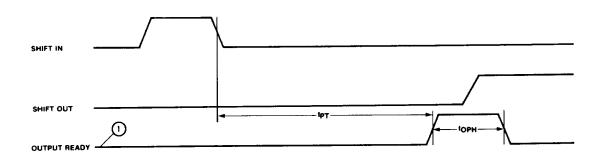

Figure 8.  $t_{PT}$  and  $t_{OPH}$  Specification

- ① Word 63 is empty.

- ② New data (A) arrives at the outputs (word 63).

- 3 Output Ready goes HIGH indicating arrival of the new data.

- Since Shift Out is held HIGH, Output Ready goes immediately LOW.

- S As soon as Shift Out goes LOW the Output Data is subject to change as shown by the dashed line on Output Ready.

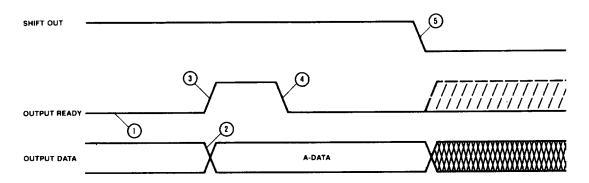

Figure 9. Data Is Shifted Out Whenever Shift Out and Output ready Are Both HIGH

① FIFO is initially full.

Figure 10. Master Reset Timing