The Future of Analog IC Technology

## DESCRIPTION

The MP5086 is a load switch, designed to provide 7A load protection covering 2.3V to 5.5V voltage range. With low  $R_{DSON}$  in tiny package, the MP5086 provides very high efficiency and space-saving solution for smart phone, tablet and other portable applications.

The MP5086 is equipped with the very accurate current monitoring function. The gain of the current monitor can be scaled for different applications. MP5086 has a NTC (Negative Temperature Coefficient Thermistor) interface. It can be used to set over temperature threshold. The MP5086 also provides other features, like fast short-circuit response time, and thermal shutdown features.

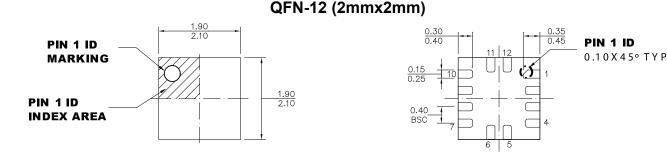

This device comes in a tiny 2mmx2mm QFN12 package.

## FEATURES

- Output Current Monitoring Accurate High to 3%

- V<sub>IN</sub> Range: 2.3V to 5.5V

- Integrated 11mΩ Low R<sub>DSON</sub> FETs

- Typical 7A Load Current

- <1µA Supply Current at Bypass Mode</li>

- Integrated NTC Interface

- Open-Drain OTP Indicator

- <200ns Short-Circuitry Response Protection</p>

- Thermal Protection

- Transportation Mode Available

- Small 2mmx2mm QFN Package

### APPLICATIONS

- Storage Drives

- Portable/Handheld Devices

- Wireless/Networking Cards

- Low Voltage I/O System Power

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

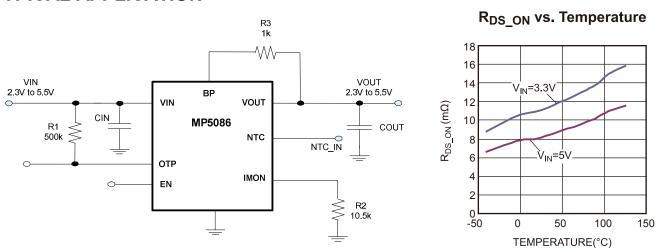

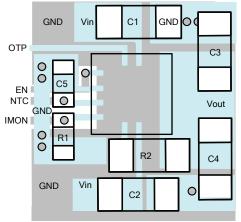

# TYPICAL APPLICATION

### **ORDERING INFORMATION**

| Part Number* | Package          | Top Marking |  |

|--------------|------------------|-------------|--|

| MP5086GG     | QFN-12 (2mmx2mm) | See Below   |  |

\*For Tape & Reel, add suffix-Z (e.g. MP5086GG-Z);

## **TOP MARKING**

CXY LLL

CX: product code of MP5086GG; Y: year code; LLL: lot number;

## PACKAGE REFERENCE

| OTP VIN                                                                    |  |  |

|----------------------------------------------------------------------------|--|--|

| EN 1 12 11 10 VOUT<br>GND 2 9 VOUT<br>NTC 3 6 VOUT<br>IMON 4 6 6<br>BP VIN |  |  |

| QFN-12 (2mmx2mm)                                                           |  |  |

### ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage V <sub>IN</sub> |                                           |

|--------------------------------|-------------------------------------------|

| V <sub>OUT</sub><br>OTP        |                                           |

| EN , IMON, NTC                 |                                           |

| All Other Pins                 |                                           |

| Junction Temperature           | 150°C                                     |

| Lead Temperature               | 260°C                                     |

| Continuous Power Dissipation   | n (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                | 1.6W                                      |

| Storage Temperature            | 65°C to +150°C                            |

|                                | ( <b>-</b> )                              |

### Recommended Operating Conditions <sup>(3)</sup>

Supply Voltage V<sub>IN</sub>..... 2.3V to 5.5V Operating Junction Temp. (T<sub>J</sub>). -40°C to +125°C

# Thermal Resistance $^{(4)}$ $\theta_{JA}$ $\theta_{JC}$

QFN-12 (2mmx2mm)...... 80

0 16 °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 3.6V, EN enable,  $T_A$ = 25°C, unless otherwise noted.

| Parameters                                      | Symbol                        | Condition                                                                                             | Min   | Тур   | Max   | Units             |

|-------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| Input and Supply Voltage Range                  |                               |                                                                                                       |       |       | •     |                   |

| Input Voltage                                   | V <sub>IN</sub>               |                                                                                                       | 2.3   |       | 5.5   | V                 |

| Supply Current                                  |                               | •                                                                                                     |       |       |       |                   |

| Normal Current                                  | I <sub>ON</sub>               | V <sub>IN</sub> =5V, Enable, NTC<br>high, No load                                                     |       | 240   | 310   | μA                |

| Bypass Current                                  | I <sub>BP</sub>               | V <sub>IN</sub> =5V, EN=0, NTC high,<br>No load, BP float                                             |       | 0.1   | 1     | μA                |

| Transportation Current                          | I <sub>TRAN</sub>             | Transportation Mode                                                                                   |       | 0.1   | 1     | μA                |

| Power FET                                       |                               |                                                                                                       |       |       |       |                   |

|                                                 |                               | V <sub>IN</sub> =5.0V                                                                                 |       | 8     |       |                   |

| Main NFET ON Resistance                         | R <sub>DSON</sub>             | V <sub>IN</sub> =3.3V                                                                                 |       | 11    |       | mΩ                |

|                                                 |                               | V <sub>IN</sub> =2.4V                                                                                 |       | 17    |       |                   |

| Bypass PFET ON Resistance                       | $R_{BP}$                      | I <sub>OUT</sub> =10mA                                                                                |       | 65    |       | Ω                 |

| Thermal Shutdown <sup>(5)</sup>                 |                               |                                                                                                       |       |       |       |                   |

| Shutdown Temperature                            | T <sub>STD</sub>              |                                                                                                       |       | 155   |       | °C                |

| Under Voltage Protection                        |                               |                                                                                                       |       |       |       |                   |

| V <sub>IN</sub> Under Voltage Lockout Threshold | $V_{\text{IN}_{\text{UVLO}}}$ | UVLO Rising Threshold                                                                                 |       | 2.0   | 2.2   | V                 |

| UVLO Hysteresis                                 | V <sub>UVLO HYS</sub>         |                                                                                                       |       | 200   |       | mV                |

| Enable                                          |                               |                                                                                                       |       |       |       |                   |

| EN High Level                                   | $V_{ENH}$                     |                                                                                                       | 1.2   |       |       | V                 |

| EN Low Level                                    | $V_{ENL}$                     |                                                                                                       |       |       | 0.4   | V                 |

| EN High to Low Response Time                    |                               | From EN off to Main FET off                                                                           |       | 5     |       | μs                |

| Soft Start                                      |                               |                                                                                                       |       |       |       |                   |

| Soft -Start                                     |                               | C <sub>OUT</sub> =44μF, C <sub>IN</sub> =44μF,<br>10% V <sub>OUT</sub> to 90% V <sub>OUT</sub>        |       | 200   |       | μs                |

| IMON                                            |                               |                                                                                                       |       |       |       |                   |

| Current Limit                                   | I <sub>OUT</sub>              | R <sub>IMON</sub> =50kΩ, ramp lout record peak current limit                                          | 1.54  | 1.64  | 1.74  | А                 |

|                                                 |                               | I <sub>OUT</sub> =3.75A                                                                               | 44.35 | 45.73 | 47.11 |                   |

| Current Monitor Accuracy                        |                               | I <sub>OUT</sub> =3A                                                                                  | 35.49 | 36.59 | 37.69 | μA                |

| ·····,                                          |                               | I <sub>OUT</sub> =1.5A <sup>(6)</sup>                                                                 | 17.39 | 18.3  | 19.22 | I.                |

| NTC Block                                       |                               |                                                                                                       | 11.00 | 10.0  | 10.22 |                   |

| NTC Comparator Falling Threshold                | Vues                          |                                                                                                       | 17.5  | 20    | 22.5  | %V <sub>OUT</sub> |

| NTC comparator railing rifeshold                | V <sub>NTC F</sub>            | With 4 7nE can between                                                                                | 17.5  | 20    | 22.5  | 10 001            |

| OTP Delay                                       | T <sub>NTC_D</sub>            | With 4.7nF cap between<br>OTP and GND , from 50%<br>NTC to 50% OTP                                    |       | 200   |       | μs                |

| OTP Refresh Voltage                             |                               |                                                                                                       | 0.6   | 0.84  |       | V                 |

| OTP High Level                                  | V <sub>OTP_H</sub>            | V <sub>IN</sub> =3.3V, pull up to V <sub>IN</sub><br>through external 50k, Over<br>Temperature happen | 3.1   |       |       | V                 |

| OTP Low Level                                   | V <sub>OTP L</sub>            | Sink 1mA                                                                                              |       |       | 0.2   | V                 |

| OTP Self-biased Voltage <sup>(5)</sup>          | VIP L                         | V <sub>IN</sub> float, EN=0, external<br>pull up to 5V through 50k<br>resistor                        |       | 0.8   | 0.2   | V                 |

| Notes:                                          |                               |                                                                                                       |       |       |       |                   |

Notes:

5) Guarantee by Characterization. Not production test.

6) If sense current is smaller than 1.5A, the IMON accuracy will be affected by some internal offset.

## **PIN FUNCTIONS**

| Pin #          | Name | Description                                                                                                                                                           |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | EN   | Enable Input. EN high logic cause IC works in normal mode. EN low logic cause IC works in bypass mode.                                                                |

| 2              | GND  | Ground.                                                                                                                                                               |

| 3              | NTC  | Thermistor Input. Connect a resistor from this pin to $V_{\text{OUT}}$ and a thermistor from this pin to ground.                                                      |

| 4              | IMON | Output Current Monitor. Provides a voltage proportional to the current flowing through the power device. Place a resistor to ground to set the gain.                  |

| 5              | BP   | Bypass FET Output. When EN is low, the main FET is off and bypass FET is on.                                                                                          |

| 6, 11          | VIN  | Input Power Supply Voltage to the Control Circuitry.                                                                                                                  |

| 7, 8, 9,<br>10 | VOUT | Output to the Load.                                                                                                                                                   |

| 12             | OTP  | Over Temperature Indicator. When NTC comparator senses the over temperature condition happened or thermal shutdown is triggered, the OTP voltage will be pulled high. |

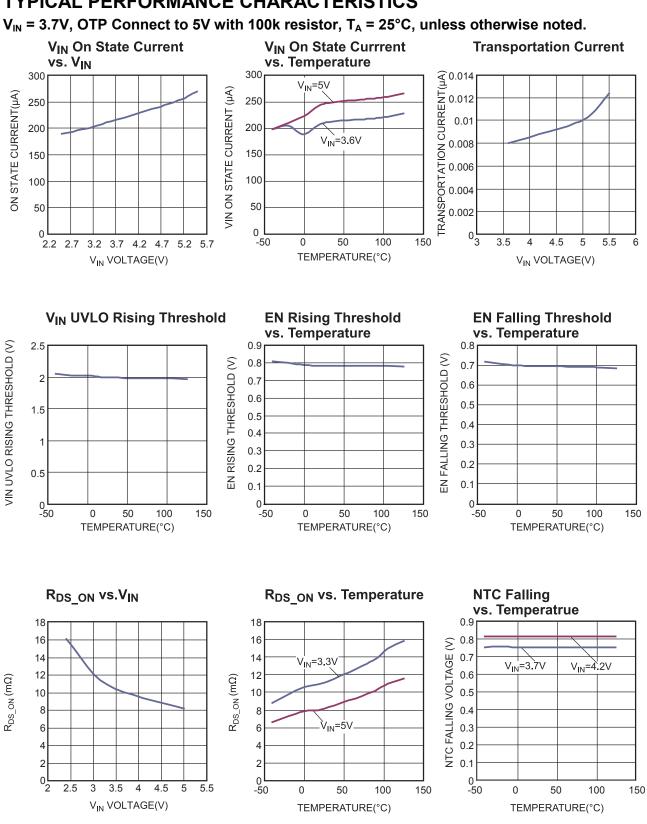

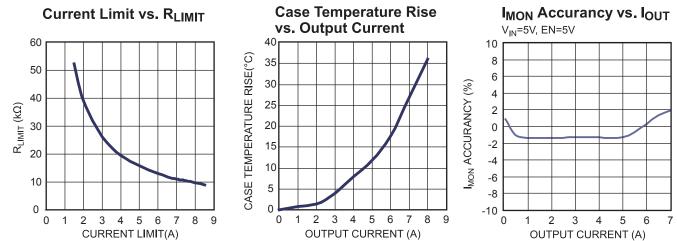

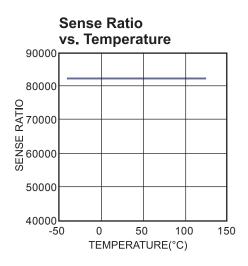

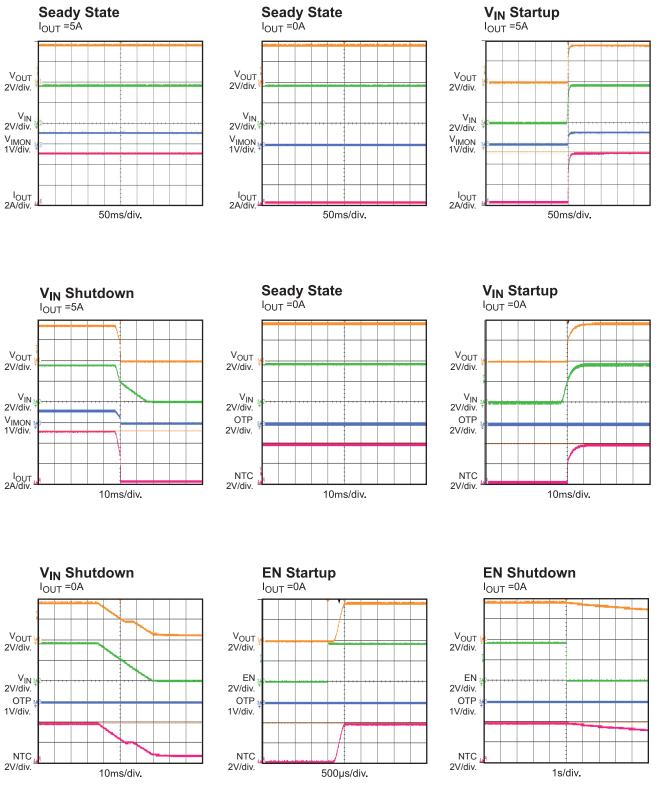

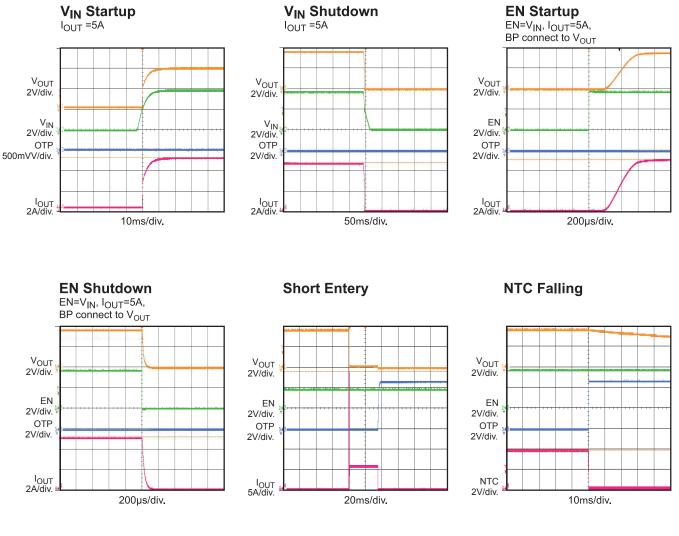

## TYPICAL PERFORMANCE CHARACTERISTICS

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 3.7V, OTP Connect to 5V with 100k resistor,  $T_A$  = 25°C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 3.7V, OTP Connect to 5V with 100k resistor,  $T_A$  = 25°C, BP pin floated, NTC Connect to Vout, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 3.7V, OTP Connect to 5V with 100k resistor,  $T_A$  = 25°C, BP pin floated, NTC Connect to Vout, unless otherwise noted.

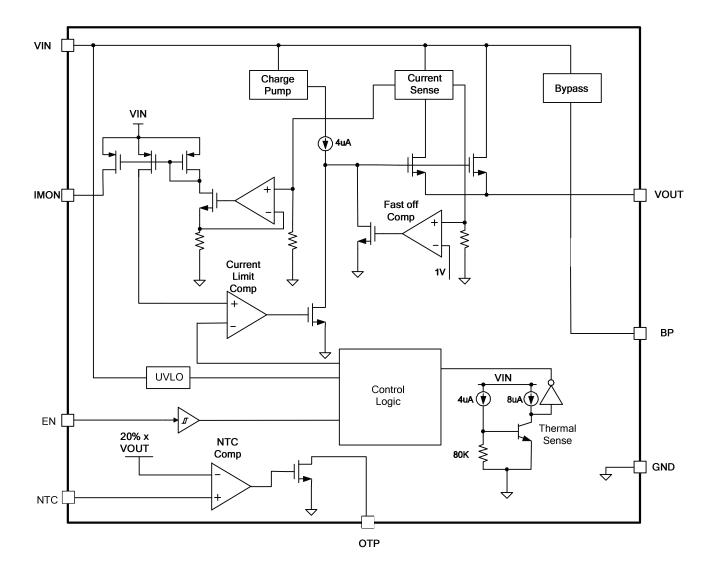

Figure 1: Functional Block Diagram

### **OPERATION**

The MP5086 is designed to limit the in-rush current to the load, thereby limiting the backplane's voltage drop and the slew rate of the voltage to the load. It provides an integrated solution to monitor the output current to eliminate the need for an external current power MOSFET, and current switch device. It also integrated fast short circuit protection, thermal shutdown feature and NTC logic to set over temperature threshold.

#### **Operation Mode**

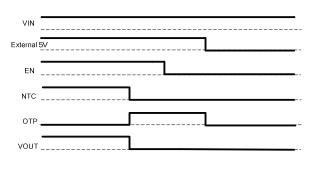

There are four operation modes in MP5086: normal mode, bypass mode, NTC protection mode and transportation mode.

When EN is high and IC not trigger any protection, IC works in normal mode. Under this status, the main MOS, bypass MOS are always on. Normal mode is main operation mode. The quiescent current is about 240µA.

The bypass mode is that EN goes low and IC not triggers any protection, it will turn off the main MOS and disable most blocks to saving energy. The bypass MOS is still on and it can take <10mA load. The quiescent current of this mode is <1 $\mu$ A. And if connect the BP to V<sub>OUT</sub>, there will be a few  $\mu$ A leakage current caused by the internal 800k $\Omega$  output sense resistor. It is recommended adding 100 $\Omega$  to 1k $\Omega$  resistor between BP and V<sub>OUT</sub> pin to limit the current externally.

The NTC protection mode means that the IC detect the NTC signal goes low or trigger over temperature protection, typically 155°C. It shutdown the main MOS and the bypass MOS forcedly, disable OTP pull-down MOSFET and latch this state. Only  $V_{IN}$  or EN restart can refresh OTP pin flag and quit this mode.

The transportation Mode means the part shutdown all blocks and reduces the quiescent current to lower than 1 $\mu$ A. When the part is in NTC protection mode, make sure EN is lower than 0.4V and OTP pin is lower than its refresh voltage, typically 0.84V, the part will enter transportation mode. Transportation mode will block any leakage from V<sub>IN</sub> to V<sub>OUT</sub> to lengthen the battery life.

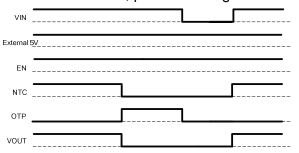

#### **Basic Logic**

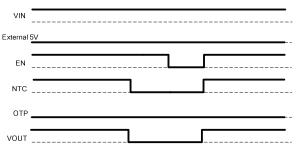

For MP5086, you can find the basic logic in below figures. OTP is connect to external 5V with a 100k resistor, please refer figure 5.

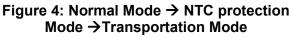

Figure 2: Normal Mode with external 5V  $\rightarrow$  NTC protection Mode  $\rightarrow$  V<sub>IN</sub> Restart

Figure 3: Normal Mode without external 5V → NTC protection Mode → EN Restart

### Enable

The enable input will decide the MP5086 operation mode. When input voltage is greater than the under-voltage lockout threshold (UVLO), typically 2.0V and pull EN pin to higher than 1.2V, MP5086 works in normal mode. Under this condition, the ultra-low  $R_{DSON}$  main power FET is on. The all features include current monitor and NTC protection are active. Pulling EN down to ground will make MP5086 work in bypass mode.

### **NTC Protection**

MP5086 integrated a NTC comparator to monitor the system temperature. When NTC pin voltage is lower than 20% of  $V_{OUT}$  voltage, the open-drain OTP indicator will be pulled high. At the same time, the OTP pin flag also turn off main power FET and bypass FET. After that, MP5086 will enter NTC protection mode and the OTP pin state is latched.

### **Current Limit**

The MP5086 provides a constant current limit that can be programmed by an external resistor. Once the device reaches its current limit threshold, the internal circuit regulates the gate voltage to hold the current in the power FET constant. The typical response time is about 20µs and the output current may have a small overshoot during this time period.

The pre-set current limit value can be calculated by below equation:

$$I_{\text{Limit}} = (1 \div R_{\text{limit}}) \times S \qquad (1)$$

S is the current sense ratio of MP5086, and this value is typically 82000 in  $V_{IN}$ =3.6V. The other values of S please refer the curves in typical performance characteristics.

If the current limit block starts to regulate the output current, the power loss on power MOSFET will cause the IC temperature rise. If the junction temperature raises to high enough, it will trigger thermal shutdown, and part will latched. The over temperature threshold is 155°C. The internal thermal protection equals to NTC protection.

#### **Short-Circuit Protection**

If the load current increases rapidly due to a short circuit, the current may exceed the current limit threshold by a lot before the control loop can respond. If the current reaches an internal secondary current limit level (typical 13A), a fast turn-off circuit activates to turn off the power FET. This limits the peak current through the switch to limit the input voltage drop. The total short circuit response time is about 200ns. If fast off works, it will keep off the power FET for typical 80µs. After that time period, it will re-turn on power FET. If the part is still in short-circuit condition. MP5086 will reduce the current limit to 2/3 of pre-set value, and hold it until the part is hot enough and thermal shutdown. When the thermal shutdown is trigged, the part will enter NTC protection mode.

## **APPLICATION INFORMATION**

#### **IMON Resistor Selection**

The current limit value can be set by IMON resistor. The current limit can be gotten by equation (1).

The current limit threshold is suggested to  $10\% \sim 15\%$  higher than maximum load current. For example, if the system's full load is 7A, set the current limit to 7.7A.

#### **Design Example**

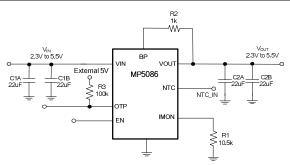

Some design example and are provided below. See Table 1 and Figure 5.

Table 1

| V <sub>IN</sub><br>(V) | Max Load Range<br>(A) | Rlimit<br>(kΩ) |

|------------------------|-----------------------|----------------|

| 5                      | 3                     | 26.1           |

| 5                      | 5                     | 15.8           |

| 5                      | 7.5                   | 10.5           |

### Figure 5: Typical Application Schematic

### Layout Guide

PCB layout is very important to achieve stable operation. Please follow these guidelines and take below figure for reference. Place  $R_{IMON}$  close to IMON pin, input cap close to  $V_{IN}$  pin. Put enough vias around IC to achieve better thermal performance.

Figure 6: Recommended Layout

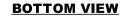

### **PACKAGE INFORMATION**

#### TOP VIEW

**SIDE VIEW**

#### **RECOMMENDED LAND PATTERN**

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS

EXPOSED PADDLE SIZE DOES NOT

INCLUDE MOLD FLASH

LEAD COPLANARITY SHALL BED.10

MILLIMETERS MAX.

JEDEC REFERENCE IS MG220.

DRAWING IS NOT TO SCALE

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.