100-Pin TQFP Commercial Temp Industrial Temp

# 36Mb Pipelined and Flow Through Synchronous NBT SRAMs

333 MHz—150 MHz 1.8 V or 2.5 V V<sub>DD</sub> 1.8 V or 2.5 V I/O

#### **Features**

- NBT (No Bus Turn Around) functionality allows zero wait read-write-read bus utilization; Fully pin-compatible with both pipelined and flow through NtRAM<sup>TM</sup>, NoBL<sup>TM</sup> and ZBT<sup>TM</sup> SRAMs

- 1.8 V or 2.5 V core power supply

- 1.8 V or 2.5 V I/O supply

- User-configurable Pipeline and Flow Through mode

- LBO pin for Linear or Interleave Burst mode

- Pin compatible with 2Mb, 4Mb, 8Mb, and 16Mb devices

- Byte write operation (9-bit Bytes)

- 3 chip enable signals for easy depth expansion

- ZZ Pin for automatic power-down

- RoHS-compliant 100-lead TQFP package available

## **Functional Description**

The GS8320Z18/36AGT-xxxV is a 36Mbit Synchronous Static SRAM. GSI's NBT SRAMs, like ZBT, NtRAM, NoBL or other pipelined read/double late write or flow through read/single late write SRAMs, allow utilization of all available bus bandwidth by eliminating the need to insert deselect cycles when the device is switched from read to write cycles.

Because it is a synchronous device, address, data inputs, and read/ write control inputs are captured on the rising edge of the input clock. Burst order control ( $\overline{LBO}$ ) must be tied to a power rail for proper operation. Asynchronous inputs include the Sleep mode enable (ZZ) and Output Enable. Output Enable can be used to override the synchronous control of the output drivers and turn the RAM's output drivers off at any time. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates complex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing.

The GS8320Z18/36AGT-xxxV may be configured by the user to operate in Pipeline or Flow Through mode. Operating as a pipelined synchronous device, meaning that in addition to the rising edge triggered registers that capture input signals, the device incorporates a rising-edge-triggered output register. For read cycles, pipelined SRAM output data is temporarily stored by the edge triggered output register during the access cycle and then released to the output drivers at the next rising edge of clock

The GS8320Z18/36AGT-xxxV is implemented with GSI's high performance CMOS technology and is available in a JEDEC-standard 100-pin TQFP package.

## **Parameter Synopsis**

|           |                 | -333 | -250 | -200 | -150 | Unit |

|-----------|-----------------|------|------|------|------|------|

|           | t <sub>KQ</sub> | 3.0  | 3.0  | 3.0  | 3.8  | ns   |

| Pipeline  | tCycle          | 3.0  | 4.0  | 5.0  | 6.7  | ns   |

| 3-1-1-1   | Curr (x18)      | 365  | 290  | 250  | 215  | mA   |

|           | Curr (x36)      | 425  | 345  | 290  | 240  | mA   |

| Flow      | t <sub>KQ</sub> | 5.0  | 5.5  | 6.5  | 7.5  | ns   |

| Through - | tCycle          | 5.0  | 5.5  | 6.5  | 7.5  | ns   |

| 2-1-1-1   | Curr (x18)      | 270  | 245  | 210  | 200  | mΑ   |

|           | Curr (x36)      | 315  | 280  | 250  | 230  | mA   |

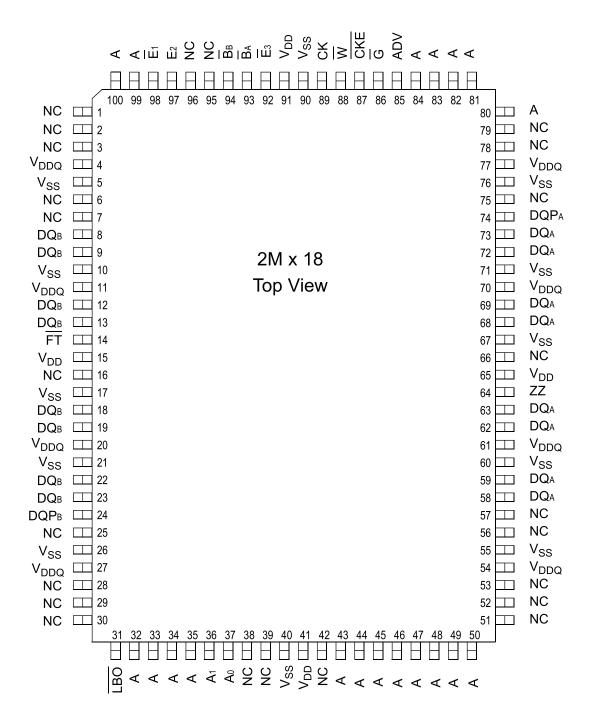

## **GS8320Z18AGT-xxxV Pinout**

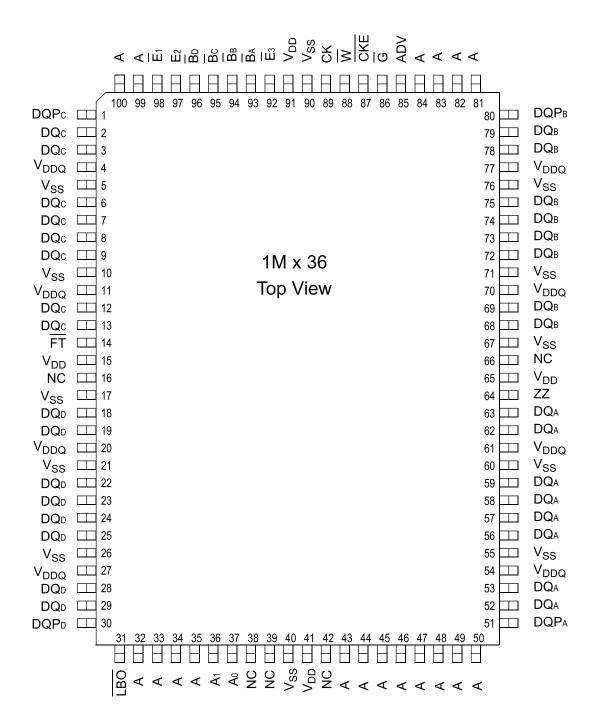

## GS8320Z36AGT-xxxV Pinout

# 100-Pin TQFP Pin Descriptions

| Symbol          | Type | Description                                                                       |

|-----------------|------|-----------------------------------------------------------------------------------|

| A0, A1          | In   | Burst Address Inputs; Preload the burst counter                                   |

| А               | In   | Address Inputs                                                                    |

| CK              | In   | Clock Input Signal                                                                |

| BA              | In   | Byte Write signal for data inputs DQA1-DQA9; active low                           |

| <u>—</u><br>Вв  | In   | Byte Write signal for data inputs DQ <sub>B1</sub> -DQ <sub>B9</sub> ; active low |

| B <sub>C</sub>  | In   | Byte Write signal for data inputs DQc1-DQc9; active low                           |

| <del>D</del> D  | In   | Byte Write signal for data inputs DQp1-DQp9; active low                           |

| $\overline{W}$  | In   | Write Enable; active low                                                          |

| <u></u>         | In   | Chip Enable; active low                                                           |

| E <sub>2</sub>  | In   | Chip Enable; Active High. For self decoded depth expansion                        |

| E <sub>3</sub>  | In   | Chip Enable; Active Low. For self decoded depth expansion                         |

| G               | In   | Output Enable; active low                                                         |

| ADV             | In   | Advance/Load; Burst address counter control pin                                   |

| CKE             | In   | Clock Input Buffer Enable; active low                                             |

| DQA             | I/O  | Byte A Data Input and Output pins                                                 |

| DQв             | I/O  | Byte B Data Input and Output pins                                                 |

| DQc             | I/O  | Byte C Data Input and Output pins                                                 |

| DQD             | I/O  | Byte D Data Input and Output pins                                                 |

| ZZ              | In   | Power down control; active high                                                   |

| FT              | In   | Pipeline/Flow Through Mode Control; active low                                    |

| LBO             | In   | Linear Burst Order; active low                                                    |

| $V_{DD}$        | In   | Core power supply                                                                 |

| V <sub>SS</sub> | In   | Ground                                                                            |

| $V_{DDQ}$       | In   | Output driver power supply                                                        |

| NC              | _    | No Connect                                                                        |

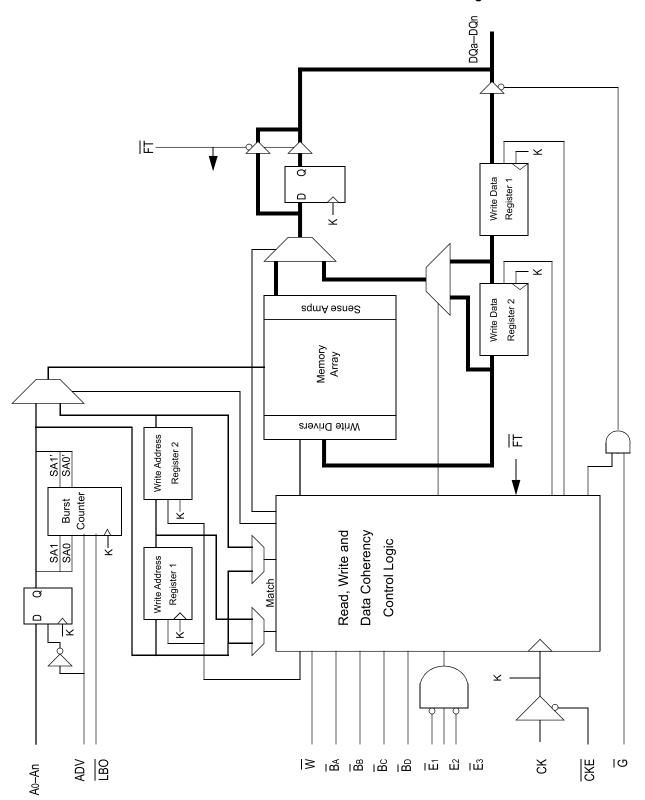

# GS8320Z18/36AGT-xxxV NBT SRAM Functional Block Diagram

#### **Functional Details**

#### Clocking

Deassertion of the Clock Enable (CKE) input blocks the Clock input from reaching the RAM's internal circuits. It may be used to suspend RAM operations. Failure to observe Clock Enable set-up or hold requirements will result in erratic operation.

#### **Pipeline Mode Read and Write Operations**

All inputs (with the exception of Output Enable, Linear Burst  $\underline{Order}$  and Sleep) are synchronized to rising clock edges. Single cycle read and write operations must be initiated with the Advance/ $\underline{Load}$  pin (ADV) held low, in order to load the new address. Device activation is accomplished by asserting all three of the Chip Enable inputs ( $\overline{E}_1$ ,  $E_2$  and  $\overline{E}_3$ ). Deassertion of any one of the Enable inputs will deactivate the device.

| Function        | w | BA | Вв | Bc | Bo |

|-----------------|---|----|----|----|----|

| Read            | Н | Х  | Х  | Х  | Х  |

| Write Byte "a"  | L | L  | Н  | Н  | Н  |

| Write Byte "b"  | L | Н  | L  | Н  | Н  |

| Write Byte "c"  | L | Н  | Н  | L  | Н  |

| Write Byte "d"  | L | Н  | Н  | Н  | L  |

| Write all Bytes | L | L  | L  | L  | L  |

| Write Abort/NOP | L | Н  | Н  | Н  | Н  |

Read operation is initiated when the following conditions are satisfied at the rising edge of clock:  $\overline{CKE}$  is asserted Low, all three chip enables ( $\overline{E}_1$ ,  $E_2$ , and  $\overline{E}_3$ ) are active, the write enable input signals  $\overline{W}$  is deasserted high, and ADV is asserted low. The address presented to the address inputs is latched in to address register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the next rising edge of clock the read data is allowed to propagate through the output register and onto the output pins.

Write operation occurs when the RAM is selected, CKE is active, and the Write input is sampled low at the rising edge of clock. The Byte Write Enable inputs  $(\overline{B}A, \overline{B}B, \overline{B}C, \& \overline{B}D)$  determine which bytes will be written. All or none may be activated. A write cycle with no Byte Write inputs active is a no-op cycle. The pipelined NBT SRAM provides double late write functionality, matching the write command versus data pipeline length (2 cycles) to the read command versus data pipeline length (2 cycles). At the first rising edge of clock, Enable, Write, Byte Write(s), and Address are registered. The Data In associated with that address is required at the third rising edge of clock.

## Flow Through Mode Read and Write Operations

Operation of the RAM in Flow Through mode is very similar to operations in Pipeline mode. Activation of a Read Cycle and the use of the Burst Address Counter is identical. In Flow Through mode the device may begin driving out new data immediately after new address are clocked into the RAM, rather than holding new data until the following (second) clock edge. Therefore, in Flow Through mode the read pipeline is one cycle shorter than in Pipeline mode.

Write operations are initiated in the same way, but differ in that the write pipeline is one cycle shorter as well, preserving the ability to turn the bus from reads to writes without inserting any dead cycles. While the pipelined NBT RAMs implement a double late write protocol, in Flow Through mode a single late write protocol mode is observed. Therefore, in Flow Through mode, address and control are registered on the first rising edge of clock and data in is required at the data input pins at the second rising edge of clock.

## **Synchronous Truth Table**

| Operation                   | Туре | Address  | СК  | CKE | ADV | W | Bx | <u>E</u> 1 | E2 | E <sub>3</sub> | G | ZZ | DQ     | Notes    |

|-----------------------------|------|----------|-----|-----|-----|---|----|------------|----|----------------|---|----|--------|----------|

| Read Cycle, Begin Burst     | R    | External | L-H | L   | L   | Н | Х  | L          | Н  | L              | L | L  | Q      |          |

| Read Cycle, Continue Burst  | В    | Next     | L-H | L   | Н   | Х | Х  | Х          | Х  | Х              | L | L  | Q      | 1,10     |

| NOP/Read, Begin Burst       | R    | External | L-H | L   | L   | Н | Х  | L          | Н  | L              | Н | L  | High-Z | 2        |

| Dummy Read, Continue Burst  | В    | Next     | L-H | L   | Н   | Х | Х  | Х          | Х  | Х              | Н | L  | High-Z | 1,2,10   |

| Write Cycle, Begin Burst    | W    | External | L-H | L   | L   | L | L  | L          | Н  | L              | Х | L  | D      | 3        |

| Write Abort, Begin Burst    | D    | None     | L-H | L   | L   | L | Н  | L          | Н  | L              | Х | L  | High-Z | 1        |

| Write Cycle, Continue Burst | В    | Next     | L-H | L   | Н   | Х | L  | Х          | Х  | Х              | Х | L  | D      | 1,3,10   |

| Write Abort, Continue Burst | В    | Next     | L-H | L   | Н   | Х | Н  | Х          | Х  | Х              | Х | L  | High-Z | 1,2,3,10 |

| Deselect Cycle, Power Down  | D    | None     | L-H | L   | L   | Х | Х  | Н          | Х  | Х              | Х | L  | High-Z |          |

| Deselect Cycle, Power Down  | D    | None     | L-H | L   | L   | Х | Х  | Х          | Х  | Н              | Х | L  | High-Z |          |

| Deselect Cycle, Power Down  | D    | None     | L-H | L   | L   | Х | Х  | Х          | L  | Х              | Х | L  | High-Z |          |

| Deselect Cycle, Continue    | D    | None     | L-H | L   | Н   | Х | Х  | Х          | Х  | Х              | Х | L  | High-Z | 1        |

| Sleep Mode                  |      | None     | Х   | Х   | Х   | Х | Х  | Х          | Х  | Х              | Х | Н  | High-Z |          |

| Clock Edge Ignore, Stall    |      | Current  | L-H | Н   | Х   | Х | Х  | Х          | Х  | Х              | Х | L  | -      | 4        |

- 1. Continue Burst cycles, whether read or write, use the same control inputs. A Deselect continue cycle can only be entered into if a Deselect cycle is executed first.

- 2. Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the W pin is sampled low but no Byte Write pins are active so no write operation is performed.

- 3. G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off during write cycles.

- 4. If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the bus will remain in High Z.

- 5. X = Don't Care; H = Logic High; L = Logic Low;  $\overline{Bx}$  = High = All Byte Write signals are high;  $\overline{Bx}$  = Low = One or more Byte/Write signals are Low

- 6. All inputs, except G and ZZ must meet setup and hold times of rising clock edge.

- 7. Wait states can be inserted by setting CKE high.

- 8. This device contains circuitry that ensures all outputs are in High Z during power-up.

- 9. A 2-bit burst counter is incorporated.

- 10. The address counter is incriminated for all Burst continue cycles.

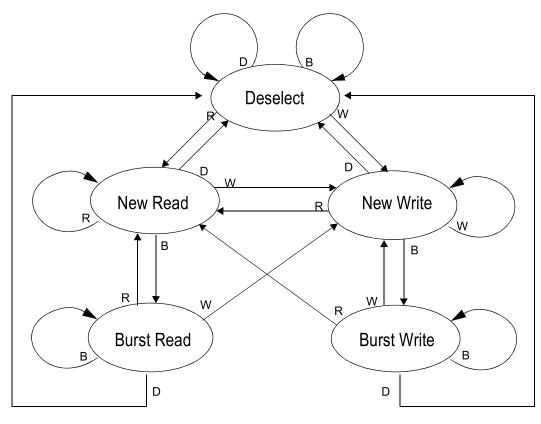

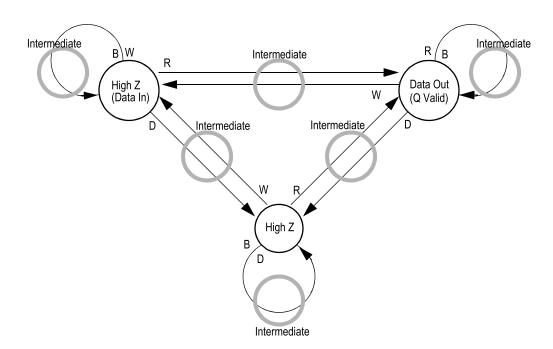

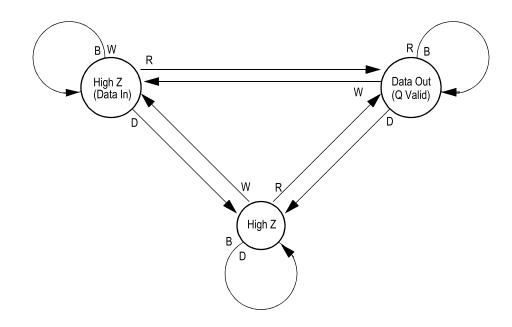

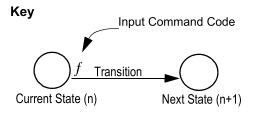

# Pipeline and Flow Through Read Write Control State Diagram

Current State and Next State Definition for Pipeline and Flow Through Read/Write Control State Diagram

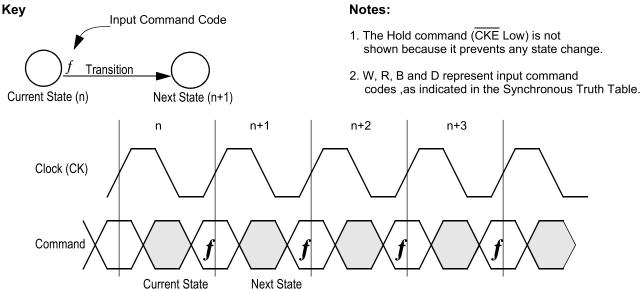

## Pipeline Mode Data I/O State Diagram

- 1. The Hold command (CKE Low) is not shown because it prevents any state change.

- 2. W, R, B, and D represent input command codes as indicated in the Truth Tables.

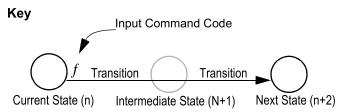

Current State and Next State Definition for Pipeline Mode Data I/O State Diagram

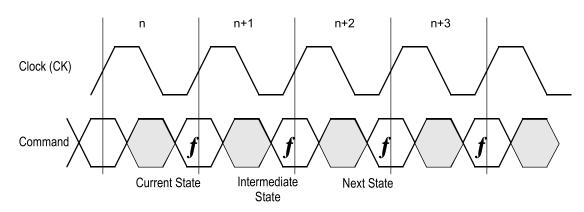

## Flow Through Mode Data I/O State Diagram

#### **Notes**

- 1. The Hold command (CKE Low) is not shown because it prevents any state change.

- 2. W, R, B and D represent input command codes as indicated in the Truth Tables.

Current State and Next State Definition for: Pipeline and Flow Through Read Write Control State Diagram

#### **Burst Cycles**

Although NBT RAMs are designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from read to write, multiple back-to-back reads or writes may also be performed. NBT SRAMs provide an on-chip burst address generator that can be utilized, if desired, to further simplify burst read or write implementations. The ADV control pin, when driven high, commands the SRAM to advance the internal address counter and use the counter generated address to read or write the SRAM. The starting address for the first cycle in a burst cycle series is loaded into the SRAM by driving the ADV pin low, into Load mode.

#### **Burst Order**

The burst address counter wraps around to its initial state after four addresses (the loaded address and three more) have been accessed. The burst sequence is determined by the state of the Linear Burst Order pin (LBO). When this pin is low, a linear burst sequence is selected. When the RAM is installed with the LBO pin tied high, Interleaved burst sequence is selected. See the tables below for details.

#### **Mode Pin Functions**

| Mode Name               | Pin Name | State   | Function                                   |

|-------------------------|----------|---------|--------------------------------------------|

| Burst Order Control     | LBO      |         | Linear Burst                               |

| Burst Order Control     | LBO      | Н       | Interleaved Burst                          |

| Output Posistor Control | FT       | L       | Flow Through                               |

| Output Register Control |          | H or NC | Pipeline                                   |

| Power Down Control      | 77       | L or NC | Active                                     |

| Power Down Control      | ZZ       | Н       | Standby, I <sub>DD</sub> = I <sub>SB</sub> |

#### Note:

There is a pull-up device on the FT pin and a pull-down device on the ZZ pin, so this input pin can be unconnected and the chip will operate in the default states as specified in the above tables.

#### **Burst Counter Sequences**

#### **Linear Burst Sequence**

|             | A[1:0] | A[1:0] | A[1:0] | A[1:0] |

|-------------|--------|--------|--------|--------|

| 1st address | 00     | 01     | 10     | 11     |

| 2nd address | 01     | 10     | 11     | 00     |

| 3rd address | 10     | 11     | 00     | 01     |

| 4th address | 11     | 00     | 01     | 10     |

#### Note:

The burst counter wraps to initial state on the 5th clock.

#### **Interleaved Burst Sequence**

|             | A[1:0] | A[1:0] | A[1:0] | A[1:0] |

|-------------|--------|--------|--------|--------|

| 1st address | 00     | 01     | 10     | 11     |

| 2nd address | 01     | 00     | 11     | 10     |

| 3rd address | 10     | 11     | 00     | 01     |

| 4th address | 11     | 10     | 01     | 00     |

#### Note:

The burst counter wraps to initial state on the 5th clock.

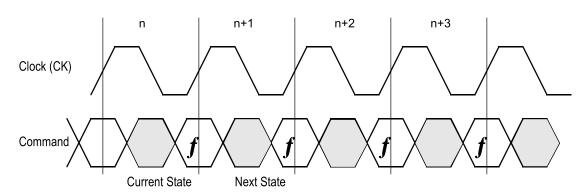

## Sleep Mode

During normal operation, ZZ must be pulled low, either by the user or by it's internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after 2 cycles of wake up time.

Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to  $I_{SB}2$ . The duration of Sleep mode is dictated by the length of time the ZZ is in a high state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high,  $I_{SB}2$  is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a deselect or read commands may be applied while the SRAM is recovering from Sleep mode.

## **Sleep Mode Timing Diagram**

#### **Designing for Compatibility**

The GSI NBT SRAMs offer users a configurable selection between Flow Through mode and Pipeline mode via the FT signal found on Pin 14. Not all vendors offer this option, however most mark Pin 14 as  $V_{DD}$  or  $V_{DDQ}$  on pipelined parts and  $V_{SS}$  on flow through parts. GSI NBT SRAMs are fully compatible with these sockets.

## **Absolute Maximum Ratings**

(All voltages reference to  $V_{\rm SS}$ )

| Symbol             | Description                      | Value                                                      | Unit |

|--------------------|----------------------------------|------------------------------------------------------------|------|

| V <sub>DD</sub>    | Voltage on V <sub>DD</sub> Pins  | -0.5 to 4.6                                                | V    |

| $V_{\mathrm{DDQ}}$ | Voltage on V <sub>DDQ</sub> Pins | –0.5 to V <sub>DD</sub>                                    | V    |

| V <sub>I/O</sub>   | Voltage on I/O Pins              | $-0.5$ to V <sub>DD</sub> +0.5 ( $\leq$ 4.6 V max.)        | V    |

| V <sub>IN</sub>    | Voltage on Other Input Pins      | $-0.5 \text{ to V}_{DD} + 0.5 \ (\leq 4.6 \text{ V max.})$ | V    |

| I <sub>IN</sub>    | Input Current on Any Pin         | +/20                                                       | mA   |

| I <sub>OUT</sub>   | Output Current on Any I/O Pin    | +/–20                                                      | mA   |

| P <sub>D</sub>     | Package Power Dissipation        | 1.5                                                        | W    |

| T <sub>STG</sub>   | Storage Temperature              | -55 to 125                                                 | °C   |

| T <sub>BIAS</sub>  | Temperature Under Bias           | -55 to 125                                                 | °C   |

#### Note:

Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component.

## Power Supply Voltage Ranges (1.8 V/2.5 V Version)

| Parameter                                 | Symbol            | Min. | Тур. | Max.            | Unit |

|-------------------------------------------|-------------------|------|------|-----------------|------|

| 1.8 V Supply Voltage                      | V <sub>DD1</sub>  | 1.7  | 1.8  | 2.0             | V    |

| 2.5 V Supply Voltage                      | V <sub>DD2</sub>  | 2.3  | 2.5  | 2.7             | V    |

| 1.8 V V <sub>DDQ</sub> I/O Supply Voltage | V <sub>DDQ1</sub> | 1.7  | 1.8  | V <sub>DD</sub> | V    |

| 2.5 V V <sub>DDQ</sub> I/O Supply Voltage | V <sub>DDQ2</sub> | 2.3  | 2.5  | V <sub>DD</sub> | V    |

# V<sub>DDQ2</sub> & V<sub>DDQ1</sub> Range Logic Levels

| Parameter                          | Symbol          | Min.                | Тур. | Max.                  | Unit |

|------------------------------------|-----------------|---------------------|------|-----------------------|------|

| V <sub>DD</sub> Input High Voltage | V <sub>IH</sub> | 0.6*V <sub>DD</sub> | _    | V <sub>DD</sub> + 0.3 | V    |

| V <sub>DD</sub> Input Low Voltage  | V <sub>IL</sub> | -0.3                |      | 0.3*V <sub>DD</sub>   | V    |

#### Notes:

- Unless otherwise noted, all performance specifications quoted are evaluated for worst case in the temperature range marked on the device.

- 2.  $V_{IH}$  (max) must be met for any instantaneous value of  $V_{DD}$ .

- 3. V<sub>DD</sub> needs to power-up before or at the same time as V<sub>DDQ</sub> to make sure V<sub>IH</sub> (max) is not exceeded.

## **Operating Temperature**

| Parameter                                            | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|--------|------|------|------|------|

| Junction Temperature<br>(Commercial Range Versions)  | TJ     | 0    | 25   | 85   | °C   |

| Junction Temperature<br>(Industrial Range Versions)* | TJ     | -40  | 25   | 100  | °C   |

#### Note:

## **Thermal Impedance**

| Package  | Test PCB<br>Substrate | θ JA (C°/W)<br>Airflow = 0 m/s | θ JA (C°/W)<br>Airflow = 1 m/s | θ JA (C°/W)<br>Airflow = 2 m/s | θ JB (C°/W) | θ JC (C°/W) |

|----------|-----------------------|--------------------------------|--------------------------------|--------------------------------|-------------|-------------|

| 100 TQFP | 4-layer               | 28.7                           | 23.8                           | 22.3                           | 15.1        | 6.5         |

#### Notes:

- 1. Thermal Impedance data is based on a number of of samples from mulitple lots and should be viewed as a typical number.

- 2. Please refer to JEDEC standard JESD51-6.

- 3. The characteristics of the test fixture PCB influence reported thermal characteristics of the device. Be advised that a good thermal path to the PCB can result in cooling or heating of the RAM depending on PCB temperature.

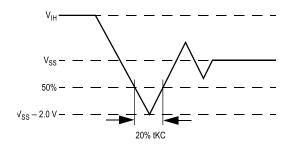

# **Undershoot Measurement and Timing**

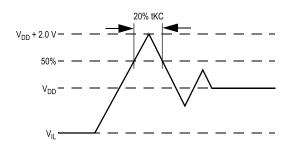

## **Overshoot Measurement and Timing**

#### Note:

Input Under/overshoot voltage must be -2 V > Vi < V<sub>DDn</sub>+2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.

## Capacitance

$$(T_A = 25^{\circ}C, f = 1 \text{ MHz}, V_{DD} = 2.5 \text{ V})$$

| Parameter                | Symbol           | Test conditions        | Тур. | Max. | Unit |

|--------------------------|------------------|------------------------|------|------|------|

| Input Capacitance        | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V  | 8    | 10   | pF   |

| Input/Output Capacitance | C <sub>I/O</sub> | V <sub>OUT</sub> = 0 V | 12   | 14   | pF   |

#### Note:

These parameters are sample tested.

<sup>\*</sup> The part numbers of Industrial Temperature Range versions end with the character "I". Unless otherwise noted, all performance specifications quoted are evaluated for worst case in the temperature range marked on the device.

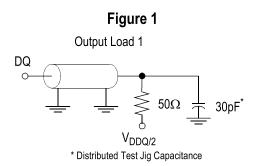

## **AC Test Conditions**

| Parameter              | Conditions              |

|------------------------|-------------------------|

| Input high level       | V <sub>DD</sub> – 0.2 V |

| Input low level        | 0.2 V                   |

| Input slew rate        | 1 V/ns                  |

| Input reference level  | V <sub>DD</sub> /2      |

| Output reference level | V <sub>DDQ</sub> /2     |

| Output load            | Fig. 1                  |

#### Notes:

- 1. Include scope and jig capacitance.

- 2. Test conditions as specified with output loading as shown in **Fig. 1** unless otherwise noted.

- 3. Device is deselected as defined by the Truth Table.

## **DC Electrical Characteristics**

| Parameter                                | Symbol           | Test Conditions                                         | Min                      | Max    |

|------------------------------------------|------------------|---------------------------------------------------------|--------------------------|--------|

| Input Leakage Current (except mode pins) | I <sub>IL</sub>  | V <sub>IN</sub> = 0 to V <sub>DD</sub>                  | –1 uA                    | 1 uA   |

| FT Input Current                         | I <sub>IN</sub>  | $V_{DD} \ge V_{IN} \ge 0 V$                             | -100 uA                  | 100 uA |

| Output Leakage Current                   | l <sub>OL</sub>  | Output Disable, V <sub>OUT</sub> = 0 to V <sub>DD</sub> | −1 uA                    | 1 uA   |

| 1.8 V Output High Voltage                | V <sub>OH1</sub> | $I_{OH} = -4 \text{ mA}, V_{DDQ} = 1.7 \text{ V}$       | V <sub>DDQ</sub> – 0.4 V | _      |

| 2.5 V Output High Voltage                | V <sub>OH2</sub> | I <sub>OH</sub> = -8 mA, V <sub>DDQ</sub> = 2.375 V     | 1.7 V                    |        |

| 1.8 V Output Low Voltage                 | V <sub>OL1</sub> | I <sub>OL</sub> = 4 mA                                  |                          | 0.4 V  |

| 2.5 V Output Low Voltage                 | V <sub>OL2</sub> | I <sub>OL</sub> = 8 mA                                  | _                        | 0.4 V  |

|   |                                                 |        |              |                 |                 | -333              | 77              | -250              | -200            | 90                | -               | -150              |      |

|---|-------------------------------------------------|--------|--------------|-----------------|-----------------|-------------------|-----------------|-------------------|-----------------|-------------------|-----------------|-------------------|------|

|   | Test Conditions                                 |        | Mode         | Symbol          | 0<br>to<br>70°C | -40<br>to<br>85°C | 0<br>to<br>70°C | -40<br>to<br>85°C | 0<br>to<br>70°C | -40<br>to<br>85°C | 0<br>to<br>70°C | -40<br>to<br>85°C | Unit |

| 1 |                                                 | (96^)  | Pipeline     | اما<br>موما     | 300<br>70       | 310<br>70         | 240<br>50       | 250<br>50         | 205<br>40       | 215<br>40         | 170<br>30       | 180               | mA   |

|   | Device Selected;<br>All other inputs            | (ocv)  | Flow Through | اما<br>موما     | 220<br>45       | 230<br>45         | 190<br>40       | 200<br>40         | 170<br>35       | 180<br>35         | 165<br>30       | 175<br>30         | mA   |

|   | $\geq V_{IH}$ or $\leq V_{IL}$<br>Output open   | (42)   | Pipeline     | اما<br>موما     | 280<br>35       | 290<br>35         | 200<br>25       | 210<br>25         | 165<br>20       | 175<br>20         | 150<br>20       | 160<br>20         | mA   |

|   |                                                 | (ol v) | Flow Through | اما<br>موما     | 180<br>25       | 190<br>25         | 160<br>20       | 170<br>20         | 150<br>20       | 160<br>20         | 140<br>20       | 150<br>20         | mA   |

|   | V C OV < ZZ                                     |        | Pipeline     | l <sub>SB</sub> | 30              | 40                | 30              | 40                | 30              | 40                | 30              | 40                | mA   |

|   | ~ ~ ~ DD — 0.5 v                                |        | Flow Through | l <sub>SB</sub> | 30              | 40                | 30              | 40                | 30              | 40                | 30              | 40                | mA   |

|   | Device Deselected;                              |        | Pipeline     | aal             | 80              | 90                | 70              | 80                | 09              | 70                | 55              | 65                | mA   |

|   | All other inputs $\geq V_{ H}$ of $\leq V_{ L}$ |        | Flow Through | aal             | 65              | 75                | 09              | 70                | 55              | 65                | 50              | 09                | mA   |

| 1 |                                                 |        |              |                 |                 |                   |                 |                   |                 |                   |                 |                   |      |

$I_{DD}$  and  $I_{DDQ}$  apply to any combination of  $V_{DD}$  and  $V_{DDQ}$  operation. All parameters listed are worst case scenario.

## **AC Electrical Characteristics**

|           | Parameter                    | Symbol            | -33 | 33  | -25 | 50  | -20 | 0   | -1  | 50  | Unit  |

|-----------|------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

|           | raiailletei                  | Syllibol          | Min | Max | Min | Max | Min | Max | Min | Max | Oilit |

|           | Clock Cycle Time             | tKC               | 3.0 | _   | 4.0 | _   | 5.0 | _   | 6.7 | _   | ns    |

|           | Clock to Output Valid        | tKQ               | _   | 3.0 | 1   | 3.0 | 1   | 3.0 | l   | 3.8 | ns    |

| Pipeline  | Clock to Output Invalid      | tKQX              | 1.5 | _   | 1.5 | _   | 1.5 |     | 1.5 | _   | ns    |

| Pipelille | Clock to Output in Low-Z     | tLZ <sup>1</sup>  | 1.5 | _   | 1.5 |     | 1.5 | _   | 1.5 |     | ns    |

|           | Setup time                   | tS                | 1.0 | _   | 1.2 | _   | 1.4 | _   | 1.5 | _   | ns    |

|           | Hold time                    | tH                | 0.1 | _   | 0.2 | _   | 0.4 | _   | 0.5 | _   | ns    |

|           | Clock Cycle Time             | tKC               | 5.0 | _   | 5.5 | _   | 6.5 | _   | 7.5 | _   | ns    |

|           | Clock to Output Valid        | tKQ               | _   | 5.0 | _   | 5.5 | _   | 6.5 | _   | 7.5 | ns    |

| Flow      | Clock to Output Invalid      | tKQX              | 2.0 | _   | 2.0 | _   | 2.0 | _   | 2.0 | _   | ns    |

| Through   | Clock to Output in Low-Z     | tLZ <sup>1</sup>  | 2.0 | _   | 2.0 | _   | 2.0 | _   | 2.0 | _   | ns    |

|           | Setup time                   | tS                | 1.3 | _   | 1.5 | _   | 1.5 | _   | 1.5 | _   | ns    |

|           | Hold time                    | tH                | 0.3 | _   | 0.5 |     | 0.5 | _   | 0.5 |     | ns    |

|           | Clock HIGH Time              | tKH               | 1.0 | _   | 1.3 | _   | 1.3 | _   | 1.5 | _   | ns    |

|           | Clock LOW Time               | tKL               | 1.2 | _   | 1.5 | _   | 1.5 | _   | 1.7 | _   | ns    |

|           | Clock to Output in<br>High-Z | tHZ <sup>1</sup>  | 1.5 | 3.0 | 1.5 | 3.0 | 1.5 | 3.0 | 1.5 | 3.8 | ns    |

|           | G to Output Valid            | tOE               | _   | 3.0 |     | 3.0 | _   | 3.0 | _   | 3.8 | ns    |

|           | G to output in Low-Z         | tOLZ <sup>1</sup> | 0   | _   | 0   | _   | 0   | _   | 0   | _   | ns    |

|           | G to output in High-Z        | tOHZ <sup>1</sup> | _   | 3.0 | _   | 3.0 | _   | 3.0 |     | 3.8 | ns    |

|           | ZZ setup time                | tZZS <sup>2</sup> | 5   | _   | 5   | _   | 5   | _   | 5   | _   | ns    |

|           | ZZ hold time                 | tZZH <sup>2</sup> | 1   | _   | 1   | _   | 1   | _   | 1   | _   | ns    |

|           | ZZ recovery                  | tZZR              | 20  | _   | 20  | _   | 20  | _   | 20  | _   | ns    |

<sup>1.</sup> These parameters are sampled and are not 100% tested.

<sup>2.</sup> ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and hold times as specified above.

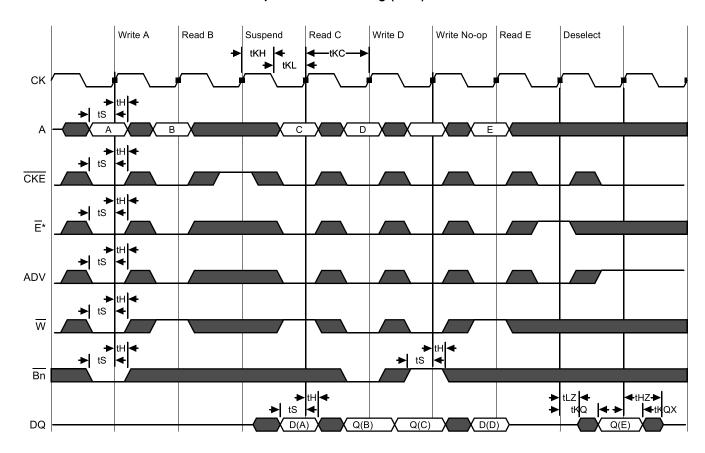

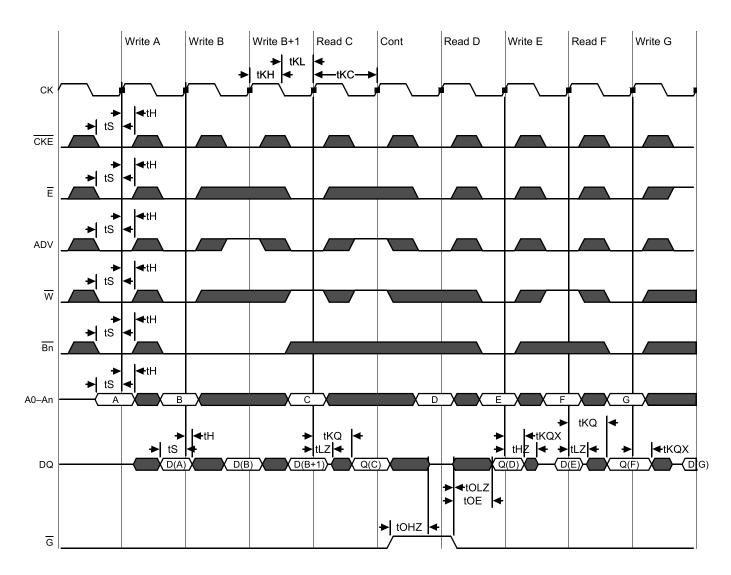

# **Pipeline Mode Timing (NBT)**

# Flow Through Mode Timing (NBT)

\*Note:  $\overline{E}$  = High(False) if  $\overline{E1}$  = 1 or  $\overline{E2}$  = 0 or  $\overline{E3}$  = 1

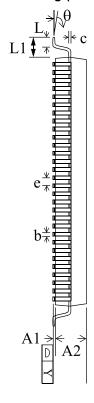

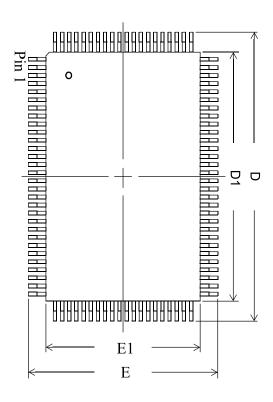

# TQFP Package Drawing (Package T)

| Symbol | Description        | Min. | Nom. | Max  |

|--------|--------------------|------|------|------|

| A1     | Standoff           | 0.05 | 0.10 | 0.15 |

| A2     | Body Thickness     | 1.35 | 1.40 | 1.45 |

| b      | Lead Width         | 0.20 | 0.30 | 0.40 |

| С      | Lead Thickness     | 0.09 | _    | 0.20 |

| D      | Terminal Dimension | 21.9 | 22.0 | 22.1 |

| D1     | Package Body       | 19.9 | 20.0 | 20.1 |

| Е      | Terminal Dimension | 15.9 | 16.0 | 16.1 |

| E1     | Package Body       | 13.9 | 14.0 | 14.1 |

| е      | Lead Pitch         | _    | 0.65 | _    |

| L      | Foot Length        | 0.45 | 0.60 | 0.75 |

| L1     | Lead Length        | _    | 1.00 | _    |

| Y      | Coplanarity        |      |      | 0.10 |

| θ      | Lead Angle         | 0°   | _    | 7°   |

- 1. All dimensions are in millimeters (mm).

- 2. Package width and length do not include mold protrusion.

## Ordering Information—GSI NBT Synchronous SRAM

| Org     | Part Number <sup>1</sup> | Туре | Voltage<br>Option | Package             | Speed <sup>2</sup><br>(MHz/ns) | T <sub>J</sub> <sup>3</sup> |

|---------|--------------------------|------|-------------------|---------------------|--------------------------------|-----------------------------|

| 2M x 18 | GS8320Z18AGT-333V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 333/5.0                        | С                           |

| 2M x 18 | GS8320Z18AGT-250V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 250/5.5                        | С                           |

| 2M x 18 | GS8320Z18AGT-200V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 200/6.5                        | С                           |

| 2M x 18 | GS8320Z18AGT-150V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 150/7.5                        | С                           |

| 1M x 36 | GS8320Z36AGT-333V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 333/5.0                        | С                           |

| 1M x 36 | GS8320Z36AGT-250V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 250/5.5                        | С                           |

| 1M x 36 | GS8320Z36AGT-200V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 200/6.5                        | С                           |

| 1M x 36 | GS8320Z36AGT-150V        | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 150/7.5                        | С                           |

| 2M x 18 | GS8320Z18AGT-333IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 333/5.0                        | I                           |

| 2M x 18 | GS8320Z18AGT-250IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 250/5.5                        | I                           |

| 2M x 18 | GS8320Z18AGT-200IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 200/6.5                        | ı                           |

| 2M x 18 | GS8320Z18AGT-150IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 150/7.5                        | I                           |

| 1M x 36 | GS8320Z36AGT-333IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 333/5.0                        | I                           |

| 1M x 36 | GS8320Z36AGT-250IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 250/5.5                        | ı                           |

| 1M x 36 | GS8320Z36AGT-200IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 200/6.5                        | I                           |

| 1M x 36 | GS8320Z36AGT-150IV       | NBT  | 1.8 V or 2.5 V    | RoHS-compliant TQFP | 150/7.5                        | ı                           |

- Customers requiring delivery in Tape and Reel should add the character "T" to the end of the part number. Example: GS8320Z36AGT-150IVT.

- 2. The speed column indicates the cycle frequency (MHz) of the device in Pipeline mode and the latency (ns) in Flow Through mode. Each device is Pipeline/Flow Through mode-selectable by the user.

- 3. C = Commercial Temperature Range. I = Industrial Temperature Range.

- 4. GSI offers other versions this type of device in many different configurations and with a variety of different features, only some of which are covered in this data sheet. See the GSI Technology web site (<a href="www.gsitechnology.com">www.gsitechnology.com</a>) for a complete listing of current offerings

# 36Mb Sync SRAM Datasheet Revision History

| File Name        | Types of Changes<br>Format or Content | Page;Revisions;Reason                                                                                                                                            |

|------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8320ZxxA_V_r1    |                                       | Creation of new datasheet                                                                                                                                        |

| 8320ZxxA_V_r1_01 | Content                               | Updated Absolute Maximum Ratings     Added thermal information                                                                                                   |

| 8320ZxxA_V_r1_02 | Content                               | Updated to reflect MP status                                                                                                                                     |

| 8320ZxxA_V_r1_03 | Content                               | <ul> <li>Updated Op current numbers</li> <li>Updated tHZ, tOE, and tOHZ to 3.0 ns for 333 and 300 MHz</li> <li>(Rev1.03a: Updated op current numbers)</li> </ul> |