### ISL28134

5V Ultra Low Noise, Auto-Zero Rail-to-Rail Precision Op Amp

FN6957 Rev.6.03 Oct 27, 2022

The <u>ISL28134</u> is a single, auto-zeroing operational amplifier optimized for single and dual supply operation from 2.25V to 6.0V and  $\pm 1.125$ V and  $\pm 3.0$ V. The ISL28134 uses auto-zeroing circuitry to provide very low input offset voltage, drift and a reduction of the 1/f noise corner below 0.1Hz. The ISL28134 achieves ultra low offset voltage, offset temperature drift, wide gain bandwidth and rail-to-rail input/output swing while minimizing power consumption.

The ISL28134 is ideal for amplifying the sensor signals of analog front-ends that include pressure, temperature, medical, strain gauge and inertial sensors down to the  $\mu V$  levels.

The ISL28134 can be used over standard amplifiers with high stability across the industrial temperature range of -40°C to +85°C and the full industrial temperature range of -40°C to +125°C. The ISL28134 is available in an industry standard pinout SOIC and SOT-23 packages.

### **Applications**

- · Medical instrumentation

- · Sensor gain amps

- · Precision low drift, low frequency ADC drivers

- · Precision voltage reference buffers

- Thermopile, thermocouple, and other temperature sensors front-end amplifiers

- · Inertial sensors

- · Process control systems

- · Weight scales and strain gauge sensors

### **Features**

- · Rail-to-rail inputs and outputs

- CMRR at  $V_{CM}$  = 0.1V beyond  $V_{S}$  ................... 135dB, typ

- No 1/f noise corner down to 0.1Hz

- 0.1Hz to 10Hz noise voltage...... 250nV<sub>P-P</sub>

- Low offset voltage ...... 2.5µV, Max

- Dual supply ...... ±1.125V to ±3.0V

- Low I<sub>CC</sub> ...... 675μA, typ

- Operating temperature range

- Industrial.....-40°C to +85°C

- Packaging

- Single: SOIC, SOT-23

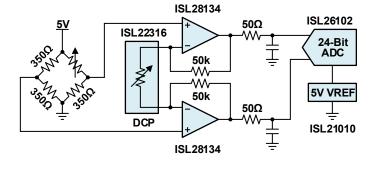

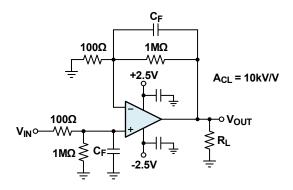

FIGURE 1. PRECISION WEIGH SCALE / STRAIN GAUGE

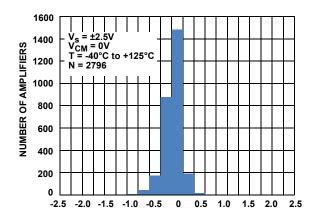

FIGURE 2. V<sub>OS</sub> HISTOGRAM V<sub>S</sub> = 5V

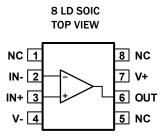

## **Pin Configurations**

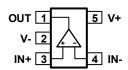

5 LD SOT-23 TOP VIEW

## **Pin Descriptions**

| ISL28134<br>(8 Ld SOIC) | ISL28134<br>(5 Ld SOT-23) | PIN<br>NAME | FUNCTION            | EQUIVALENT CIRCUIT                         |

|-------------------------|---------------------------|-------------|---------------------|--------------------------------------------|

| 2                       | 4                         | IN-         | Inverting input     | (See Circuit 1)                            |

| 3                       | 3                         | IN+         | Non-inverting input | IN+ OSC OSC Circuit 1                      |

| 4                       | 2                         | V-          | Negative supply     |                                            |

| 6                       | 1                         | OUT         | Output              | V+ OUT V- Circuit 2                        |

| 7                       | 5                         | V+          | Positive supply     |                                            |

| 1, 5, 8                 | -                         | NC          | No Connect          | Pin is floating. No connection made to IC. |

## **Ordering Information**

| PART NUMBER<br>(Notes 2, 3) | PART<br>MARKING  | PACKAGE DESCRIPTION (RoHS Compliant) | PKG.<br>DWG. # | CARRIER TYPE<br>(Note 1) | TEMP RANGE      |

|-----------------------------|------------------|--------------------------------------|----------------|--------------------------|-----------------|

| ISL28134IBZ                 | 28134            | 8 Ld SOIC                            | M8.15E         | Tube                     | -40°C to +85°C  |

| ISL28134IBZ-T13             | IBZ              |                                      |                | Reel, 2.5k               |                 |

| ISL28134IBZ-T7              |                  |                                      |                | Reel, 1k                 |                 |

| ISL28134IBZ-T7A             |                  |                                      |                | Reel, 250                |                 |

| ISL28134FHZ-T7              | BEEA (Note 4)    | 5 Ld SOT-23                          | P5.064A        | Reel, 3k                 | -40°C to +125°C |

| ISL28134FHZ-T7A             |                  |                                      |                | Reel, 250                |                 |

| ISL28134ISENSEV1Z           | Evaluation Board |                                      |                |                          |                 |

| ISL28134SOICEVAL1Z          | Evaluation Board |                                      |                |                          |                 |

#### NOTES:

- 1. See  $\underline{\mathsf{TB347}}$  for details about reel specifications.

- These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus

anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 3. For Moisture Sensitivity Level (MSL), see the ISL28134 device page. For more information about MSL, see TB363.

- 4. The part marking is located on the bottom of the part.

### **Absolute Maximum Ratings**

| Supply Voltage V+ to V                            |   |

|---------------------------------------------------|---|

| Input Differential Voltage                        |   |

| •                                                 |   |

| Input Current                                     |   |

| Voltage VOUT to GND (10s)                         | • |

| dv/dt Supply Slew Rate                            | 5 |

| Human Body Model (Tested per JED22-A114F) 4k      | ٧ |

| Machine Model (Tested per JED22-A115B)300         | ٧ |

| Charged Device Model (Tested per JED22-C110D) 2k\ | ٧ |

| Latch-up (Passed Per JESD78B)+125°0               | С |

### **Thermal Information**

| Thermal Resistance (Typical)      | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------|----------------------|----------------------|

| 5 Ld SOT-23 (Notes 5, 6)          | 225                  | 116                  |

| 8 Ld SOIC (Notes 5, 6)            | 125                  | 77.2                 |

| Maximum Storage Temperature Range | 6                    | 65°C to +150°C       |

| Pb-Free Reflow Profile            |                      | see <u>TB493</u>     |

### **Operating Conditions**

| Ambient Operating Temperature Range |                             |

|-------------------------------------|-----------------------------|

| Industrial Grade Package            | 40°C to +85°C               |

| Full Industrial Grade Package       | 40°C to +125°C              |

| Operating Voltage Range             | 2.25V (±1.125V) to 6V (±3V) |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See <u>TB379</u> for details.

- 6. For  $\theta_{\mbox{\scriptsize JC}}\!,$  the "case temp" location is taken at the package top center.

# **Electrical Specifications** $V_S = 5V$ , $V_{CM} = 2.5V$ , $T_A = +25^{\circ}C$ , unless otherwise specified. Boldface limits apply across the specified operating temperature range.

| PARAMETER                          | DESCRIPTION                                     | TEST CONDITIONS                          | MIN<br>( <u>Note 7</u> ) | TYP  | MAX<br>(Note 7) | UNITS    |

|------------------------------------|-------------------------------------------------|------------------------------------------|--------------------------|------|-----------------|----------|

| DC SPECIFICATIONS                  |                                                 |                                          | <u>'</u>                 | Į.   | J.              | <u>I</u> |

| V <sub>OS</sub>                    | Input Offset Voltage                            |                                          | -2.5                     | -0.2 | 2.5             | μ۷       |

|                                    |                                                 | T <sub>A</sub> = -40°C to +85°C          | -3.4                     | -    | 3.4             | μV       |

|                                    |                                                 | T <sub>A</sub> = -40°C to +125°C         | -4                       | -    | 4               | μV       |

| TCV <sub>OS</sub>                  | Input Offset Voltage Temperature<br>Coefficient | T <sub>A</sub> = -40°C to +125°C         | -15                      | -0.5 | 15              | nV/°C    |

| I <sub>B</sub>                     | Input Bias Current                              |                                          | -300                     | ±120 | 300             | рA       |

|                                    |                                                 | T <sub>A</sub> = -40°C to +85°C          | -300                     | -    | 300             | рA       |

|                                    |                                                 | T <sub>A</sub> = -40°C to +125°C         | -550                     | -    | 550             | рA       |

| TCIB                               | Input Bias Current Temperature<br>Coefficient   | $T_A = -40$ °C to +85 °C                 | -                        | ±1.4 | -               | pA/°C    |

|                                    |                                                 | T <sub>A</sub> = -40°C to +125°C         | -                        | ±2   | -               | pA/°C    |

| los                                | Input Offset Current                            |                                          | -600                     | ±240 | 600             | рA       |

|                                    |                                                 | T <sub>A</sub> = -40°C to +85°C          | -600                     | -    | 600             | рA       |

|                                    |                                                 | T <sub>A</sub> = -40°C to +125°C         | -750                     | -    | 750             | рA       |

| TCIOS                              | Input Offset Current Temperature Coefficient    | $T_A = -40$ °C to +85 °C                 | -                        | ±2.8 | -               | pA/°C    |

|                                    |                                                 | T <sub>A</sub> = -40°C to +125°C         | -                        | ±4   | -               | pA/°C    |

| Common Mode Input<br>Voltage Range |                                                 | V+ = 5.0V, V- = 0V<br>Guaranteed by CMRR | -0.1                     | -    | 5.1             | V        |

| CMRR                               | Common Mode Rejection Ratio                     | V <sub>CM</sub> = -0.1V to 5.1V          | 120                      | 135  | -               | dB       |

|                                    |                                                 | V <sub>CM</sub> = -0.1V to 5.1V          | 115                      | -    | -               | dB       |

| PSRR                               | Power Supply Rejection Ratio                    | V <sub>S</sub> = 2.25V to 6.0V           | 120                      | 135  | -               | dB       |

|                                    |                                                 | V <sub>S</sub> = 2.25V to 6.0V           | 120                      | -    | -               | dB       |

| V <sub>S</sub>                     | Supply Voltage (V+ to V-)                       | Guaranteed by PSRR                       | 2.25                     | -    | 6.0             | ٧        |

# **Electrical Specifications** $V_S = 5V$ , $V_{CM} = 2.5V$ , $T_A = +25$ °C, unless otherwise specified. Boldface limits apply across the specified operating temperature range. (Continued)

| PARAMETER                                      | DESCRIPTION                                                         | TEST CONDITIONS                                                                                              | MIN<br>(Note 7) | TYP  | MAX<br>(Note 7) | UNITS             |

|------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|-------------------|

| Is                                             | Supply Current Per Amplifier                                        | R <sub>L</sub> = OPEN                                                                                        | -               | 675  | 900             | μΑ                |

|                                                |                                                                     | R <sub>L</sub> = OPEN<br>T <sub>A</sub> = -40°C to +85°C                                                     | -               | -    | 1075            | μΑ                |

|                                                |                                                                     | R <sub>L</sub> = OPEN<br>T <sub>A</sub> = -40 °C to +125 °C                                                  | -               | -    | 1150            | μΑ                |

| I <sub>SC</sub>                                | Short Circuit Output Source Current                                 | R <sub>L</sub> = Short to V-                                                                                 | -               | 65   | -               | mA                |

|                                                | Short Circuit Output Sink Current                                   | R <sub>L</sub> = Short to V+                                                                                 | -               | -65  | -               | mA                |

| V <sub>OH</sub>                                | Output Voltage Swing, HIGH                                          | $R_L = 10k\Omega$ to $V_{CM}$                                                                                | 15              | 10   | -               | mV                |

|                                                | From V <sub>OUT</sub> to V <sub>+</sub>                             | $R_L = 10k\Omega$ to $V_{CM}$                                                                                | 15              | -    | -               | mV                |

| V <sub>OL</sub>                                | Output Voltage Swing, LOW                                           | $R_L = 10k\Omega$ to $V_{CM}$                                                                                | -               | 10   | 15              | mV                |

|                                                | From V <sub>-</sub> to V <sub>OUT</sub>                             | $R_L = 10k\Omega$ to $V_{CM}$                                                                                | -               | -    | 15              | mV                |

| A <sub>OL</sub>                                | Open Loop Gain                                                      | $R_L = 1M\Omega$                                                                                             | -               | 174  | -               | dB                |

| AC SPECIFICATIONS                              |                                                                     |                                                                                                              |                 | 1    | 1               |                   |

| C <sub>IN</sub> Input Capacitance              | Input Capacitance                                                   | Differential                                                                                                 | -               | 5.2  | -               | pF                |

|                                                |                                                                     | Common Mode                                                                                                  | -               | 5.6  | -               | pF                |

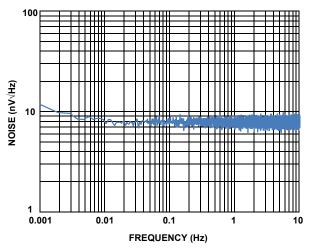

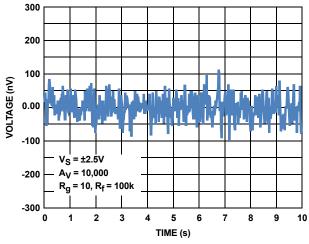

| e <sub>N</sub>                                 | Input Noise Voltage                                                 | f = 0.1Hz to 10Hz                                                                                            | -               | 250  | 400             | nV <sub>P-P</sub> |

|                                                |                                                                     | f = 10Hz                                                                                                     | -               | 8    | -               | nV/√Hz            |

|                                                |                                                                     | f = 1kHz                                                                                                     | -               | 10   | -               | nV/√Hz            |

| I <sub>N</sub>                                 | Input Noise Current                                                 | f = 1kHz                                                                                                     | -               | 200  | -               | fA/√Hz            |

| GBWP                                           | Gain Bandwidth Product                                              |                                                                                                              | -               | 3.5  | -               | MHz               |

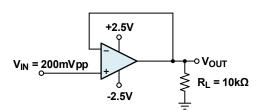

| EMIRR                                          | EMI Rejection Ratio                                                 | A <sub>V</sub> = +1, V <sub>IN</sub> = 200mV <sub>p-p</sub> , V <sub>CM</sub> = 0V,<br>V+ = 2.5V, V- = -2.5V | -               | 75   | -               | dB                |

| TRANSIENT RESPON                               | SE                                                                  |                                                                                                              | ll .            |      |                 | .1                |

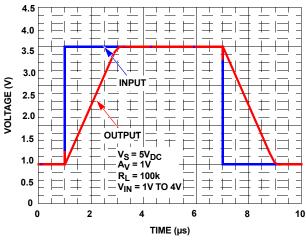

| SR                                             | Positive Slew Rate                                                  | $V+ = 5V$ , $V- = 0V$ , $V_{OUT} = 1V$ to $3V$ , $R_L = 100k\Omega$ ,                                        | -               | 1.5  | -               | V/µs              |

|                                                | Negative Slew Rate                                                  | C <sub>L</sub> = 3.7pF                                                                                       | -               | 1.0  | -               | V/µs              |

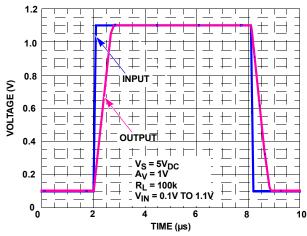

| t <sub>r</sub> , t <sub>f</sub> , Small Signal | Rise Time, t <sub>r</sub> 10% to 90%                                | $V+ = 5V, V- = 0V, V_{OUT} = 0.1V_{P-P}, R_F = 0\Omega,$                                                     | -               | 0.07 | -               | μs                |

|                                                | Fall Time, t <sub>f</sub> 10% to 90%                                | $R_L = 100k\Omega, C_L = 3.7pF$                                                                              |                 | 0.17 | -               | μs                |

| t <sub>r</sub> , t <sub>f</sub> Large Signal   | Rise Time, t <sub>r</sub> 10% to 90%                                | $V+ = 5V, V- = 0V, V_{OUT} = 2V_{P-P}, R_F = 0\Omega,$                                                       | -               | 1.3  | -               | μs                |

|                                                | Fall Time, t <sub>f</sub> 10% to 90%                                | $R_L = 100k\Omega$ , $C_L = 3.7pF$                                                                           | -               | 2.0  | -               | μs                |

| t <sub>s</sub>                                 | Settling Time to 0.1%, 2V <sub>P-P</sub> Step                       | $A_V = -1$ , $R_F = 1k\Omega$ , $C_L = 3.7pF$                                                                | -               | 100  | -               | μs                |

| t <sub>recover</sub>                           | Output Overload Recovery Time, Recovery to 90% of Output Saturation | $A_V = +2$ , $R_F = 10k\Omega$ , $R_L = 100k$ , $C_L = 3.7pF$                                                | -               | 3.1  | -               | μs                |

# **Electrical Specifications** $V_S = 2.5V$ , $V_{CM} = 1.25V$ , $T_A = +25$ °C, unless otherwise specified. **Boldface limits apply over the specified** operating temperature range.

| PARAMETER                          | DESCRIPTION                                     | TEST CONDITIONS                                           | MIN<br>(Note 7) | ТҮР  | MAX<br>(Note 7) | UNITS             |

|------------------------------------|-------------------------------------------------|-----------------------------------------------------------|-----------------|------|-----------------|-------------------|

| DC SPECIFICATIONS                  |                                                 |                                                           | *               | •    |                 | *                 |

| V <sub>OS</sub>                    | Input Offset Voltage                            |                                                           | -2.5            | -0.2 | 2.5             | μV                |

|                                    |                                                 | $T_A = -40 ^{\circ}\text{C to} + 85 ^{\circ}\text{C}$     | -3.4            | -    | 3.4             | μV                |

|                                    |                                                 | $T_A = -40$ °C to +125 °C                                 | -4              | -    | 4               | μV                |

| TCV <sub>OS</sub>                  | Input Offset Voltage Temperature<br>Coefficient | T <sub>A</sub> = -40°C to +125°C                          | -15             | -0.5 | 15              | nV/°C             |

| IB                                 | Input Bias Current                              |                                                           | -300            | ±120 | 300             | pА                |

|                                    |                                                 | $T_A = -40 ^{\circ}\text{C to} + 85 ^{\circ}\text{C}$     | -300            | -    | 300             | pA                |

|                                    |                                                 | $T_A = -40$ °C to +125 °C                                 | -550            | -    | 550             | рА                |

| TCIB                               | Input Bias Current Temperature                  | $T_A = -40 ^{\circ}\text{C to} + 85 ^{\circ}\text{C}$     | -               | ±1.4 | -               | pA/°C             |

|                                    | Coefficient                                     | $T_A = -40 ^{\circ}\text{C to} + 125 ^{\circ}\text{C}$    | -               | ±2   | -               | pA/°C             |

| I <sub>OS</sub>                    | Input Offset Current                            |                                                           | -600            | ±240 | 600             | pА                |

|                                    |                                                 | $T_A = -40$ °C to +85 °C                                  | -600            | -    | 600             | pA                |

|                                    |                                                 | $T_A = -40 ^{\circ}\text{C to} + 125 ^{\circ}\text{C}$    | -750            | -    | 750             | pA                |

| TCI <sub>OS</sub>                  | Input Offset Current Temperature<br>Coefficient | $T_A = -40$ °C to +85 °C                                  | -               | ±2.8 | -               | pA/°C             |

|                                    |                                                 | $T_A = -40 ^{\circ}\text{C to} + 125 ^{\circ}\text{C}$    | -               | ±4   | -               | pA/°C             |

| Common Mode Input<br>Voltage Range |                                                 | V+ = 2.5V, V- = 0V<br>Guaranteed by CMRR                  | -0.1            | -    | 2.6             | V                 |

| CMRR                               | Common Mode Rejection Ratio                     | V <sub>CM</sub> = -0.1V to 2.6V                           | 120             | 135  | -               | dB                |

|                                    |                                                 | V <sub>CM</sub> = -0.1V to 2.6V                           | 115             | -    | -               | dB                |

| Is                                 | Supply Current per Amplifier                    | R <sub>L</sub> = OPEN                                     | -               | 715  | 940             | μΑ                |

|                                    |                                                 | $R_L = OPEN$<br>$T_A = -40$ °C to +85 °C                  | -               | -    | 1115            | μА                |

|                                    |                                                 | R <sub>L</sub> = OPEN<br>T <sub>A</sub> = -40°C to +125°C | -               | -    | 1190            | μА                |

| I <sub>SC</sub>                    | Short Circuit Output Source Current             | R <sub>L</sub> = Short to Ground                          | -               | 65   | -               | mA                |

|                                    | Short Circuit Output Sink Current               | R <sub>L</sub> = Short to V+                              | -               | -65  | -               | mA                |

| v <sub>oh</sub>                    | Output Voltage Swing, HIGH                      | $R_L = 10k\Omega$ to $V_{CM}$                             | 15              | 10   | -               | mV                |

|                                    | From V <sub>OUT</sub> to V <sub>+</sub>         | $R_L = 10k\Omega$ to $V_{CM}$                             | 15              | -    | -               | mV                |

| V <sub>OL</sub>                    | Output Voltage Swing, LOW                       | $R_L = 10k\Omega$ to $V_{CM}$                             | -               | 10   | 15              | mV                |

|                                    | From V <sub>-</sub> to V <sub>OUT</sub>         | $R_L = 10k\Omega$ to $V_{CM}$                             | -               | -    | 15              | mV                |

| AC SPECIFICATIONS                  |                                                 |                                                           |                 |      |                 |                   |

| C <sub>IN</sub>                    | Input Capacitance                               | Differential                                              | -               | 5.2  | -               | pF                |

|                                    |                                                 | Common Mode                                               | -               | 5.6  | -               | pF                |

| e <sub>N</sub>                     | Input Noise Voltage                             | f = 0.1Hz to 10Hz                                         | -               | 250  | 400             | nV <sub>P-P</sub> |

|                                    | input tolor votage                              | f = 10Hz                                                  | -               | 8    | -               | nV/√Hz            |

|                                    |                                                 | f = 1kHz                                                  | -               | 10   | -               | nV/√Hz            |

| I <sub>N</sub>                     | Input Noise Current                             | f = 1kHz                                                  | -               | 200  | -               | fA/√Hz            |

| GBWP                               | Gain Bandwidth Product                          |                                                           | _               | 3.5  | _               | MHz               |

# **Electrical Specifications** $V_S = 2.5V$ , $V_{CM} = 1.25V$ , $T_A = +25$ °C, unless otherwise specified. Boldface limits apply over the specified operating temperature range. (Continued)

| PARAMETER                                      | DESCRIPTION                                                         | TEST CONDITIONS                                                    | MIN<br>(Note 7) | TYP  | MAX<br>(Note 7) | UNITS |

|------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|------|-----------------|-------|

| TRANSIENT RESPON                               | ISE                                                                 |                                                                    |                 |      |                 |       |

| SR                                             | Positive Slew Rate                                                  | V+ = 2.5V, V- = 0V, V <sub>OUT</sub> = 0.25V to 2.25V,             | -               | 1.5  | -               | V/µs  |

|                                                | Negative Slew Rate                                                  | $R_L = 100k\Omega, C_L = 3.7pF$                                    | -               | 1.0  | -               | V/µs  |

| t <sub>r</sub> , t <sub>f</sub> , Small Signal | Rise Time, t <sub>r</sub> 10% to 90%                                | V+ = 2.5V, V- = 0V, V <sub>OUT</sub> = 0.1V <sub>P-P</sub> ,       | -               | 0.07 | -               | μs    |

|                                                | Fall Time, t <sub>f</sub> 10% to 90%                                | $R_F = 0\Omega$ , $R_L = 100k\Omega$ , $C_L = 3.7pF$               | -               | 0.17 | -               | μs    |

| t <sub>r</sub> , t <sub>f</sub> Large Signal   | Rise Time, t <sub>r</sub> 10% to 90%                                | $V+ = 2.5V$ , $V- = 0V$ , $V_{OUT} = 2V_{P-P}$ , $R_F = 0\Omega$ , | -               | 1.3  | -               | μs    |

|                                                | Fall Time, t <sub>f</sub> 10% to 90%                                | $R_L = 100k\Omega, C_L = 3.7pF$                                    | -               | 2.0  | -               | μs    |

| t <sub>s</sub>                                 | Settling Time to 0.1%, 2V <sub>P-P</sub> Step                       | $A_V = -1$ , $R_F = 1k\Omega$ , $C_L = 3.7pF$                      | -               | 100  | -               | μs    |

| t <sub>recover</sub>                           | Output Overload Recovery Time, Recovery to 90% of Output Saturation | $A_V = +2$ , $R_F = 10k\Omega$ , $R_L = 100k$ , $C_L = 3.7pF$      | -               | 1.5  | -               | μs    |

#### NOTE:

## Typical Performance Curves $T_A = +25$ °C, $V_{CM} = 0$ V Unless otherwise specified.

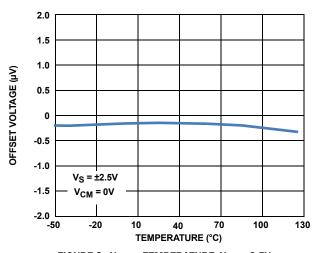

FIGURE 3.  $V_{OS}$  vs TEMPERATURE,  $V_S = \pm 2.5V$

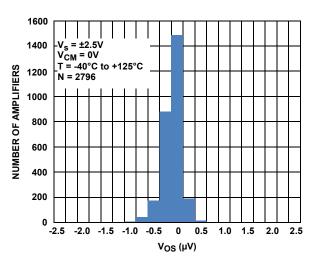

FIGURE 5.  $V_{OS}$  HISTOGRAM  $V_S = 5V$

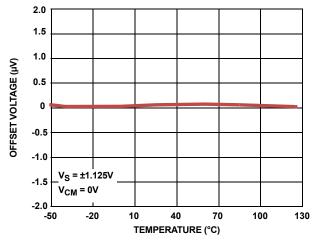

FIGURE 4.  $V_{OS}$  vs TEMPERATURE,  $V_S = \pm 1.125V$

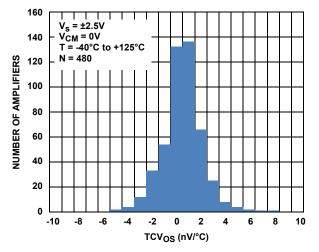

FIGURE 6. TCV<sub>OS</sub> HISTOGRAM V<sub>S</sub> = 5V

<sup>7.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## Typical Performance Curves $T_A = +25 \,^{\circ}$ C, $V_{CM} = 0$ V Unless otherwise specified. (Continued)

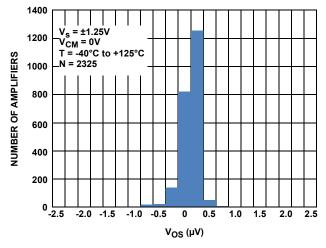

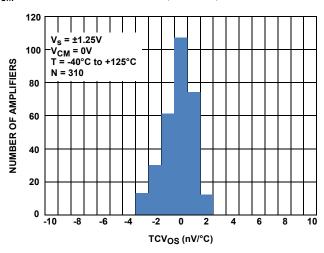

FIGURE 7.  $V_{OS}$  HISTOGRAM  $V_S = 2.5V$

FIGURE 8.  $TCV_{OS}$  HISTOGRAM  $V_S = 2.5V$

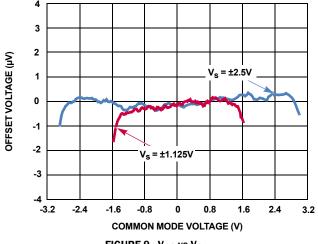

FIGURE 9. V<sub>OS</sub> vs V<sub>CM</sub>

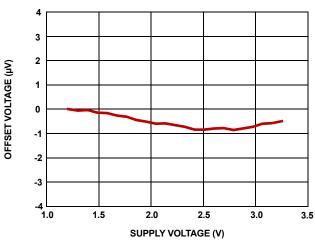

FIGURE 10. V<sub>OS</sub> vs SUPPLY VOLTAGE

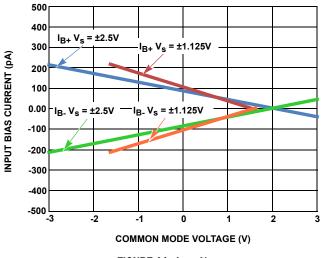

FIGURE 11. IB vs VCM

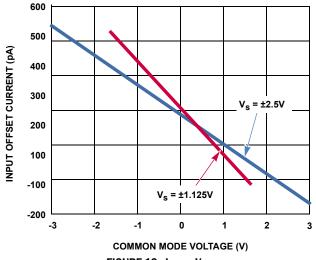

FIGURE 12.  $I_{OS}$  vs  $V_{CM}$

# Typical Performance Curves T<sub>A</sub> = +25 °C, V<sub>CM</sub> = 0V Unless otherwise specified. (Continued)

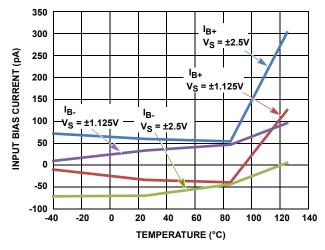

FIGURE 13. IB vs TEMPERATURE

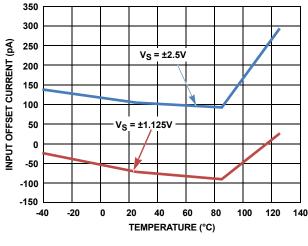

FIGURE 14. I<sub>OS</sub> vs TEMPERATURE

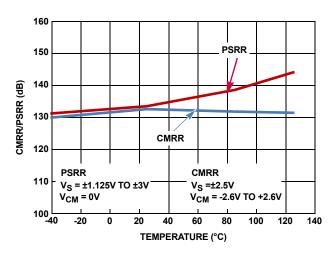

FIGURE 15. CMRR and PSRR vs TEMPERATURE

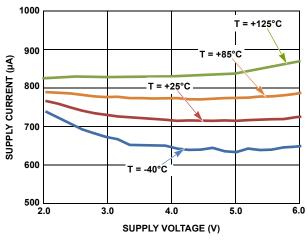

FIGURE 16. SUPPLY CURRENT vs SUPPLY VOLTAGE

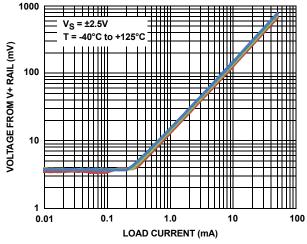

FIGURE 17. OUTPUT HIGH OVERHEAD VOLTAGE vs LOAD CURRENT

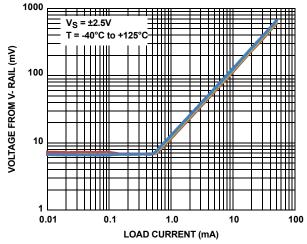

FIGURE 18. OUTPUT LOW OVERHEAD VOLTAGE vs LOAD CURRENT

# **Typical Performance Curves** $T_A = +25 \,^{\circ}\text{C}$ , $V_{CM} = 0V$ Unless otherwise specified. (**Continued**)

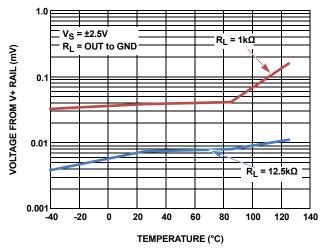

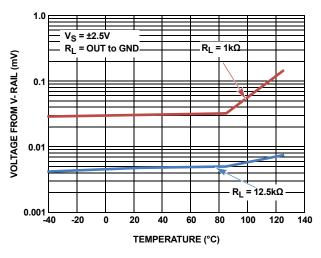

FIGURE 19. V<sub>OH</sub> vs TEMPERATURE

FIGURE 20. V<sub>OL</sub> vs TEMPERATURE

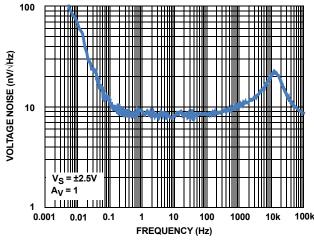

FIGURE 21. INPUT NOISE VOLTAGE DENSITY vs FREQUENCY

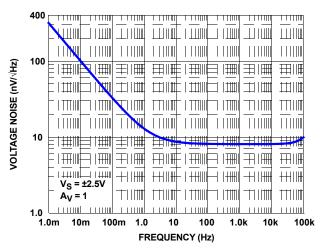

FIGURE 22. INPUT NOISE VOLTAGE 0.1Hz TO 10Hz

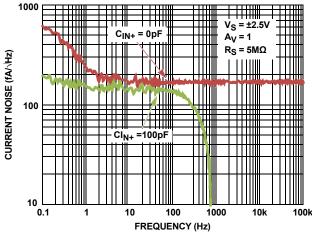

FIGURE 23. INPUT NOISE CURRENT DENSITY vs FREQUENCY

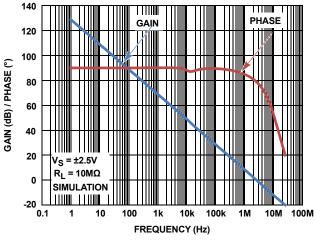

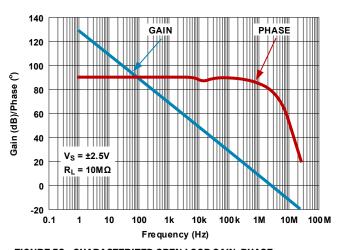

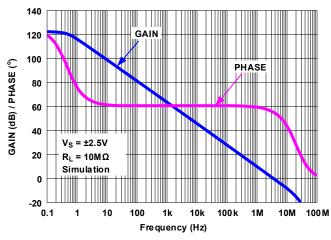

FIGURE 24. OPEN LOOP GAIN AND PHASE,  $R_L = 10M$

## Typical Performance Curves $\tau_A = +25 \,^{\circ} \, \text{C}$ , $V_{\text{CM}} = 0 \,^{\circ} \, \text{Unless otherwise specified.}$ (Continued)

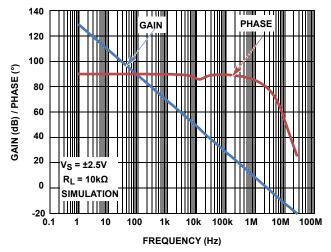

FIGURE 25. OPEN LOOP GAIN AND PHASE,  $R_L = 10k$

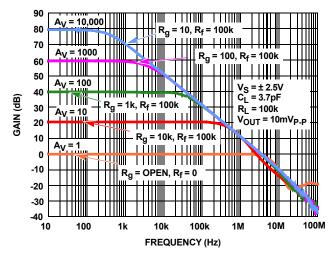

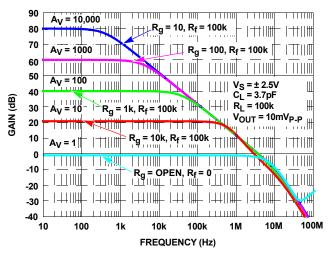

FIGURE 26. FREQUENCY RESPONSE vs CLOSED LOOP GAIN

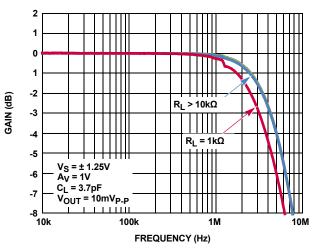

FIGURE 27. GAIN vs FREQUENCY vs  $R_{L_1} V_S = 2.5V$

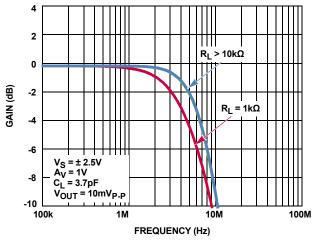

FIGURE 28. GAIN vs FREQUENCY vs  $R_{L_1} V_S = 5.0V$

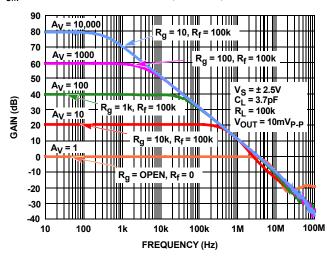

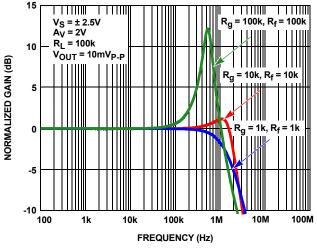

FIGURE 29. GAIN vs FREQUENCY vs FEEDBACK RESISTOR VALUES  $R_{f}/R_{g}$

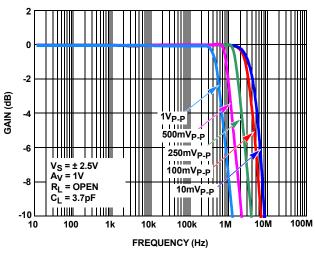

FIGURE 30. GAIN vs FREQUENCY vs Vout

## Typical Performance Curves $T_A = +25 \,^{\circ} \, C$ , $V_{CM} = 0 \,^{\circ} \, U$ Unless otherwise specified. (Continued)

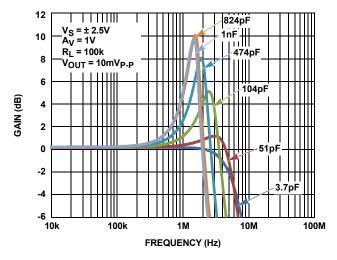

FIGURE 31. GAIN vs FREQUENCY vs CL

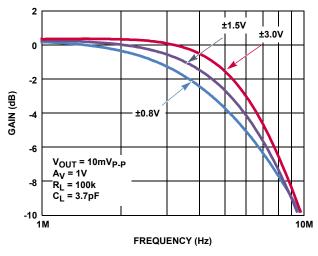

FIGURE 32. GAIN vs FREQUENCY vs SUPPLY VOLTAGE

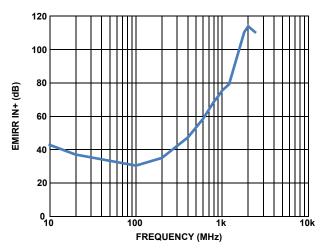

FIGURE 33. EMIRR AT IN+ PIN vs FREQUENCY

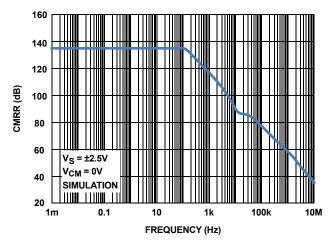

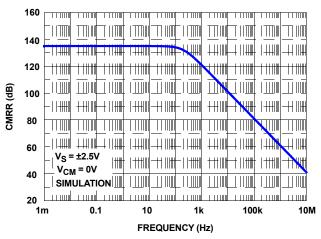

FIGURE 34. CMRR vs FREQUENCY,  $V_S = 5V$

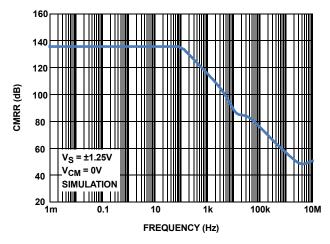

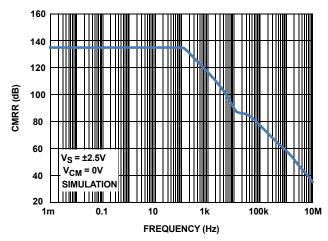

FIGURE 35. CMRR vs FREQUENCY, V<sub>S</sub> = 2.5V

# Typical Performance Curves T<sub>A</sub> = +25 °C, V<sub>CM</sub> = 0V Unless otherwise specified. (Continued)

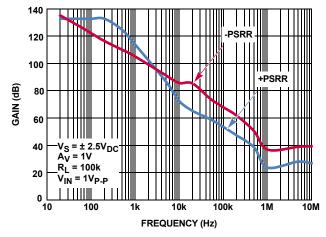

FIGURE 36. PSRR vs FREQUENCY,  $V_S = 5V$

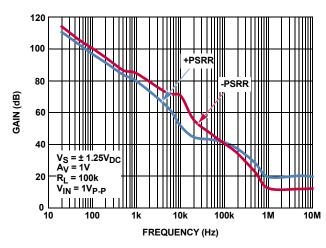

FIGURE 37. PSRR vs FREQUENCY, V<sub>S</sub> = 2.5V

FIGURE 38. NO PHASE INVERSION

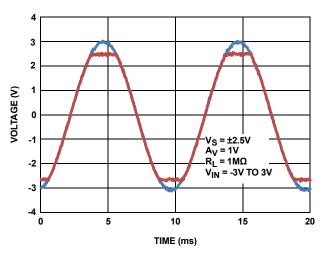

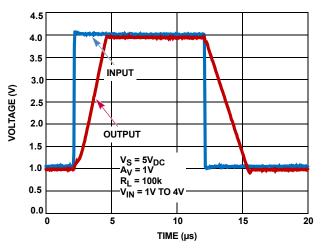

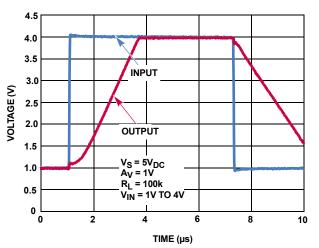

FIGURE 39. LARGE SIGNAL STEP RESPONSE (3V)

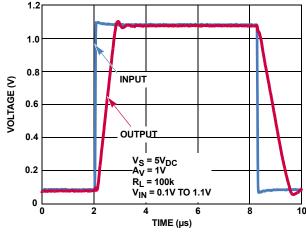

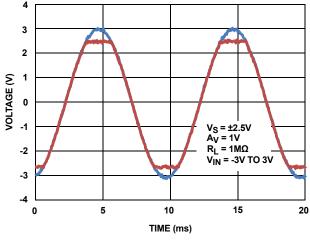

FIGURE 40. LARGE SIGNAL STEP RESPONSE (1V)

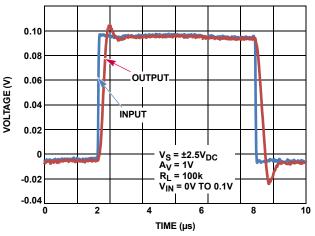

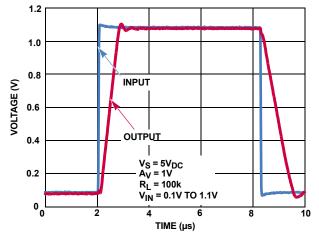

FIGURE 41. SMALL SIGNAL STEP RESPONSE (100mV)

## Typical Performance Curves $T_A = +25 \,^{\circ} \, \text{C}$ , $V_{CM} = 0 \,^{\circ} \, \text{Unless otherwise specified.}$ (Continued)

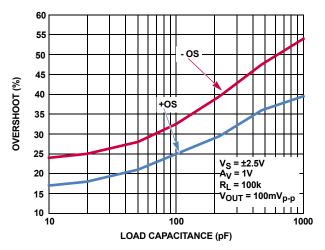

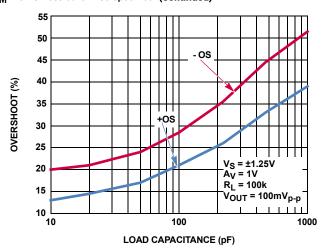

FIGURE 42. SMALL SIGNAL OVERSHOOT vs LOAD CAPACITANCE,  $VS = \pm 2.5V$

## **Applications Information**

### **Functional Description**

The ISL28134 is a single 5V rail-to-rail input/output amplifier that operates on a single or dual supply. The ISL28134 uses a proprietary auto-zeroing technique that combines a 3.5MHz main amplifier with a very high open loop gain (174dB) offset-nulling amplifier to achieve very low offset voltage and drift (0.2µV, 0.5nV/°C) while having a low supply current (675µA). The very low 1/f noise corner <0.1Hz and low input noise voltage (8nV/ $\sqrt{\text{Hz}}$  at 100Hz) of the amplifier makes it ideal for low frequency precision applications requiring very high gain and low noise.

This multi-path amplifier architecture contains a time continuous main amplifier whose input DC offset is corrected by a parallel-connected, high gain offset-nulling DC correction amplifier operating at 100kHz. From DC to ~10kHz, both amplifiers are active with the DC offset correction active with most of the low frequency gain provided by the nulling amplifier. A 10kHz crossover filter cuts off the low frequency nulling amplifier path leaving the main amplifier active out to the -3dB frequency (3.5MHz GBWP).

The key benefits of this architecture for precision applications are rail-to-rail inputs/outputs, high open loop gain, low DC offset and temperature drift, low 1/f noise corner and low input noise voltage. The noise is virtually flat across the frequency range from a few MHz out to 100kHz, except for the narrow noise peak at the amplifier crossover frequency (10kHz).

#### **Power Supply Considerations**

The ISL28134 features a wide supply voltage operating range. The ISL28134 operates on single (+2.25V to +6.0V) or dual (±1.125 to ±3.0V) supplies. Power supply voltages greater than the +6.5V absolute maximum (specified in the "Absolute Maximum Ratings" on page 4) can permanently damage the device. Performance of the device is optimized for supply voltages greater than 2.5V. This makes the ISL28134 ideal for portable 3V battery applications that require the precision performance. It is highly recommended that a

FIGURE 43. SMALL SIGNAL OVERSHOOT vs LOAD CAPACITANCE,  $V_S = \pm 1.25 V$

$0.01\mu F$  or larger high frequency decoupling capacitor is placed across the power supply pins of the IC to maintain high performance of the amplifier.

### Rail-to-rail Input and Output (RRIO)

Unlike some amplifiers whose inputs may not be taken to the power supply rails or whose outputs may not drive to the supply rails, the ISL28134 features rail-to-rail inputs and outputs. This allows the amplifier inputs to have a wide common mode range (100mV beyond supply rails) while maintaining high CMRR (135dB) and maximizes the signal to noise ratio of the amplifier by having the  $V_{OH}$  and  $V_{OL}$  levels be at the V+ and V- rails, respectively.

#### **Low Input Voltage Noise Performance**

In precision applications, the input noise of the front end amplifier is a critical parameter. Combined with a high DC gain to amplify the small input signal, the input noise voltage will result in an output error in the amplifier. A  $1\mu V_{P.P}$  input noise voltage with an amplifier gain of 10,000V/V will result in an output offset in the range of 10mV, which can be an unacceptable error source. With only  $250\text{nV}_{P.P}$  at the input, along with a flat noise response down to 0.1Hz, the ISL28134 can amplify small input signals with minimal output error.

The ISL28134 has the lowest input noise voltage compared to other competitor's Auto-Zero amplifiers with similar supply currents (see Table 1). The overall input referred voltage noise of an amplifier can be expressed as a sum of the input noise voltage, input noise current of the amplifier and the Johnson noise of the gain-setting resistors used. The product of the input noise current and external feedback resistors along with the Johnson noise, increases the total output voltage noise as the value of the resistance goes up. For optimizing noise performance, choose lower value feedback resistors to minimize the effect of input noise current. Although the ISL28134 features a very low  $200f\text{A}/\sqrt{\text{Hz}}$  input noise current, at source impedances  $>100k\Omega$ , the input referred noise voltage will be dominated by the input current noise. Keep source input impedances under  $10k\Omega$  for optimum performance.

| <br>_ | _ |  |

|-------|---|--|

|       |   |  |

|       |   |  |

| PART         | VOLTAGE NOISE AT<br>100Hz | 0.1Hz TO 10Hz PEAK-TO-PEAK<br>VOLTAGE NOISE |

|--------------|---------------------------|---------------------------------------------|

| Competitor A | 22nV/√Hz                  | 600nV <sub>P-P</sub>                        |

| Competitor B | 16nV/√Hz                  | 260nV <sub>P-P</sub>                        |

| Competitor C | 90nV/√Hz                  | 1500nV <sub>P-P</sub>                       |

| ISL28134     | 8nV/√Hz                   | 250nV <sub>P-P</sub>                        |

#### **High Source Impedance Applications**

The input stage of auto-zero amplifiers do not behave like conventional amplifier input stages. The ISL28134 uses switches that continually sample the nulling amplifier input at 100kHz to reduce the input offset to  $1\mu V$ . The dynamic behavior of these switches induces a charge injection current to the input terminals of the amplifier. The charge injection current has a DC path to ground through the resistances seen at the input terminals of the amplifier. Higher input impedance cause an apparent shift in the input bias current of the amplifier. Input impedances larger than  $10k\Omega$  begin to have significant increases in the bias currents. To minimize the effect of impedance on input bias currents, an input resistance of  $<10k\Omega$  is recommended.

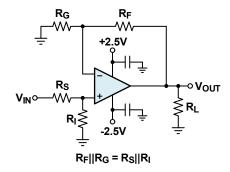

Because the nulling amplifier has charge injection currents at each terminal, the input impedance should be balanced across each input (see Figure 44). The input impedance of the amplifier should be matched between the IN+ and IN- terminals to minimize total input offset current. Input offset currents show up as an additional output offset voltage, as shown in Equation 1:

$$V_{OSTOT} = V_{OS} - R_F * I_{OS}$$

(EQ. 1)

If the offset voltage of the amplifier is negative, the input offset currents will add to the total output offset. For a 10,000V/V gain amplifier using 1M $\Omega$  feedback resistor, a 500pA total input offset current will have an additional output offset voltage of 0.5mV. By keeping the input impedance low and balanced across the amplifier inputs, the input offset current is kept below 100pA, resulting in an offset voltage 0.1mV or less.

FIGURE 44. CIRCUIT IMPLEMENTATION FOR REDUCING INPUT BIAS CURRENTS

#### IN+ and IN- Protection

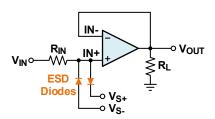

The ISL28134 is capable of driving the input terminals up to and beyond the supply rails by about 0.5V. Back biased ESD diodes from the input pins to the V+ and V- rails will conduct current when the input signals go more than 0.5V beyond the rail (see Figure 45). The ESD protection diodes must be current limited to 20mA or less to prevent damage of the IC. This current can be reduced by placing a resistor in series with the IN+ and IN- inputs in the event the input signals go beyond the rail.

FIGURE 45. INPUT CURRENT LIMITING

#### **EMI Rejection**

Electromagnetic Interference (EMI) can be a problem in high frequency applications for precision amplifiers. The op amp pins are susceptible to EMI signals which can rectify high frequency inputs beyond the amplifier bandwidth and present itself as a shift in DC offset voltage. Long trace leads to op amp pins may act as an antenna for radiated RF signals, which result in a total conductive EMI noise into the op amp inputs.

The most susceptible pin is the non-inverting IN+ input therefore, EMI rejection (EMIR) on this pin is important for RF type applications. The ability of the amplifier output to reject EMI is called EMI Rejection Ratio (EMIRR) and is computed as:

EMIRR (dB) = 20 log (

$$V_{IN}$$

PEAK/ $\Delta V_{OS}$

The test circuit for measuring the DC offset of the amplifier with an RF signal input to the IN+ pin is shown in Figure 46. The EMIRR performance of the ISL28134 at the IN+ pin across a frequency of 10MHz to 2.4GHz is plotted on Figure 33. The ISL28134 shows a typical EMIRR of 75dB at 1GHz. For better EMI immunity, a small RFI filter can be placed at the input to attenuate out of band signals and reduce DC offset shift from high frequency RF signals into the IN+ pin. For example, a  $15\Omega$  and 100pF RC filter will roll off signals above 100MHz for better EMIRR performance.

FIGURE 46. CIRCUIT TESTING EMIRR

#### **Output Phase Reversal**

The Output phase reversal is the unexpected inversion of the amplifier output signal when the inputs exceed the common mode input range. Since the ISL28134 is a rail-to-rail input amplifier, the ISL28134 is specifically designed to prevent output phase reversal within its common mode input range. In fact, the ISL28134 will not phase invert even when the input signals go 0.5V beyond the supply rails (see <a href="Figure 38">Figure 38</a>). If input signals are expected to go beyond the rails, it is highly recommended to minimize the forward biased ESD diode current to prevent phase inversion by placing a resistor in series with the input.

#### **High Gain, Precision DC-Coupled Amplifier**

Precision applications that need to amplify signals in the range of a few  $\mu V$  require gain in the order of thousands of V/V to get a good signal to the Analog to Digital Converter (ADC). This can be achieved by using a very high gain amplifier with the appropriate open loop gain and bandwidth.

In addition to the high gain and bandwidth, it is important that the amplifier have low  $V_{OS}$  and temperature drift along with a low input noise voltage. For example, an amplifier with  $100\mu V$  offset voltage and  $0.5\mu V/\,^{\circ}C$  offset drift configured in a closed loop gain of  $10,\!000V/V$  would produce an output error of 1V and a  $5mV/\,^{\circ}C$  temperature dependent error. Unless offset trimming and temperature compensation techniques are used, this error makes it difficult to resolve the input voltages needed in the precision application.

The ISL28134 features a low V<sub>OS</sub> of  $\pm 4\mu V$  max and a very stable 10nV/°C max temperature drift, which produces an output error of only  $\pm 40$ mV and a temperature error of 0.1mV/°C. With an ultra low input noise of 210nV<sub>P-P</sub> (0.1Hz to 10Hz) and no 1/f corner frequency, the ISL28134 is capable of amplifying signals in the  $\mu V$  range with high accuracy. For even further DC precision, some feedback filtering C<sub>F</sub> (see Figure 47) to reduce the noise can be implemented as a total signal stage amplifier. As a method of best practice, the ISL28134 should be impedance matched at the two input terminals. A balancing capacitor of the same value at the on-inverting terminal will result in the amplifier input impedances tracking across frequency

FIGURE 47. HIGH GAIN, PRECISION DC-COUPLED AMPLIFIER

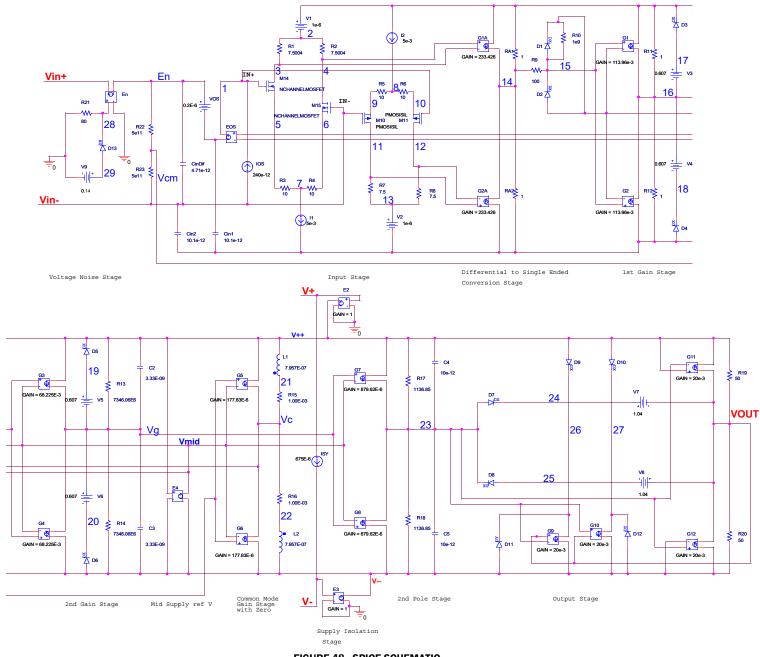

#### **ISL28134 SPICE Model**

Figure 48 shows the SPICE model schematic and Figure 49 shows the net list for the SPICE model. The model is a simplified version of the actual device and simulates important AC and DC parameters. The AC parameters incorporated into the model are: 1/f and flat band noise voltage, slew rate, CMRR, and gain and phase. The DC parameters are 1/f0, 1/f0, total supply current, output voltage swing and output current limit (65mA). The model uses typical parameters given in the "Electrical Specifications" table beginning on page 4. The AVOL is adjusted for 174dB with the dominant pole at 6.5mHz. The CMRR is set at 135dB, 1/f1 = 200Hz. The input stage models the actual device to present an accurate AC representation. The model is configured for an ambient temperature of +25°C.

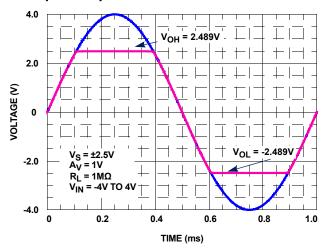

<u>Figures 50</u> through <u>63</u> show the characterization vs simulation results for the noise voltage, open loop gain phase, closed loop gain vs frequency, CMRR, large signal 3V step response, large signal 1V step response, and output voltage swing  $V_{OH}/V_{OL}$  ±2.5V supplies (no phase inversion).

#### LICENSE STATEMENT

The information in the SPICE model is protected under United States copyright laws. Renesas Corporation hereby grants users of this macro-model, hereto referred to as "Licensee", a nonexclusive, nontransferable license to use this model, as long as the Licensee abides by the terms of this agreement. Before using this Macro-Model, the Licensee should read this license. If the Licensee does not accept these terms, permission to use the model is not granted.

The Licensee may not sell, loan, rent, or license the macro-model, in whole, in part, or in modified form, to anyone outside the Licensee's company. The Licensee may modify the Macro-Model to suit his/her specific applications, and the Licensee may make copies of this Macro-Model for use within their company only.

This Macro-Model is provided "AS IS, WHERE IS, AND WITH NO WARRANTY OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE."

In no event will Renesas be liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of this Macro-Model. Renesas reserves the right to make changes to the product and the Macro-Model without prior notice.

FIGURE 48. SPICE SCHEMATIC

| *ISL28134 Macromodel                                                                  | *                               | G_G6 V VC VCM VMID 177.83E-6            |

|---------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------|

| *                                                                                     | *Input Stage                    | E EOS 1 30 VC VMID 1                    |

| *Revision History:                                                                    | M M10 11 VIN- 9 9 PMOSISIL      | R_R15 VC 21 1.00E-03                    |

| * Revision A, LaFontaine June 17th 2011                                               |                                 | R_R16 22 VC 1.00E-03                    |

| * Model for Noise, quiescent supply currents,                                         | M M14 3 1 5 5 NCHANNELMOSFET    | R_R22 EN VCM 5e11                       |

| *CMRR135dB f = 200Hz, AVOL 174dB f =                                                  | M M15 4 VIN- 6 6 NCHANNELMOSFET | R R23 VCM VIN- 5e11                     |

| *6.5mHz, SR = 1.5V/us, GBWP 3.5MHz.                                                   |                                 | _<br>L_L1                               |

| *Copyright 2011 by Intersil Corporation                                               | I I2 V++ 8 DC 5e-3              | L_L2 22 V 7.957E-07                     |

| *Refer to data sheet "LICENSE STATEMENT"                                              | I IOS VIN- 1 DC 240e-12         | *                                       |

| *Use of this model indicates your acceptance                                          | G G1A V++ 14 4 3 233.4267       | *2nd Pole Stage                         |

| *with the terms and provisions in the License                                         | G_G2A V 14 11 12 233.4267       | G_G7 V++ 23 VG VMID 879.62E-6           |

| *Statement.                                                                           | V V1 V++ 2 1e-6                 | G G8 V 23 VG VMID 879.62E-6             |

| *                                                                                     | V V2 13 V 1e-6                  | R R17 23 V++ 1136.85                    |

| *Intended use:                                                                        | V_VOS EN 30 0.2E-6              | R_R18 V 23 1136.85                      |

| *This Pspice Macromodel is intended to give                                           | R_R1 3 2 7.5004                 | C C4 23 V++ 10e-12                      |

| *typical DC and AC performance                                                        | R R2 4 2 7.5004                 | C_C5 V 23 10e-12                        |

| *characteristics under a wide range of                                                | R_R3 5 7 10                     | *                                       |

| *external circuit configurations using<br>*compatible simulation platforms – such as  | R R4 76 10                      | *Output Stage                           |

| *iSim PE.                                                                             | <del>-</del>                    | . •                                     |

| *                                                                                     | R_R5 98 10                      |                                         |

| *Device performance features supported by                                             | R_R6 8 10 10                    | G_G10 27 V 23 VOUT 20e-3                |

| *this model:                                                                          | R_R7 13 11 7.5                  | G_G11 VOUT V++ V++ 23 20e-3             |

| *Typical, room temp., nominal power supply                                            | R_R8 13 12 7.5                  | G_G12 V VOUT 23 V 20e-3                 |

| *voltages used to produce the following                                               | R_RA1 14 V++ 1                  | V_V7 24 VOUT 1.04                       |

| *characteristics:                                                                     | R_RA2 V 14 1                    | V_V8 VOUT 25 1.04                       |

| *Open and closed loop I/O impedances,                                                 | C_CinDif VIN- EN 4.71e-12       | D_D7 23 24 DX                           |

| *Open loop gain and phase,                                                            | C_Cin1 V 30 10.1e-12            | D_D8 25 23 DX                           |

| *Closed loop bandwidth and frequency                                                  | C_Cin2 V VIN- 10.1e-12          | D_D9 V++ 26 DX                          |

| *response,                                                                            | *                               | D_D10 V++ 27 DX                         |

| *Loading effects on closed loop frequency                                             | *1st Gain Stage                 | D_D11 V 26 DY                           |

| ,                                                                                     | G_G1 V++ 16 15 VMID 113.96e-3   | D_D12 V 27 DY                           |

| *response,                                                                            | G_G2 V 16 15 VMID 113.96e-3     | R_R19 VOUT V++ 50                       |

| *Input noise terms including 1/f effects,                                             | V_V3 17 16 0.607                | R_R20 V VOUT 50                         |

| *Slew rate, Input and Output Headroom limits *to I/O voltage swing, Supply current at | V_V4 16 18 0.607                | *                                       |

| *nominal specified supply voltages,                                                   | D_D1 15 VMID DX                 | .model pmosisil pmos (kp=16e-3 vto=-0.6 |

| *Output current limiting (65mA)                                                       | D_D2 VMID 15 DX                 | +kf=0 af=1)                             |

| *                                                                                     | D_D3                            | .model NCHANNELMOSFET nmos (kp=3e-3     |

| *Device performance features NOT                                                      | D D4 V 18 DX                    | +vto=0.6 kf=0 af=1)                     |

| *supported by this model:                                                             | R_R9                            | .model DN D(KF=6.69e-9 af=1)            |

| *Harmonic distortion effects,                                                         | R_R10                           | .MODEL DX D(IS=1E-12 Rs=0.1 kf=0 af=1)  |

| *Disable operation (if any),                                                          |                                 | .MODEL DY D(IS=1E-15 BV=50 Rs=1 kf=0    |

| *Thermal effects and/or over temperature                                              | R R12 V 16 1                    | +af=1)                                  |

| *parameter variation,                                                                 | *                               | .ends ISL28134                          |

| *Performance variation vs. supply voltage,                                            | *2nd Gain Stage                 |                                         |

| *Part to part performance variation due to                                            | G_G3 V++ VG 16 VMID 68.225E-3   |                                         |

| *normal process parameter spread,                                                     | G G4 V VG 16 VMID 68.225E-3     |                                         |

| *Any performance difference arising from                                              | V V5 19 VG 0.607                |                                         |

| , .                                                                                   | V_V6 VG 20 0.607                |                                         |

| *different packaging,                                                                 | D_D5 19 V++ DX                  |                                         |

| *Load current reflected into the power supply                                         | D D6 V 20 DX                    |                                         |

| *current.                                                                             | R_R13 VG V++ 7346.06E6          |                                         |

| * source ISL28134                                                                     | R_R14 V VG 7346.06E6            |                                         |

| * Connections: ±input                                                                 | C_C2 VG V++ 3.33E-09            |                                         |

| * Connections: +input                                                                 |                                 |                                         |

| *                                                                                     | C_C3 V VG 3.33E-09              |                                         |

| *     -Vsupply                                                                        | *Mid cupply Pof                 |                                         |

| *       output                                                                        | *Mid supply Ref                 |                                         |

| *                                                                                     | E_E4 VMID V V++ V 0.5           |                                         |

| .subckt ISL28134 Vin+ Vin- V+ V- VOUT                                                 | *Cupply loolation Ctare         |                                         |

| *                                                                                     | *Supply Isolation Stage         |                                         |

| *Voltage Noise                                                                        | E_E2 V++ 0 V+ 0 1               |                                         |

| E En VIN+ EN 28 0 1                                                                   | E_E3 V 0 V- 0 1                 |                                         |

| D D13 29 28 DN                                                                        | I_ISY V+ V- DC 675E-6           |                                         |

| V_V9 29 0 0.14                                                                        | *                               |                                         |

| V_V9 29 0 0.14<br>R R21 28 0 80                                                       | *Common Mode Gain Stage         |                                         |

| 11.21 20 0 00                                                                         | G_G5 V++ VC VCM VMID 177.83E-6  |                                         |

|                                                                                       |                                 |                                         |

FIGURE 49. SPICE NET LIST

### **Characterization vs Simulation Results**

FIGURE 50. CHARACTERIZED INPUT NOISE VOLTAGE

FIGURE 51. SIMULATED INPUT NOISE VOLTAGE

FIGURE 52. CHARACTERIZED OPEN-LOOP GAIN, PHASE vs FREQUENCY

FIGURE 53. SIMULATED OPEN-LOOP GAIN, PHASE vs FREQUENCY

FIGURE 54. CHARACTERIZED CLOSED-LOOP GAIN vs FREQUENCY

FIGURE 55. SIMULATED CLOSED-LOOP GAIN vs FREQUENCY

### **Characterization vs Simulation Results (Continued)**

FIGURE 56. CHARACTERIZED CMRR vs FREQUENCY

FIGURE 58. CHARACTERIZED LARGE SIGNAL STEP RESPONSE (3V)

FIGURE 60. CHARACTERIZED SMALL-SIGNAL TRANSIENT RESPONSE

FIGURE 57. SIMULATED CMRR vs FREQUENCY

FIGURE 59. SIMULATED LARGE SIGNAL STEP RESPONSE (3V)

FIGURE 61. SIMULATED SMALL-SIGNAL TRANSIENT RESPONSE

## **Characterization vs Simulation Results** (Continued)

FIGURE 62. CHARACTERIZED NO PHASE INVERSION

FIGURE 63. SIMULATED NO PHASE INVERSION, VOH AND VOL

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oct 27, 2022 | 6.03     | Updated Figures 52 and 53.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Feb 22, 2022 | 6.02     | Removed Related Literature section. Updated the Ordering Information table formatting. Corrected error in EC tables for $V_{OS}$ (-40C to 125C) in the MAX column changed from -4uV to +4uV and moved $V_{OS}$ and TCV <sub>OS</sub> specs from the bottom of the first EC table ( $V_S$ = 5V) to the top of the 2nd EC table ( $V_S$ = 2.5V).                                                                                                                                                               |

| Mar 12, 2020 | 6.01     | Updated Title Updated links throughout. Updated Related Literature. Updated Figures 1, 44, 45, 46, and 47. Updated Pin Configuration diagrams and circuits in Pin Description table. Updated Functional Description and High Source Impedance Applications sections. Removed About Intersil section. Updated disclaimer.                                                                                                                                                                                     |

| Oct 14, 2014 | 6.00     | Figure 44 updated from: $R_s//R_g = R_S//R_g$ to: $R_F//R_i = R_S//R_g$ . Removed part numbers ISL28134FRUZ-T7 and ISL28134FBZ from ordering information table. Removed 6 LD UTDFN throughout the document. Removed pod L6.1.6x1.6.                                                                                                                                                                                                                                                                          |

| Jul 3, 2013  | 5.00     | Updated the figure 1 on page 1, and changed title from "PRECISION 10-BIT WEIGH SCALE/STRAIN GAUGE" to "PRECISION WEIGH SCALE / STRAIN GAUGE".  Updated Figure 21: "Input noise voltage density vs frequency" on page 10.  Added typical EMIRR spec to Electrical Spec table under section "AC SPECIFICATIONS" on page 5.  Added applications paragraph to "EMI Rejection" on page 15.  Added 2 Figures, 33 and 46, describing the test circuit and typical performance graph for "EMI Rejection" on page 15. |

| Aug 3, 2012  | 4.00     | Made correction to Figure 1 on page 1 by changing resistor label from "1M $\Omega$ " to "20k $\Omega$ ".                                                                                                                                                                                                                                                                                                                                                                                                     |

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision. (Continued)

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dec 12, 2011 | 3.00     | Updated front page introduction to reflect +125°C grade and SOT-23 package release.  Updated Figure 1 with newer relevant Apps Circuit  Updated Figure 2 with extended temp range -40°C to 125°C  Updated "Operating Conditions" on page 3 by removing "Coming Soon" from ISL28134FHZ SOT-23 package  Updated "Operating Conditions" on page 4 to include Full Industrial Grade Package.  Updated "Electrical Specifications" Tables for both Vs = 5V and Vs = 2.5V (page 4 to page 7) as follows:  Modified common conditions at top of tables from "Boldface limits apply over the operating temperature range, -40°C to +85°C." to "Boldface limits apply over the specified operating temperature range Added MIN/MAX vos spec from -40°C to 125°C: ±4µV  Updated Conditions cell for TCVos from +85°C to +125°C. No limit change.  Added MIN/MAX bias spec from -40°C to 125°C: ±550pA  Added Typ TClois spec from -40°C to 125°C: ±2pA/C  Added MIN/MAX los spec from -40°C to 125°C: ±750pA  Added Typ TClos spec from TA = -40°C to +125°C: ±4pA/C  Updated Conditions cell for Common Mode Input Voltage Range Spec (removed T <sub>A</sub> = -40°C to +85°C). No limit change.  Updated Conditions cell for CRRR for over temp (bolded) specs (removed T <sub>A</sub> = -40°C to +85°C). No limit change  Updated Conditions cell for VSRR for over temp (bolded) specs (removed T <sub>A</sub> = -40°C to +85°C). No limit change  Added MAX Is spec from -40°C to 125°C: ±150pA  Updated Conditions cell for VOI for over temp (bolded) specs (removed T <sub>A</sub> = -40°C to +85°C). No limit change.  Added MAX Is spec from -40°C to 125°C: ±150pA  Updated Conditions cell for VOI for over temp (bolded) specs (removed T <sub>A</sub> = -40°C to +85°C). No limit change.  Added Max Is spec from -40°C to 125°C: ±150pA  Updated Conditions cell for VOI for over temp (bolded) specs (removed T <sub>A</sub> = -40°C to +85°C). No limit change.  Added Max Is spec from -40°C to 125°C: ±150pA  Updated Conditions cell for VOI for over temp (bolded) specs (removed T <sub>A</sub> = -40°C to +85°C). No limit change.  Added Mix Is spec from -40°C to +85°C). No limit c |

| Jul 6, 2011  | 2.00     | .ends ISL28134"  Added Evaluation board to "Ordering Information" on page 3.  Updated "INPUT NOISE VOLTAGE DENSITY vs FREQUENCY" on page 10 (Changed MIN frequency from 100ml to 1mHz)  Updated "LARGE SIGNAL STEP RESPONSE (3V)" on page 13 by changing the Time from 0 to 10 to 0 to 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              |          | Added "ISL28134 SPICE Model" section, which includes Schematic, Macromodel and Characterization vs Simulation Results.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

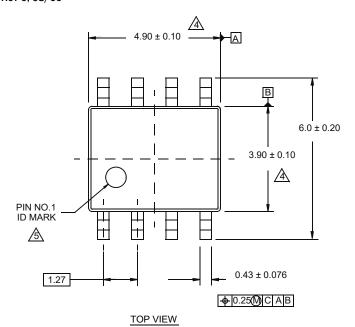

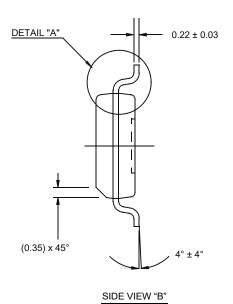

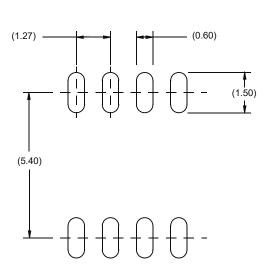

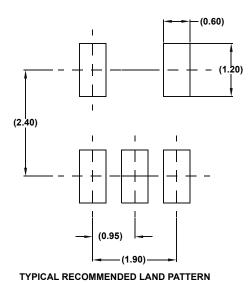

## **Package Outline Drawings**

For the most recent package outline drawing, see M8.15E.

M8.15E

8 Lead Narrow Body Small Outline Plastic Package Rev 0,08/09

0.175 ± 0.075

SIDE VIEW "A

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension does not include interlead flash or protrusions.

Interlead flash or protrusions shall not exceed 0.25mm per side.

- 5. The pin #1 identifier may be either a mold or mark feature.

- 6. Reference to JEDEC MS-012.

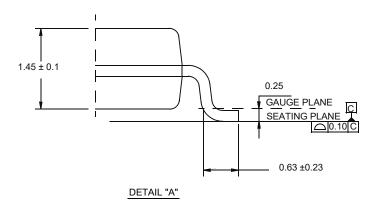

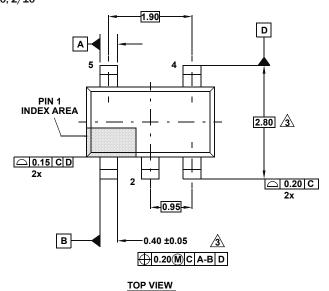

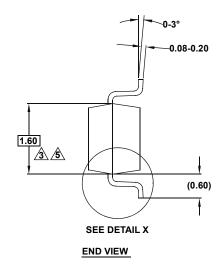

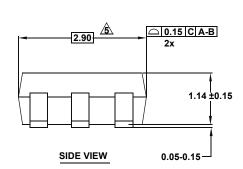

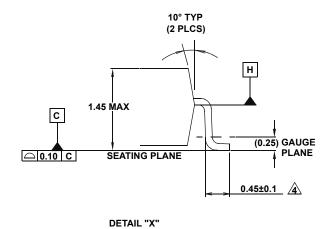

#### For the most recent package outline drawing, see P5.064A.

#### P5.064A 5 Lead Small Outline Transistor Plastic Package Rev 0, 2/10

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 3 Dimension is exclusive of mold flash, protrusions or gate burrs.

- 4. Foot length is measured at reference to guage plane.

- 5. This dimension is measured at Datum "H".

- 6. Package conforms to JEDEC MO-178AA.

#### **IMPORTANT NOTICE AND DISCLAIMER**