INTEGRATED 10/100/1000 GIGABIT ETHERNET TRANSCEIVER

**REV V1.09**

# Revision History

| Revision | Release Date | Summary                                                                                                                                                                      |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1      |              | Draft                                                                                                                                                                        |

| 1.0      | 2019/07/15   | Update register                                                                                                                                                              |

| 1.01     | 2019/8/1     | Modify power related pins description                                                                                                                                        |

| 1.02     | 2019/10/09   | Modify Pin description mistakes                                                                                                                                              |

| 1.03     | 2019/12/06   | Update Register table                                                                                                                                                        |

| 1.04     | 2019/12/24   | Update LED related Register                                                                                                                                                  |

| 1.05     | 2020/01/13   | Modify Pin description Update power on sequence Update Power consumption                                                                                                     |

| 1.06     | 2020/02/13   | Modify clock register ext reg 0x0c                                                                                                                                           |

| 1.07     | 2020/02/18   |                                                                                                                                                                              |

| 1.08     | 2020/03/09   | Modify the default value of extended register 0x37, 0x80, 0xb8, 0xb9, 0xba, 0xbb.  Modify package information, ordering information,  Add crystal/external clock requirement |

| 1.09     | 2020/03/10   | Official Release                                                                                                                                                             |

Motor Comm

# CONTENT

| 1. | General Description                             | 8  |

|----|-------------------------------------------------|----|

|    | TARGET APPLICATIONS                             | 8  |

| 2. | Feature                                         | 9  |

| 3. | PIN assigment                                   | 9  |

|    | QFN40 5x5mm                                     | 9  |

|    | 3.2 Pin Descriptions                            | 10 |

|    | MDI                                             | 11 |

|    | RGMII                                           | 11 |

|    | Management Interface and Interrupt              | 11 |

|    | LED                                             | 11 |

|    | System Signal Group/Reference                   | 12 |

|    | Power                                           | 12 |

| 3  | Function Description                            | 14 |

|    | Application Diagram                             | 14 |

|    | 1000BASE-T/100Base-Tx/10Base-Te application     | 14 |

|    | Hyper range HR-100 4 pair application           | 14 |

|    | Transmit Functions                              | 15 |

|    | Transmit Encoder Modes Encoder Mode Description |    |

|    | Receive Functions                               | 15 |

|    | Receive Decoder Modes                           | 15 |

|    | Hyper range                                     | 15 |

|    | Echo Canceller                                  | 16 |

|    | NEXT Canceller                                  | 16 |

|    | Baseline Wander Canceller                       | 16 |

|    | Digital Adaptive Equalizer                      | 16 |

|    | Management interface                            | 17 |

|   | Auto-Negoitation                                        | 17 |

|---|---------------------------------------------------------|----|

|   | LDS (Link discovey signaling)                           | 18 |

|   | Polarity detection and auto correction                  | 18 |

|   | EEE                                                     | 18 |

| 4 | Operational Description                                 | 19 |

|   | Reset                                                   | 19 |

|   | PHY Address                                             | 19 |

|   | RGMII interface                                         | 20 |

|   | RGMII                                                   | 20 |

|   | Loopback mode                                           | 20 |

|   | Digital Loopback                                        | 20 |

|   | External loopback                                       | 21 |

|   | Remote PHY loopback                                     | 22 |

|   | Master-slave configuration                              | 22 |

|   | LED                                                     | 22 |

|   | Auto Negotiation                                        | 23 |

|   | Power Supplies                                          | 24 |

| 5 | Register Overview                                       | 25 |

|   | MII Management Interface Clause 22 Register Programming | 25 |

|   | PHY MII regisiter                                       | 26 |

|   | Phy MII 00h: Basic control register 0x00                | 26 |

|   | Phy MII 01h: Basic status register 0x01                 | 27 |

|   | Phy MII 02h: PHY identification register1 0x02          | 29 |

|   | Phy MII 03h: PHY identification register2 0x03          | 29 |

|   | Phy MII 04h: Auto-Negotiation advertisement 0x04        | 30 |

|   | Phy MII 05h: Auto-Negotiation link partner ability 0x05 | 34 |

|   | Phy MII 06h: Auto-Negotiation expansion register 0x06   | 36 |

|   | Phy MII 07h: Auto-Negotiation NEXT Page register 0x07   | 36 |

| Phy MII 08h: Auto-Negotiation link partner Received NEXT Page register 0x08 | 37 |

|-----------------------------------------------------------------------------|----|

| Phy MII 09h: MASTER-SLAVE control register 0x09                             | 38 |

| Phy MII 0Ah: MASTER-SLAVE status register 0x0A                              | 41 |

| Phy MII 0Dh: MMD access control register 0x0D                               | 42 |

| Phy MII 0Eh: MMD access data register 0x0E                                  | 43 |

| Phy MII 0Fh: Extended status register 0x0F                                  | 43 |

| Phy MII 10h: PHY specific function control register                         | 44 |

| Phy MII 11h: PHY specific status register 0x11                              | 45 |

| Phy MII 12h: Interrupt Mask Register 0x12                                   | 47 |

| Phy MII 13h: Interrupt Mask Register 0x13                                   | 48 |

| Phy MII 14h: Speed Auto Downgrade Control Register 0x14                     | 49 |

| Phy MII 15h: Rx Error Counter Register 0x15                                 | 50 |

| Phy MII 1Eh: Debug Register's Address Offset Register 0x1E                  | 50 |

| Phy MII 1Fh: Debug Register's Data Register                                 | 51 |

| PHY EXTENDED register                                                       |    |

| Phy EXT 00h: MS config debug Register 0x00                                  |    |

| Phy EXT 04h: Manual EEE Ability Regi <mark>ste</mark> r 0x04                | 52 |

| Phy EXT 09h: 100BT Extra Test Mode Register 0x09                            |    |

| Phy EXT 0Ah: 10BT Debug, LPBKs Register 0x0A                                | 53 |

| Phy EXT 0Ch: Phy clock gating Register 0x0C                                 | 54 |

| Phy EXT 0Dh: Delay and driver strength cfg Register 0x0D                    | 55 |

| Phy EXT 27h: Sleep Control1 0x27                                            | 56 |

| Phy EXT 2Dh: EEE 1000BT Wake Error Timer 0x2D                               | 56 |

| Phy EXT 2Eh: EEE 100BT Wake Error Timer 0x2E                                | 57 |

| Phy EXT 30h: EEE Quite Timer Th 0x30                                        | 57 |

| Phy EXT 34h: EEE Control2 0x34                                              | 57 |

| Phy EXT 36h: EEE 100BT Control2 0x36                                        | 57 |

| Phy EXT 37h: EEE 100BT Control3 0x37                                        | 58 |

| Phy EXT 38h: pkgen cfg1 0x38 | 59 |

|------------------------------|----|

| Phy EXT 80h: vct_cfg0 0x80   | 60 |

| Phy EXT 81h: vct_cfg1 0x81   | 60 |

| Phy EXT 82h: vct_cfg2 0x82   | 61 |

| Phy EXT 83h: vct_cfg3 0x83   | 61 |

| Phy EXT 84h: vct_mon0 0x84   | 62 |

| Phy EXT 85h: vct_mon1 0x85   | 62 |

| Phy EXT 86h: vct_mon2 0x86   | 62 |

| Phy EXT 87h: vct_mon3 0x87   |    |

| Phy EXT 88h: vct_mon4 0x88.  |    |

| Phy EXT 89h: vct_mon5 0x89   | 63 |

| Phy EXT 8Ah: vct_mon6 0x8A   | 63 |

| Phy EXT 8Bh: vct_mon7 0x8B   | 63 |

| Phy EXT 8Ch: vct_mon8 0x8C   | 63 |

| Phy EXT 8Dh: vct_mon9 0x8D   | 64 |

| Phy EXT 8Eh: vct_monA 0x8E   |    |

| Phy EXT 8Fh: vct_monB 0x8F   |    |

| Phy EXT 90h: vct_monC 0x90   |    |

| Phy EXT 91h: vct_monD 0x91   | 64 |

| Phy EXT 92h: vct_monE 0x92   | 65 |

| Phy EXT 93h: vct_monF 0x93   | 65 |

| Phy EXT 94h: vct_mon10 0x94  | 65 |

| Phy EXT 95h: vct_cfg4 0x95   | 65 |

| Phy EXT 96h: vct_cfg5 0x96   | 66 |

| Phy EXT 97h: vct_cfg6 0x97   | 66 |

| Phy EXT 98h: vct_cfg7 0x98   | 66 |

| Phy EXT 99h: vct_cfg8 0x99   | 66 |

| EXT B7h: LED General Control | 67 |

6

| EXT B8h: LED1 Control                                  | 68 |

|--------------------------------------------------------|----|

| EXT B9h: LED2 Control                                  | 70 |

| EXT BAh: LED Blink Control                             | 71 |

| EXT BBh: LED3 Control                                  | 72 |

| PHY MMD1                                               | 74 |

| Phy MMD1 00h: PMA/PMD control 1 register 0x00          | 74 |

| Phy MMD1 05h: PMA/PMD devices in package 0x05          | 74 |

| Phy MMD1 08h: PMA/PMD status 2 register 0x08           | 74 |

| PHY MMD3                                               | 75 |

| Phy MMD3 00h: PCS control 1 register 0x00              | 75 |

| Phy MMD3 01h: PCS status 1 register 0x01               | 75 |

| Phy MMD3 05h: PCS devices in package register 0x05     | 76 |

| Phy MMD3 08h: PCS devices in package register 0x08     | 77 |

| Phy MMD3 14h: EEE control and capability register 0x14 | 77 |

| Phy MMD3 16h: EEE wake error counter 0x16              | 77 |

| PHY MMD7                                               |    |

| Phy MMD7 00h: AN Control Register 0x00                 | 78 |

| Phy MMD7 01h: AN Status Register 0x01                  | 78 |

| Phy MMD7 05h: AN devices in package Register 0x05      | 78 |

| Phy MMD7 3Ch: Local Device EEE Ability 0x3C            | 79 |

| Phy MMD7 3Dh: Link Partner EEE Ability 0x3D            | 79 |

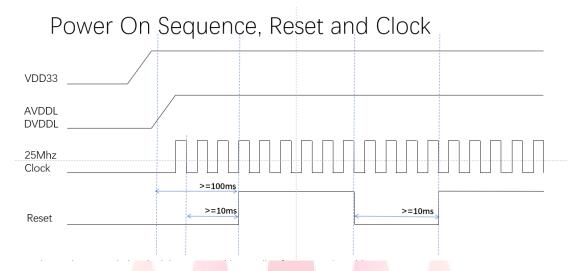

| Timing and AC Characteristics                          | 81 |

| Power ON sequence                                      | 81 |

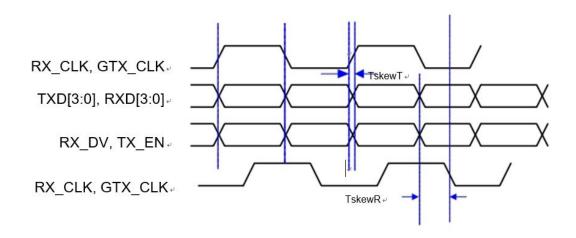

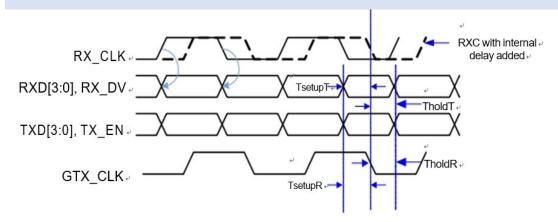

| RGMII Characteristics                                  | 81 |

| RGMII Timing w/o delay                                 | 82 |

| RGMII Timing with internal delay                       | 83 |

| MDIO                                                   | 83 |

| Crystal Requirement                                    | 84 |

|    | Oscillator/External Clock Requirement | . 84 |

|----|---------------------------------------|------|

| 7  | Power Requirements                    | . 85 |

|    | Power Requirement                     | . 85 |

|    | Power consumption (Typical)           | . 86 |

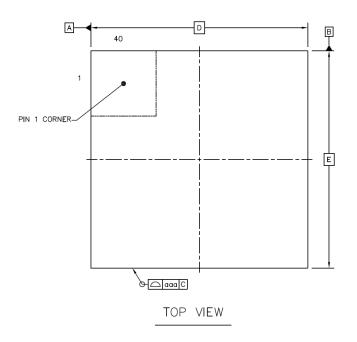

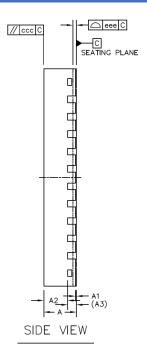

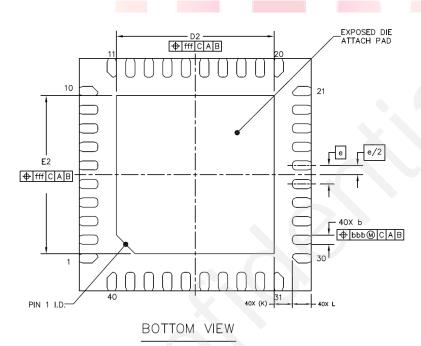

| 8  | Mechanical and Thermal                | . 87 |

|    | RoHS-Compliant Packaging              | . 87 |

| 9  | Mechanical Information                | . 88 |

| 10 | Ordering Information                  | an   |

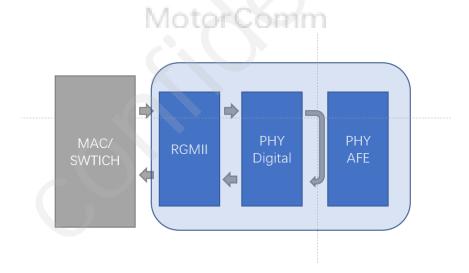

# 1. GENERAL DESCRIPTION

The MotorComm YT8511C YT8511H is a triple-speed 10/100/1000BASE-T Gigabit Ethernet (GbE) Ethernet physical layer transceiver (PHY). Ideally suited for a wide range of industry applications, it is manufactured using a standard digital CMOS process and contains all the active circuitry required to implement the physical layer functions to transmit and receive data on a on Category 5 unshielded twisted-pair (UTP) cabling.

Based on cutting-edge DSP technology, combing adaptive equalizers, echo canceller, phase-locked, ADCs, phase-locked loops, line drivers, encoders/decoders, echo cancelers and all other required support circuitry at a Gigabit data rate to achieve robust performance and exceed automotive electromagnetic interference (EMI) requirements in severe environments with very low power dissipation.

The YT8511C YT8511H is designed to be fully compliant with RGMII interface specifications, allowing compatibility with standard Ethernet media access controllers (MACs) and switch controllers.

The YT8511 delivers the most comprehensive technology solution required by industry operating temperature.

#### TARGET APPLICATIONS

- HDTV

- Gaming machines

- IP Cameras

- Printers

- LED wall

## 2. FEATURE

- 10BASE-Te/100BASE-Tx/1000 BASE-T IEEE 802.3 compliant

- HYPER Range Supported, 4 pair HR-100 mode, enhance 100Mbps distance more than 400 meter

- Supports 1000 BASE-T PCS and autonegotiation with next page support

Supports RGMII interface to MAC devices with a broad I/O voltage level options 2.5V and is compatible with 3.3V I/O.

- RGMII timing modes support internal delay and external delay on Rx path

- Error-free operation up to 120 meters of CAT5e cable.

- Supports Wake-on-LAN (WoL) to detect magic packet and notify the sleeping system to wake up

- Robust Cable Discharge Event (CDE)

- Jumbo Frame support up to 10KB (full duplex)

- All digital baseline wander correction Automatic channel swap (ACS)

- Automatic MDI/MDIX crossover

- Automatic polarity correction

- IEEE 802.3u compliant Auto-Negotiation

- Software programmable LED modes

- Multiple Loopback modes for diagnostics

# 3. PIN ASSIGMENT

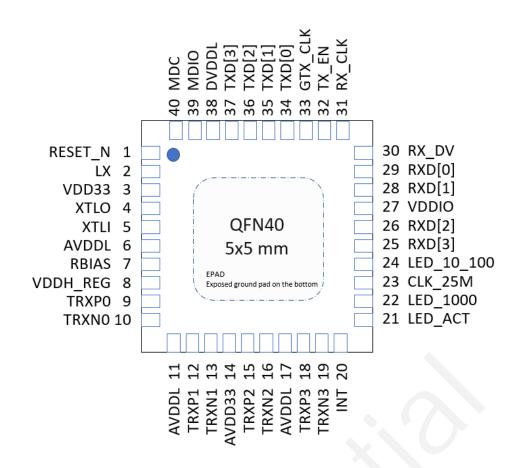

QFN40 5X5MM

# 3.2 PIN DESCRIPTIONS

- $\bullet$  I = Input

- $\bullet$  O = Output

- I/O = Bidirectional

- OD = Open-drain output

- OT = Tristateable signal

- $\bullet$  B = Bias

- PU = Internal pull-up

- PD = Internal pull-down

- SOR = Sample on reset

- CS = Continuously sampled

- ST = Schmitt trigger

- XT = Crystal inputs/outputs pin type

- D = Digital pin type

- G = RGMII pin type

- A = Analog pin type

| Symbol   | Pin   | Туре    | Description                                                    |

|----------|-------|---------|----------------------------------------------------------------|

| MDI      |       |         |                                                                |

| TRXP0,   | 9     | IA,     | Media-dependent interface $0, 100\Omega$ transmission line     |

| TRXN0    | 10    | OA      | , , , , , , , , , , , , , , , , , , , ,                        |

| TRXP1,   | 12,   | IA,     | Media-dependent interface 1, $100\Omega$ transmission line     |

| TRXN1    | 13    | OA      | -                                                              |

| TRXP2,   | 15,   | IA,     | Media-dependent interface 2, $100\Omega$ transmission line     |

| TRXN2    | 16    | OA      |                                                                |

| TRXP3,   | 18,   | IA,     | Media-dependent interface 3, $100\Omega$ transmission line     |

| TRXN3    | 19    | OA      |                                                                |

| RGMII    |       |         |                                                                |

| GTX_CLK  | 33    | I, PD   | RGMII transmit clock, 125/25/2.5 MHz digital. Adding a 220hm   |

|          |       |         | damping resistor is recommended for EMI design near MAC        |

|          |       |         | side.                                                          |

| RX_CLK   | 31    | I/O,    | 125MHz digital, adding a 220hm damping resistor is             |

|          |       | PD      | recommended for EMI design near PHY side.                      |

| RX_DV    | 30    | I/O,    | RGMII receive data valid                                       |

|          |       | PD      |                                                                |

| RXD[0]   | 29    | I/O,    | RGMII received data 0                                          |

|          |       | PD      |                                                                |

| RXD[1]   | 28    | I/O,    | RGMII received data 1                                          |

|          |       | PD      |                                                                |

| RXD[2]   | 26    | I/O,    | RGMII received data 2                                          |

|          |       | PD      |                                                                |

| RXD[3]   | 25    | I/O,    | RGMII received data 3                                          |

|          |       | PD      |                                                                |

| TX_EN    | 32    | I, PD   | RGMII transmit enable                                          |

| TXD[0]   | 34    | I, PD   | RGMII transmit data 0                                          |

| TXD[1]   | 35    | I, PD   | RGMII transmit data 1                                          |

| TXD[2]   | 36    | I, PD   | RGMII transmit data 2                                          |

| TXD[3]   | 37    | I, PD   | RGMII transmit data 3                                          |

| MANAGEME | NT IN | ΓERFAC  | E AND INTERRUPT                                                |

| MDC      | 40    | I, PU   | Management data clock reference                                |

| MDIO     | 39    | I/O, D, | Management data, pull-up resistor to 3.3V/2.5V                 |

|          |       | PU      |                                                                |

| INT      | 20    | I/O, D, | Interrupt Signal to System; default OD-gate, needs an external |

|          |       | PD      | pull up resistor                                               |

|          |       |         |                                                                |

| LED      |       |         |                                                                |

|          |       |         |                                                                |

| LED_ACT    | 21    | I/O,    | Parallel LED output for 10/100/1000 BASE-T activity, active     |  |  |

|------------|-------|---------|-----------------------------------------------------------------|--|--|

| _          |       | PU      | blinking. LED active based upon power-on strapping. If pulled   |  |  |

|            |       |         | up, active low, if pulled down, active high                     |  |  |

| LED_1000   | 22    | I/O,    | Parallel LED output for 1000 BASE-T link, LED active based      |  |  |

|            |       | PU      | upon power-on strapping.                                        |  |  |

| LED_10_100 | 24    | I/O,    | Parallel LED output for 10/100 BASE-T link.                     |  |  |

|            |       | PU      |                                                                 |  |  |

| SYSTEM SIG | NAL C | GROUP/F | REFERENCE                                                       |  |  |

| CLK_25M    | 23    | O, PD   | 25 MHz clock output (default). It can be 125, 62.5 or 25 MHz    |  |  |

|            |       |         | clock output                                                    |  |  |

| RESET_N    | 1     | I       | System reset, active low. Requires an external pull-up resistor |  |  |

| XTLI       | 5     | IA      | Crystal oscillator input. Requires a capacitor to GND. Support  |  |  |

|            |       |         | external 25 MHz, 1.2V swing clock input through this pin.       |  |  |

| XTLO       | 4     | OA      | Crystal oscil <mark>lator</mark> output; add a capacitor to GND |  |  |

| RBIAS      | 7     | OA      | External 2.4 k ohm 1% to GND to set bias current                |  |  |

| POWER      |       |         |                                                                 |  |  |

| LX         | 2     | OA      | Power inductor pin. Add an external 4.7 uH power inductor       |  |  |

|            |       |         | between this pin and pin 38.                                    |  |  |

| VDDH_REG   | 8     | OA      | 3.3V or 2.5 V regulator output. A 1uF capacitor connected to    |  |  |

|            |       |         | GND.                                                            |  |  |

| VDDIO      | 27    | IA      | VDDIO input.                                                    |  |  |

|            |       |         | Connect this pin to pin 8 (VDDH_REG) directly.                  |  |  |

| AVDDL      | 6,    | P       | 1.2 V analog power input. Connect to Pin 38 through a bead      |  |  |

|            | 11    |         |                                                                 |  |  |

|            | 17    |         |                                                                 |  |  |

| DVDDL      | 38    | P       | 1.2 V digital core power input. Connect to power inductor and   |  |  |

|            |       | 20      | 10uF+0.1uF ceramic capacitors to GND                            |  |  |

| VDD33      | 3     | P       | 3.3 V power for switching regulator                             |  |  |

| AVDD33     | 14    | P       | Analog 3.3 V power input for PHY, from VDD33 through a bead     |  |  |

|            |       |         |                                                                 |  |  |

| POWFR  | $\cap$ N I | CTDA                           |         |

|--------|------------|--------------------------------|---------|

| PUVVFK | UIIV       | $\mathcal{O} \cap \mathcal{K}$ | PPIIVIO |

| PHY Pin    | PHY Core Config               | Description                                                        | Default |

|------------|-------------------------------|--------------------------------------------------------------------|---------|

| RXD0       | PHYADDRESS0                   | LED_ACT, RXD[1:0] sets the lower three bits of the                 | 0       |

|            |                               | physical address. The upper two bits of the physical address       |         |

|            |                               | are set to the default, "00"                                       |         |

| RXD1       | PHYADDRESS1                   | LED_ACT, RXD[1:0] sets the lower three bits of the                 | 0       |

|            |                               | physical address. The upper two bits of the physical address       |         |

|            |                               | are set to the default, "00"                                       |         |

| LED_ACT    | PHYADDRESS2                   | LED_ACT, RXD[1:0] sets the lower three bits of the                 | 1       |

|            |                               | physical address. The upper two bits of the physical address       |         |

|            |                               | are set to the default, "00"                                       |         |

| RX_DV      | RGMII IO power                | 0= RGMII IO 3.3V                                                   |         |

|            | selection                     | 1= RGMII IO 2.5V                                                   |         |

| RXD2       | PLLON selection               | 0= PLL off in hibernation when cable unplugged                     | 0       |

|            |                               | 1= PLL on in hibernation when cable unplugged                      |         |

| LED_1000   | TEST Mode                     | 0=Test Mode only for internal use                                  | 1       |

|            |                               | 1=N <mark>ormal M</mark> ode, M <mark>ust ext</mark> ernal pull up |         |

| RXD3       | Low Power Mode                | 0= Force Low Power mode for shorter cable application              | 0       |

|            | selection                     | 1= Normal cable application                                        |         |

| LED_10_100 | RXC delay enable              | 0= RXC delay disable                                               | 1       |

|            |                               | 1= RXC delay enable                                                |         |

| RX_CLK     | clk 2 <mark>5m</mark> disable | 0= clk 25m output enable                                           | 0       |

|            |                               | 1= clk 25m output disable                                          |         |

NOTE: 0=Pull-down, 1=Pull-up

# 3 FUNCTION DESCRIPTION

The YT8511 is MotorComm low cost GbE PHY. It is a highly integrated analog front end (AFE) and digital signal transceiver, providing high performance combined with substantial cost reduction. The YT8511 provides physical layer functions for half/full duplex 10 BASE-Te, 100 BASE-Tx and 1000 BASE-T Ethernet to transmit and receive high-speed data over standard category 5 (CAT5) unshielded twisted pair cable.

The YT8511 10/100/1000 PHY is fully 802.3ab compliant, and supports the reduced Gigabit Media-Independent Interface (RGMII) to connect to a Gigabit-capable MAC.

The YT8511 transceiver combines echo canceller, near end cross talk (NEXT) canceller, feed-forward equalizer, feedback equalizer, and timing recovery, to enhance signal performance in noisy environments.

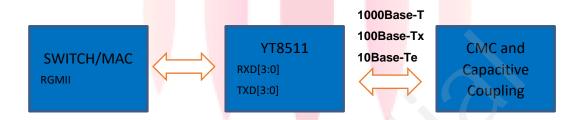

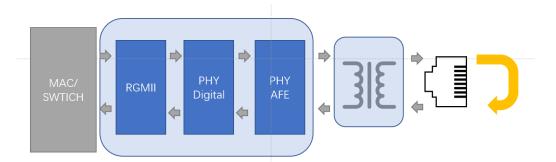

## APPLICATION DIAGRAM

#### 1000BASE-T/100BASE-TX/10BASE-TE APPLICATION

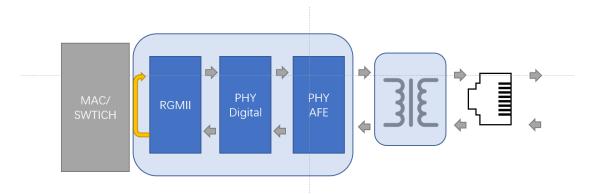

### HYPER RANGE HR-100 4 PAIR APPLICATION

#### TRANSMIT FUNCTIONS

#### TRANSMIT ENCODER MODES ENCODER MODE DESCRIPTION

#### 1000 BASE-T

In 1000 BASE-T mode, the YT8511 scrambles transmit data bytes from the MAC interfaces to 8-bit symbols and encodes them into 4D five-level PAM signals over the four pairs of CAT5 cable.

#### 100 BASE-TX

In 100 BASE-TX mode, 4-bit data from the MII is 4B/5B serialized, scrambled, and encoded to a three-level MLT3 sequence transmitted by the PMA.

#### 10 BASE-TE

In 10 BASE-Te mode, the YT8511 transmits and receives Manchester-encoded data.

#### RECEIVE FUNCTIONS

#### RECEIVE DECODER MODES

#### 1000 BASE-T

In 1000 BASE-T mode, the PMA recovers the 4D PAM signals after accounting for the cabling conditions such as skew among the four pairs, the pair swap order, and the polarity of the pairs. The resulting code group is decoded into 8-bit data values. Data stream delimiters are translated appropriately and data is output to the MAC interfaces.

100 BASE-TX

#### IN 100 BASE-TX MODE, THE RECEIVE

data stream is recovered and descrambled to align to the symbol boundaries. The aligned data is then parallelized and 5B/4B decoded to 4-bit data. This output runs to the MII receive data pins after data stream delimiters have been translated.

#### 10 BASE-TE

In 10 BASE-Te mode, the recovered 10 BASE-Te signal is decoded from Manchester then aligned.

#### HYPER RANGE

Hyper-range is the motor-comm proprietary mode in extended cable reach application up to 400m in 100M mode. HR-100 is 100Mbps Mode.

#### ECHO CANCELLER

A hybrid circuit is used to transmit and receive simultaneously on each pair. A signal reflects back as an echo if the transmitter is not perfectly matched to the line. Other connector or cable imperfections, such as patch panel discontinuity and variations in cable impedance along the twisted pair cable, also result in drastic SNR degradation on the receive signal. The YT8511 device implements a digital echo canceller to adjust for echo and is adaptive to compensate for the varied channel conditions.

#### **NEXT CANCELLER**

The 1000 BASE-T physical layer uses all four pairs of wires to transmit data. Because the four twisted pairs are bundled together, significant high frequency crosstalk occurs between adjacent pairs in the bundle. The YT8511 device uses three parallel NEXT cancellers on each receive channel to cancel high frequency crosstalk. The YT8511 cancels NEXT by subtracting an estimate of these signals from the equalizer output.

#### BASELINE WANDER CANCELLER

Baseline wander results from Ethernet links that AC-couple to the transceivers and from AC coupling that cannot maintain voltage levels for longer than a short time. As a result, transmitted pulses are distorted, resulting in erroneous sampled values for affected pulses. Baseline wander is more problematic in the 1000 BASE-T environment than in 100 BASE-TX due to the DC baseline shift in the transmit and receive signals. The YT8511 device uses an advanced baseline wander cancellation circuit that continuously monitors and compensates for this effect, minimizing the impact of DC baseline shift on the overall error rate.

#### DIGITAL ADAPTIVE EQUALIZER

The digital adaptive equalizer removes inter- symbol interference at the receiver. The digital adaptive equalizer takes unequalized signals from ADC output and uses a combination of feedforward equalizer (FFE) and decision feedback equalizer (DFE) for the best optimized signal-to-noise (SNR) ratio.

#### MANAGEMENT INTERFACE

The Status and Control registers of the device are accessible through the MDIO and MDC serial interface. The functional and electrical properties of this management interface comply with IEEE 802.3, Section 22 and also support MDC clock rates up to 12.5 MHz.

#### **AUTO-NEGOITATION**

The YT8511 negotiates its operation mode using the auto negotiation mechanism according to IEEE 802.3 clause 28 over the copper media. Auto negotiation supports choosing the mode of operation automatically by comparing its own abilities and received abilities from link partner. The advertised abilities include:

a) Speed: 10/100/1000Mbps

b) Duplex mode: full duplex and/or half duplex

Auto negotiation is initialized when the following scenarios happen:

- a) Power-up/Hardware/Software reset

- b) Auto negotiation restart

- c) Transition from power-down to power up

- d) Link down

Auto negotiation is enabled for YT8511 by default, and can be disable byoftware control.

## LDS (LINK DISCOVEY SIGNALING)

YT8511 supports long range ethernet (LRE), which uses link discovery signaling (LDS) instead of auto negotiation since the extended cable reach attenuates the auto negotiation link pulses. LDS is an extended reach signaling scheme and protocol, which is used to

- a) Master/Slave assignment

- b) Estimate cable length

- c) Confirm pair number and pair connectivity ordering

- d) Choose highest common operation mode

IEEE-compliant PHYs will ignore LDS signal since its frequency is less than 2MHz according to IEEE802.3 clause 14. If the link partner is an IEEE legacy ethernet PHY, YT8511 can detect the standard NLP, FLP, MLT-3 IDLE signal, or 100BASE-T4 signal, and then transits LDS mode into Clause 28 auto negotiation mode.

Forcing pair number and speed mode is also supported. The same forcing must be done at both ends of the link.

## POLARITY DETECTION AND AUTO CORRECTION

YT8511 can detect and correct two types of cable errors: swapping of pairs within the UTP cable and swapping of wires within a pair.

#### EEE

EEE is IEEE 802.3az, an extension of the IEEE 802.3 standard. EEE defines support for the PHY to operate in Low Power Idle (LPI) mode which, when enabled, supports QUIET times during low link utilization allowing both link partners to disable portions of each PHY's circuitry and save power.

## 4 OPERATIONAL DESCRIPTION

#### RESET

YT8511 have a hardware reset pin(RESET\_N) which is low active. RESET\_N should be active for at least 10ms to make sure all internal logic is reset to a known state. Hardware reset should be applied after power up.

RESET\_N is also used as enable for power on strapping. After RESET\_N is released, YT8511 latches input value on strapping pin which is used as configuration information which provides flexibility in application without mdio access. Detailed information please refer to pin description in table x(add index for table and figure).

YT8511 also provides two software reset control registers which are used to reset all internal logic except some mdio configuration registers. For detailed information about what register will be reset by software reset, please refer to register table. Configure bit 15 of lds mii register(address 0x0) or mii register(address 0x0) to 1 to enable software reset. These two bits are self-clear after reset process is done.

#### PHY ADDRESS

For YT8511, {LED\_ACT, RXD[1:0]} is used to generate lower 3 bits of phy address. The upper 2 bits are always 0. So valid phy address is from 5'b00000 to 5'b00111.

YT8511 always response to phy address 0. Bit[6] of extended register(address 0x0) is enable control for phy address 0 and its default value is 1'b1. It also has another broadcast phy address which is configurable through mdio. Bit[4:0] of extended register(address 0x0) is broadcast phy address and its default value is 5'b11111. Bit[5] of extended register(address 0x0) is enable control for broadcast phy address and its default value is 1'b1.

| PHY Pin | PHY Core    | Description                                                  | Default |

|---------|-------------|--------------------------------------------------------------|---------|

|         | Config      |                                                              |         |

| RXD0    | PHYADDRESS0 | LED_ACT, RXD[1:0] sets the lower three bits of the           | 0       |

|         |             | physical address. The upper two bits of the physical address |         |

|         |             | are set to the default, "00"                                 |         |

| RXD1    | PHYADDRESS1 | LED_ACT, RXD[1:0] sets the lower three bits of the           | 0       |

|         |             | physical address. The upper two bits of the physical address |         |

|         |             | are set to the default, "00"                                 |         |

| LED_ACT | PHYADDRESS2 | LED_ACT, RXD[1:0] sets the lower three bits of the           | 1       |

|         |             | physical address. The upper two bits of the physical address |         |

|         |             | are set to the default, "00"                                 |         |

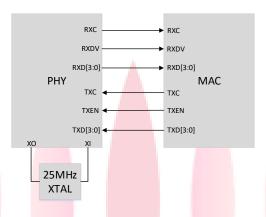

#### **RGMII INTERFACE**

#### **RGMII**

Reduced gigabit media independent interface is a subset of GMII which is used for gigabit Ethernet. For 100M/10M application, RGMII is similar to MII. The only difference is that tx\_er/rx\_er is transmitted by tx\_en/rx\_dv on the falling edge of clock. TXD[3:0] and RXD[3:0] will be duplicated on both rising and falling edge of clock. For 100M application, TXC and RXC are 25MHz; for 10M application, TXC and RXC are 2.5MHz.

Figure . connection diagram of RGMII

## LOOPBACK MODE

There are three loopback modes in YT8511.

#### DIGITAL LOOPBACK

Digital loopback provides the ability to loop transmitted data back to the receiver using digital circuitry in the YT8511 device.

Figure . digital loopback

1000M loopback: write register 0x0 = 0x4140 to enable 1000M digital loopback.

100M loopback: write register 0x0 = 0x6100 to enable 100M digital loopback.

10M loopback: write register 0x0 = 0x4100 to enable 10M digital loopback.

## EXTERNAL LOOPBACK

External cable loopback loops Tx to Rx through a complete digital and analog path and an external cable, thus testing all the digital data paths and all the analog circuits. Figure shows a block diagram of external cable loopback.

Figure . external loopback

#### REMOTE PHY LOOPBACK

The Remote loopback connects the MDI receive path to the MDI transmit path, near the RGMII interface, thus the remote link partner can detect the connectivity in the resulting loop. Figure below, shows the path of the remote loopback.

#### MASTER-SLAVE CONFIGURATION

Master and slave configuration only exist in HR-100 mode.

Master and slave configuration is from lds negotiating result or in force mode, it comes from bit 3 of lds mii reg(address 0h0).

#### **LED**

The LED interface can either be controlled by the PHY or controlled manually, independent of the state of the PHY. Three status LEDs are available. These can be used to indicate operation speed, duplex mode, and link status. The LEDs can be programmed to different status functions from their default value. They can also be controlled directly from the register interface.

| Symbol     | 10M<br>link | 10M<br>active | 100M<br>link | 100M<br>active | 1000M<br>link | 1000M<br>active |

|------------|-------------|---------------|--------------|----------------|---------------|-----------------|

| LED_10_100 | off         | off           | on           | on             | off           | off             |

| LED_1000   | off         | off           | off          | off            | on            | on              |

| LED_ACT    | on          | blink         | on           | blink          | on            | blink           |

## **AUTO NEGOTIATION**

When auto negotiation is enabled, YT8511 operation mode is based on the negotiation results, including speed and duplex mode. Registers configurations are shown as:

| Register Type | Register Address | Write Value | Comments                             |

|---------------|------------------|-------------|--------------------------------------|

| Extended      | 16'h0100         | 16'h0006    | Bit2: 1'b1, Access IEEE MII regs     |

| MII           | 16'h0000         |             | Bit12: 1'b1, enable auto negotiation |

Table: Enable auto negotiation

| Register Type | Register Address | Write Value | Comments                             |

|---------------|------------------|-------------|--------------------------------------|

| Extended      | 16'h0100         | 16'h0006    | Bit2: 1'b1, Access IEEE MII regs     |

| MII           | 16'h0000         |             | Bit9: 1'b1, restart auto negotiation |

Table: Restart auto negotiation

| Register Type | Register Address | Write Value            | Comments                                                      |

|---------------|------------------|------------------------|---------------------------------------------------------------|

| Extended      | 16'h0100         | 16'h <mark>0006</mark> | Bit <mark>2: 1'b1,</mark> Acce <mark>ss IEE</mark> E MII regs |

| MII           | 16'h0001         |                        | Bit5: 1'b1, AN complete; 1'b0, AN not                         |

|               |                  |                        | complete                                                      |

|               | V                |                        | Bit3: 1'b1, support AN; 1'b0, not support                     |

|               | , V              |                        | AN                                                            |

|               | Y                | V                      | Bit2: 1'b1, Link up; 1'b0, link down                          |

| MII           | 16'h0011         | Y                      | Bit15-14: 2'b00, 10Mbps; 2'b01:                               |

|               |                  |                        | 100Mbps                                                       |

|               | 之公               | <b>大</b> 左             | Bit5: 1'b1, link is downgrade; 1'b0, link                     |

|               | TH               | $\wedge$               | is not downgrade                                              |

Table: Auto negotiation status

When auto negotiation is disabled, forcing speed and duplex mode is also support. Forcing 10BASE-T has been discussed in the LDS part. Registers configuration for Forcing 100BASE-TX is shown as:

| Register Type | Register Address | Write Value | Comments                              |

|---------------|------------------|-------------|---------------------------------------|

| Extended      | 16'h0100         | 16'h0006    | Bit2: 1'b1, Access IEEE MII regs      |

| MII           | 16'h0000         |             | Bit12: 1'b0, disable auto negotiation |

|               |                  |             | Bit6,13: 2'b01, 100Mbps               |

|               |                  |             | Bit8: 1'b1, full duplex               |

Table: Forcing 100BASE-TX

During auto negotiation, YT8511 supports automatic MDI crossover by detecting and correcting external crossover cable. If the link partner also supports automatic MDI crossover, only one device performs the crossover according to IEEE 802.3 Clause 40.4.4. YT8511 also supports forcing MDI/MDIX mode. Registers configurations are shown as:

| Register Type | Register Address | Write Value | Comments                           |

|---------------|------------------|-------------|------------------------------------|

| Extended      | 16'h0100         | 16'h0006    | Bit2: 1'b1, Access IEEE MII regs   |

| MII           | 16'h0010         |             | Bit6-5: 2'b00, forcing MDI; 2'b01, |

|               |                  |             | forcing MDIX; 2'b11, automatic MDI |

|               |                  |             | crossover                          |

Table: MDI/MDI-X configuration

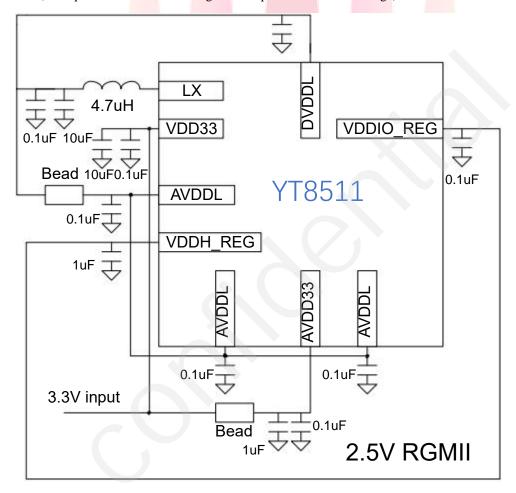

## POWER SUPPLIES

The YT8511 device requires only one external power supply: 3.3 V. Inside the chip there is a 3.3V rail, 2.5V rail, 1.2V rail.

YT8511 integrates a switch regulator which converts 3.3V to 1.2V at a high-efficiency for core power rail. (It is optional for an external regulator to provide this core voltage).

# 5 REGISTER OVERVIEW

#### MII MANAGEMENT INTERFACE CLAUSE 22 REGISTER PROGRAMMING

The YT8511 transceiver is designed to be fully compliant with the MII clause of the IEEE 802.3u Ethernet specification.

The MII management interface registers are written and read serially, using the MDIO and MDC pins.

A clock of up to 25 MHz must drive the MDC pin of the YT8511. Data transferred to and from the MDIO pin is synchronized with the MDC clock. The following sections describe what each MII read or write instruction contains.

| Notation | Description                    |  |  |  |

|----------|--------------------------------|--|--|--|

| RW       | Read and write                 |  |  |  |

| SC       | Self-clear                     |  |  |  |

| RO       | Read only                      |  |  |  |

| LH       | Latch high                     |  |  |  |

| LL       | Latch low                      |  |  |  |

| RC       | Read clear                     |  |  |  |

| SWC      | Clear to 0 when software reset |  |  |  |

| sws      | Set to 1 when software reset   |  |  |  |

| CRW      | Read and conditionally Write   |  |  |  |

| POS      | Power On Strapping             |  |  |  |

Motor Comm

# PHY MII REGISITER

| PHY MII | 00H: BASIC CONTRO    | L REGIST  | ΓER 0X00 |                                                                                                                                                                                                                                                                                                          |

|---------|----------------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Symbol               | Access    | Default  | Description                                                                                                                                                                                                                                                                                              |

| 15      | Reset                | RW SC     | 0x0      | PHY Software Reset. Writing 1 to this bit causes immediate PHY reset. Once the operation is done, this bit is cleared automatically.  0: Normal operation  1: PHY reset                                                                                                                                  |

| 14      | Loopback             | RW<br>SWC | 0x0      | Internal loopback control 1'b0: disable loopback 1'b1: enable loopback                                                                                                                                                                                                                                   |

| 13      | Speed_Selection(LSB) | RW        | Сопп     | LSB of speed_selection[1:0]. Link speed can be selected via either the Auto-Negotiation process, or manual speed selection speed_selection[1:0].  Speed_selection[1:0] is valid when Auto-Negotiation is disabled by clearing bit 0.12 to zero.  Bit6 bit13  1 1 = Reserved 1 0 = 1000Mb/s 0 1 = 100Mb/s |

| 12      | Autoneg_En           | RW        | 0x1      | to enable auto-negotiation;     enable auto-negotiation is disabled.                                                                                                                                                                                                                                     |

| 11      | Power_down           | RW<br>SWC | 0x0      | 1 = Power down 0 = Normal operation When the port is switched from power down to normal operation, software reset and Auto- Negotiation are performed even                                                                                                                                               |

|     |                       |       |     | bit[15] RESET and bit[9] RESTART_AUTO_NEGOTIATI |

|-----|-----------------------|-------|-----|-------------------------------------------------|

|     |                       |       |     | ON are not set by the user.                     |

|     |                       |       |     | Orvare not set by the user.                     |

| 10  | Isolate               | RW    | 0x0 | Isolate phy from                                |

|     |                       | SWC   |     | RGMII/SGMII/FIBER.                              |

|     |                       |       |     | 1'b0: Normal mode                               |

|     |                       |       |     | 1'b1: Isolate mode                              |

| 9   | Re_Autoneg            | RW SC | 0x0 | Auto-Negotiation automatically                  |

|     |                       | SWS   |     | restarts after hardware or software             |

|     |                       |       |     | reset regardelss of bit[9]                      |

|     | A                     |       |     | RESTART.                                        |

|     | A A                   |       |     | 1 = Restart Auto-Negotiation                    |

|     | A A                   |       |     | Process                                         |

|     |                       |       |     | 0 = Normal operation                            |

| 8   | Duplex_Mode           | RW    | 0x1 | The duplex mode can be selected                 |

|     |                       |       |     | via either the Auto-Negotiation                 |

|     |                       |       |     | process or manual duplex                        |

|     | V W                   |       |     | selection. Manual duplex selection              |

|     | V                     |       |     | is allowed when Auto-Negotiation                |

|     |                       |       |     | is disabled by setting bit[12]                  |

|     |                       |       |     | AUTO_NEGOTIATION to 0.                          |

|     | 之公                    | -     | 左   | 1 = Full Duplex                                 |

|     | 10                    | A     | 75  | 0 = Half Duplex                                 |

| 7   | Collision_Test        | RW    | 0x0 | Setting this bit to 1 makes the COI             |

|     |                       | SWC   |     | signal asserted whenever the                    |

|     |                       |       |     | TX_EN signal is asserted.                       |

|     |                       |       |     | 1 = Enable COL signal test                      |

|     |                       |       |     | 0 = Disable COL signal test                     |

| 6   | Speed_ Selection(MSB) | RW    | 0x1 | See bit13.                                      |

|     |                       | 20    | 0x0 | Reserved. Write as 0, ignore on                 |

| 5:0 | Reserved              | RO    | UAU | Reserved. Write as 0, ignore on                 |

PHY MII 01H: BASIC STATUS REGISTER 0X01

| Bit | Symbol                   | Access    | Default | Description                                                                                                                                                                                                                         |

|-----|--------------------------|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | 100Base-T4               | RO        | 0x0     | PHY doesn't support 100BASE-T4                                                                                                                                                                                                      |

| 14  | 100Base-X_Fd             | RO        | 0x1     | PHY supports 100BASE-X_FD                                                                                                                                                                                                           |

| 13  | 100Base-X_Hd             | RO        | 0x1     | PHY supports 100BASE-X_HD                                                                                                                                                                                                           |

| 12  | 10Mbps_Fd                | RO        | 0x1     | PHY supports 10Mbps_Fd                                                                                                                                                                                                              |

| 11  | 10Mbps_Hd                | RO        | 0x1     | PHY supports 10Mbps_Hd                                                                                                                                                                                                              |

| 10  | 100Base-T2_Fd            | RO        | 0x0     | PHY doesn't support 100Base-<br>T2_Fd                                                                                                                                                                                               |

| 9   | 100Base-T2_Hd            | RO        | 0x0     | PHY doesn't support 100Base-<br>T2_Hd                                                                                                                                                                                               |

| 8   | Extended_Status          | RO        | 0x1     | Whether support EXTended status register in 0Fh 0: Not supported 1: Supported                                                                                                                                                       |

| 7   | Unidirect_Ability        | RO        | 0x0     | 1'b0: PHY able to transmit from MII only when the PHY has determined that a valid link has been established 1'b1: PHY able to transmit from MII regardless of whether the PHY has determined that a valid link has been established |

| 6   | Mf_Preamble_ Suppression | RO        | 0x1     | 1'b0: PHY will not accept management frames with preamble suppressed 1'b1: PHY will accept management frames with preamble suppressed                                                                                               |

| 5   | Autoneg_Complete         | RO<br>SWC | Ox0     | 1'b0: Auto-negotiation process not completed 1'b1: Auto-negotiation process completed                                                                                                                                               |

| 3     | Remote_Fault  Autoneg_Ability | RO RC<br>SWC<br>LH | 0x0     | 1'b0: no remote fault condition detected 1'b1: remote fault condition detected 1'b0: PHY not able to perform                                          |

|-------|-------------------------------|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3     | Autonog_Aomity                | KO                 | UXI     | Auto-negotiation  1'b1: PHY able to perform Auto- negotiation                                                                                         |

| 2     | Link_Status                   | RO<br>SWC<br>LL    | 0x0     | Link status 1'b0: Link is down 1'b1: Link is up                                                                                                       |

| 1     | Jabber_Detect                 | RO RC<br>SWC<br>LH | 0x0     | 10Baset jabber detected. It would assert if TX activity lasts longer than 42ms.  1'b0: no jabber condition detected  1'b1: Jabber condition detected. |

| 0     | Extended_Capability           | RO                 | 0x1     | To indicate whether support EXTended registers, to access from address register 1Eh and data register 1Fh 1'b0: Not supported 1'b1: Supported         |

|       | 松谷                            | 大                  | 车       | 前                                                                                                                                                     |

|       | 02H: PHY IDENTIFICA           | ATION R            |         |                                                                                                                                                       |

| Bit   | Symbol                        | Access             | Default | Description                                                                                                                                           |

| 15:0  | Phy_Id                        | RO                 | 0x0     | Bits 3 to 18 of the Organizationally Unique Identifier                                                                                                |

|       |                               |                    |         |                                                                                                                                                       |

|       | 03H: PHY IDENTIFICA           | I                  | 1       |                                                                                                                                                       |

| Bit   | Symbol                        | Access             | Default | Description                                                                                                                                           |

| 15:10 | Phy_Id                        | RO                 | 0x0     | Bits 19 to 24 of the Organizationally Unique Identifier                                                                                               |

| 9:4   | Type_No                       | RO                 | 0x10    | 6 bits manufacturer's type number                                                                                                                     |

| 3:0     | Revision_No        | RO      | 0xa      | 4 bits manufacturer's revision number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY MII | 04H: AUTO-NEGOTIA  | TION AD | VERTISEM | 1ENT 0X04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bit     | Symbol             | Access  | Default  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15      | NEXT_Page  Ack     | RW      | 0x0      | This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:  • Software reset is asserted by writing register 0x0 bit[15]  • Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]  • The port is switched from power down to normal operation by writing register 0x0 bit[11]  • Link goes down  If 1000BASE-T is advertised, the required next pages are automatically transmitted. This bit must be set to 0 if no additional next page is needed.  1 = Advertise  0 = Not advertised  Always 0. |

| 13      | Remote_Fault       | RW      | 0x0      | 1 = Set Remote Fault bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | Zionoto_1 uuit     |         | OAG .    | 0 = Do not set Remote Fault bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12      | Extended_NEXT_Page | RW      | 0x1      | Extended nEXT page enable control bit $1 = \text{Local device supports}$ transmission of extended next pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|    |                  |      |              | 0 = Local device does not support<br>transmission of extended next                              |

|----|------------------|------|--------------|-------------------------------------------------------------------------------------------------|

|    |                  |      |              | pages.                                                                                          |

| 11 | Asymmetric_Pause | RW   | 0x1          | This bit is updated immediately after the writing operation; however the configuration does not |

|    |                  |      |              | take effect until any of the                                                                    |

|    |                  |      |              | following occurs:                                                                               |

|    |                  |      |              | Software reset is asserted by                                                                   |

|    |                  |      |              | writing register 0x0 bit[15]                                                                    |

|    |                  |      |              | Restart Auto-Negotiation is                                                                     |

|    | A                |      |              | triggered by writing register 0x0                                                               |

|    | , A              |      |              | bit[9]                                                                                          |

|    |                  |      | <b>n</b> . / | The port is switched from power down to normal operation by                                     |

|    |                  |      |              | writing register 0x0 bit[11]                                                                    |

|    |                  |      |              | • Link goes down                                                                                |

|    |                  |      |              | 1 = Asymmetric Pause                                                                            |

|    |                  |      |              | 0 = No asymmetric Pause                                                                         |

| 10 | Pause            | RW   | 0x1          | This bit is updated immediately                                                                 |

|    | Ψ.               |      |              | after the writing operation;                                                                    |

|    |                  |      |              | however the configuration does not                                                              |

|    | 27.5             |      |              | take effect until any of the                                                                    |

|    | 7台               | 太    | # 1          | following occurs:                                                                               |

|    |                  |      |              | • Software reset is asserted by                                                                 |

|    | IVI              | otor | COPI         | writing register 0x0 bit[15]  • Restart Auto-Negotiation is                                     |

|    |                  |      |              | triggered by writing register 0x0                                                               |

|    |                  |      |              | bit[9]                                                                                          |

|    |                  |      |              | • The port is switched from power                                                               |

|    |                  |      |              | down to normal operation by                                                                     |

|    |                  |      |              | writing register 0x0 bit[11]                                                                    |

|    |                  |      |              | Link goes down                                                                                  |

|    |                  |      |              | 1 = MAC PAUSE implemented                                                                       |

|    |                  |      |              | 0 = MAC PAUSE not                                                                               |

|    |                  |      |              | implemented                                                                                     |

| 9 | 100BASE-T4                 | RO | 0x0 | 1 = Able to perform 100BASE-T4 0 = Not able to perform 100BASE- T4 Always 0                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|----------------------------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 | 100BASE-<br>TX_Full_Duplex | RW | 0x1 | This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:  • Software reset is asserted by writing register 0x0 bit[15]  • Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]  • The port is switched from power down to normal operation by writing register 0x0 bit[11]  • Link goes down  1 = Advertise  0 = Not advertised                                                               |

| 7 | 100BASE- TX_Half_Duplex    | RW | 0x1 | This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:  This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:  • Software reset is asserted by writing register 0x0 bit[15]  • Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]  • The port is switched from power down to normal operation by |

|   |                        |    |     | writing register 0x0 bit[11]  • Link goes down  1 = Advertise  0 = Not advertised                                                                                                                                                                                                                                                                                                                                               |

|---|------------------------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | 10BASE- Te_Full_Duplex | RW | Ox1 | This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs: • Software reset is asserted by writing register 0x0 bit[15] • Restart Auto-Negotiation is triggered by writing register 0x0 bit[9] • The port is switched from power down to normal operation by writing register 0x0 bit[11] • Link goes down 1 = Advertise 0 = Not advertised |

| 5 | 10BASE- Te_Half_Duplex | RW | Ox1 | This bit is updated immediately after the writing operation; however the configuration does not take effect until any of the following occurs:  • Software reset is asserted by writing register 0x0 bit[15]  • Restart Auto-Negotiation is triggered by writing register 0x0 bit[9]  • The port is switched from power down to normal operation by writing register 0x0 bit[11]                                                |

|       |                                       |         |                   | Mo                                  |

|-------|---------------------------------------|---------|-------------------|-------------------------------------|

|       |                                       |         |                   | Link goes down                      |

|       |                                       |         |                   | 1 = Advertise                       |

|       |                                       |         |                   | 0 = Not advertised                  |

|       |                                       |         |                   |                                     |

|       |                                       |         |                   |                                     |

|       |                                       |         |                   |                                     |

| 4:0   | Selector_Field                        | RW      | 0x1               | Selector Field mode.                |

|       |                                       |         |                   | 00001 = IEEE 802.3                  |

|       |                                       |         |                   |                                     |

| PHY M | II 05H: AUTO-NEGOTI <i>A</i>          | TION LI | NK PARTN          | FR ABILITY 0X05                     |

| Bit   | Symbol                                | Access  | Default           | Description                         |

|       | · .                                   |         |                   | -                                   |

| 15    | 1000Base-X_Fd                         | RO      | 0x0               | Received Code Word Bit 15           |

|       | A A                                   | SWC     |                   | 1 = Link partner is capable of next |

|       |                                       |         |                   | page                                |

|       |                                       |         |                   | 0 = Link partner is not capable of  |

|       |                                       |         |                   | next page                           |

| 14    | ACK                                   | RO      | 0x0               | Acknowledge. Received Code          |

|       |                                       | SWC     |                   | Word Bit 14                         |

|       | V W                                   |         |                   | 1 = Link partner has received link  |

|       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |         |                   | code word                           |

|       | *                                     |         |                   | 0 = Link partner has not received   |

|       |                                       |         |                   | link code word                      |

| 13    | REMOTE_FAULT                          | RO      | 0x0               | Remote Fault. Received Code         |

|       | 竹台                                    | SWC     | <del>7</del> => ] | Word Bit 13                         |

|       | N./I                                  | atar    | Canar             | 1 = Link partner has detected       |

|       | IVI                                   | LUCI    | COHI              | remote fault                        |

|       |                                       |         |                   | 0 = Link partner has not detected   |

|       |                                       |         |                   | remote fault                        |

| 12    | RESERVED                              | RO      | 0x0               | Technology Ability Field.           |

| 12    | ALIGER ( ED                           | SWC     | 0.00              | Received Code Word Bit 12           |

|       |                                       |         |                   |                                     |

| 11    | ASYMMETRIC_PAUS                       | RO      | 0x0               | Technology Ability Field.           |

|       | E                                     | SWC     |                   | Received Code Word Bit 11           |

|       |                                       |         |                   | 1 = Link partner requests           |

|       |                                       |         |                   | asymmetric pause                    |

|       |                                       |         |                   | 0 = Link partner does not request   |

|    |                                       | •        | •               | Mo                                |

|----|---------------------------------------|----------|-----------------|-----------------------------------|

|    |                                       |          |                 | asymmetric pause                  |

| 10 | PAUSE                                 | RO       | 0x0             | Technology Ability Field.         |

| 10 | TAUSE                                 | SWC      | UXU             | Received Code Word Bit 10         |

|    |                                       | Swe      |                 | 1 = Link partner supports pause   |

|    |                                       |          |                 | operation                         |

|    |                                       |          |                 | 0 = Link partner does not support |

|    |                                       |          |                 | pause operation                   |

| 9  | 100BASE-T4                            | RO       | 0x0             | Technology Ability Field.         |

|    |                                       | SWC      |                 | Received Code Word Bit 9          |

|    | A                                     |          |                 | 1 = Link partner supports         |

|    | . A                                   |          |                 | 100BASE-T4                        |

|    |                                       |          |                 | 0 = Link partner does not         |