#### 1. DESCRIPTION

The XD/XL3485 is a 3.3V powered, half-duplex, low-power RS-485 transceivers that fully meets the requirements of the TIA/EIA-485 standard.

The XD/XL3485 consists of a driver and a receiver, both of which can be independently enabled and disabled. When both are disabled, both the driver and receiver

The XD/XL3485 has a 1/8 load, allowing 256 XD/XL3485 transceivers to be connected in parallel on the same communication bus. Error-free data transmission of up to 12 Mbps is possible.

The XD/XL3485 has an operating voltage range of 3.0~3.6 V. It is fail-safe, over-temperature protected, current-limited, and over-voltage protected.

#### 2. FEATURES

- 3.3V supply powered, half-duplex;

- 1/8 unit load, allowing up to 256 devices to be connected to the bus;

- Driver short-circuit output protection;

- Over-temperature protection function;

- Low-power shutdown function;

- Receiver open-circuit failure protection;

- High noise immunity;

- Integrated transient voltage resist function;

- Data rates up to 12 Mbps in electrically noisy environments;

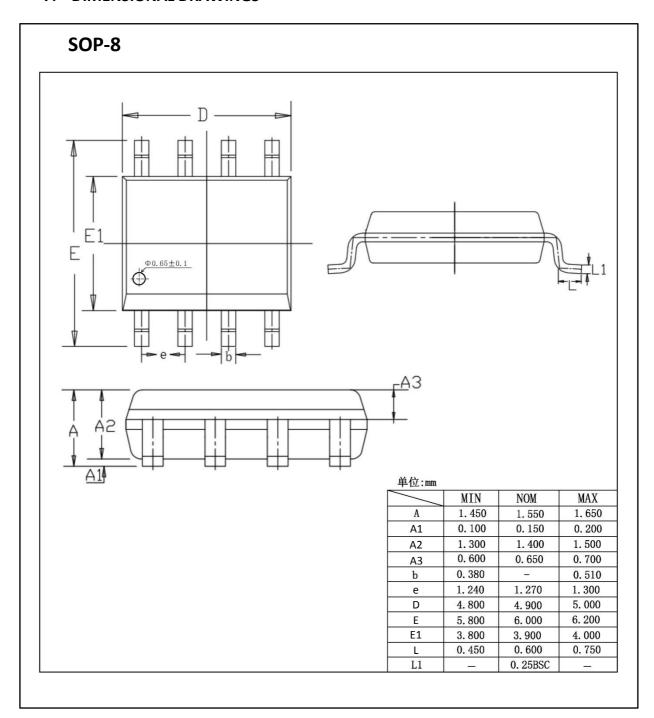

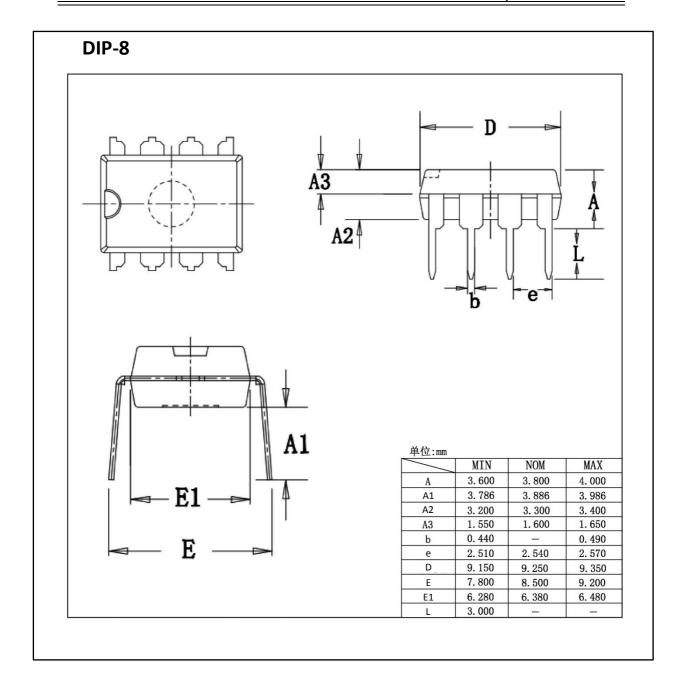

- SOP-8(XL3485), DIP-8(XD3485)

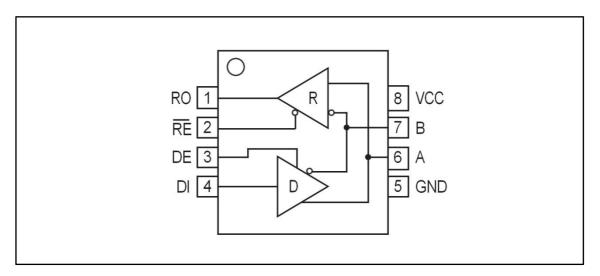

# 3. PIN CONFIGURATIONS AND FUNCTIONS

#### **Pin Functions**

| Pin | Name | Description                                                                                                                                                                                                                                                                              |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RO   | Receiver output.  When /RE is low, if A-B≧200mV, RO output is high; if A-B≦-200mV, RO output is low.                                                                                                                                                                                     |

| 2   | RE   | Receiver output enable control.  When /RE is low, the receiver output is enabled and the RO output is active; when /RE is high, the receiver output is disabled and the RO is in high resistance state;  When /RE is high and DE is low, the device enters the low power shutdown mode.  |

| 3   | DE   | Driver output enable control.  The driver output is active when DE is high, and the output is highly resistive when DE is low;  When /RE is high and DE is low, the device enters the low-power shutdown mode.                                                                           |

| 4   | DI   | DI driver input. When DE is high, a low level on DI will cause the driver in-phase terminal A output to be low and the driver inverting terminal B output to be high; a high level on DI will cause the in-phase terminal output to be high and the inverting terminal output to be low. |

| 5   | GND  | Ground                                                                                                                                                                                                                                                                                   |

| 6   | Α    | Receiver In-Phase Inputs and Driver In-Phase outputs                                                                                                                                                                                                                                     |

| 7   | В    | Receiver Inverting Inputs and Driver Inverting outputs                                                                                                                                                                                                                                   |

| 8   | Vcc  | Power supply                                                                                                                                                                                                                                                                             |

# 4. SPECIFICATIONS

# 4.1. Absolute Maximum Ratings

| PARAMETER                           | SYMBOL     | VALUE   | UNIT |

|-------------------------------------|------------|---------|------|

| Supply Voltage                      | VCC        | +7      | V    |

| Control Port Voltage                | RE, DE, DI | -0.3~+7 | V    |

| Bus-side input voltage              | A、B        | -7~13   | V    |

| Receiver output voltage             | RO         | -0.3~+7 | V    |

| Operating Temperature Range         |            | -40~85  | °C   |

| Storage operating temperature range |            | -55~150 | °C   |

| Welding temperature range           |            | 300     | °C   |

| Cartinana                           | SOP-8      | 400     | mW   |

| Continuous power consumption        | DIP-8      | 700     | mW   |

<sup>[1]</sup> Maximum Limit Parameter values are values above which irrecoverable damage to the device may occur. Under these conditions it is detrimental to the normal operation of the device, and continuous operation of the device at the maximum permissible ratings may affect the reliability of the device. the reference point for all voltages is ground.

www.xinluda.com 3 / 14 Rev 2.3

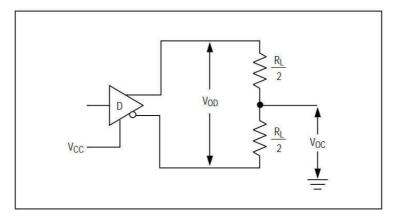

## 4.2. Driver DC Electrical Characteristics

| PARAMETER                                                    | SYMBOL | MBOL TEST CONDITIONS       |      | ТҮР | MAX | UNIT |

|--------------------------------------------------------------|--------|----------------------------|------|-----|-----|------|

| Driver Differential Output<br>(no load))                     | VOD1   |                            |      | 3.3 |     | V    |

| Drive Differential Outputs                                   | VOD2   | Figure 2,RL = 54Ω          | 1.5  |     | VCC |      |

| blive billerential outputs                                   | VODZ   | Figure 2, RL = 100 Ω       | 2    |     | VCC | V    |

| Change in output voltage<br>amplitude<br>(NOTE1)             | ΔVOD   | Figure 2,RL = 54 Ω         |      |     | 0.2 | V    |

| Output common mode voltage                                   | voc    | Figure 2,RL = 54 Ω         |      |     | 3   | V    |

| Change in common mode<br>output voltage amplitude<br>(NOTE1) | ΔVOC   | Figure 2, RL = $54 \Omega$ |      |     | 0.2 | V    |

| High Level Input                                             | VIH    | DE, DI, RE                 | 2.0  |     |     | V    |

| Low Level Input                                              | VIL    | DE, DI, RE                 |      |     | 0.8 | V    |

| Logic Input Current                                          | IIN1   | DE, DI, RE                 | -2   |     | 2   | uA   |

| Current at output short-circuit,<br>short-circuit to high    | IOSD1  | Short circuit to 0V~12V    |      |     | 250 | mA   |

| Current at output short-circuit, short-circuit to low        | IOSD2  | Short circuit to -7V~0V    | -250 |     |     | mA   |

| Over Temperature Shutdown<br>Threshold Temperature           |        |                            |      | 140 |     | °C   |

| Over-temperature shutdown hysteresis temperature             |        |                            |      | 20  |     | °C   |

( Unless otherwise specified, VCC=3.3V $\pm$ 10% ,Temp=TMIN~TMAX, typical value at VCC=+3.3V, Temp=25  $^{\circ}$ C)

NOTE1:  $\Delta$ VOD and  $\Delta$ VOC are the changes in the amplitude values of VOD and VOC, respectively, caused by changes in the state of the DI of the input signals.

# 4.3. Receiver DC Electrical Characteristics

| PARAMETER                               | SYMBOL | TEST CONDITIONS                          | MIN  | ТҮР | MAX | UNIT |

|-----------------------------------------|--------|------------------------------------------|------|-----|-----|------|

| Input current (A, B)                    | IIN2   | DE = 0 V,<br>VCC=0 or 3.3V<br>VIN = 12 V |      |     | 125 | uA   |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |        | DE = 0 V,<br>VCC=0 or 3.3V VIN = -7 V    | -100 |     |     | uA   |

www.xinluda.com 4 / 14 Rev 2.3

| Forward Input Threshold Voltage    | VIT+ | -7V≦VCM≦12V                     |         |    | +200 | mV |

|------------------------------------|------|---------------------------------|---------|----|------|----|

| Reverse Input Threshold<br>Voltage | VIT- | -7V≦VCM≦12V                     | -200    |    |      | mV |

| Input Hysteresis Voltage           | Vhys | -7V≦VCM≦12V                     | 10      | 30 |      | mV |

| High Level Output Voltage          | VOH  | IOUT = -2.5mA,<br>VID = +200 mV | VCC-1.5 |    |      | V  |

| Low Level Output Voltage           | VOL  | IOUT = +2.5mA,<br>VID = -200 mV |         |    | 0.4  | V  |

| Tri-state input leakage current    | IOZR | 0.4 V < VO < 2.4 V              |         |    | ±1   | uA |

| Receiver input resistance          | RIN  | -7V≦VCM≦12V                     | 96      |    |      | kΩ |

| Receiver short-circuit current     | IOSR | 0 V≤VO≤VCC                      | ±8      |    | ±60  | mA |

# 4.4. Supply Current

| PARAMETER        | SYMBOL            | TEST CONDITIONS    | MIN | ТҮР | MAX | UNIT |

|------------------|-------------------|--------------------|-----|-----|-----|------|

| Supply Current   | I <sub>CC1</sub>  | RE=0V,<br>DE = 0 V |     | 520 | 800 | uA   |

|                  | I <sub>CC2</sub>  | RE=VCC,<br>DE=VCC  |     | 540 | 700 | uA   |

| Shutdown current | I <sub>SHDN</sub> | RE=VCC,<br>DE=0V   |     | 0.5 | 10  | uA   |

# 4.5. Driver Switching Characteristics

| PARAMETER                                   | SYMBOL           | TEST CONDITIONS                            | MIN | ТҮР | MAX | UNIT |

|---------------------------------------------|------------------|--------------------------------------------|-----|-----|-----|------|

| Driver differential output delay            | t <sub>DD</sub>  | RDIFF = $60 \Omega$ ,                      |     | 10  | 35  | ns   |

| Driver Differential Output  Transition Time | t <sub>TD</sub>  | CL1=CL2=100pF<br>(See Figure 3 and 4)      |     | 12  | 25  | ns   |

| Drive propagation delay from                | t <sub>PLH</sub> |                                            |     | 8   | 35  | ns   |

| Drive propagation delay from high to low    | t <sub>PHL</sub> | RDIFF = $27 \Omega$ , (See Figure 3 and 4) |     | 8   | 35  | ns   |

| tPLH-tPHL                       | tPDS |                                           | 1   | 8   | ns |

|---------------------------------|------|-------------------------------------------|-----|-----|----|

| Enable to Output High           | tPZH | RL= 110Ω,                                 | 20  | 90  | ns |

| Enable to Output Low            | tPZL | (See Figure 5、6)                          | 20  | 90  | ns |

| Input low to forbidden energy   | tPLZ | RL= 110Ω,                                 | 20  | 80  | ns |

| Input high to forbidden energy  | tPHZ | (See Figure 5、6)                          | 20  | 80  | ns |

| Off condition, Enable to output | tDSH | RL= $110\Omega$ , (See Figure 5 $\sim$ 6) | 500 | 900 | ns |

| Off condition, Enable to output | tDSL | RL= $110\Omega$ , (See Figure 5 \( 6 \))  | 500 | 900 | ns |

# 4.6. Receiver Switching Characteristics

| PARAMETER                                                   | SYMBOL | TEST CONDITIONS                      | MIN | ТҮР | MAX  | UNIT |

|-------------------------------------------------------------|--------|--------------------------------------|-----|-----|------|------|

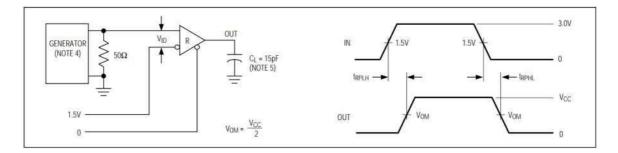

| Receiver input to output propagation delay from low to high | tRPLH  |                                      |     | 80  | 150  | ns   |

| Receiver input to output propagation delay from high to low | tRPHL  | CL=15pF<br>See Figure 7 and Figure 8 |     | 80  | 150  | ns   |

| tRPLH – tRPHL                                               | tRPDS  |                                      |     | 7   | 10   | ns   |

| Enable to Output Low Time                                   | tRPZL  | CL=15pF<br>See Figure 7 and Figure 8 |     | 20  | 50   | ns   |

| Enable to Output High Time                                  | tRPZH  | CL=15pF<br>See Figure 7 and Figure 8 |     | 20  | 50   | ns   |

| From low output to disabled time                            | tPRLZ  | CL=15pF<br>See Figure 7 and Figure 8 |     | 20  | 45   | ns   |

| From high output to disablement time                        | tPRHZ  | CL=15pF<br>See Figure 7 and Figure 8 |     | 20  | 45   | ns   |

| Enable to Output High Time in Off State                     | tRPSH  | CL=15pF<br>See Figure 7 and Figure 8 |     | 200 | 1400 | ns   |

| Enable to Output Low Time in Off State                      | tRPSL  | CL=15pF<br>See Figure 7 and Figure 8 |     | 200 | 1400 | ns   |

| Time to shutdown                                            | tSHDN  | NOTE2 80                             |     |     | 300  | ns   |

NOTE2: When the duration of /RE=1, DE=0 is less than 80ns, the device must not enter the shutdown state, when it is more than 300ns, it must enter the shutdown state.

# 4.7. Function Table

# Sending menu

| control                                |    | input | out         | put |  |  |

|----------------------------------------|----|-------|-------------|-----|--|--|

| /RE                                    | DE | DI    | А           | В   |  |  |

| х                                      | 1  | 1     | Н           | L   |  |  |

| х                                      | 1  | 0     | L H         |     |  |  |

| 0                                      | 0  | х     | z z         |     |  |  |

| 1                                      | 0  | х     | Z(shutdown) |     |  |  |

| X: arbitrary level; Z: high resistance |    |       |             |     |  |  |

## **Receiving menu**

| control |                   | input                 | output |  |  |  |  |  |

|---------|-------------------|-----------------------|--------|--|--|--|--|--|

| /RE     | DE                | A-B                   | RO     |  |  |  |  |  |

| 0       | Х                 | ≥200mV                | Ħ      |  |  |  |  |  |

| 0       | х                 | ≤-200mV               | L      |  |  |  |  |  |

| 0       | Х                 | Open/Short Circuit    | н      |  |  |  |  |  |

| 1 X     |                   | Х                     | Z      |  |  |  |  |  |

|         | X: arbitrary leve | l; Z: high resistance | !      |  |  |  |  |  |

# 4.8. Test Circuit

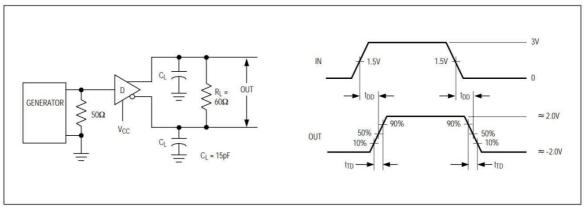

Figure 2 Driver DC Test Load

CL Contains probe and stray capacitance (below)

Figure. 3 Driver Differential Delay and Transition Time

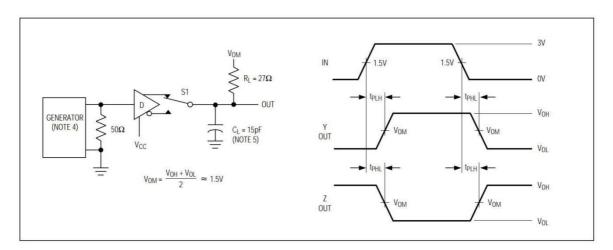

Figure 4 Driver propagation delay

www.xinluda.com 8 / 14 Rev 2.3

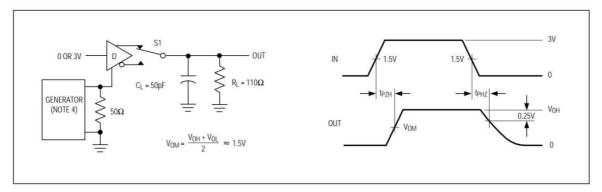

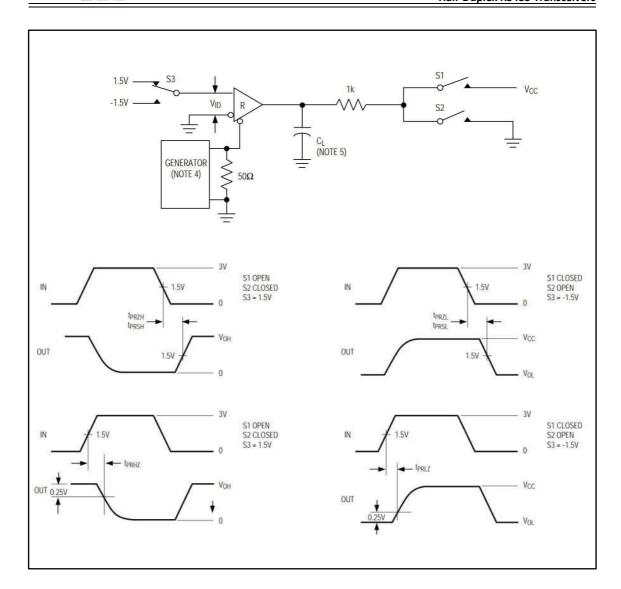

**Figure 5 Driver Enable and Disable Times**

**Figure 6 Driver Enable and Disable Times**

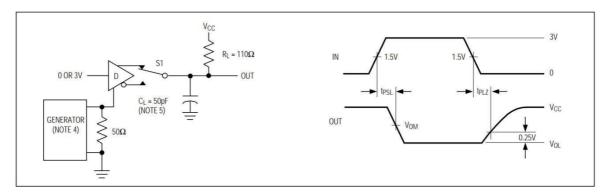

Figure. 7 Receiver propagation delay test circuit

www.xinluda.com 9 / 14 Rev 2.3

**Figure 8 Receiver Enable and Disable Times**

www.xinluda.com 10 / 14 Rev 2.3

#### 5. PRODUCT DESCRIPTION

#### 5.1. Brief Description

The XD/XL3485 is a half-duplex, high-speed transceivers for RS-485 communications, consisting of a driver and receiver. With fail-safe, over-voltage, over-current, and over-temperature protection, the XD/XL3485 achieves error-free data transmission up to 12Mbps.

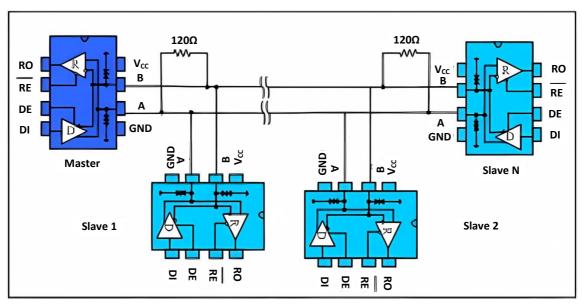

#### 5.2. 256 transceivers hooked up to the bus

Standard RS485 receivers have an input impedance of  $12k\Omega$  (1 unit load) and standard drivers can drive up to 32 unit loads. The XD/XL3485 transceivers has a receiver with 1/8 unit load input impedance (96k  $\Omega$ ), allowing up to 256 transceivers to be hooked up in parallel on the same communications bus. These devices can be combined in any combination, or with other RS485 transceivers, on the same bus as long as the total load does not exceed 32 unit loads.

## 5.3. Driver output protection

Two mechanisms are used to avoid excessive output current and power consumption caused by faults or bus conflicts. First, overcurrent protection, which provides fast short-circuit protection over the entire common-mode voltage range (referenced to typical operating characteristics). Second, a thermal shutdown circuit that forces the driver outputs into a high resistance state when the core temperature exceeds 140°C.

#### 5.4. Typical Applications

Bus-based networking: The XD/XL3485 RS485 transceivers is designed for bi-directional data communication over a multi-point bus transmission line. Figure 9 shows a typical networking application circuit. These devices can also be used as linear transponders for cable lengths longer than 4000 ft. To minimise reflections, the transmission line should be terminated with its characteristic impedance at both ends, and the lengths of branch connections off the trunk should be as short as possible.

Figure 9 Bus RS485 half-duplex communication network

<u>www.xinluda.com</u> 11 / 14 Rev 2.3

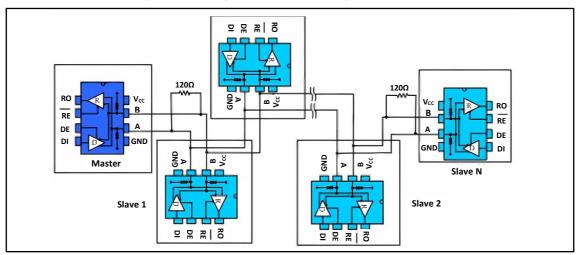

**Hand-in-hand networking:** also known as daisy-chain topology, is the standard and specification for RS485 bus cabling, and is the RS485 bus topology recommended by TIA and other organisations. Its wiring is the master control device and multiple slave control devices to form a hand in hand connection, as shown in Figure 10, do not leave a branch is the hand in hand way. This wiring method has the advantages of small signal reflection and high communication success rate.

Figure 10 Handshake RS485 half-duplex communication network

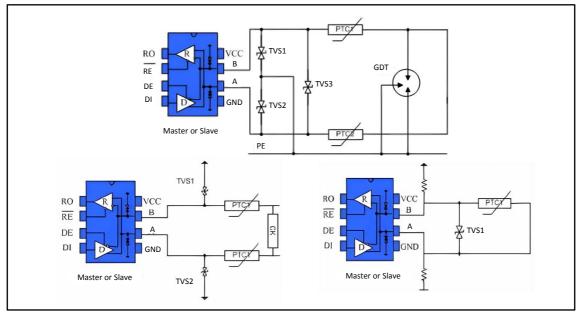

**Bus port protection:** In harsh environments, RS485 communication ports are usually well protected against static electricity, lightning surge protection and other additional protection, and even need to prevent 380V mains access solutions to avoid damage to smart meters and industrial control hosts. Figure 11 shows three common RS485 bus port protection scheme. The first is a three-stage protection scheme in which the AB port is connected in parallel with a TVS device to the protection ground, a TVS device is connected in parallel between the AB ports, a thermistor is connected in series with the AB port, and a gas discharge tube is connected in parallel to the protection ground. The third one is the scheme of connecting upper and lower pull-down resistors to the power supply and ground respectively, connecting TVS between AB, and connecting thermistor to one of the ports of A or B.

Figure 11 Port protection scheme

www.xinluda.com 12 / 14 Rev 2.3

# 6. ORDERING INFORMATION

## **Ordering Information**

| Part<br>Number | Device<br>Marking | Package<br>Type | Body size<br>(mm) | Temperature<br>(°C) | MSL  | Transport<br>Media | Package<br>Quantity |

|----------------|-------------------|-----------------|-------------------|---------------------|------|--------------------|---------------------|

| XL3485         | XL3485            | SOP-8           | 4.90 * 3.90       | -40 to +85          | MSL3 | T&R                | 2500                |

| XD3485         | XD3485            | DIP-8           | 9.25 * 6.38       | -40 to +85          | MSL3 | Tube 50            | 2000                |

#### 7. DIMENSIONAL DRAWINGS