# PES2200-12-080xA AC-DC Front-End Power Supply

The PES2200-12-080xA is a 2200 Watt AC to DC, power-factorcorrected (PFC) power supply that converts standard AC power into a main output of +12 VDC for powering intermediate bus architectures (IBA) in high performance and reliability servers, routers, and network switches.

The PES2200-12-080xA utilizes full digital control architecture for greater efficiency, control, and functionality.

This power supply meets international safety standards and displays the CE-Mark for the European

Low Voltage Directive (LVD).

#### **Key Features & Benefits**

- High Efficiency, meet 80 plus "Platinum" efficiency requirement

- Auto-selected input voltage ranges: 90-140 VAC, 180-264 VAC

- AC input with active power factor correction

- 2200 W continuous output power capability

- Always-on 12 VSB / 3.5 A standby output

- Hot-plug capable

- Parallel operation with active current sharing

- Full digital controls for improved performance

- High power density design: 59 W/in<sup>3</sup>

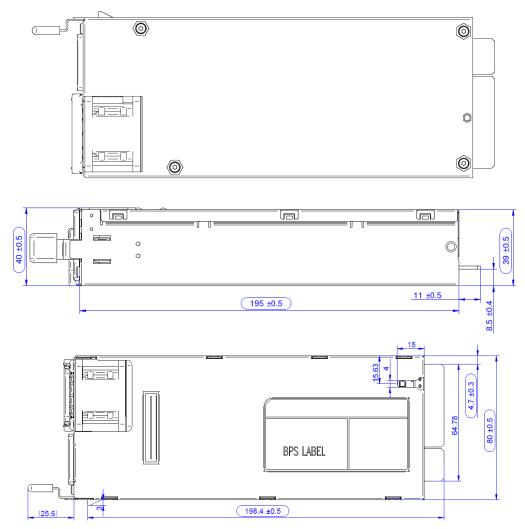

- Small form factor: 80 x 40 x 195 mm (3.15 x 1.57 x 7.68 in)

- Power Management Bus communication interface for control, programming and monitoring

- Status LED with fault signaling

#### **Applications**

- Networking Switches

- Servers & Routers

- Telecommunications

#### **1. ORDERING INFORMATION**

| PES            | 2200        | -    | 12        | -    | 080   | x                                                   | Α     | x                           |

|----------------|-------------|------|-----------|------|-------|-----------------------------------------------------|-------|-----------------------------|

| Product Family | Power Level | Dash | V1 Output | Dash | Width | Airflow                                             | Input | Specific code <sup>3</sup>  |

| PES Front-Ends | 2200 W      |      | 12 V      |      | 80 mm | N: Normal <sup>1)</sup><br>R: Reverse <sup>2)</sup> | A: AC | x = Blank<br>x = S+3 digits |

<sup>1</sup> "N" Normal Airflow (NAF) from Output connector to Input DC socket

Ordering PN: PES2200-12-080NA

<sup>2</sup> "R" Reverse Airflow (RAF) from Input DC socket to Output connector

Ordering PN: PES2200-12-080RA

<sup>3</sup> Contact factory for availability of Specific code

Ordering PN: PES2200-12-080NAS474

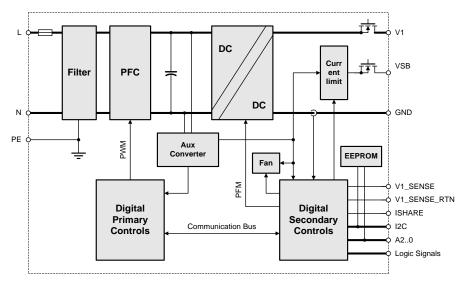

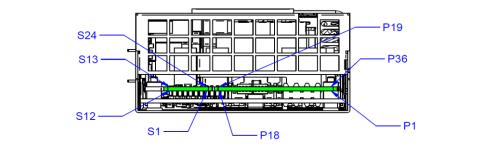

#### 2. OVERVIEW

The PES2200-12-080xA AC/DC power supply is a fully DSP controlled, highly efficient front-end power supply. It incorporates resonance-soft-switching technology to reduce component stresses, providing increased system reliability and very high efficiency. With a wide input operational voltage range the PES2200-12-080xA maximizes power availability in demanding server, network, and other high availability applications. The supply is fan cooled and ideally suited for integration with a matching airflow path.

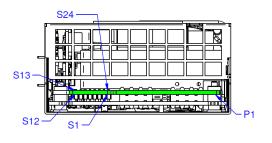

The PFC stage is digitally controlled using a state-of-the-art digital signal processing algorithm to guarantee best efficiency and unity power factor over a wide operating range. The DC/DC stage uses soft switching resonant techniques in conjunction with synchronous rectification. An active OR-ing device on the output ensures no reverse load current and renders the supply ideally suited for operation in redundant power systems. The always-on standby output provides power to external power distribution and management controllers. It is protected with an active OR-ing device for maximum reliability.

Status information is provided with a front-panel LED. In addition, the power supply can be controlled and the fan speed set via the I<sup>2</sup>C bus. The I<sup>2</sup>C bus allows full monitoring of the supply, including input and output voltage, current, power, and inside temperatures. Cooling is managed by a fan controlled by the DSP controller. The fan speed is adjusted automatically depending on the actual power demand and supply temperature and can be overridden through the I<sup>2</sup>C bus.

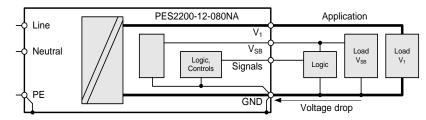

Figure 1. PES2200-12-080xA Block Diagram

#### 3. ABSOLUTE MAXIMUM RATINGS

Stresses in excess of the absolute maximum ratings may cause performance degradation, adversely affect long-term reliability, and cause permanent damage to the supply.

| PARAME  | TER           | CONDITIONS / DESCRIPTION | MIN | MAX | UNITS |

|---------|---------------|--------------------------|-----|-----|-------|

| Vi maxc | Maximum Input | Continuous               |     | 264 | VAC   |

#### 4. INPUT

General Condition:  $T_A = 0...50$  °C, unless otherwise noted.

| PARAME         | TER                                 | DESCRIPTION / CONDITION                                                                                | MIN  | NOM   | MAX | UNIT |

|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------|------|-------|-----|------|

| Vinom          | AC Nominal Input Voltage            | Rated Voltage High Line (Vinom HL)                                                                     | 200  | 230   | 240 | VAC  |

| <b>v</b> i nom | AC Nominal input voltage            | Rated Voltage Low Line (Vinom LL)                                                                      | 100  | 115   | 127 | VAC  |

| Vinom DC       | DC Nominal Input Voltage            | Rated HVDC                                                                                             |      | 240   |     | VDC  |

| ViDC           | DC Input Voltage range              | Normal operating ( $V_{i min}$ to $V_{i max}$ )                                                        | 180  |       | 300 | VDC  |

| Vi             | Input Voltage Ranges                | Normal operating (Vi min HL to Vi max HL), High Line                                                   | 180  |       | 264 | VAC  |

| Vi             | input voltage Ranges                | Normal operating (Vi min LL to Vi max LL), Low Line                                                    | 90   |       | 140 | VAC  |

| ,              | Maximum langet Commant              | $V_{IN} = 90$ VAC, $I_{1} = 96$ A, $I_{SB} = 3.5$ A                                                    |      |       | 15  | ARMS |

| li max         | Maximum Input Current               | $V_{IN} = 180 \text{ VAC}, I_7 = 183 \text{ A}, I_{SB} = 3.5 \text{ A}$                                |      |       | 14  | ARMS |

| li inrush      | Inrush Current Limitation           | $Vi \min$ to $Vi \max$ , $T_{\rm NTC} = 25^{\circ}$ C, 5 ms                                            |      |       | 50  | Ap   |

| $f_i$          | Input Frequency                     |                                                                                                        | 47   | 50/60 | 63  | Hz   |

|                |                                     | Vi = 230 VAC, 50 Hz and 60 Hz, $Vi$ = 115 VAC,60 Hz                                                    |      |       |     |      |

|                |                                     | 10% Load                                                                                               | 0.8  |       |     | W/VA |

| PF             | Power Factor                        | 20% Load                                                                                               | 0.9  |       |     | W/VA |

|                |                                     | 50% Load                                                                                               | 0.9  |       |     | W/VA |

|                |                                     | 100% Load                                                                                              | 0.95 |       |     | W/VA |

| Vi on          | Turn-on Input Voltage <sup>1</sup>  | Ramping up                                                                                             | 85   |       | 90  | VAC  |

| Vi off         | Turn-off Input Voltage <sup>1</sup> | Ramping down                                                                                           | 80   |       | 85  | VAC  |

|                |                                     | V <sub>IN</sub> = 230 VAC, 10% load                                                                    | 82   |       |     | %    |

|                | Efficiency 2                        | V <sub>IN</sub> = 230 VAC, 20% load                                                                    | 90   | 94    |     | %    |

| η              | Efficiency <sup>2</sup>             | V <sub>IN</sub> = 230 VAC, 50% load                                                                    | 94   | 95    |     | %    |

|                |                                     | V <sub>IN</sub> = 230 VAC, 100% load                                                                   | 91   | 93    |     | %    |

| τ              | Hold up Time 14                     | <i>V</i> <sub><i>IN</i></sub> = 230 VAC, <i>I</i> <sub>1</sub> = 183 A, <i>I</i> <sub>SB</sub> = 3.5 A | 11   |       |     | ms   |

| Tv1 holdup     | Hold-up Time V1                     | <i>V</i> <sub>IN</sub> = 115 VAC, <i>I</i> <sub>1</sub> = 96 A, <i>I</i> <sub>SB</sub> = 3.5 A         | 11   |       |     | ms   |

| TVSB holdup    | Hold-up Time VSB                    | 12 V <sub>SB</sub> , full load                                                                         | 70   |       |     | ms   |

|                |                                     |                                                                                                        |      |       |     |      |

#### 4.1 INPUT FUSE

Time-lag 20 A input fuse (5.4 x 22.5 mm) in series with the L-line inside the power supply protects against severe defects. The fuse is not accessible from the outside and is therefore not a serviceable part.

#### **4.2 INRUSH CURRENT**

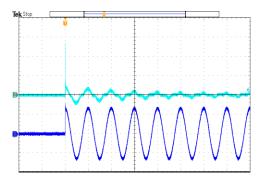

The AC-DC power supply exhibits an X capacitance of only 5.9  $\mu$ F, resulting in a low and short peak current, when the supply is connected to the mains. The internal bulk capacitor will be charged through a PTC which will limit the inrush current.

**NOTE:** Do not repeat plug-in / out operations within a short time, or else the internal in-rush current limiting device (NTC) may not sufficiently cool down.

<sup>&</sup>lt;sup>2</sup> Efficiency measured without fan power per EPA server guidelines.

Asia-Pacific

Europe, Middle East

+86 755 298 85888

+353 61 225 977

North America +1 408 785 5200

BCD.01005\_A

<sup>&</sup>lt;sup>1</sup> The Front-End is provided with a typical hysteresis of 5 VAC during turn-on and turn-off within the ranges.

PSU will restart once input voltage within the Vion.

#### 4.3 INPUT UNDER-VOLTAGE

If the sinusoidal input voltage stays below the input under voltage lockout threshold Vi on, the supply will be inhibited. Once the input voltage returns within the normal operating range, the supply will return to normal operation again.

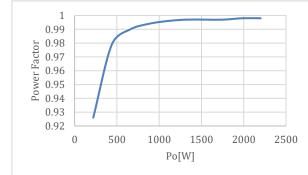

#### **4.4 POWER FACTOR CORRECTION**

Power factor correction (PFC) is achieved by controlling the input current waveform synchronously with the input voltage. A fully digital controller is implemented giving outstanding PFC results over a wide input voltage and load ranges. The input current will follow the shape of the input voltage. If for instance the input voltage has a trapezoidal waveform, then the current will also show a trapezoidal waveform.

#### 4.5 EFFICIENCY

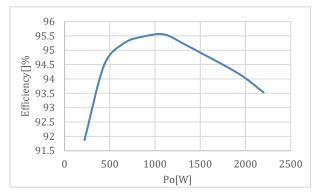

High efficiency (see *Figure 2*) is achieved by using state-of-the-art silicon power devices in conjunction with soft-transition topologies minimizing switching losses and a full digital control scheme. Synchronous rectifiers on the output reduce the losses in the high current output path. The speed of the fan is digitally controlled to keep all components at an optimal operating temperature regardless of the ambient temperature and load conditions.

Figure 2. Efficiency vs. Load (ratio metric loading)

Figure 3. Power factor vs. Load

Figure 4. Inrush current, Vin = 230Vac, 90° CH1: Vin (250V/div), CH2: Iin (10A/div)

#### **4.6 INPUT LINE CURRENT HARMONIC**

The power supply shall meet the requirements of EN61000-3-2 Class A and the Guidelines for the Suppression of Harmonics in Appliances and General Use Equipment Class A for harmonic line current content at full rated power.

|                                           | Per: EN 61000-3-2                                                  | Per: JEIDA MITI                                                   |

|-------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|

| Harmonic Order<br>n                       | Maximum permissible Harmonic<br>current at 230 VAC / 50 Hz in Amps | Maximum permissible Harmonic current at 100 VAC /50 Hz in Amps    |

|                                           | Odd Harmoni                                                        | ics                                                               |

| 3<br>5<br>7<br>9<br>11<br>13<br>15≤ n ≤39 | 2.3<br>1.14<br>0.77<br>0.4<br>0.33<br>0.21<br>0.15x (15/n)         | 5.29<br>2.622<br>1.771<br>0.92<br>0.759<br>0.483<br>0.345x (15/n) |

| 13211239                                  | Even Harmon                                                        | · · · · · · · · · · · · · · · · · · ·                             |

| 2<br>4<br>6<br>8≤ n ≤40                   | 1.08<br>0.43<br>0.3<br>0.23x (8/n)                                 | 2.484<br>0.989<br>0.69<br>0.529x (8/n)                            |

Table 1. Harmonic Limits for Class A Equipment

#### **4.7 AC LINE TRANSIENT SPECIFICATION**

AC line transient conditions shall be defined as "sag" and "surge" conditions. "Sag" conditions are also commonly referred to as "brownout", these conditions will be defined as the AC line voltage dropping below nominal voltage conditions. "Surge" will be defined to refer to conditions when the AC line voltage rises above nominal voltage. The power supply shall meet the requirements under the following AC line sag and surge conditions.

#### AC Line Sag (10 sec interval between each sagging)

| Duration            | Sag  | Operating AC Voltage      | Line<br>Frequency | Performance Criteria                          |

|---------------------|------|---------------------------|-------------------|-----------------------------------------------|

| 0 to 1/2 AC cycle   | 95%* | Nominal AC Voltage ranges | 50/60 Hz          | No loss of function or performance            |

| 1 AC cycle to 500ms | >30% | Nominal AC Voltage ranges | 50/60 Hz          | Loss of function acceptable, self-recoverable |

\* Comment: for 95% sag condition, the load is 80%.

#### AC Line Surge

| Duration          | Surge | Operating AC Voltage             | Line<br>Frequency | Performance Criteria               |

|-------------------|-------|----------------------------------|-------------------|------------------------------------|

| Continuous        | 10%   | Nominal AC Voltages              | 50/60 Hz          | No loss of function or performance |

| 0 to 1/2 AC cycle | 30%   | Mid-point of nominal AC Voltages | 50/60 Hz          | No loss of function or performance |

Table 2. AC Line Transient Performance

Asia-Pacific Europe, Middle East +86 755 298 85888 +353 61 225 977

**North America** +1 408 785 5200

BCD.01005\_A

#### 5. OUTPUT

General condition:  $T_A$  = 0...50 °C,  $V_{i}$  = 230 VAC unless otherwise noted.

|                                          |                                                    |                                                                                                                                                             | D. ALD L | Nov  |                   |                            |

|------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------------------|----------------------------|

| PARAME                                   |                                                    | DESCRIPTION / CONDITION                                                                                                                                     | MIN      | NOM  | MAX               | UNIT                       |

| Main Out                                 |                                                    |                                                                                                                                                             | _        | 10.0 | _                 | VDC                        |

| V <sub>1 nom</sub><br>V <sub>1 set</sub> | Nominal Output Voltage<br>Output Setpoint Accuracy | $0.5 \cdot I_{1 \text{ nom}}, T_A = 25^{\circ}\text{C}$                                                                                                     | -1       | 12.0 | +1                | ۷DC<br>%V <sub>1 nom</sub> |

| dV1 load                                 | Load Regulation                                    | 0 to 100% l1 nom                                                                                                                                            |          |      | 240               | mV                         |

| dV1 line                                 | Line Regulation                                    | Vimin LL to Vimax HL                                                                                                                                        |          |      | 120               | mV                         |

| dV <sub>1 tot</sub>                      | Total Regulation                                   | $V_{imin}$ to $V_{imax}$ , 0 to 100% $I_{1nom}$                                                                                                             | -5       |      | +5                | %V₁ nom                    |

|                                          |                                                    | Vimin HL to Vimax HL                                                                                                                                        |          | 2200 |                   | W                          |

| P <sub>1 nom</sub>                       | Nominal Output Power                               | $V_{iminLL}$ to $V_{imaxLL}$                                                                                                                                |          | 1155 |                   | W                          |

| I <sub>1 peak</sub>                      | Peak Output Loading                                | $V_{i \min HL}$ to $V_{i \max HL}$ (max 20 s)<br>$V_{i \min HL}$ to $V_{i \max HL}$ (max 100 µs)<br>$V_{i \min LL}$ to $V_{i \max LL}$ (max 20 s)           |          |      | 205<br>300<br>115 | ADC<br>ADC<br>ADC          |

| I <sub>1 nom</sub>                       | O day t O mark                                     | Vimin HL to Vimax HL                                                                                                                                        | 0.0      |      | 183               | ADC                        |

| It nom red                               | Output Current                                     | Vimin LL to Vimax LL                                                                                                                                        | 0.0      |      | 96                | ADC                        |

| V1 pp                                    | Output Ripple Voltage <sup>3</sup>                 | Vimin to Vimax, 0 to 100% /1 nom, 20MHz Bandwidth                                                                                                           |          |      | 150               | mVpp                       |

| dl1 share                                | Current Sharing                                    | Deviation from $h_{tot}$ / N, $h$ > 20%                                                                                                                     | -5       |      | +5                | % <i>I</i> 1 nom           |

| VISHARE                                  | Current Share Bus Voltage                          | I <sub>1 nom</sub>                                                                                                                                          |          | 8    |                   | VDC                        |

| dV <sub>1 dyn</sub>                      | Dynamic Load Regulation                            | Test frequency between 50 Hz and 5 kHz at duty cycles from 10% to 90%, $\Delta$ I1 = 60% I1 <sub>nom</sub> , I1 = 3 A 100%                                  | 11.40    |      | 12.60             | VDC                        |

| trec                                     | Recovery Time                                      | $I1_{nom}$ , 2000 µF capacitive loading<br>dI1/dt = 0.25 A/µs, recovery within 1% of V1 <sub>nom</sub>                                                      |          |      | 2                 | ms                         |

| tv1 rise                                 | Output Voltage Rise Time                           | $V_1 = 1090\% V_{1 \text{ nom}}$                                                                                                                            | 1        |      | 70                | ms                         |

| tv1 ovr sh                               | Output Turn-on Overshoot                           | Vinom HL, 0 to 100% /1 nom                                                                                                                                  |          |      | 0.6               | V                          |

| dV1 sense                                | Remote Sense                                       | Compensation for cable drop, 0 to 100% <i>I</i> <sub>1 nom</sub>                                                                                            |          |      | 0.25              | V                          |

| $C_{V1 \ load}$                          | Capacitive Loading                                 |                                                                                                                                                             |          |      | 22                | mF                         |

| Standby (                                | Output VsB                                         |                                                                                                                                                             |          |      |                   |                            |

| V <sub>SB nom</sub>                      | Nominal Output Voltage                             | $0.5 \cdot I_{SB nom}, T_A = 25^{\circ} \text{C}$                                                                                                           |          | 12.0 |                   | VDC                        |

| V <sub>SB set</sub>                      | Output Setpoint Accuracy                           | 0.45 1000/ ICD north                                                                                                                                        | -1       |      | +1                | %V <i>SBnom</i>            |

| <i>dVsb</i> load                         | Load Regulation                                    | 0 to 100% ISB nom                                                                                                                                           |          |      | 480               | mV                         |

| dV <sub>sb</sub> line                    | Line Regulation                                    | ViminLL to Vimax HL                                                                                                                                         | <b>-</b> |      | 120               | mV                         |

| dV <sub>SB tot</sub>                     | Total Regulation                                   | $V_{imin}$ to $V_{imax}$ , 0 to 100% $I_{SB nom}$                                                                                                           | -5       | 40   | +5                | %V <sub>SBnom</sub>        |

| P <sub>SB nom</sub>                      | Nominal Output Power                               | V <sub>i</sub> min to V <sub>imax</sub>                                                                                                                     |          | 42   | 4                 | W                          |

| ISB peak                                 | Peak Output Loading                                | Vimin LL to Vimax HL                                                                                                                                        | 0.0      |      | 4                 | ADC                        |

| ISB nom                                  | Output Current                                     | Vimin to Vimax                                                                                                                                              | 0.0      |      | 3.5               | ADC                        |

| V <sub>SB pp</sub>                       | Output Ripple Voltage <sup>3</sup>                 | <i>Vi min</i> to <i>Vi max</i> , 0 to 100% <i>ISB nom</i> , 20 MHz bandwidth                                                                                | 44.10    |      | 120               | mVpp                       |

| dVsB dyn                                 | Dynamic Load Regulation                            | $\Delta k_{\rm SB} = 50\% k_{\rm SB nom}, k_{\rm SB} = 0 \dots 100\% k_{\rm SB nom},$<br>d k_{\rm SB}/dt = 0.25A/µs, recovery within 1% of $k_{\rm SB nom}$ | 11.40    |      | 12.60             | VDC                        |

| t <sub>rec</sub>                         | Recovery Time                                      |                                                                                                                                                             | _        |      | 2                 | ms                         |

| t <sub>VSB rise</sub>                    | Output Voltage Rise Time                           | $V_{\rm SB} = 1090\% V_{\rm SB nom},$                                                                                                                       | 5        |      | 10                | ms                         |

| t <sub>VSB ovr sh</sub>                  | Output Turn-on Overshoot                           | Vinom HL, 0 to 100% ISB nom                                                                                                                                 |          |      | 0.6               | V                          |

| $C_{VSB}$ load                           | Capacitive Loading                                 |                                                                                                                                                             |          |      | 1000              | μF                         |

3 Ripple noise and dynamic load measured with a 10 µF low ESR capacitor in parallel with a 0.1 µF ceramic capacitor at the point of measurement.

tech.support@psbel.com belfuse.com/power-solutions

#### 5.1 OUTPUT GROUND / CHASSIS CONNECTION

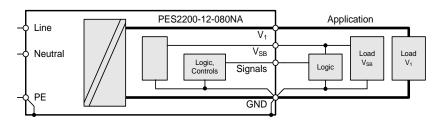

The output return path serves as power and signal ground. All output voltages and signals are referenced to these pins. To prevent a shift in signal and voltage levels due to ground wiring voltage drop a low impedance ground plane should be used as shown in Figure 5. Alternatively, separated ground signals can be used as shown in Figure 6. In this case the two ground planes should be connected together at the power supplies ground pins.

#### NOTE:

Within the power supply the output GND pins are connected to the Chassis, which in turn is connected to the Protective Earth terminal on the AC inlet. Therefore, it is not possible to set the potential of the output return (GND) to any other than Protective Earth potential.

Figure 5. Common Low Impedance Ground Plane

Figure 6. Separated Power and Signal Ground

#### 5.2 CLOSED LOOP STABILITY

The power supply shall be unconditionally stable under all line/load/transient load conditions including capacitive load ranges. A minimum of: 45 degrees phase margin and -6dB-gain margin is required. The power supply manufacturer shall provide proof of the unit's closed-loop stability with local sensing through the submission of Bode plots. Closed-loop stability must be ensured at 10%, 20%, 50% and 100% loads as applicable, 0% is just for reference.

#### 5.3 RESIDUAL VOLTAGE IMMUNITY IN STANDBY MODE

The power supply should be immune to any residual voltage placed on its outputs (Typically a leakage voltage through the system from standby output) up to 500 mV. There shall be no additional heat generated, nor stressing of any internal components with this voltage applied to any individual or all outputs simultaneously. It also should not trip the protection circuits during turn on.

The residual voltage at the power supply outputs for no load condition shall not exceed 100mV when AC voltage is applied and the PSON\_L signal is de-asserted.

#### 5.4 COMMON MODE NOISE

The common mode noise on any output shall not exceed 350 mV pk-pk over the frequency band of 10 Hz to 20 MHz.

The measurement shall be made across a 100  $\Omega$  resistor between each of DC outputs, including ground at the DC power connector and chassis ground (power subsystem enclosure), the test set-up shall use a FET probe such as Tektronix model P6046 or equivalent.

Asia-Pacific Europe, Middle East North America +353 61 225 977 +86 755 298 85888

+1 408 785 5200 BCD.01005\_A

#### 5.5 SOFT STARTING

The Power Supply shall contain control circuit which provides monotonic soft start for its outputs without overstress of the AC line or any power supply components at any specified AC line or load conditions.

#### 5.6 ZERO LOAD STABILITY REQUIREMENTS

When the power subsystem operates in a no load condition, it does not need to meet the output regulation specification, but it must operate without any tripping of over-voltage or other fault circuitry. When the power subsystem is subsequently loaded, it must begin to regulate and source current without fault.

#### 5.7 HOT SWAP REQUIREMENTS

Hot swapping a power supply is the process of inserting and extracting a power supply from an operating power system. During this process the output voltages shall remain within the limits with the capacitive load specified. The hot swap test must be conducted when the system is operating under static, dynamic, and zero loading conditions. The power supply shall use a latching mechanism to prevent insertion and extraction of the power supply when the AC power cord is inserted into the power supply.

#### 5.8 FORCED LOAD SHARING

The PES front-ends have an active current share scheme implemented for V1. All the ISHARE current share pins need to be interconnected in order to activate the sharing function. If a supply has an internal fault or is not turned on, it will disconnect its ISHARE pin from the share bus. This will prevent dragging the output down (or up) in such cases.

The current share function uses an analog bus to transmit and receive current share information. The controller implements a Master/Slave current share function. The power supply providing the largest current among the group is automatically the Master. The other supplies will operate as Slaves and increase their output current to a value close to the Master by slightly increasing their output voltage. The voltage increase is limited to +250 mV. The output will share within 10% at full load.

The 12 VSB output is not required to actively share current between power supplies (passive sharing).

#### 5.9 RIPPLE / NOISE

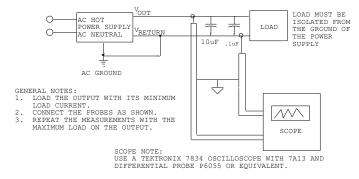

The test set-up shall be following Figure 7.

Figure 7. Differential Noise Test Setup

NOTE: Load must be isolated from the safety ground to Figure 7.

NOTE: When performing this test, the probe clips and capacitors should be located close to the load.

#### 6. PROTECTION

| PARAME              | TER                                    | DESCRIPTION / CONDITION                                    | MIN                  | NOM                | MAX   | UNIT |

|---------------------|----------------------------------------|------------------------------------------------------------|----------------------|--------------------|-------|------|

| F                   | Input fuse (L)                         | Not use accessible, time-lag (T)                           |                      | 20                 |       | А    |

| V1 OV               | OV Threshold V1                        | Over Voltage V1 Protection, Latch-off Type                 | 13.0                 | 13.0 13.9 14.5     |       | VDC  |

| Vvsb ov             | OV Threshold VSB                       | Over Voltage $V_{SB}$ Protection, Automatic recovery Type  | 13.0                 | 13.0 13.9 14.5     |       | VDC  |

| V1 UV               | UV Threshold V1                        | Under Voltage V1 Protection, Latch-off Type                | 11.2                 |                    | VDC   |      |

| V <sub>VSB UV</sub> | UV Threshold VSB                       | Under Voltage $V_{SB}$ Protection, Automatic recovery Type | 11.2                 |                    |       | VDC  |

| lv1 oc              | OC Limit V1                            | Over Current Limitation, Latch-off, Vimin HL to Vimax HL   | Defende eachier C /  |                    |       | ADC  |

| IV1 OC              |                                        | Over Current Limitation, Latch-off, Vimin LL to Vimax LL   | Refer to section 6.5 |                    | 0.0   | ADC  |

| Ivsb oc             | OC Limit VSB                           | Over Current Limitation, Automatic recovery Type           | 4.5 5.5              |                    | А     |      |

| T <sub>SD</sub>     | Over Temperature On<br>Critical Points | Automatic shut-down                                        | Re                   | fer to <i>Tabl</i> | le 11 | °C   |

#### 6.1 PROTECTION CIRCUITS

Protection circuits inside the power supply shall cause only the power supply's main output to shut down. If the power supply latches off due to a protection circuit tripping, an AC cycle OFF for 15 sec and a PSON\_L cycle HIGH for 1 sec shall be able to reset the power supply.

#### 6.2 OVER TEMPERATURE PROTECTION (OTP)

The power supply will be protected against over temperature conditions caused by loss of fan cooling or excessive ambient temperature.

In an OTP condition the PSU will shut down, OT warning SMB\_ALERT\_L assertion must always precede the OTP shutdown, when the power supply temperature drops to within specified limits, the power supply shall restore power automatically, while the 12 VSB remains always on, the OTP circuit must have built in margin such that the power supply will not oscillate on and off due to temperature recovering condition, the OTP trip temperature level shall be at least 5degC higher than SMB\_ALERT\_L over temperature warning threshold level.

#### 6.3 OVER VOLTAGE PROTECTION

The PES2200-12-080xA front-end provides a fixed threshold overvoltage (OV) protection implemented with a HW comparator for both the main and the standby output. Once an OV condition has been triggered on the main output, the supply will shut down and latch the fault condition. The latch can be unlocked by disconnecting the supply from the AC mains or by toggling the PSON\_L input. 12 VSB will be auto-recovered after removing OVP limit.

#### 6.4 UNDER VOLTAGE DETECTION

Both main and standby outputs are monitored. LED and PWOK\_H pin signal if the output voltage exceeds ±5% of its nominal voltage.

The main output will latch off if the main output voltage V<sub>1</sub> falls below 11.2 V (typically in an overload condition), The latch can be unlocked by disconnecting the supply from the AC mains or by toggling the PSON\_L input.

If the standby output leaves its regulation bandwidth for more than 10 ms then the main output is disabled to protect the system.

#### 6.5 Current limitation

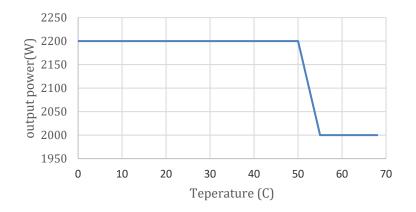

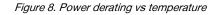

The main output current limitation level IV1 lim will decrease if the ambient (inlet) temperature increases beyond 50 °C (see Figure 8 and Table 3). Note that the current limitation on V1 will kick in at a current level approximately 10A-16A higher nominal output current that is shown.

The 2nd protection is a substantially rectangular output characteristic controlled by a software feedback loop. This protects the power supply and system during the 20s peak load. after the 20s goes out, the supply will shut down.

The 3rd protection is a substantially rectangular output characteristic controlled by a software feedback loop. This protects the power supply and system during the 20ms blanking time of the static over current protection. If the output current is rising fast and reaches IV1 lim, the supply will immediately shut down.

Asia-Pacific Europe, Middle East North America +86 755 298 85888 +353 61 225 977

+1 408 785 5200

When the main output over current, the V1 will shut down and latch off. The latch can be cleared by recycling the input voltage or the PSON\_L input. A failure on the Main output will shut down only the Main output, while Standby continues to operate. Additionally, the main output power limitation will decrease if the ambient (inlet) temperature increases beyond 55°C, which is defined as a short term operation condition and NOT recommend to operate at this condition for long term.

| Vin (Vac) | 50℃<br>lout_Nom (A) | 50°C<br>lout OCP (A) | 50°C<br>peak load (A) (20s) | 55℃<br>Iout Nom (A) | 55°C<br>lout OCP (A) | 55°C<br>peak load (A) (20s) |

|-----------|---------------------|----------------------|-----------------------------|---------------------|----------------------|-----------------------------|

| 90        | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 100       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 110       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 120       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 130       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 140       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 150       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 160       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 170       | 96                  | 103~110              | 110                         | 96                  | 103~110              | 110                         |

| 175       | 183                 | 196~205              | 205                         | 167                 | 179 ~187             | 187                         |

| 180       | 183                 | 196~205              | 205                         | 167                 | 179 ~187             | 187                         |

| 190       | 183                 | 196~205              | 205                         | 167                 | 179 ~187             | 187                         |

| 200       | 183                 | 196~205              | 205                         | 167                 | 179 ~187             | 187                         |

| 210       | 183                 | 196~205              | 205                         | 167                 | 179 ~187             | 187                         |

| 220       | 183                 | 196~205              | 205                         | 167                 | 179 ~187             | 187                         |

| 270       | 183                 | 196~205              | 205                         | 167                 | 179 ~187             | 187                         |

Table 3. Main Output Nominal Output Current I1 nomli & Current Limitation Iv1 lim vs Inlet Temperature (degC) & Vin(Vac)

#### 6.6 PEAK LOAD WITH ADDED SYSTEM BUFFER CAPACITANCE

The power supply shall be able to support higher peak power levels with added system buffer capacitance for up to 100  $\mu$ s. Table 4 are PMAX testing conditions.

| PEAK POWER | PEAK CURRENT | SYSTEM CAPACITANCE | PEAK LOAD DURATION | VOLTAGE UNDERSHOOT |

|------------|--------------|--------------------|--------------------|--------------------|

| 2736W      | 228A         | 6,150 μF           | 100 µs             | 5%                 |

Table 4. PMAX Testing Conditions

### 7. MONITORING

The power supply operating parameters can be accessed through I<sup>2</sup>C interface. For more details refer to chapter I2C / POWER MANAGEMENT BUS COMMUNICATION and document PES2200-12-080xA Power Management Bus Communication Manual.

| PARAMET            | ER                          | DESCRIPTION / CONDITION                  | MIN NO | M MAX | UNIT |

|--------------------|-----------------------------|------------------------------------------|--------|-------|------|

| V <sub>i mon</sub> | Input Voltage               | $V_{i \min LL} \leq V_i \leq V_{i \max}$ | -2     | +2    | VAC  |

| l <sub>i mon</sub> | Input Current               |                                          | -1     | +1    | А    |

| Pimon              |                             | <i>P</i> <sub>i</sub> > 700 W            | -5     | +5    | %    |

| <b>r</b> 'i mon    | True Input Power            | <i>P</i> i ≤700 W                        | 35     | 35    | W    |

| <i>E</i> .         | Total Input Energy          | <i>P</i> i > 700 W                       | -5     | +5    | %    |

| Ei mon             | Total Input Energy          | <i>P</i> i ≤700 W                        | 35     | 35    | W    |

| V1 mon             | V1 Voltage                  |                                          | -1     | +1    | %    |

| 1.                 | V1 Current                  | l1 > 30 A                                | -2     | +2    | %    |

| I <sub>1 mon</sub> | V <sub>1</sub> Current      | l1 ≤ 30 A                                | -1     | +1    | А    |

| Π                  | I/ Output Dowor             | Po > 250 W                               | -5     | +5    | %    |

| P <sub>nom</sub>   | V <sub>7</sub> Output Power | Po ≤ 250 W                               | -15    | +15   | W    |

| <b>-</b>           |                             | Po > 250 W                               | -5     | +5    | %    |

| Enom               | V1 Onput Energy             | Po ≤ 250 W                               | -15    | +15   | W    |

| Tambmon            | Ambient Temperature         | $0^{\circ}C \le T_{amb} \le 55^{\circ}C$ | -5     | +5    | °C   |

| Fs                 | Fan speed                   |                                          | -500   | +500  | RPM  |

Asia-Pacific Euro +86 755 298 85888

Europe, Middle East +353 61 225 977 North America +1 408 785 5200

BCD.01005\_A

#### 8. SIGNALING AND CONTROL

#### **8.1 ELECTRICAL CHARACTERISTICS**

| PARAMET         | ER                                     | DESCRIPTION / CONDITION                                      | MIN | NOM  | MAX  | UNIT |

|-----------------|----------------------------------------|--------------------------------------------------------------|-----|------|------|------|

| PSON_L          |                                        |                                                              |     |      |      |      |

| VIL             | Input Low Level Voltage                | PSON_L: Main output enabled                                  | 0   |      | 0.8  | V    |

| ViH             | Input High Level Voltage               | PSON_L: Main output disabled                                 | 2   |      | 5.25 | V    |

| IIL,H           | Maximum Source Current                 | $V_{1} = -0.2 \text{ V to } +3.5 \text{ V}$                  |     |      | 4    | mA   |

| Rpull up        | Pull-up to 3V3 Located in Power Supply |                                                              |     | 10   |      | kΩ   |

| PWOK_H          |                                        |                                                              |     |      |      |      |

| Vol             | Output Low Level Voltage               | $Vi < V_{i \min LL}, I_{sink} = 400 \ \mu A$                 | 0   |      | 0.4  | V    |

| V <sub>OH</sub> | Output High Level Voltage              | $Vi > V_{i  min  LL}$ , $I_{source} = 200  \mu A$            | 2.4 |      | 3.46 | V    |

| la              | Maximum Sink Current                   | PWOK_H = low                                                 |     |      | 400  | μA   |

| ls              | Maximum Source Current                 | $PWOK_H = high$                                              |     |      | 2    | mA   |

| SMB_ALE         | RT_L                                   |                                                              |     |      |      |      |

| Vext            | Maximum External Pull up Voltage       |                                                              |     |      | 3.46 | V    |

| Vol             | Output Low Level Voltage               | Failure or Warning condition, <i>Isink</i> < 4 mA            | 0   |      | 0.4  | V    |

| Rpull up        | Pull-up to 3V3 Located in Power Supply |                                                              |     | None |      |      |

| ls              | Sink Current                           | SMB_ALERT_L = low                                            |     |      | 4    | mA   |

| 15              | Sink ourient                           | SMB_ALERT_L= high                                            |     |      | 50   | μA   |

| VIN_OK_H        | ,                                      |                                                              |     |      |      |      |

| Vext            | Maximum External Pull up Voltage       |                                                              |     |      | 3.46 | V    |

| Vol             | Output Low Level Voltage               | Failure or Warning condition, <i>I<sub>sink</sub></i> < 4 mA | 0   |      | 0.4  | V    |

| Rpull up        | Pull-up to 3V3 Located in Power Supply |                                                              |     | 1    |      | kΩ   |

| ls              | Sink Current                           | VIN OK H = low                                               |     |      | 4    | mA   |

#### **8.2 SENSE INPUTS**

The main output has sense lines implemented to compensate for voltage drop on load wires in both positive and negative path. The maximum allowed voltage drop is 200 mV on the positive rail and 50 mV on the GND rail. With open sense inputs the main output voltage will rise by 250 mV. Therefore, if not used, these inputs should be connected to the power output and GND at the power supply connector. The sense inputs are protected against short circuit. In this case the power supply will shut down.

#### 8.3 PRESENT\_L OUTPUT

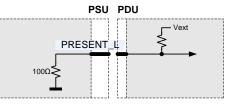

The PRESENT\_L pin is wired through a 100 Ohms resistor to internal GND within the power supply. This pin does indicate that there is a power supply present in this system slot. An external pull-up resistor has to be added within the application. Current into PRESENT\_L should not exceed 5mA to guarantee a low level voltage if power supply is seated.

Figure 9. PRESENT\_L Connection

#### 8.4 PSON\_L INPUT

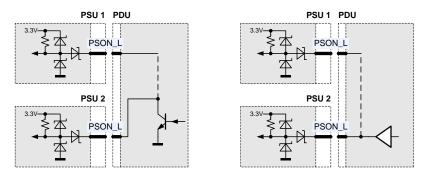

The PSON\_L is an internally pulled-up (3.3 V) input signal to enable/disable the main output V1 of the front-end. With low level input the main output is enabled. This active-low pin is also used to clear any latched fault condition. The PSON\_L can be either controlled by an open collector device or by a voltage source.

Figure 10. PSON\_L connection

#### 8.5 PWOK\_H OUTPUT

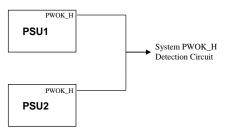

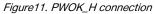

PWOK\_H is a power OK signal and will be pulled HIGH by the power supply to indicate that all the outputs are within the regulation limits of the power supply. When any output voltage falls below regulation limits or when AC power has been removed for a time sufficiently long so that power supply operation is no longer guaranteed, PWOK\_H will be de-asserted to a LOW state. The start of the PWOK\_H delay time shall be inhibited as long as any power supply output is in current limit. The PWOK\_H and I2C bus of PSU are connected together on the redundant system. The below block diagram was shown the wiring on the system. The internal PWOK\_H circuit of power supply is designed so that the PWOK\_H bus is the wire-ORed function of the individual PWOK\_H signals of all the power supply in parallel. Suggest system Pull-up to 3V3 and pull-up resistance is 10K. The PWOK\_H signal also can be separated for each PSU design in system side to indicate each PSU output

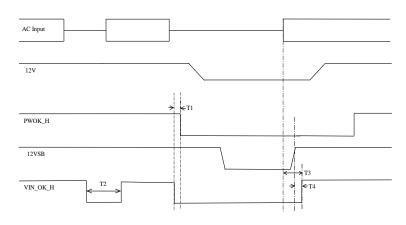

#### 8.6 SMB\_ALERT\_L OUTPUT

The SMB\_ALERT\_L signal indicates that the power supply is experiencing a problem that the system agent should investigate. This is a logical OR of the Shutdown and Warning events. It is asserted (pulled Low) at Shutdown or Warning events such as reaching temperature warning/shutdown threshold of critical component, general failure, over-current, over-voltage, undervoltage or low-speed of failed fan. This signal may also indicate the power supply is operating in an environment exceeding the specified limits. This signal is to be asserted in parallel with LED turning solid Yellow.

The power supply shall assert the over temperature SMB\_ALERT\_L signal when a hot spot or inlet temperature sensor crosses a warning threshold. The inlet temperature warning threshold must be set at 59°C, preventing exhaust air and cord temperatures temperature exceeding safety ratings. The warning gets de-asserted once inlet air temperature returns into specified operating temperature range. Fan speed control algorithm shall ramp up the fan speed to the maximum prior to the SMB\_ALERT\_L insertion.

In case exhaust air temperature exceeds 70 °C higher temp rating cord must be used.

Asia-Pacific

Europe, Middle East

+86 755 298 85888

+353 61 225 977

977 +1 4

North America +1 408 785 5200 BCD.01005\_A

Figure 12. SMB\_ALERT\_L Connection

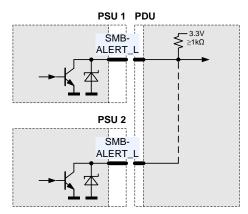

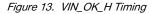

#### 8.7 VIN\_OK\_H OUTPUT

This signal will be asserted, driven high, by the power supply to indicate that the input voltage meets the minimum requirements of the parametric PSU specification.

The PSU shall de-assert (drive low) under input over-voltage condition.

AC Line and AC loss detection algorithm

AC line voltage detection for power on:

The power supply will use Vrms to determine if the input voltage is within the specified requirements for turning on the power supply unit as called out by the individual power supply specification for AC input voltage range. The Vrms of the input must be determined within 5-cycles after the application of AC & Standby has reached regulation. Assertion requirements for VIN\_OK\_H remain the same.

AC line voltage detection for an AC brownout and dropout:

PSU shall detect both AC brown out and dropout conditions and issue a power down warning to the end system. The PSU shall de-assert (drive low) VIN\_OK\_H at least 4mS(T1) prior to the de-assertion of PWOK\_H upon input conditions that fall below the Vin (turn-off) specification of the PSU parametric specification. Under such conditions. After VIN\_OK\_H de-assertion, the PSU shall be capable of delivering all outputs within the regulation limits for at least 4mS before de-asserting PWOK\_H(T1). In a similar manner the PSU shall de-assert PWOK\_H a minimum of 1 ms prior to the main rail voltage degrading to 95% of the set point voltage value. Upon a VIN\_OK\_H de-assertion, the PSU shall derive an average RMS input voltage, measured over a moving average window equal to T2, to establish if conditions meet the requirements for assertion of VIN\_OK\_H. Refer to *Figure 13*.

| PARAMETER | DESCRIPTION / CONDITION | MIN | NOM | MAX  | UNIT |

|-----------|-------------------------|-----|-----|------|------|

| T1        | VIN_OK_H & PWOK_H       | 4   |     |      | ms   |

| T2        | VIN_OK_H Dwell Time     | 75  |     | 120  | ms   |

| Т3        | VIN_OK_H delay to AC    |     |     | 1700 | ms   |

| T4        | VIN_OK_H to 12VSB       |     |     | 20   | ms   |

NOTE: T2 is the minimum VIN\_OK\_H de-assertion dwell time that is initiated when the PSU has declared a loss of input voltage.

Table 5. VIN\_OK\_H Timing Requirements

#### **8.8 TIMING REQUIREMENTS**

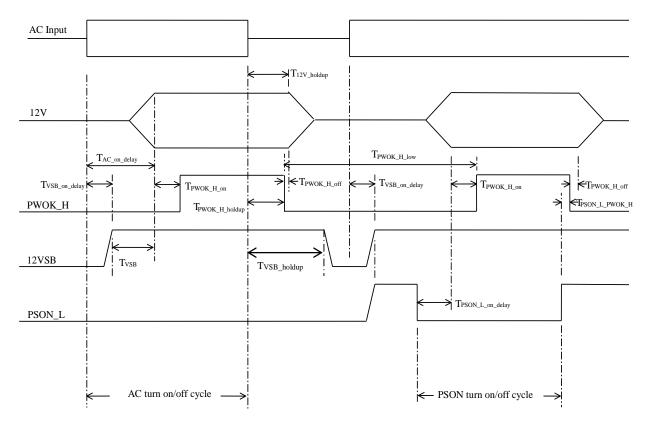

These are the timing requirements for the power supply operation. The output voltages must rise from 10% to within regulation limits ( $T_{vout\_rise}$ ) within 1 to 70 ms. For 12 VSB, it is allowed to rise from 5.0 between 10 ms. All outputs must rise monotonically. *Table 6* shows the timing requirements for the power supply being turned on and off two ways; 1) via the AC input with PSON\_L held low; 2) via the PSON\_L signal with the AC input applied. The PSU needs to remain off for 1 second minimum after PWOK\_H is de-asserted.

Figure 14. Turn On/Off Timing

Asia-Pacific Europe, +86 755 298 85888 +35

Europe, Middle East +353 61 225 977 North America +1 408 785 5200

© 2021 Bel Power Solutions

BCD.01005\_A

| PARAMETER               | DESCRIPTION / CONDITION                                                                                    | MIN   | NOM | MAX  | UNIT |

|-------------------------|------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| T <sub>12V_rise</sub>   | Output voltage rise time                                                                                   | 1.0 * |     | 70 * | ms   |

| TvsB_on_delay           | Delay from AC being applied to 12VSB being within regulation.                                              |       |     | 1500 | ms   |

| T AC_on_delay           | Delay from AC being applied to all output voltages being within regulation.                                |       |     | 3000 | ms   |

| T <sub>12V_holdup</sub> | Time 12V output voltage stay within regulation after loss of AC.                                           | 10.5  |     |      | ms   |

| TPWOK_H_holdup          | Delay from loss of AC to de-assertion of PWOK_H                                                            | 9     |     |      | ms   |

| TPSON_L_on_delay        | Delay from PSON_L active to output voltages within regulation limits.                                      | 5     |     | 400  | ms   |

| T PSON_L_PWOK_H         | Delay from PSON_L deactivate to PWOK_H being de-asserted.                                                  |       |     | 5    | ms   |

| TPWOK_H_on              | Delay from output voltages within regulation limits to PWOK_H asserted at turn on.                         | 100   |     | 500  | ms   |

| T PWOK_H_off            | Delay from PWOK_H de-asserted to output voltages dropping out of<br>regulation limits.                     | 1     |     |      | ms   |

| TPWOK_H_low             | Duration of PWOK_H being in the de-asserted state during an off/on cycle<br>using AC or the PSON_L signal. | 100   |     |      | ms   |

| T <sub>VSB</sub>        | Delay from 12VSB being in regulation to O/Ps being in regulation at AC turn on.                            | 50    |     | 1000 | ms   |

| T <sub>VSB_holdup</sub> | Time the 12VSB output voltage stays within regulation after loss of AC.                                    | 70    |     |      | ms   |

| TAC_off_SMB_ALERT_L     | The power supply shall assert the SMB_ALERT_L signal quickly after a loss<br>of AC input voltage           |       |     | 2    | ms   |

\* The 12VSB output voltage rise time shall be from 5.0 ms between 10 ms.

#### Table 6. Timing Requirements

#### 8.9 HOT\_STANDBY

The hot-standby operation is an operating mode allowing to further increase efficiency at light load conditions in a redundant power supply system. Under specific conditions one of the power supplies is allowed to disable Oring gate, to make sure into hot standby mode. This will save the power losses associated with this power supply and at the same time the other power supply will operate in a load range having a better efficiency.

#### 8.10 LED INDICATOR

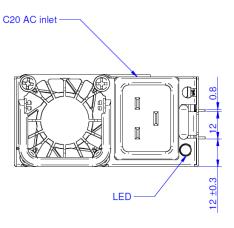

The front-end has one front LED showing the status of the supply. The LED is bi-colored: green and yellow and indicates AC and DC power presence and warning or fault conditions. *Table 8* lists the different LED status.

|        | MIN λd<br>WAVELENGTH | NOMINAL λd<br>WAVELENGTH | MAX λd<br>WAVELENGTH | UNITS |

|--------|----------------------|--------------------------|----------------------|-------|

| Green  |                      | 570                      |                      | nm    |

| Yellow |                      | 590                      |                      | nm    |

#### Table 7. LED Characteristics

| OPERATING CONDITION                                                                                                     | LED STATE        |

|-------------------------------------------------------------------------------------------------------------------------|------------------|

| Output ON and OK                                                                                                        | Solid GREEN      |

| No AC power to all power supplies                                                                                       | OFF              |

| AC present / Only 12VSB on (PS off) or PS in Hot standby state                                                          | 1Hz Blink GREEN  |

| AC cord unplugged; with a second power supply in parallel still with AC input power.                                    | OFF              |

| Power supply warning events where the power supply continues to operate; high temp, high power, high current, slow fan. | 1Hz Blink YELLOW |

| Power supply critical event causing a shutdown; failure, OCP, OVP, Fan Fail                                             | Solid YELLOW     |

| Power supply in FW upload mode                                                                                          | 2Hz Blink GREEN  |

Table 8. LED Status

#### 9. I2C / POWER MANAGEMENT BUS COMMUNICATION

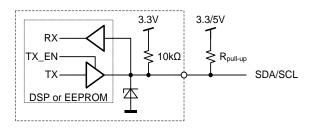

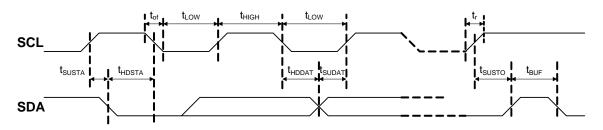

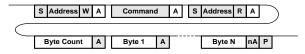

The PES front-end is a communication Slave device only; it never initiates messages on the l<sup>2</sup>C/SMBus by itself. The communication bus voltage and timing is defined in *Figure 15* further characterized through:

- The SDA/SCL IOs use 3V3 logic levels

- External pull-up resistors on SDA/SCL required for correct signal edges

- Full SMBus clock speed of 100 kbps

- Clock stretching limited to 1 ms

- SCL low time-out of >25 ms with recovery

- within 10 ms

- Recognizes any time Start/Stop bus conditions

Figure 15. Physical layer of communication interface

Communication to the DSP or the EEPROM will be possible as long as the input AC voltage is provided. If no AC is present, communication to the unit is possible as long as it is connected to a life  $V_{SB}$  output or  $V_1$  output (provided e.g. by the redundant unit).

| PARAMETER        | DESCRIPTION                                  | CONDITION                                | MIN       | MAX                                   | UNIT |

|------------------|----------------------------------------------|------------------------------------------|-----------|---------------------------------------|------|

| SCL / SDA        |                                              |                                          |           |                                       |      |

| ViL              | Input low voltage                            |                                          | -0.5      | 1.0                                   | V    |

| Ин               | Input high voltage                           |                                          | 2.3       | 3.5                                   | V    |

| <b>I∕</b> hys    | Input hysteresis                             |                                          | 0.15      |                                       | V    |

| Vol              | Output low voltage                           | 3 mA sink current                        | 0         | 0.4                                   | V    |

| <i>t</i> r       | Rise time for SDA and SCL                    |                                          | 20+0.1Cb1 | 1000                                  | ns   |

| <i>t</i> of      | Output fall time ViHmin $\rightarrow$ ViLmax | $10 \text{ pF} < C_b^1 < 400 \text{ pF}$ | 20+0.1Cb1 | 250                                   | ns   |

| <i>l</i> i       | Input current SCL/SDA                        | 0.1 VDD < Vi < 0.9 VDD                   | -10       | 10                                    | μA   |

| G                | Internal Capacitance for each SCL/SDA        |                                          |           | 50                                    | pF   |

| <i>f</i> scl     | SCL clock frequency                          |                                          | 0         | 100                                   | kHz  |

| <i>R</i> pull-up | External pull-up resistor                    | f <sub>SCL</sub> ≤ 100 kHz               |           | 1000 ns / C <sub>b</sub> <sup>1</sup> | Ω    |

| <i>t</i> HDSTA   | Hold time (repeated) START                   | f <sub>SCL</sub> ≤ 100 kHz               | 4.0       |                                       | μs   |

| <i>t</i> Low     | Low period of the SCL clock                  | f <sub>SCL</sub> ≤ 100 kHz               | 4.7       |                                       | μs   |

| <i>t</i> HIGH    | High period of the SCL clock                 | f <sub>SCL</sub> ≤ 100 kHz               | 4.0       |                                       | μs   |

| <i>t</i> susta   | Setup time for a repeated START              | f <sub>SCL</sub> ≤ 100 kHz               | 4.7       |                                       | μs   |

| <i>t</i> hddat   | Data hold time                               | f <sub>SCL</sub> ≤ 100 kHz               | 0         | 3.45                                  | μs   |

| <i>t</i> SUDAT   | Data setup time                              | f <sub>SCL</sub> ≤ 100 kHz               | 250       |                                       | ns   |

| <i>t</i> susto   | Setup time for STOP condition                | f <sub>SCL</sub> ≤ 100 kHz               | 4.0       |                                       | μs   |

| <i>t</i> BUF     | Bus free time between STOP and START         | f <sub>SCL</sub> ≤ 100 kHz               | 5         |                                       | ms   |

<sup>1</sup> Cb = Capacitance of bus line in pF, typically in the range of 10...400 pF

Table 9. I2C / SMBus Specification

Asia-Pacific | +86 755 298 85888

Europe, Middle East +353 61 225 977 North America +1 408 785 5200

BCD.01005\_A

PES2200-12-080xA

Figure 16. PC / SMBus Timing

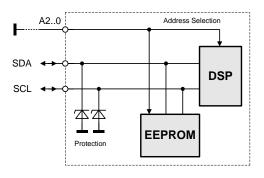

#### ADDRESS SELECTION

The address for I<sup>2</sup>C communication can be configured by pulling address input pins A2, A1 and A0 either to GND (Logic Low) or leave them open (Logic High). An internal pull up resistor will cause the A2 / A1 / A0 pin to be in High Level if left open. A fixed addressing offset exists between the Controller and the EEPROM.

| *0 |    | •••        | I2C Address * |        |  |

|----|----|------------|---------------|--------|--|

| A2 | A1 | <b>A</b> 0 | Controller    | EEPROM |  |

| 0  | 0  | 0          | 0xB0          | 0xA0   |  |

| 0  | 0  | 1          | 0xB2          | 0xA2   |  |

| 0  | 1  | 0          | 0xB4          | 0xA4   |  |

| 0  | 1  | 1          | 0xB6          | 0xA6   |  |

| 1  | 0  | 0          | 0xB8          | 0xA8   |  |

| 1  | 0  | 1          | 0xBA          | 0xAA   |  |

| 1  | 1  | 0          | 0xBC          | 0xAC   |  |

| 1  | 1  | 1          | 0xBE          | 0xAE   |  |

|    |    |            |               |        |  |

\* The LSB of the address byte is the R/W bit

Table 10. Address and Protocol Encoding

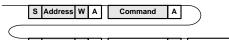

#### 9.1 CONTROLLER AND EEPROM ACCESS

The controller and the EEPROM in the power supply share the same I2C bus physical layer (see *Figure 17*) and can be accessed under different addresses, see ADDRESS SELECTION.

The SDA/SCL lines are connected directly to the controller and EEPROM which are supplied by internal 3V3.

The EEPROM provides 256 bytes of user memory. None of the bytes are used for the operation of the power supply.

Figure 17. I2C Bus to DSP and EEPROM

18

#### 9.2 EEPROM PROTOCOL

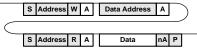

The EEPROM follows the industry communication protocols used for this type of device. Even though page write / read commands are defined, it is recommended to use the single byte write / read commands. **WRITE**

# The write command follows the SMBus 1.1 Write Byte protocol. After the device address with the write bit cleared a first byte with the data address to write to is sent followed by the data byte and the STOP condition. A new START condition on the bus should only occur after 5ms of the last STOP condition to allow the EEPROM to write the data into its memory.

#### READ

The read command follows the SMBus 1.1 Read Byte protocol. After the device address with the write bit cleared the data address byte is sent followed by a repeated start, the device address and the read bit set. The EEPROM will respond with the data byte at the specified location.

#### 9.3 POWER MANAGEMENT BUS PROTOCOL

The Power Management Bus is an open standard protocol that defines means of communicating with power conversion and other devices. For more information, please see the System Management Interface Forum web site at : <u>www.powerSIG.org</u>.

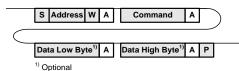

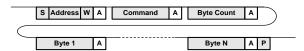

Power Management Bus command codes are not register addresses. They describe a specific command to be executed. The PES2200-12-080xA supply supports the following basic command structures:

- Clock stretching limited to 1 ms

- SCL low time-out of >25 ms with recovery within 10 ms

- Recognized any time Start/Stop bus conditions

#### WRITE

The write protocol is the SMBus 1.1 Write Byte/Word protocol. Note that the write protocol may end after the command byte or after the first data byte (Byte command) or then after sending 2 data bytes (Word command).

In addition, Block write commands are supported with a total maximum length of 255 bytes.

#### READ

The read protocol is the SMBus 1.1 Read Byte/Word protocol. Note that the read protocol may request a single byte or word.

S Address R A Data (Low) Byte A Data High Byte<sup>1</sup> nA P

In addition, Block read commands are supported with a total maximum length of 255 bytes.

) Optional

Asia-Pacific

Europe,

+86 755 298 85888

+35

Europe, Middle East +353 61 225 977 North America +1 408 785 5200

BCD.01005\_A

19

#### 9.4 POWER SUPPLY DIAGNOSTIC "EVENT RECORDER"

The power supply shall save the latest Power Management Bus data and other pertinent data into nonvolatile memory when a critical event shuts down the power supply. This data shall be accessible via the Power Management Bus interface with an external source providing power to the 12Vstby output.

Critical Events to trigger an update to the Event Recorder includes:

- Output OVP

- Output OCP

- Input OV/UV Fault

- Fan fault

- OTP

- Other faults to cause output shutdown.

Refer to BCA.00199\_PES2200-12-080xA Power Management Bus Communication Application Note for further information about the Power Management Bus commands to support this function.

#### 9.5 FIRMWARE UPDATE

The power supply shall have the capability to update its firmware via the Power Management Bus interface while it is in standby mode. This FW can be updated when in the system and in standby mode and outside the system with power applied to the 12Vstby pins. BPS standard GUI supports the firmware upgrade function.

#### 9.6 GRAPHICAL USER INTERFACE

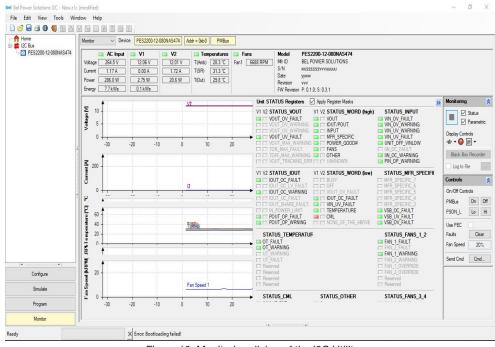

Bel Power Solutions provides with its "I<sup>2</sup>C Utility" a Windows® XP/Vista/Win7 compatible graphical user interface allowing the programming and monitoring of the PES2200-12-080xA Front-End. The utility can be downloaded on: <u>belfuse.com/power-solutions</u> and supports both the PSMI and Power Management Bus protocols.

The GUI allows automatic discovery of the units connected to the communication bus and will show them in the navigation tree. In the monitoring view the power supply can be controlled and monitored.

If the GUI is used in conjunction with the YTM.00103 Evaluation Board it is also possible to control the PSON\_L pin(s) of the power supply.

Figure 18. Monitoring dialog of the I2C Utility

#### **10. TEMPERATURE AND FAN CONTROL**

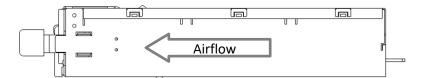

To achieve best cooling results sufficient airflow through the supply must be ensured. Do not block or obstruct the air-flow at the rear of the supply by placing large objects directly at the output connector. The PES2200-12-080xA is pro-vided with a rear to front airflow, which means the air enters through the DC-output of the supply and leaves at the AC-inlet. The PES2200-12-080xA supply has been designed for horizontal operation.

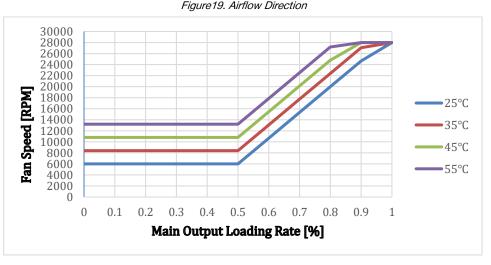

The fan inside of the supply is controlled by a microprocessor. The rpm of the fan is adjusted to ensure optimal supply cooling and is a function of output power and the inlet temperature.

The fan oscillation shall be controlled such that associated sound power level variation falls within a band of 2.0 dBA (roughly 10% mean speed). This condition may be treated as steady state fan speed condition.

After the new load and/or cooling condition steady state is established, transition to the steady state fan speed shall take place within 60 s.

The PES2200-12-080xA provides access via I<sup>2</sup>C to the measured temperatures of in total 4 sensors within the power supply, see *Table 11*. The microprocessor is monitoring these temperatures and if warning threshold of one of these sensors is reached it will set fan to maximum speed. If temperatures continue to rise above shut down threshold the main output V1 (or VSB if auxiliary converter is affected) will be disabled. At the same time the warning or fault condition is signalized accordingly through LED, PWOK\_H and SMB\_ALERT\_L.

| TEMPERATURE SENSOR                                        | DESCRIPTION / CONDITION                                            | POWER<br>MANAGEMENT<br>BUS REGISTER | WARNING<br>THRESHOLD | SHUT DOWN<br>THRESHOLD |

|-----------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------|----------------------|------------------------|

| Inlet air temperature (NA)<br>Outlet air temperature (RA) | Sensor located on control board close to DC<br>end of power supply | 8Dh                                 | NA:98<br>RA:95       | NA:73<br>RA:100        |

| Syn rectifier Mosfet                                      | Sensor located close to Syn rectifier Mosfet                       | 8Eh                                 | NA:110<br>RA:120     | NA:115<br>RA:128       |

| Outlet air temperature (NA)<br>Inlet air temperature (RA) | Sensor located on main board close to AC front of power supply     | 8Fh                                 | NA:80<br>RA:68       | NA:85<br>RA:73         |

| PFC heat sink                                             | Sensor located on PFC heat sink                                    | EAh                                 | 96                   | 101                    |

Table 11. Temperature Sensor Location and Thresholds

#### Figure 20. Fan Speed vs. Main Output Load

**Comment:** The fan minimum speed is 6000RPM.

Asia-Pacific

Europe, Middle East

+86 755 298 85888

+353 61 225 977

le East I 25 977 +<sup>-</sup>

North America +1 408 785 5200 BCD.01005\_A

### **11. ELECTROMAGNETIC COMPATIBILITY**

#### 11.1 IMMUNITY

| PARAMETER                          | DESCRIPTION / CONDITION                                                                                                                                                                  | CRITERION               |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| ESD Contact Discharge              | IEC / EN 61000-4-2, ±8 kV, 25+25 discharges per test point<br>(metallic case, LEDs, connector body)                                                                                      | А                       |

| ESD Air Discharge                  | IEC / EN 61000-4-2, ±15 kV, 25+25 discharges per test point<br>(non-metallic user accessible surfaces)                                                                                   | А                       |

| Radiated Electromagnetics<br>Filed | IEC / EN 61000-4-3, 10 V/m, 1 kHz/80% Amplitude Modulation,<br>1 μs Pulse Modulation, 10 kHz2 GHz                                                                                        | А                       |

| Burst                              | IEC / EN 61000-4-4, level 3<br>AC port ±2 kV, 1 minute<br>DC port ±1 kV, 1 minute                                                                                                        | A                       |

| Surge                              | IEC / EN 61000-4-5<br>Line to earth: level 3, ±2 kV<br>Line to line: level 2, ±1 kV                                                                                                      | А                       |

| RF Conducted Immunity              | IEC/EN 61000-4-6, Level 3, 10 Vrms, CW, 0.1 80 MHz                                                                                                                                       | А                       |

| Voltage Dips and Interruptions     | IEC/EN 61000-4-11<br>1) Vi 230Volts, 80% Load, Dip 100%, Duration 10ms<br>2) Vi 230Volts, 100% Load, Dip 100%, Duration < 50 ms<br>3) Vi 230Volts, 100% Load, Dip 100%, Duration > 50 ms | A<br>V1: B; VSB: A<br>B |

#### 11.2 EMISSION

| PARAMETER                                                                                     | DESCRIPTION / CONDITION                                             | CRITERION   |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------|

|                                                                                               | EN 55032/CISPR32: 0.15 30 MHz, QP and AVG, single power supply      | Class A     |

| Conducted Emission EN 55032/CISPR32: 0.15 30 MHz, QP and AVG,<br>2 power supplies in a system |                                                                     | Class A     |

| De dista d Ensis sis a                                                                        | EN 55032/CISPR32: 30 MHz 1 GHz, QP, single power supply             | Class A     |

| Radiated Emission                                                                             | EN 55032/CISPR32: 30 MHz 1 GHz, QP,<br>2 power supplies in a system | Class A     |

| Acoustical Noise                                                                              | A-weighted sound power, 25°C, 50% Load                              | 60 dB (TBD) |

#### **12. SAFETY / APPROVALS**

Maximum electric strength testing is performed in the factory according to UL/CSA/IEC/EN 62368-1 and IEC 60950-1. Inputto-output electric strength tests should not be repeated in the field. Bel Power Solutions will not honor any warranty claims resulting from electric strength field tests.