# **General Description**

The 8SLVD2104 is a high-performance differential dual 1:4 LVDS fanout buffer. The device is designed for the fanout of high-frequency, very low additive phase-noise clock and data signals. The 8SLVD2104 is characterized to operate from a 2.5V power supply. Guaranteed output-to-output and part-to-part skew characteristics make the 8SLVD2104 ideal for those clock distribution applications demanding well-defined performance and repeatability. Two independent buffers with four low skew outputs each are available. The integrated bias voltage generators enables easy interfacing of single-ended signals to the device inputs. The device is optimized for low power consumption and low additive phase noise.

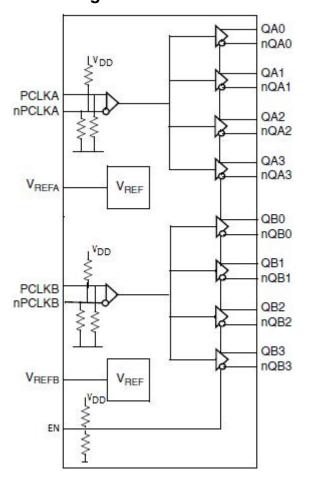

# **Block Diagram**

#### **Features**

- Two 1:4, low skew, low additive jitter LVDS fanout buffers

- · Two differential clock inputs

- Differential pairs can accept the following differential input levels: LVDS and LVPECL

- · Maximum input clock frequency: 2GHz

- · Output bank skew: 35ps, (maximum)

- · Propagation delay: 300ps, (maximum)

- Low additive RMS phase jitter, 156.25MHz (10kHz 20MHz): 105fs, (maximum)

- · 2.5V supply voltage

- Lead-free (RoHS 6) 28-Lead VFQFN package

- -40°C to 85°C ambient operating temperature

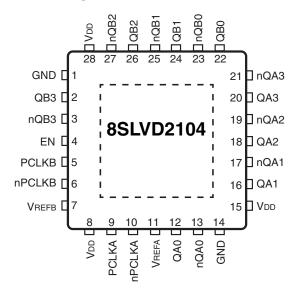

# Pin Assignment

28-Lead, 5mm x 5mm VFQFN

# **Pin Description and Pin Characteristic Tables**

Table 1. Pin Descriptions<sup>1</sup>

| Number | Name              | Туј    | ре                  | Description                                                                             |

|--------|-------------------|--------|---------------------|-----------------------------------------------------------------------------------------|

| 1      | GND               | Power  |                     | Power supply ground.                                                                    |

| 2      | QB3               | Output |                     | Differential output pair P2 LVDC interfere levels                                       |

| 3      | nQB3              | Output |                     | Differential output pair B3. LVDS interface levels.                                     |

| 4      | EN                | Input  | Pullup/<br>Pulldown | Output enable pin. V <sub>DD</sub> /2 default when left floating.                       |

| 5      | PCLKB             | Input  | Pulldown            | Non-inverting differential clock/data input.                                            |

| 6      | nPCLKB            | Input  | Pullup/<br>Pulldown | Inverting differential clock/data input. $V_{DD}/2$ default when left floating.         |

| 7      | V <sub>REFB</sub> | Output |                     | Bias voltage reference for the PCLKB, nPCLKB input pair.                                |

| 8      | $V_{DD}$          | Power  |                     | Power supply pin.                                                                       |

| 9      | PCLKA             | Input  | Pulldown            | Non-inverting differential clock/data input.                                            |

| 10     | nPCLKA            | Input  | Pullup/<br>Pulldown | Inverting differential clock/data input. V <sub>DD</sub> /2 default when left floating. |

| 11     | V <sub>REFA</sub> | Output |                     | Bias voltage reference for the PCLKA, nPCLKA input pair.                                |

| 12,    | QA0               | Output |                     | Differential output pair AO LVDS interface levels                                       |

| 13     | nQA0              | Output |                     | Differential output pair A0. LVDS interface levels.                                     |

| 14     | GND               | Power  |                     | Power supply ground.                                                                    |

| 15     | $V_{DD}$          | Power  |                     | Power supply pin.                                                                       |

| 16     | QA1               | Output |                     | Differential output pair A1. LVDS interface levels.                                     |

| 17     | nQA1              | Output |                     | Differential output pail A1. LVD3 lifterface levels.                                    |

| 18,    | QA2               | Output |                     | Differential output pair A2. LVDS interface levels.                                     |

| 19     | nQA2              | Output |                     | - Differential output pair Az. EVD3 interface levels.                                   |

| 20     | QA3               | Output |                     | Differential output pair A3. LVDS interface levels.                                     |

| 21     | nQA3              | Output |                     | - Differential output pair A3. EVD3 interface levels.                                   |

| 22     | QB0               | Output |                     | Differential output pair B0. LVDS interface levels.                                     |

| 23     | nQB0              | Output |                     | - Differential output pair Bo. EVD3 interface levels.                                   |

| 24     | QB1               | Output |                     | Differential output pair B1. LVDS interface levels.                                     |

| 25     | nQB1              | Output |                     | Differential output pair DT. EVDO Interface levels.                                     |

| 26     | QB2               | Output |                     | Differential output pair B2. LVDS interface levels.                                     |

| 27     | nQB2              | Output |                     | Differential output pair Dz. EVD3 interface levels.                                     |

| 28     | $V_{DD}$          | Power  |                     | Power supply pin.                                                                       |

|        | ePAD              |        |                     | Thermal pad. Connect to ground.                                                         |

NOTE 1: Pulldown and Pullup refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

## **Table 2. Pin Characteristics**

| Symbol                | Parameter                  |                                 | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|----------------------------|---------------------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance          |                                 |                 |         | 2       |         | pF    |

| R <sub>PULLDOWN</sub> | Input Pulldown<br>Resistor | EN,<br>PCLK[A:B],<br>nPCLK[A:B] |                 |         | 51      |         | kΩ    |

| R <sub>PULLUP</sub>   | Input Pullup<br>Resistor   | EN,<br>nPCLK[A:B]               |                 |         | 51      |         | kΩ    |

# **Function Table**

# Table 3. EN Input Selection Function Table 1

| Input    |                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| EN       | Operation                                                                                                                                  |

| 0 (Low)  | Outputs are disabled and static at Qx = 0 (low level) and nQx = 1 (high level).                                                            |

| 1 (High) | Bank A outputs are enabled and Bank B outputs are disabled at the following static levels:  QBx = 0 (low level) and nQBx = 1 (high level). |

| Open     | All outputs enabled.                                                                                                                       |

NOTE 1: EN is an asynchronous control input pin.

# **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Electrical Characteristics* or *AC Electrical Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                                            | Rating                          |

|-----------------------------------------------------------------|---------------------------------|

| Supply Voltage, V <sub>DD</sub>                                 | 4.6V                            |

| Inputs, V <sub>I</sub>                                          | -0.5V to V <sub>DD</sub> + 0.5V |

| Outputs, I <sub>O</sub> (LVDS) Continuous Current Surge Current | 10mA<br>15mA                    |

| Maximum Junction Temperature, T <sub>J,MAX</sub>                | 125°C                           |

| Storage Temperature, T <sub>STG</sub>                           | -65°C to 150°C                  |

| ESD - Human Body Model <sup>1</sup>                             | 2000V                           |

| ESD - Charged Device Model <sup>1</sup>                         | 1500V                           |

NOTE 1: According to JEDEC/JESD JS-001-2012/22-C101E.

# **DC Electrical Characteristics**

Table 4A. Power Supply Characteristics,  $V_{DD} = 2.5V \pm 5\%$ ,  $T_A = -40$ °C to 85°C<sup>1</sup>

| Symbol          | Parameter            | Test Conditions                                                         | Minimum | Typical | Maximum | Units |

|-----------------|----------------------|-------------------------------------------------------------------------|---------|---------|---------|-------|

| $V_{DD}$        | Power Supply Voltage |                                                                         | 2.375   | 2.5     | 2.625   | V     |

| I <sub>DD</sub> | Power Supply Current | All outputs terminated with 100 $\Omega$ in between nQx, Qx; DC to 2GHz |         | 145     | 170     | mA    |

NOTE 1: Qx, nQx denotes QA[3:0], nQA[3:30], and QB[3:0], nQB[3:0].

Table 4B. LVCMOS/LVTTL Input Characteristics,  $V_{DD}$  = 2.5V  $\pm$  5%,  $T_A$  = -40°C to 85°C

| Symbol           | Parameter                   |    | Test Conditions                | Minimum               | Typical            | Maximum               | Units |

|------------------|-----------------------------|----|--------------------------------|-----------------------|--------------------|-----------------------|-------|

| V <sub>MID</sub> | Input Voltage -<br>Open Pin | EN | Open                           |                       | V <sub>DD</sub> /2 |                       | V     |

| V <sub>IH</sub>  | Input High Voltage          | EN |                                | 0.7 * V <sub>DD</sub> |                    | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>  | Input Low Voltage           | EN |                                | -0.3                  |                    | 0.2 * V <sub>DD</sub> | V     |

| I <sub>IH</sub>  | Input High Current          | EN | $V_{DD} = V_{IN} = 2.625V$     |                       |                    | 150                   | μA    |

| I <sub>IL</sub>  | Input Low Current           | EN | $V_{DD} = 2.625V, V_{IN} = 0V$ | -150                  |                    |                       | μΑ    |

Table 4C. Differential Input Characteristics,  $V_{DD}$  = 2.5V  $\pm$  5%,  $T_A$  = -40°C to 85°C

| Symbol                                   | Parameter                                         |                                    | Test Conditions                                | Minimum | Typical | Maximum             | Units |

|------------------------------------------|---------------------------------------------------|------------------------------------|------------------------------------------------|---------|---------|---------------------|-------|

| I <sub>IH</sub>                          | Input High<br>Current                             | PCLKA, nPCLKA<br>PCLKB, nPCLKB     | $V_{DD} = V_{IN} = 2.625V$                     |         |         | 150                 | μΑ    |

| Input Low<br>Current                     | PCLKA, PCLKB                                      | $V_{DD} = 2.625V, V_{IN} = 0V$     | -10                                            |         |         | μΑ                  |       |

|                                          | Current                                           | nPCLKA, nPCLKB                     | V <sub>DD</sub> = 2.625V, V <sub>IN</sub> = 0V | -150    |         |                     | μΑ    |

| V <sub>REFA</sub> ,<br>V <sub>REFB</sub> | Reference Voltages<br>for Input Bias              |                                    | $V_{DD} = 2.5V; I_{REF} = +100\mu A$           | 1.0     |         | 1.35                | V     |

| V                                        | / <sub>PP</sub> Peak-to-Peak Voltage <sup>1</sup> |                                    | f <sub>REF</sub> < 1.5 GHz                     | 0.15    |         | 1.6                 | V     |

| V <sub>PP</sub>                          |                                                   |                                    | f <sub>REF</sub> > 1.5 GHz                     | 0.2     |         | 1.6                 | V     |

| V <sub>CMR</sub>                         | Common M                                          | lode Input Voltage <sup>1, 2</sup> |                                                | 1.0     |         | $V_{DD} - V_{PP}/2$ | V     |

NOTE 1:  $V_{\text{IL}}$  should not be less than -0.3V.

NOTE 2: Common mode input voltage is defined at the crosspoint.

Table 4D. LVDS Output DC Characteristics,  $V_{DD} = 2.5V \pm 5\%$ ,  $T_A = -40$ °C to 85°C<sup>1, 2</sup>

| Symbol          | Parameter                        | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|----------------------------------|-----------------|---------|---------|---------|-------|

| V <sub>OD</sub> | Differential Output Voltage      |                 | 247     |         | 454     | mV    |

| $\Delta V_{OD}$ | V <sub>OD</sub> Magnitude Change |                 |         |         | 50      | mV    |

| V <sub>OS</sub> | Offset Voltage                   |                 | 1.0     |         | 1.4     | V     |

| $\Delta V_{OS}$ | V <sub>OS</sub> Magnitude Change |                 |         |         | 50      | mV    |

NOTE 1: Qx, nQx denotes QA[3:0], nQA[3:30], and QB[3:0], nQB[3:0].

NOTE 2:  $100\Omega$  termination across differential outputs.

# **AC Electrical Characteristics**

Table 5. AC Electrical Characteristics,  $V_{DD} = 2.5V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C^{1}$

| Symbol                          | Parameter                                                                       | Test Conditions                                                                                                                                                                                                                   | Minimum | Typical | Maximum | Units |

|---------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| f <sub>REF</sub>                | Input Frequency                                                                 |                                                                                                                                                                                                                                   |         |         | 2       | GHz   |

| ΔV/Δt                           | Input Edge Rate                                                                 |                                                                                                                                                                                                                                   | 0.75    |         |         | V/ns  |

| t <sub>PD</sub>                 | Propagation Delay <sup>2</sup>                                                  | PCLKA, nPCLKA to QA[3:0], nQA[3:0] PCLKB, nPCLKB to QB[3:0], nQB[3:0]                                                                                                                                                             | 100     | 196     | 300     | ps    |

|                                 | Channel Isolation                                                               | NOTE <sup>3</sup>                                                                                                                                                                                                                 |         | 65      |         | dB    |

| tsk(o)                          | Output Skew <sup>4, 5, 6</sup>                                                  | Any Output                                                                                                                                                                                                                        |         | 20      | 40      | ps    |

| tsk(b)                          | Output Bank Skew <sup>4, 5</sup>                                                | Within QA[3:0] or QB[3:0] Outputs                                                                                                                                                                                                 |         | 17      | 35      | ps    |

| tsk(p)                          | Pulse Skew                                                                      | f <sub>REF</sub> = 100MHz                                                                                                                                                                                                         | -50     |         | 50      | ps    |

| tsk(pp)                         | Part-to-Part Skew <sup>5, 7</sup>                                               |                                                                                                                                                                                                                                   |         |         | 200     | ps    |

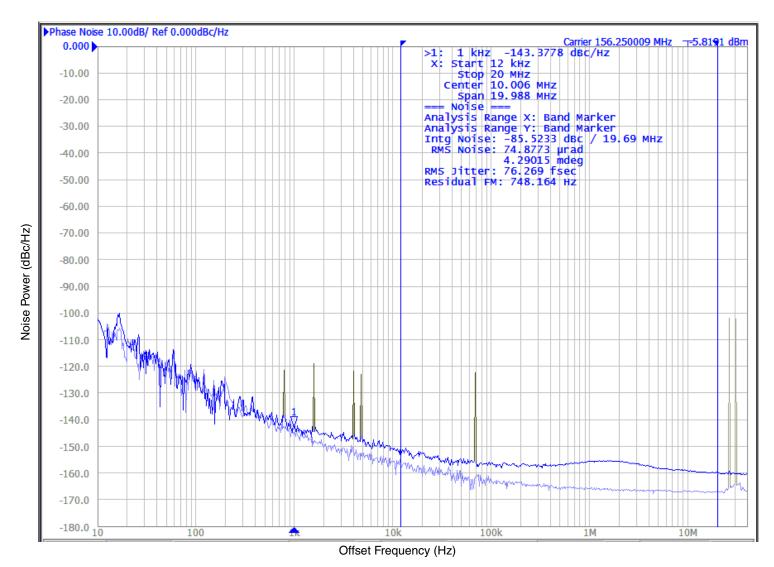

|                                 | Buffer Additive Phase Jitter,<br>RMS; refer to Additive Phase<br>Jitter Section | f <sub>REF</sub> = 156.25MHz Square Wave, V <sub>PP</sub> = 1V,<br>Integration Range: 1kHz – 40MHz                                                                                                                                |         | 90      | 125     | fs    |

|                                 |                                                                                 | f <sub>REF</sub> = 156.25MHz Square Wave, V <sub>PP</sub> = 1V,<br>Integration Range: 10kHz – 20MHz                                                                                                                               |         | 70      | 105     | fs    |

|                                 |                                                                                 | f <sub>REF</sub> = 156.25MHz Square Wave, V <sub>PP</sub> = 1V,<br>Integration Range: 12kHz – 20MHz                                                                                                                               |         | 70      | 105     | fs    |

| t <sub>JIT</sub>                |                                                                                 | f <sub>REF</sub> = 156.25MHz Square Wave, V <sub>PP</sub> = 0.5V, Integration Range: 1kHz – 40MHz                                                                                                                                 |         | 100     | 165     | fs    |

|                                 |                                                                                 | f <sub>REF</sub> = 156.25MHz Square Wave, V <sub>PP</sub> = 0.5V, Integration Range: 10kHz – 20MHz                                                                                                                                |         | 72      | 130     | fs    |

|                                 |                                                                                 | f <sub>REF</sub> = 156.25MHz Square Wave, V <sub>PP</sub> = 0.5V, Integration Range: 12kHz – 20MHz                                                                                                                                |         | 72      | 130     | fs    |

| +                               | Spurious suppression, coupling                                                  | $\begin{split} f_{QB0} &= 500 \text{MHz}, \ V_{PP \ (PCLKB)} = 0.15 \text{V}, \\ V_{CMR (PCLKB)} &= 1 \ \text{V and} \ f_{QA1} = 62.5 \text{MHz}, \\ V_{PP (PCLKA)} &= 1.0 \text{V}, \ V_{CMR (PCLKA)} = 1 \text{V} \end{split}$  |         | 67      |         | dB    |

| t <sub>JIT,</sub> SP            | from QA3 to QB0                                                                 | $\begin{split} f_{QB0} &= 500 \text{MHz}, \ V_{PP \ (PCLKB)} = 0.15 \text{V}, \\ V_{CMR (PCLKB)} &= 1 \text{V and } f_{QA1} = 15.625 \text{MHz}, \\ V_{PP \ (PCLKA)} &= 1.0 \text{V}, \ V_{CMR (PCLKA)} = 1 \text{V} \end{split}$ |         | 80      |         | dB    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/ Fall Time                                                          | 20% to 80%                                                                                                                                                                                                                        |         | 120     | 225     | ps    |

- NOTE 1: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

- NOTE 2: Measured from the differential input crossing point to the differential output crossing point.

- NOTE 3: Channel Isolation is defined as the output amplitude delta between the measured output with active input and the same output with inactive input when the other channel is active.

- NOTE 4: Defined as skew among outputs at the same supply voltage and with equal load conditions. Measured at the differential cross point.

- NOTE 5: This parameter is defined in accordance with JEDEC Standard 65.

- NOTE 6: Both PCLKA, nPCLKA and PCLKB, nPCLKB inputs are phase aligned.

- NOTE 7: Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross point.

## **Additive Phase Jitter**

The spectral purity in a band at a specific offset from the fundamental compared to the power of the fundamental is called the *dBc Phase Noise*. This value is normally expressed using a Phase noise plot and is most often the specified plot in many applications. Phase noise is defined as the ratio of the noise power present in a 1Hz band at a specified offset from the fundamental frequency to the power value of the fundamental. This ratio is expressed in decibels (dBm) or a ratio

of the power in the 1Hz band to the power in the fundamental. When the required offset is specified, the phase noise is called a *dBc* value, which simply means dBm at a specified offset from the fundamental. By investigating jitter in the frequency domain, we get a better understanding of its effects on the desired application over the entire time record of the signal. It is mathematically possible to calculate an expected bit error rate given a phase noise plot.

As with most timing specifications, phase noise measurements have issues relating to the limitations of the measurement equipment. The noise floor of the equipment can be higher or lower than the noise floor of the device. Additive phase noise is dependent on both the noise floor of the input source and measurement equipment.

Additive phase jitter was measured with a Wenzel 156.25MHz oscillator as the input source.

# **Applications Information**

## **Recommendations for Unused Input and Output Pins**

#### Inputs:

#### PCLK/nPCLK Inputs

For applications not requiring the use of a differential input, both the PCLK and nPCLK pins can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from PCLK to ground.

#### **Outputs:**

#### **LVDS Outputs**

All unused LVDS output pairs can be either left floating or terminated with  $100\Omega$  across. If they are left floating, there should be no trace attached.

#### **V**<sub>REFX</sub>

Unused  $V_{\text{REFA}}$  and  $V_{\text{REFB}}$  pins can be left floating. We recommend that there is no trace attached.

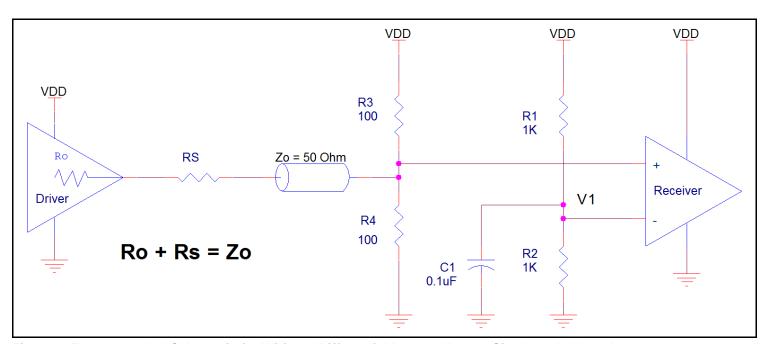

#### Wiring the Differential Input to Accept Single-Ended Levels

*Figure 1* shows how a differential input can be wired to accept single ended levels. The reference voltage  $V_1 = V_{DD}/2$  is generated by the bias resistors R1 and R2. The bypass capacitor (C1) is used to help filter noise on the DC bias. This bias circuit should be located as close to the input pin as possible. The ratio of R1 and R2 might need to be adjusted to position the  $V_1$ in the center of the input voltage swing. For example, if the input clock is driven from a single-ended 2.5V LVCMOS driver and the DC offset (or swing center) of this signal is 1.25V, the R1 and R2 values should be adjusted to set the V1 at 1.25V. The values below are for when both the single ended swing and  $V_{DD}$  are at the same voltage. This configuration requires that the sum of the output impedance of the driver (Ro) and the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the input will attenuate the signal in half. This can be done in one of two ways. First, R3 and R4 in parallel should

equal the transmission line impedance. For most  $50\Omega$  applications, R3 and R4 can be  $100\Omega$ . The values of the resistors can be increased to reduce the loading for slower and weaker LVCMOS driver. When using single-ended signaling, the noise rejection benefits of differential signaling are reduced. Even though the differential input can handle full rail LVCMOS signaling, it is recommended that the amplitude be reduced while maintaining an edge rate faster than 1V/ns. The datasheet specifies a lower differential amplitude, however this only applies to differential signals. For single-ended applications, the swing can be larger, however  $V_{\rm IL}$  cannot be less than -0.3V and  $V_{\rm IH}$  cannot be more than  $V_{\rm DD}$  + 0.3V. Though some of the recommended components might not be used, the pads should be placed in the layout. They can be utilized for debugging purposes. The datasheet specifications are characterized and quaranteed by using a differential signal.

Figure 1. Recommended Schematic for Wiring a Differential Input to Accept Single-ended Levels

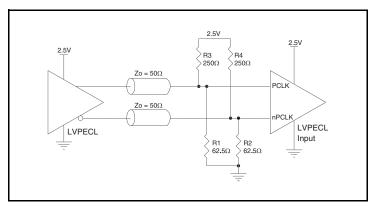

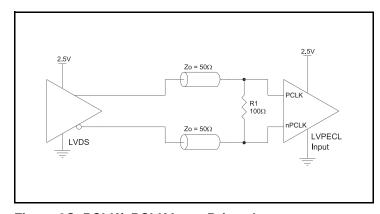

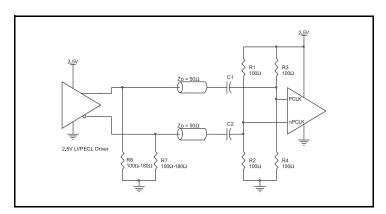

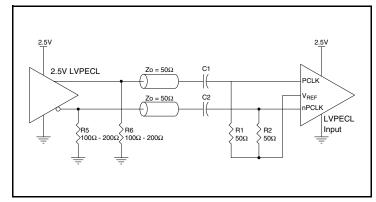

## 2.5V LVPECL Clock Input Interface

The PCLK /nPCLK accepts LVPECL, LVDS, and other differential signals. Both signals must meet the  $V_{PP}$  and  $V_{CMR}$  input requirements. *Figure 2A to Figure 2D* show interface examples for the PCLK/ nPCLK input driven by the most common driver types. The

input interfaces suggested here are examples only. If the driver is from another vendor, use their termination recommendation. Please consult with the vendor of the driver component to confirm the driver termination requirements.

Figure 2A. PCLK/nPCLK Input Driven by a 2.5V LVPECL Driver

Figure 2C. PCLK/nPCLK Input Driven by a 2.5V LVDS Driver

Figure 2B. PCLK/nPCLK Input Driven by a 2.5V LVPECL Driver with AC Couple

Figure 2D. PCLK/nPCLK Input Driven by a 2.5V LVPECL Driver AC Couple with V<sub>REF</sub> bias

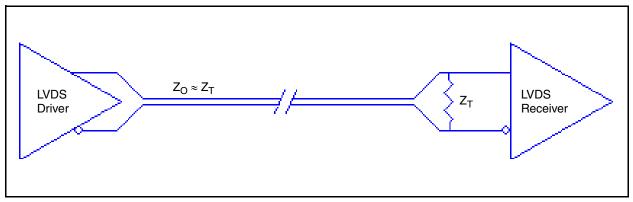

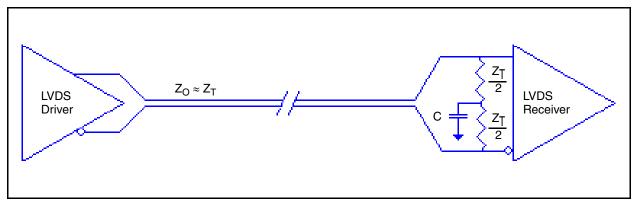

#### **LVDS Driver Termination**

For a general LVDS interface, the recommended value for the termination impedance  $(Z_T)$  is between  $90\Omega$  and  $132\Omega$ . The actual value should be selected to match the differential impedance  $(Z_0)$  of your transmission line. A typical point-to-point LVDS design uses a  $100\Omega$  parallel resistor at the receiver and a  $100\Omega$  differential transmission-line environment. In order to avoid any transmission-line reflection issues, the components should be surface mounted and must be placed as close to the receiver as possible. IDT offers a full line of LVDS compliant devices with two types of output structures: current source and voltage source. The

standard termination schematic as shown in *Figure 3A* can be used with either type of output structure. *Figure 3B*, which can also be used with both output types, is an optional termination with center tap capacitance to help filter common mode noise. The capacitor value should be approximately 50pF. If using a non-standard termination, it is recommended to contact IDT and confirm if the output structure is current source or voltage source type. In addition, since these outputs are LVDS compatible, the input receiver's amplitude and common-mode input range should be verified for compatibility with the output.

Figure 3A. Standard LVDS Termination

Figure 3B. Optional LVDS Termination

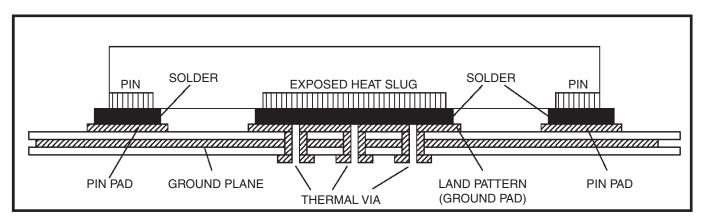

#### **VFQFN EPAD Thermal Release Path**

In order to maximize both the removal of heat from the package and the electrical performance, a land pattern must be incorporated on the Printed Circuit Board (PCB) within the footprint of the package corresponding to the exposed metal pad or exposed heat slug on the package, as shown in *Figure 4*. The solderable area on the PCB, as defined by the solder mask, should be at least the same size/shape as the exposed pad/slug area on the package to maximize the thermal/electrical performance. Sufficient clearance should be designed on the PCB between the outer edges of the land pattern and the inner edges of pad pattern for the leads to avoid any shorts.

While the land pattern on the PCB provides a means of heat transfer and electrical grounding from the package to the board through a solder joint, thermal vias are necessary to effectively conduct from the surface of the PCB to the ground plane(s). The land pattern must be connected to ground through these vias. The vias act as "heat pipes". The number of vias (i.e. "heat pipes") are application specific

and dependent upon the package power dissipation as well as electrical conductivity requirements. Thus, thermal and electrical analysis and/or testing are recommended to determine the minimum number needed. Maximum thermal and electrical performance is achieved when an array of vias is incorporated in the land pattern. It is recommended to use as many vias connected to ground as possible. It is also recommended that the via diameter should be 12 to 13mils (0.30 to 0.33mm) with 1oz copper via barrel plating. This is desirable to avoid any solder wicking inside the via during the soldering process which may result in voids in solder between the exposed pad/slug and the thermal land. Precautions should be taken to eliminate any solder voids between the exposed heat slug and the land pattern. Note: These recommendations are to be used as a guideline only. For further information, please refer to the Application Note on the Surface Mount Assembly of Amkor's Thermally/ Electrically Enhance Leadframe Base Package, Amkor Technology.

Figure 4. P.C. Assembly for Exposed Pad Thermal Release Path – Side View (drawing not to scale)

## **Power Considerations**

This section provides information on power dissipation and junction temperature for the 8SLVD2104. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The following is the power dissipation for  $V_{DD} = 2.5V + 5\% = 2.625V$ , which gives worst case results.

Maximum current at 85°C: I<sub>DD MAX</sub> = 156mA

Power MAX = V<sub>DD MAX</sub> \* I<sub>DD MAX</sub> = 2.625V \* 156mA = 409.5mW

## 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad directly affects the reliability of the device. The maximum recommended junction temperature is 125°C. Limiting the internal transistor junction temperature, Tj, to 125°C ensures that the bond wire and bond pad temperature remains below 125°C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + TA

Tj = Junction Temperature

$\theta_{JA}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

T<sub>A</sub> = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{JA}$  must be used. Assuming no air flow and a multi-layer board, the appropriate value is 46.2°C/W per *Table 6* below.

Therefore, Tj for an ambient temperature of 85°C with all outputs switching is:

$85^{\circ}\text{C} + 0.4095\text{W} * 46.2^{\circ}\text{C/W} = 103.9^{\circ}\text{C}$ . This is below the limit of  $125^{\circ}\text{C}$ .

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow and the type of board (multi-layer).

Table 6. Thermal Resistance  $\theta_{\text{JA}}$  for 28 Lead VFQFN, Forced Convection

| $\theta_{JA}$ at 0 Air Flow                 |          |          |          |  |  |  |

|---------------------------------------------|----------|----------|----------|--|--|--|

| Meters per Second                           | 0        | 1        | 2        |  |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 46.2°C/W | 39.4°C/W | 37.1°C/W |  |  |  |

# **Reliability Information**

# Table 7. $\theta_{\text{JA}}$ vs. Air Flow Table for a 28-Lead VFQFN

| $\theta_{JA}$ at 0 Air Flow                 |          |          |          |  |  |

|---------------------------------------------|----------|----------|----------|--|--|

| Meters per Second                           | 0        | 1        | 2        |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 46.2°C/W | 39.4°C/W | 37.1°C/W |  |  |

# **Transistor Count**

The transistor count for the 8SLVD2104 is: 394

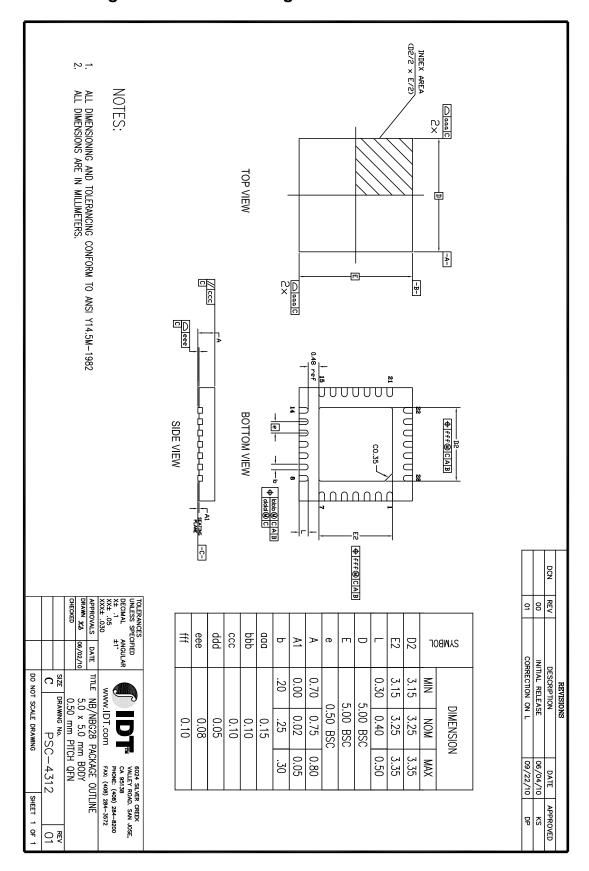

# 28-Lead VFQFN Package Outline and Package Dimensions

# **Ordering Information**

**Table 8. Ordering Information**

| Part/Order Number | Marking      | Package                  | Shipping Packaging                          | Temperature   |

|-------------------|--------------|--------------------------|---------------------------------------------|---------------|

| 8SLVD2104NBGI     | SLVD2104NBGI | 28 Lead VFQFN, Lead-Free | Tray                                        | -40°C to 85°C |

| 8SLVD2104NBGI8    | SLVD2104NBGI | 28 Lead VFQFN, Lead-Free | Tape & Reel<br>pin 1 orientation: EIA-481-C | -40°C to 85°C |

| 8SLVD2104NBGI/W   | SLVD2104NBGI | 28 Lead VFQFN, Lead-Free | Tape & Reel<br>pin 1 orientation: EIA-481-D | -40°C to 85°C |

Table 9. Pin 1 Orientation in Tape and Reel Packaging

| Part Number Suffix | Pin 1 Orientation      | Illustration                                                                                   |

|--------------------|------------------------|------------------------------------------------------------------------------------------------|

| 8                  | Quadrant 1 (EIA-481-C) | Correct Pin 1 ORIENTATION  CARRIER TAPE TOPSIDE (Round Sprocket Holes)  USER DIRECTION OF FEED |

| /W                 | Quadrant 2 (EIA-481-D) | Correct Pin 1 ORIENTATION CARRIER TAPE TOPSIDE (Round Sprocket Holes)  USER DIRECTION OF FEED  |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

## **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

## **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/