# Programmable USB Type-C PD Controller

### Hynetek Semiconductor Co., Ltd.

# **HUSB311**

#### **FEATURES**

- Dual-Role Port PD Compatible

- Attach/Detach Detection as Host, Device or DRP

- Current Capability Definition and Detection

- Cable Recognition

- Dead Battery Support

- VCONN Path Control

- Ultra-low Power Mode for Attach Detection

- Simple I<sup>2</sup>C Interface with Indication Pin

- Dual Slave Address for Dual Port Application

- BIST Mode Supported

- Programmable Default Settings

- 9-Ball WLCSP (WLCSP-9B) and 14-Lead QFN (QFN-14L) Packages

#### **APPLICATIONS**

**Smartphones**

**Tablets**

Laptops

Monitors

#### **GENERAL DESCRIPTION**

The HUSB311 is a USB Type-C PD controller that complies with the latest USB Type-C and PD3.0 standards. It implements the USB Type-C port power control for VCONN, USB Type-C CC control and sensing and USB PD Message delivery. HUSB311 has programmable  $R_{\text{P}}$  and  $R_{\text{d}}$  settings for each CC line. It does the USB type-C detection including attach and orientation. HUSB311 integrates a complete BMC encoding including a receiver and transmitter. With this physical layer of the USB BMC power delivery protocol, HUSB311 is able to handle the PD protocol and support any power up to 100W and perform role swap as needed. The BMC PD block enables full support for alternative interfaces of the Type-C specification.

HUSB311 uses I<sup>2</sup>C to communicate with the TCPM via employing an INT signal for requesting attention.

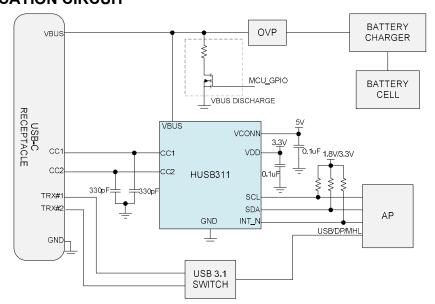

#### TYPICAL APPLICATION CIRCUIT

Figure 1. HUSB311 Typical Application Circuit

# **HUSB311**

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Typical Application Circuit                 | 1  |

| Table of Contents                           | 2  |

| Revision History                            | 2  |

| Pin Configuration and Function Descriptions | 3  |

| Recommended Operating Conditions            | 5  |

| Specifications                              | 6  |

| Absolute Maximum Ratings                    | 8  |

| Thermal Resistance                          | 8  |

| ESD Caution                                 | 8  |

| Functional Block Diagram                    | 9  |

| Theory of Operation                         | 10 |

| Communication Bus                           | 10 |

| Rx Buffer                                   | 10 |

| Dead Battery Mode                           | 11 |

| Registers                                   | 12 |

| Package Outline Dimensions                  | 23 |

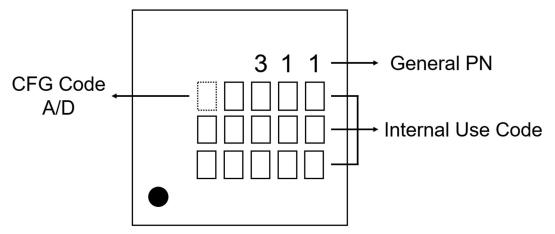

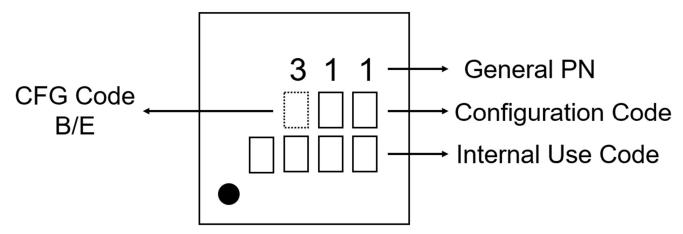

| Package TOP Marking                         | 25 |

| Ordering Guide                              | 26 |

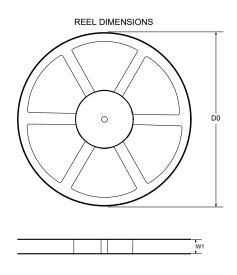

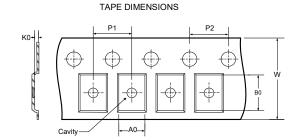

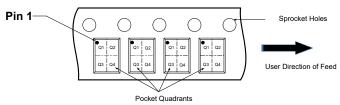

| Tape and Reel Information                   | 27 |

| Important Notice                            | 28 |

### **REVISION HISTORY**

| Version  | Date    | Descriptions                                        |  |  |  |

|----------|---------|-----------------------------------------------------|--|--|--|

| Rev. 2.0 | 08/2021 | Initial version                                     |  |  |  |

| Rev. 2.1 | 12/2021 | Update Package TOP Marking                          |  |  |  |

|          |         | Add CDM ESD Rating                                  |  |  |  |

|          |         | Update Thermal Resistance                           |  |  |  |

| Rev. 2.2 | 01/2022 | Update HUSB311_ALA to HUSB311_BLA                   |  |  |  |

| Rev. 2.3 | 03/2022 | Update HUSB311_BLA Package Top Marking              |  |  |  |

| Rev. 2.4 | 05/2022 | Add Tape and Reel Information                       |  |  |  |

| Rev. 2.5 | 07/2022 | ADD HUSB311_DCC& HUSB311_ELA                        |  |  |  |

|          |         | Modify Tape and Reel Information                    |  |  |  |

| Rev. 2.6 | 03/2023 | Modify the upper threshold of VCONN Present to 2.5V |  |  |  |

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

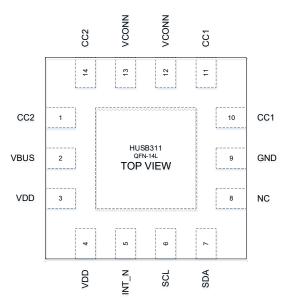

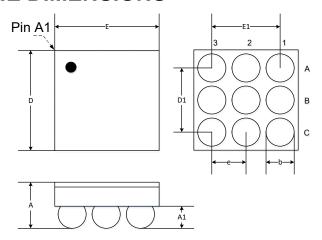

Figure 2. HUSB311\_ACC& HUSB311\_DCC Pin Assignment

Table 1. HUSB311\_ACC& HUSB311\_DCC Pin Function Descriptions

| Pin No. Pin Name Type <sup>1</sup> |       | Type <sup>1</sup> | Description                                                                                                                                        |  |  |  |  |  |

|------------------------------------|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A1                                 | CC2   | I/O               | Type-C connector Configuration Channel (CC2) pins. Initially used to determine when a attach event has occurred and what the orientation detected. |  |  |  |  |  |

| A2                                 | VBUS  | Α                 | VBUS input pin for attach and detach detection when operating as a Sink port (Device).                                                             |  |  |  |  |  |

| A3                                 | VDD   | P                 | Input supply voltage.                                                                                                                              |  |  |  |  |  |

| B1                                 | VCONN | Р                 | Regulated input pin connected to correct CC pin as VCONN to power Type-C full-featured cables and other accessories.                               |  |  |  |  |  |

| B2                                 | INT_N | 0                 | Active low and open drain type interrupt output used to prompt the processor to read the registers.                                                |  |  |  |  |  |

| B3                                 | SCL   | 1                 | I <sup>2</sup> C serial clock signal connected to the I <sup>2</sup> C master. The address is 0x4E or 0x3E.                                        |  |  |  |  |  |

| C1                                 | CC1   | I/O               | Type-C connector Configuration Channel (CC1) pins. Initially used to determine when a attach event has occurred and what the orientation detected. |  |  |  |  |  |

| C2                                 | GND   | Α                 | Ground plane.                                                                                                                                      |  |  |  |  |  |

| C3                                 | SDA   | I/O               | I <sup>2</sup> C serial data signal connected to the I <sup>2</sup> C master.                                                                      |  |  |  |  |  |

<sup>1</sup> Legend:

A = Analog Pin

P = Power Pin

D = Digital Pin

I = Input Pin O=Output Pin

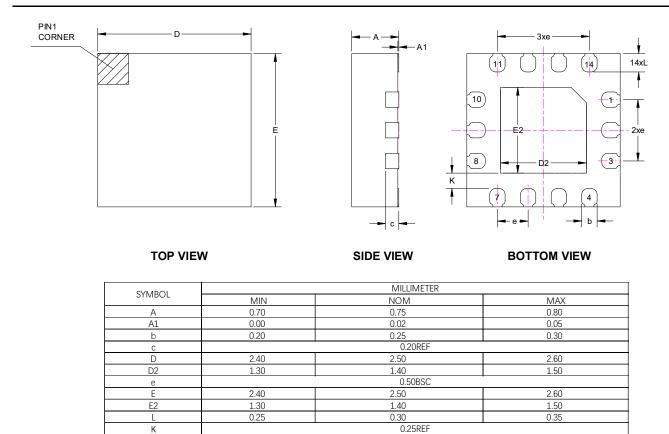

Figure 3. HUSB311\_BLA& HUSB311\_ELA Pin Assignment

Table 2. HUSB311\_BLA& HUSB311\_ELA Pin Function Descriptions

| Pin No. | Pin Name | Type <sup>1</sup> | Description                                                                                                                                        |  |  |  |  |  |

|---------|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1,14    | CC2      | I/O               | Type-C connector Configuration Channel (CC2) pins. Initially used to determine when a attach event has occurred and what the orientation detected. |  |  |  |  |  |

| 2       | VBUS     | Α                 | VBUS input pin for attach and detach detection when operating as a Sink port (Device).                                                             |  |  |  |  |  |

| 3,4     | VDD      | P                 | Input supply voltage.                                                                                                                              |  |  |  |  |  |

| 12,13   | VCONN    | P                 | Regulated input pin connected to correct CC pin as VCONN to power Type-C full-featured cables and other accessories.                               |  |  |  |  |  |

| 5       | INT_N    | 0                 | Active low and open drain type interrupt output used to prompt the processor to read the registers.                                                |  |  |  |  |  |

| 6       | SCL      | 1                 | I <sup>2</sup> C serial clock signal connected to the I <sup>2</sup> C master. The address is 0x4E or 0x3E.                                        |  |  |  |  |  |

| 10,11   | CC1      | I/O               | Type-C connector Configuration Channel (CC1) pins. Initially used to determine when a attach event has occurred and what the orientation detected. |  |  |  |  |  |

| 8       | NC       | Α                 | Not connected pin. This pin can be floating or connected to GND directly.                                                                          |  |  |  |  |  |

| 9       | GND      | Α                 | Ground plane.                                                                                                                                      |  |  |  |  |  |

| 7       | SDA      | I/O               | I <sup>2</sup> C serial data signal connected to the I <sup>2</sup> C master                                                                       |  |  |  |  |  |

1 Legend:

A = Analog Pin

P = Power Pin

D = Digital Pin

I = Input Pin O=Output Pin

# **RECOMMENDED OPERATING CONDITIONS**

#### Table 3.

| Parameter                              | Rating           |

|----------------------------------------|------------------|

| Supply Input Voltage                   | 3.0 V to 5.5 V   |

| VCONN Input Voltage                    | 3.3 V to 5.5 V   |

| VCONN Supply Current                   | 0 to 600 mA      |

| VCONN Supply Voltage                   | 3 V to 5.5 V     |

| Operating Temperature Range (Junction) | −40 °C to 125 °C |

| Ambient Temperature Range              | −40 °C to 85 °C  |

# **SPECIFICATIONS**

$V_{\text{DD}}$  = 3.3 V and  $T_{\text{A}}$  = 25  $^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

Table 4.

| Parameter                                                                                            | Symbol                     | Test Conditions/Comments                                                                | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| GENERAL PARAMETERS                                                                                   |                            |                                                                                         |      |      |      |      |

| Supply Voltage                                                                                       | V <sub>DD</sub>            |                                                                                         | 3    |      | 5.5  | V    |

| Supply UVLO Voltage                                                                                  | V <sub>UVLO_R</sub>        | Rising edge                                                                             |      | 2.7  |      | V    |

|                                                                                                      | V <sub>UVLO</sub> F        | Falling edge                                                                            |      | 2.64 |      | V    |

| DRP Toggle Current consumption                                                                       | I <sub>Q_DRP</sub>         | CC1/2 are togging and not attached. VCONN=5V, VDD current                               |      | 33   |      | μA   |

|                                                                                                      | IVCN5V_DRP                 | CC1/2 are togging and not attached. VCONN=5V, VCONN current                             |      | 20   |      | μA   |

|                                                                                                      | IQ_DRP1                    | CC1/2 are togging and not attached. VCONN=0V                                            |      | 33   |      | μA   |

| Operation Current                                                                                    | ICC_OPR                    | CC is attached with R <sub>p</sub> and in Bus Idle status                               |      | 2    |      | mA   |

| Type C CC Logic                                                                                      |                            |                                                                                         |      |      |      |      |

| Pull-down Voltage in Dead<br>Battery Mode with Source Default<br>R <sub>p</sub>                      | V <sub>RDB_DEF</sub>       | Source Default R <sub>p</sub> is 80μA±20%                                               | 0.25 |      | 1.5  | V    |

| Pull-down Voltage in Dead Battery Mode with Source 1.5A R <sub>p</sub>                               | VRDB_1.5A                  | Source Default R <sub>p</sub> is 180μA±8%                                               | 0.45 |      | 1.5  | V    |

| Pull-down Voltage in Dead<br>Battery Mode with Source 3A R <sub>p</sub>                              | V <sub>RDB_3A</sub>        | Source Default R <sub>p</sub> is 330µA±8%                                               | 0.85 |      | 2.5  | V    |

| Rd in Active Mode                                                                                    | R <sub>d</sub>             | VDD>V <sub>UVLO</sub> , CC is configured as R <sub>d</sub>                              | 4.6  | 5.1  | 5.6  | kΩ   |

| Attach Detection Threshold in Sink Mode                                                              | vRd_Snk                    | With R <sub>p</sub> is connected externally, CC is configured as R <sub>d</sub>         | 0.25 |      | 2.04 | V    |

| Default Pull up current source in Source Mode                                                        | IRP_DEF                    | CC is configured as Default R <sub>p</sub>                                              | 64   | 80   | 96   | μA   |

| 1.5A Pull up current source in Source Mode                                                           | IRP_1P5                    | CC is configured as 1.5A R <sub>p</sub>                                                 | 166  | 180  | 194  | μA   |

| 3A Pull up current source in Source Mode                                                             | IRP_3P0                    | CC is configured as 3A R <sub>p</sub>                                                   | 304  | 330  | 356  | μA   |

| Attach Detection Threshold in Source Mode                                                            | vRd_Src                    | With R <sub>d</sub> is connected externally, CC is configured as Default R <sub>p</sub> | 0.25 |      | 1.5  | V    |

|                                                                                                      |                            | With R <sub>d</sub> is connected externally, CC is configured as 1.5A R <sub>p</sub>    | 0.45 |      | 1.5  | V    |

|                                                                                                      |                            | With $R_d$ is connected externally, CC is configured as $3AR_p$                         | 0.85 |      | 2.45 | V    |

| PD BMC                                                                                               |                            |                                                                                         |      |      |      |      |

| Bit Rate                                                                                             | <b>f</b> BitRate           |                                                                                         | 270  | 300  | 330  | kbps |

| Maximum difference between the bit-rate during the part of the packet following the Preamble         | PBitRate                   |                                                                                         |      |      | 0.25 | %    |

| and the reference bit-rate                                                                           |                            |                                                                                         |      |      |      |      |

| Time from the end of last bit of a<br>Frame until the start of the first bit<br>of the next Preamble | t <sub>InterFrameGap</sub> |                                                                                         | 25   |      |      | μs   |

| Time before the start of the first bit of the Preamble when the transmitter shall start driving the  | t <sub>StartDrive</sub>    |                                                                                         | -1   |      | 1    | μs   |

| line                                                                                                 |                            |                                                                                         |      |      |      |      |

| Time to cease driving the line after the end of the last bit of the Frame                            | t <sub>EndDriveBMC</sub>   |                                                                                         |      |      | 23   | μs   |

| Parameter                                                             | Symbol                        | Test Conditions/Comments                                                               | Min  | Тур   | Max  | Unit |

|-----------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------|------|-------|------|------|

| Fall Time                                                             | t <sub>Fall</sub>             | 10 % and 90 % amplitude points, with CC pin load of 200pF and 5.1KΩ in parallel        | 300  |       |      | ns   |

| Time to cease driving the line after the final high-to-low transition | tHoldLowBMC                   |                                                                                        | 1    |       |      | μs   |

| Rise Time                                                             | t <sub>Rise</sub>             | 10 % and 90 % amplitude points, with CC pin load of 200pF and $5.1K\Omega$ in parallel | 300  |       |      | ns   |

| Voltage Swing                                                         | vSwing                        | With CC pin load of 1.2nF and $5.1K\Omega$ in parallel                                 | 1.05 | 1.125 | 1.2  | V    |

| TX Output Impedance                                                   | ZDriver                       | BMC Tx output impedance while HUSB311 is driving the CC line                           | 33   | 50    | 75   | Ω    |

| Time window for detecting non-idle                                    | t <sub>TransitionWindow</sub> |                                                                                        | 12   |       | 20   | μs   |

| Receiver Input Impedance                                              | ZBMCRx                        |                                                                                        | 1    |       |      | MΩ   |

| VCONN Source Control                                                  |                               |                                                                                        |      |       |      |      |

| VCONN FET Conduction Resistance                                       | Rvcn                          |                                                                                        |      |       | 1    | Ω    |

| VCONN OC Threshold                                                    | Ivcn_oc                       |                                                                                        |      | 650   |      | mA   |

| VCONN Present Threshold                                               | V <sub>VCN_PRS</sub>          |                                                                                        | 2    |       | 2.5  | V    |

| Time for VCONN to turn on                                             | t <sub>VCN_ON</sub>           | VCONN=5V and EN_VCONN=1b                                                               |      | 300   |      | μs   |

| VBUS Detection                                                        |                               |                                                                                        |      |       |      |      |

| VBUS Present Threshold                                                | V <sub>BUS_PRS_F</sub>        | Assert VBUS_PRESENT bit                                                                |      | 3.8   |      | V    |

|                                                                       | V <sub>BUS_PRS_R</sub>        | Set VBUS_PRESENT bit                                                                   |      | 4     |      | V    |

| VBUS vSave0V                                                          | vSafe0V                       | To trigger VBUS_80 interruption                                                        |      | 8.0   |      | V    |

| VBUS Measure Range                                                    | V <sub>BUS_M_RG</sub>         |                                                                                        | 4    |       | 22   | V    |

| VBUS Measure Step                                                     | LSB <sub>VBUS_M1</sub>        | VBUS=4-10V                                                                             |      | 0.5   |      | V    |

|                                                                       | LSB <sub>VBUS_M2</sub>        | VBUS=10-20V                                                                            |      | 1     |      | V    |

| I <sup>2</sup> C Electrical Characteristics                           |                               |                                                                                        |      |       |      |      |

| SCL Clock Frequency                                                   | f <sub>SCL</sub>              |                                                                                        | 50   |       | 1000 | kHz  |

| I <sup>2</sup> C Bus Supply Range                                     | V <sub>DD_I2C</sub>           |                                                                                        | 1.5  |       | 3.6  | V    |

| Low Level Input Voltage                                               | V <sub>IL</sub>               |                                                                                        |      |       | 0.4  | V    |

| High Level Input Voltage                                              | ViH                           |                                                                                        | 1.2  |       |      | V    |

| Low Level Output Voltage                                              | VoL                           | Open Drain Output, Sink Current=2mA                                                    |      |       | 0.4  | V    |

| Input Current Each IO Pin                                             | l <sub>1</sub>                | With 0.9V <sub>DD</sub> applied                                                        | -10  |       | 10   | μΑ   |

| Pulse width of spikes that must be suppressed by the input filter     | t <sub>sp</sub>               |                                                                                        |      |       | 50   | ns   |

| Data Hold Time                                                        | t <sub>HD:DAT</sub>           |                                                                                        | 0    |       |      | μs   |

| Data Set-Up Time                                                      | t <sub>SU:DAT</sub>           |                                                                                        | 50   |       |      | ns   |

| Leakage Current Each IO Pin                                           | ILKG                          | With VDD_I <sup>2</sup> C on each pin, VDD=5V                                          | -1   |       | 1    | μA   |

| INT_N PIN                                                             |                               |                                                                                        |      |       |      |      |

| _<br>Leakage Current                                                  | ILKG                          |                                                                                        | -1   |       | 1    | μA   |

| Low Level Output Voltage                                              | VoL                           | Sink Current=2mA                                                                       |      |       | 0.4  | V    |

#### ABSOLUTE MAXIMUM RATINGS

#### Table 5.

| Parameter                     | Rating           |

|-------------------------------|------------------|

| VBUS                          | -0.3 V to 30 V   |

| CC1,CC2                       | -0.3 V to 24 V   |

| VDD, VCONN, INT_N, SCL, SDA   | -0.3 V to 6 V    |

| Junction Temperature          | 150 °C           |

| Storage Temperature Range     | −65 °C to 150 °C |

| Soldering Conditions          | JEDEC J-STD-020  |

| Electrostatic Discharge (ESD) |                  |

| Human Body Model              | ±2000 V          |

| Charged Device Model          | ±500 V           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

#### **Table 6. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | θυς  | Unit |  |  |  |

|--------------|-----------------|------|------|--|--|--|

| QFN-14L      | 106             | 10.8 | °C/W |  |  |  |

| WLCSP-9B     | 118.3           | 68.9 | °C/W |  |  |  |

#### **ESD CAUTION**

#### **Electrostatic Discharge Sensitive Device.**

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

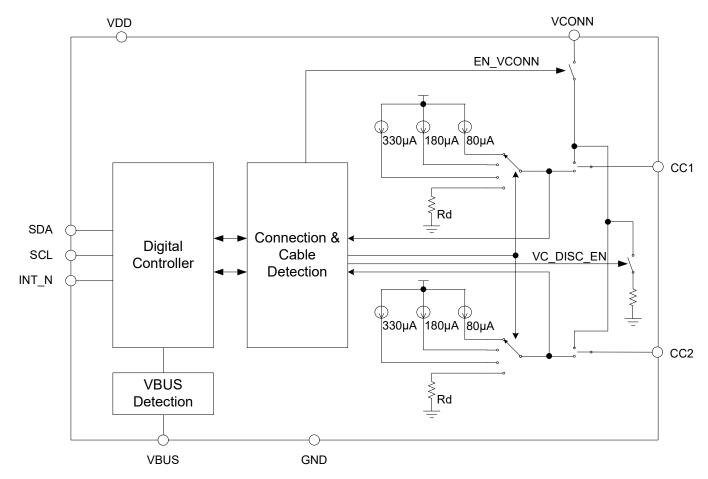

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 4. HUSB311 Functional Block Diagram

#### THEORY OF OPERATION

HUSB311 is a USB type C Port Controller (TCPC). It is a PD PHY level controller which handles VBUS and VCONN power connections, CC logic and USB PD message delivery through a simple register interface. HUSB311 implements the portion of protocol layer in the USB PD specification. It sends and receives messages constructed in the TCPM and places them on the CC connections. HUSB311 implements the following portions of the USB PD protocol layer:

- CRCReceiverTimer(PRL Tx wait for Phy Response state)

- RetryCounter(PRL Tx Check RetryCounter State)

- Message ID is not checked in HUSB311 when a non-GoodCRC message is received. Retried messages that are received are passed to the TCPM via I<sup>2</sup>C

- A message transmission is considered successful after receiving a GoodCRC response with the matching MessageID and SOP type

Two ways allow for asynchronous messages are received (see 0x50 definition).

Two way to handle BIST mode (see 0x19 definition).

#### **COMMUNICATION BUS**

HUSB311 communicates with TCPM via I<sup>2</sup>C bus. Two slave addresses are supported for HUSB311, 0x4E and 0x3E. It incorporates the I<sup>2</sup>C spec combined portion of SMBUS. There is an open drain active low output pin INT to indicate a change of state.

Some register of HUSB311 is 16-bit. It is important to access this register by writing or reading at the first address. See more details in the Register Map.

Once TCPM writes to a register or a bit that is reserved, HUSB311 ignores and does nothing.

#### **RX BUFFER**

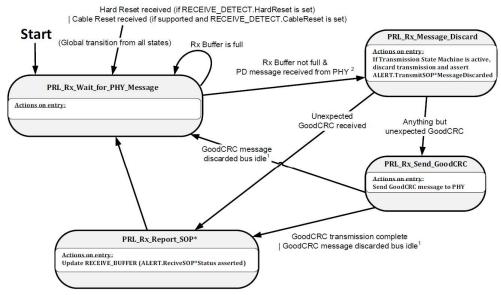

HUSB311 implements an Rx buffer for PD message reception. The main purpose of Rx buffer is:

- 1. Rx buffer is able to handle two set of 32 bytes date (1 byte Count number + 1 byte Frame type + 2 bytes Message Header+ 28 bytes data)

- 2. When there are already two sets of data stored in Rx buffer and the rest set of registers is 0, HUSB311 is not able to respond any following PD message (NOT include the CableReset, HardReset) unless TCPM reads Rx buffer and clear the RX\_BUF by set Alert.RX\_SOP\_MSG\_STATUS and Alert.RXBUF\_OVFLOW

HUSB311 performs RX\_BUFF as following state diagram. To start this state diagram, it depends on the RECEIVE\_DETECT register settings (0x2F). If a not enabled type of message is received, the state will not change anything. Please note that if an unexpected GoodCRC is received during the transition, this unexpected GoodCRC should be treated as a command PD message.

<sup>&</sup>lt;sup>1</sup> This transition is taken by the TCPC when the GoodCRC message has been discarded due to CC being busy, and after CC

Figure 5. Rx\_BUFF State Machine Diagram

After the GoodCRC according to the received PD message is sent in PRL\_Rx\_Send\_GoodCRC, HUSB311 is going to PRL Rx Report SOP\* state and assert INT N pin for attention.

TCPM handles the Alert interruption after INT\_N is asserted. The Rx Buff is accessed by TCPM to transmit the data. TCPM should clean the RX\_BUFF by writing Alert[2]=1. Once HUSB311 receives the write command to set Alert[2]=1.

#### **DEAD BATTERY MODE**

Low battery power could cause conditions in which communication over USB Type-C can no longer be maintained. When this situation occurs, it is critical to transition to attached. SNK state so that power from VBUS can be used to charge the battery back to an operational level. This condition is known as Dead Battery Mode.

The HUSB311 supports dead-battery mode by presenting Rd to both CC pins when VDD is no longer active.

In the dead-battery mode access to HUSB311 registers is not available. Upon exiting dead-battery mode, the HUSB311 enters mode dictated by the value of ROLE\_CONTROL register (Register 0x1A).

becomes idle again (see USB PD specification). Two alternate allowable transitions are shown.

Messages do not include Hard Reset or Cable Reset signals, or expected GoodCRC messages (GoodCRC message is only expected after the TCPC has sent a PD message, and the TCPC Protocol Layer State Machine is in PRL\_Tx\_Wait\_for\_PHY\_Response).

### **REGISTERS**

HUSB311 has several registers to configure the functions. The registers are accessed by the  $I^2C$  address of 0x4E or 0x3E. The detailed function is defined as below:

Table 7. Register Map

| Add  | Register Name  | Bit | Filed                    | Default | Туре | Description                                                                                             |

|------|----------------|-----|--------------------------|---------|------|---------------------------------------------------------------------------------------------------------|

| 0x00 | VENDOR_ID      | 7:0 | VID[7:0]                 | 0x99    | R    | A unique 16-bit unsigned integer Assigned by the USB-IF to the Vendor                                   |

| 0x01 |                | 7:0 | VID[15:8]                | 0x2E    | R    |                                                                                                         |

| 0x02 | PRODUCT_ID     | 7:0 | PID[7:0]                 | 0x11    | R    | A unique 16-bit unsigned integer. Assigned uniquely by the Vendor to identify the HUSB311               |

| 0x03 |                | 7:0 | PID[15:8]                | 0x03    | R    |                                                                                                         |

| 0x04 | DEVICE_ID      | 7:0 | DID[7:0]                 | 0x00    | R    | A unique 16-bit unsigned integer. Assigned by the Vendor to identify the version of the HUSB311         |

| 0x05 |                | 7:0 | DID[15:8]                | 0x00    | R    |                                                                                                         |

| 0x06 | USBTYPEC_REV   | 7:0 | USBTYPEC_RE V            | 0x11    | R    | Version number assigned by USB-IF (Currently at Revision 1.1 – 0001 0001)                               |

| 0x07 |                | 7:0 | Reserved                 | 0       | R    |                                                                                                         |

| 80x0 | USBPD_REV_VER  | 7:0 | USBPD_VER                | 0x11    | R    | 0001 0000 - Version 1.0                                                                                 |

|      |                |     |                          |         |      | 0001 0001 – Version 1.1 Etc                                                                             |

| 0x09 |                | 7:0 | USBPD_REV                | 0x20    | R    | 0010 0000 - Revision 2.0                                                                                |

| 0x0A | PD_INTERFACE_R | 7:0 | PDIF_VER                 | 0x10    | R    | 0001 0000 - Version 1.0                                                                                 |

|      | EV             |     |                          |         |      | 0001 0001 – Version 1.1 etc.                                                                            |

| 0x0B |                | 7:0 | PDIF_REV                 | 0x10    | R    | 0010 0000 – Revision 1.0                                                                                |

| 0x10 | ALERTL         | 7   | ALARM_VBUS_<br>VOLTAGE_H | 0       | R    | Not support                                                                                             |

|      |                | 6   | TX_SUCCESS               | 0       | RW   | 0b: Cleared                                                                                             |

|      |                |     |                          |         |      | 1b: Reset or SOP* message transmission successful                                                       |

|      |                | 5   | TX_DISCARD               | 0       | RW   | 0b: Cleared                                                                                             |

|      |                |     |                          |         |      | 1b: Reset or SOP* message transmission not sent due to incoming receive message                         |

|      |                | 4   | TX_FAIL                  | 0       | RW   | 0b: Cleared                                                                                             |

|      |                |     |                          |         |      | 1b: SOP* message transmission not successful, no GoodCRC response received on SOP* message transmission |

|      |                | 3   | RX_HARD_RES              | 0       | RW   | 0b: Cleared                                                                                             |

|      |                |     | ET                       |         |      | 1b: Received Hard Reset message                                                                         |

|      |                | 2   | RX_SOP_MSG_              | 0       | RW   | 0b: Cleared                                                                                             |

|      |                |     | STATUS                   |         |      | 1b: RECEIVE_BUFFER register changed                                                                     |

|      |                | 1   | POWER_STATU              | 0       | RW   | 0b: Cleared                                                                                             |

|      |                |     | S                        |         |      | 1b: Port status changed                                                                                 |

|      |                | 0   | CC_STATUS                | 0       | RW   | 0b : Cleared                                                                                            |

|      |                |     |                          |         |      | 1b : CC_STATUS is changed                                                                               |

| 0x11 | ALERTH         | 7   | Reserved                 | 0       | R    | Not support                                                                                             |

|      |                | 6   | Reserved                 | 0       | R    | Not support                                                                                             |

|      |                | 5   | Reserved                 | 0       | R    | Not support                                                                                             |

|      |                | 4   | Reserved                 | 0       | R    | Not support                                                                                             |

|      |                | 3   | Reserved                 | 0       | R    | Not support                                                                                             |

|      |                | 2   | RXBUF_OVFLO              | 0       | RW   | 0b: HUSB311 Rx buffer is functioning properly                                                           |

|      |                |     | W                        |         |      | 1b: HUSB311 Rx buffer has overflowed                                                                    |

| Add  | Register Name         | Bit | Filed                      | Default | Туре | Description                           |

|------|-----------------------|-----|----------------------------|---------|------|---------------------------------------|

|      |                       | 1   | FAULT                      | 0       | RW   | 0b: No Fault                          |

|      |                       |     |                            |         |      | 1b: A Fault has occurred              |

|      |                       | 0   | Reserved                   | 0       | R    | Not support                           |

| 0x12 | ALERT_MASKL           | 7   | M_ALARM_VBU<br>S_VOLTAGE_H | 1       | R    | Not support                           |

|      |                       | 6   | M_TX_SUCCES                | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | S                          |         |      | 1b: Interrupt unmasked                |

|      |                       | 5   | M_TX_DISCAR                | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | D                          |         |      | 1b: Interrupt unmasked                |

|      |                       | 4   | M_TX_FAIL                  | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     |                            |         |      | 1b : Interrupt unmasked               |

|      |                       | 3   | M_RX_HARD_R                | 1       | RW   | 0b : Interrupt masked                 |

|      |                       |     | ESET                       |         |      | 1b : Interrupt unmasked               |

|      |                       | 2   | M_RX_SOP_M                 | 1       | RW   | 0b : Interrupt masked                 |

|      |                       |     | SG_STATUS                  |         |      | 1b : Interrupt unmasked               |

|      |                       | 1   | M_POWER_ST                 | 1       | RW   | 0b : Interrupt masked                 |

|      |                       |     | ATUS                       |         |      | 1b : Interrupt unmasked               |

|      |                       | 0   | M_CC_STATUS                | 1       | RW   | 0b : Interrupt masked                 |

|      |                       |     |                            |         |      | 1b : Interrupt unmasked               |

| 0x13 | ALERT_MASKH           | 7   | Reserved                   | 0       | R    | Not support                           |

|      |                       | 6   | Reserved                   | 0       | R    | Not support                           |

|      |                       | 5   | Reserved                   | 0       | R    | Not support                           |

|      |                       | 4   | Reserved                   | 0       | R    | Not support                           |

|      |                       | 3   | Reserved                   | 1       | R    | Not support                           |

|      |                       | 2   | M_RXBUF_                   | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | OVFLOW                     |         |      | 1b: Interrupt unmasked                |

|      |                       | 1   | M_FAULT                    | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     |                            |         |      | 1b: Interrupt unmasked                |

|      |                       | 0   | M_ALARM_VBU<br>S_VOLTAGE_L | 1       | R    | Not support                           |

| 0x14 | POWER_STATUS_<br>MASK | 7   | Reserved                   | 0       | R    | Not support                           |

|      |                       | 6   | M_TCPC_INITI               | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | AL                         |         |      | 1b: Interrupt unmasked                |

|      |                       | 5   | M_SRC_NonDef ault          | 1       | R    | Not support                           |

|      |                       | 4   | M_SRC_VBUS                 | 1       | R    | Not support                           |

|      |                       | 3   | M_VBUS_PRES                | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | ENT_DETC                   |         |      | 1b: Interrupt unmasked                |

|      |                       | 2   | M_VBUS_PRES                | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | ENT                        |         |      | 1b: Interrupt unmasked                |

|      |                       | 1   | M_VCONN_                   | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | PRESENT                    |         |      | 1b: Interrupt unmasked                |

|      |                       | 0   | M_SINK_VBUS                | 1       | R    | Not support                           |

| 0x15 | FAULT_STATUS_M        | 7   | M_VCON_OV                  | 0       | RW   | 0b: Interrupt masked                  |

|      | ASK                   |     |                            |         |      | 1b: Interrupt unmasked                |

|      |                       | 6   | M_FORCE_OFF                | 1       | RW   | 0b: Interrupt masked                  |

|      |                       |     | _VBUS                      |         |      | 1b: Interrupt unmasked                |

|      | ]                     |     |                            |         |      | This field has no meaning for HUSB311 |

|      |                       | 5   | M_AUTO_DISC<br>_FAIL       | 1       | RW   | 0b: Interrupt masked                  |

| Add  | Register Name | Bit | Filed                     | Default | Type  | Description                                                                                                                                                                                                                                                                                            |

|------|---------------|-----|---------------------------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |               |     |                           |         |       | 1b: Interrupt unmasked                                                                                                                                                                                                                                                                                 |

|      |               |     |                           |         |       | This field has no meaning for HUSB311                                                                                                                                                                                                                                                                  |

|      |               | 4   | M_FORCE_DIS               | 1       | RW    | 0b: Interrupt masked                                                                                                                                                                                                                                                                                   |

|      |               |     | C_FAIL                    |         |       | 1b: Interrupt unmasked                                                                                                                                                                                                                                                                                 |

|      |               |     |                           |         |       | This field has no meaning for HUSB311                                                                                                                                                                                                                                                                  |

|      |               | 3   | M_VBUS_OC                 | 1       | RW    | 0b: Interrupt masked                                                                                                                                                                                                                                                                                   |

|      |               |     |                           |         |       | 1b: Interrupt unmasked                                                                                                                                                                                                                                                                                 |

|      |               |     |                           |         |       | This field has no meaning for HUSB311                                                                                                                                                                                                                                                                  |

|      |               | 2   | M_VBUS_OV                 | 1       | RW    | 0b: Interrupt masked                                                                                                                                                                                                                                                                                   |

|      |               |     |                           |         |       | 1b: Interrupt unmasked                                                                                                                                                                                                                                                                                 |

|      |               |     |                           |         |       | This field has no meaning for HUSB311                                                                                                                                                                                                                                                                  |

|      |               | 1   | M_VCON_OC                 | 1       | RW    | 0b: Interrupt masked                                                                                                                                                                                                                                                                                   |

|      |               | '   | voo.v_oo                  |         | ' ' ' | 1b: Interrupt unmasked                                                                                                                                                                                                                                                                                 |

|      |               | 0   | M_I <sup>2</sup> C_ERROR  | 1       | RW    | 0b: Interrupt masked                                                                                                                                                                                                                                                                                   |

|      |               |     | M_I O_EIXIXOIX            | '       | 1000  | 1b: Interrupt unmasked                                                                                                                                                                                                                                                                                 |

| 0x18 | CONFIG STANDA | 7   | H_IMPEDENCE               | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

| 0.00 | RD OUTPUT     | '   | H_IIVIFEDENCE             | 0       | N     | Not support                                                                                                                                                                                                                                                                                            |

|      |               | 6   | DBG ACC CO                | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

|      |               |     | NNECT O                   |         | '`    | Not support                                                                                                                                                                                                                                                                                            |

|      |               | 5   | AUDIO_ACC_C               | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

|      |               |     | ONNECT                    |         |       |                                                                                                                                                                                                                                                                                                        |

|      |               | 4   | ACTIVE CABLE              | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

|      |               |     | _CONNECT                  |         |       |                                                                                                                                                                                                                                                                                                        |

|      |               | 3:2 | MUX_CTRL                  | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

|      |               | 1   | CONNECT_PR<br>ESENT       | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

|      |               | 0   | CONNECT_ORI               | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

| 0x19 | TCPC_CONTROL  | 7   | Reserved                  | 0       | R     |                                                                                                                                                                                                                                                                                                        |

|      | _             | 6   | EN_LK4CNCT_<br>ALERT      | 0       | RW    | 0b: Disable ALERT.CcStatus assertion when CC_STATUS.Looking4Connection changes                                                                                                                                                                                                                         |

|      |               |     |                           |         |       | 1b: Enable ALERT.CcStatus assertion when CC STATUS.Looking4Connection changes                                                                                                                                                                                                                          |

|      |               | 5:4 | Reserved                  | 0       | R     |                                                                                                                                                                                                                                                                                                        |

|      |               | 3:2 | I <sup>2</sup> C_CK_STRET | 0       | R     | Not support                                                                                                                                                                                                                                                                                            |

|      |               | 0.2 | CH CH                     |         | '`    | The support                                                                                                                                                                                                                                                                                            |

|      |               | 1   | BIST_TEST_M<br>ODE        | 0       | RW    | Normal Operation. Incoming messages enabled by RECEIVE_DETECT passed to TCPM via Alert                                                                                                                                                                                                                 |

|      |               |     |                           |         |       | 1: BIST Test Mode. Incoming messages enabled by RECEIVE_DETECT result in GoodCRC response but may not be passed to the TCPM via Alert. HUSB311 may temporarily store incoming messages in the Rx Buffer, but this may or may not result in a Receive SOP* Message Status or a Rx Buffer Overflow alert |

|      |               | 0   | PLUG_ORIENT               | 0       | RW    | 0b: When VCONN is enabled (0x1C[0]=1), apply it to the CC2 pin. Monitor the CC1 pin for BMC communications                                                                                                                                                                                             |

|      |               |     |                           |         |       | 1b: When VCONN is enabled (0x1C[0]=1), apply it to the CC1 pin. Monitor the CC2 pin for BMC communications                                                                                                                                                                                             |

| 0x1A | ROLE_CONTROL  | 7   | Reserved                  | 0       | R     |                                                                                                                                                                                                                                                                                                        |

| Add  | Register Name | Bit | Filed                             | Default | Туре | Description                                                                                                                                                    |

|------|---------------|-----|-----------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |               | 6   | DRP                               | 0       | RW   | 0b: No DRP. Bits B30 determine Rp/Rd settings                                                                                                                  |

|      |               |     |                                   |         |      | 1b: DRP                                                                                                                                                        |

|      |               | 5:4 | RP_VALUE                          | 0       | RW   | 00b: Rp default                                                                                                                                                |

|      |               |     | _                                 |         |      | 01b: Rp 1.5 A                                                                                                                                                  |

|      |               |     |                                   |         |      | 10b: Rp 3.0 A                                                                                                                                                  |

|      |               |     |                                   |         |      | 11b: Reserved                                                                                                                                                  |

|      |               | 3:2 | CC2                               | 10      | RW   | 00b : Reserved                                                                                                                                                 |

|      |               |     |                                   |         |      | 01b: Rp (Use Rp definition in B54)                                                                                                                             |

|      |               |     |                                   |         |      | 10b : Rd                                                                                                                                                       |

|      |               |     |                                   |         |      | 11b: Open (Disconnect or don't care)                                                                                                                           |

|      |               | 1:0 | CC1                               | 10      | RW   | 00b : Reserved                                                                                                                                                 |

|      |               |     |                                   |         |      | 01b: Rp (Use Rp definition in B54)                                                                                                                             |

|      |               |     |                                   |         |      | 10b: Rd                                                                                                                                                        |

|      |               |     |                                   |         |      | 11b: Open (Disconnect or don't care)                                                                                                                           |

| 0x1B | FAULT_CONTROL | 7   | DIS_VCON_OV                       | 0       | RW   | 0b: VCONN OV Fault detection circuit enabled when EN_VCONN=1 (Reg0x1C[0]=1)                                                                                    |

|      |               |     |                                   |         |      | 1b: VCONN OV Fault detection circuit disabled                                                                                                                  |

|      |               | 6:5 | Reserved                          | 0       | R    | Not support                                                                                                                                                    |

|      |               | 4   | DIS_FORCE_O<br>FF_VBUS            | 0       | R    | Not support                                                                                                                                                    |

|      |               | 3   | DIS_VBUS_DIS<br>C_FAULT_TIME<br>R | 0       | R    | Not support                                                                                                                                                    |

|      |               | 2   | DIS_VBUS_OC                       | 0       | R    | Not support                                                                                                                                                    |

|      |               | 1   | DIS_VBUS_OV                       | 0       | R    | Not support                                                                                                                                                    |

|      |               | 0   | DIS_VCON_OC                       | 0       | RW   | 0b: Fault detection circuit enabled when EN_VCONN=1 (Reg0x1C[0]=1)                                                                                             |

|      |               |     |                                   |         |      | 1b: Fault detection circuit disabled                                                                                                                           |

| 0x1C | POWER_CONTRO  | 7   | Reserved                          | 0       | R    |                                                                                                                                                                |

|      |               | 6   | VBUS_VOL_<br>MONITOR              | 0       | R    | Not support                                                                                                                                                    |

|      |               | 5   | DIS_VOL_ALAR<br>M                 | 0       | R    | Not support                                                                                                                                                    |

|      |               | 4   | AUTO_DISC_<br>DISCNCT             | 0       | R    | Not support                                                                                                                                                    |

|      |               | 3   | BLEED_DISC                        | 0       | R    | Not support                                                                                                                                                    |

|      |               | 2   | FORCE_DISC                        | 0       | R    | Not support                                                                                                                                                    |

|      |               | 1   | VCONN_<br>POWER_SPT               | 0       | RW   | 0b: HUSB311 delivers at least 1W on VCONN.  1b: HUSB311 delivers at least the power indicated in DEVICE_CAPABILITIES.VCONN_POWER                               |

|      |               | 0   | EN_VCONN                          | 0       | RW   | This bit control the path from VCONN pin to the repopulated CC pin (unattached CC).  0b: Disable VCONN Path(default)  1b: Enable VCONN Source to unattached CC |

| 0x1D | CC_STATUS     | 7:6 | Reserved                          | 0       | R    |                                                                                                                                                                |

|      |               | 5   | Look4Connectio<br>n               | 0       | R    | 0b: the HUSB311 is NOT actively looking for a connection. A transition from 1 to 0 indicates a potential connection has been found                             |

| Add | Register Name | Bit | Filed              | Default | Туре | Description                                                                                                                                                                |

|-----|---------------|-----|--------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |               |     |                    |         |      | 1b: the HUSB311 is looking for a connection (toggling as a DRP or looking for a connection as Sink/Source only condition)                                                  |

|     |               | 4   | Connect_RESU<br>LT | 1       | R    | 0b: the HUSB311 is currently presenting Rp 1b: the HUSB311 is currently presenting Rd                                                                                      |

|     |               | 3:2 | CC2_STATUS         | 0       | R    | If (ROLE_CONTROL.CC2 = Rp) or (Connect_RESULT = 0)                                                                                                                         |

|     |               |     |                    |         |      | 00b: SRC.Open (Open, Rp)                                                                                                                                                   |

|     |               |     |                    |         |      | 01b: SRC.Ra (below maximum vRa)                                                                                                                                            |

|     |               |     |                    |         |      | 10b: SRC.Rd (within the vRd range)                                                                                                                                         |

|     |               |     |                    |         |      | 11b: reserved  If (ROLE_CONTROL.CC2 = Rd) or (Connect_RESULT = 1)                                                                                                          |

|     |               |     |                    |         |      | 00b: SNK.Open (Below maximum vRa)                                                                                                                                          |

|     |               |     |                    |         |      | 01b: SNK.Default (Above minimum vRd-<br>Connect)                                                                                                                           |

|     |               |     |                    |         |      | 10b: SNK.Power1.5 (Above minimum vRd-Connect) Detects Rp 1.5 A                                                                                                             |

|     |               |     |                    |         |      | 11b: SNK.Power3.0 (Above minimum vRd-Connect) Detects Rp 3.0 A                                                                                                             |

|     |               |     |                    |         |      | If ROLE_CONTROL.CC2 = 00b, this field is set to 00b                                                                                                                        |

|     |               |     |                    |         |      | If ROLE_CONTROL.CC2 = Open, this field is set to 00b and this change doesn't cause an Alert.CCStatus                                                                       |

|     |               |     |                    |         |      | This field always returns 00b if (CC_STATUS[5] = 1), that means the CCStatus is not updated to these bits or (POWER_CONTROL.EN_VCONN = 1 and TCPC CONTROL.PLUG ORIENT =0). |

|     |               |     |                    |         |      | Otherwise, the returned value depends upon ROLE_CONTROL.CC2                                                                                                                |

|     |               | 1:0 | CC1_STATUS         | 0       | R    | If (ROLE_CONTROL.CC1 = Rp) or (Connect_RESULT = 0)                                                                                                                         |

|     |               |     |                    |         |      | 00b: SRC.Open (Open, Rp)                                                                                                                                                   |

|     |               |     |                    |         |      | 01b: SRC.Ra (below maximum vRa)                                                                                                                                            |

|     |               |     |                    |         |      | 10b: SRC.Rd (within the vRd range)                                                                                                                                         |

|     |               |     |                    |         |      | 11b: reserved  If (ROLE_CONTROL.CC1 = Rd) or Connect_RESULT= 1)                                                                                                            |

|     |               |     |                    |         |      | 00b: SNK.Open (Below maximum vRa)                                                                                                                                          |

|     |               |     |                    |         |      | 01b: SNK.Default (Above minimum vRd-Connect)                                                                                                                               |

|     |               |     |                    |         |      | 10b: SNK.Power1.5 (Above minimum vRd-<br>Connect) Detects Rp-1.5 A                                                                                                         |

|     |               |     |                    |         |      | 11b: SNK.Power3.0 (Above minimum vRd-Connect) Detects Rp-3.0 A                                                                                                             |

|     |               |     |                    |         |      | If ROLE_CONTROL.CC1 = 00b, this field is set to 00b                                                                                                                        |

|     |               |     |                    |         |      | If ROLE_CONTROL.CC1 = Open, this field is set to 00b and this change doesn't cause an Alert.CCStatus                                                                       |

|     |               |     |                    |         |      | This field always returns 00b if (CC_STATUS[5] = 1), that means the CCStatus is not updated to these bits or (POWER_CONTROL.EN_VCONN = 1 and TCPC CONTROL.PLUG ORIENT =    |

| Add  | Register Name | Bit | Filed                  | Default | Туре | Description                                                                                                                                                                                                      |

|------|---------------|-----|------------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | . 3           |     |                        |         | 71   | 1). Otherwise, the returned value depends upon ROLE CONTROL.CC1                                                                                                                                                  |

| 0x1E | POWER_STATUS  | 7   | DBG_ACC_CO<br>NNECT    | 0       | R    | Not support                                                                                                                                                                                                      |

|      |               | 6   | TCPC_INITIAL           | 0       | R    | 0b: The HUSB311 has completed initialization and all registers are valid 1b: The HUSB311 is still performing internal initialization and the only registers that are guaranteed to return the correct values are |

|      |               |     |                        |         |      | 00h0Fh                                                                                                                                                                                                           |

|      |               | 5   | SRC_NonDefaul<br>t     | 0       | R    | Not support                                                                                                                                                                                                      |

|      |               | 4   | SRC_VBUS               | 0       | R    | Not support                                                                                                                                                                                                      |

|      |               | 3   | VBUS_PRESEN<br>T_DETC  | 1       | R    | This bit reflects the status of 0x90[1] 0b: VBUS Present Detection Disabled (Reg0x90[1]=0b) 1b: VBUS Present Detection Enabled (Reg0x90[1]=1b)                                                                   |