#### **Features**

- ±250mV input voltage range optimized for current measurement using shunt resistors

- Low offset error and drift: ±0.2mV (max), ±0.9μV/°C (max)

- Fixed gain: 8.2

- Low gain error and drift:

±0.3% (max), ±30ppm/°C (max)

- Low nonlinearity and drift: 0.03%, ±1ppm/°C (typical)

- 3.3V to 5V operation on high side

- System-level diagnostic features

- Safety-related certifications:

7071V<sub>PK</sub> reinforced isolation per DIN VDE V

0884-17: 2021-10

5.0kV<sub>RMS</sub> isolation for 1 minute per UL1577

- High CMTI: 150kV/μs (typical)

## **Applications**

- Shunt-resistor-based current sensing in:

- Motor drives

- Frequency inverters

- Uninterruptible power supplies

### **Description**

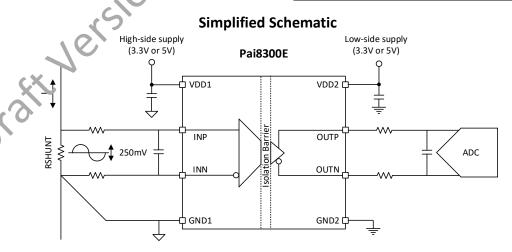

The Pai8300E is a precision, isolated amplifier with an output separated from the input circuitry by an isolation barrier that is highly resistant to magnetic interference. This barrier is certified to provide reinforced galvanic isolation of up to 5kV<sub>RMS</sub> according to VDE V 0884-17 and UL1577. Used in conjunction with isolated power supplies, this isolated amplifier separates parts of the system that operate on different common-mode varage levels and protects lower-voltage parts from damage.

The input of the Pais 300E is optimized for direct connection to shunt resistors or other low voltage level signal sources. The excellent performance of the device supports accurate current control resulting in system-level power savings. The integrated missing high-side supply voltage detection and input common mode overvoltage detection simplify system-level design and diagnostics.

The Pai8300E is specified over the extended industrial temperature range of -40°C to +125°C.

| PART NUMBER  | PACKAGE   | BODY SIZE    |

|--------------|-----------|--------------|

| Pai8300E-W5R | WB SOIC-8 | 5.85mm*7.5mm |

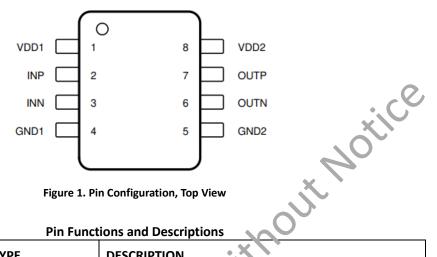

# 1 Pin Configurations and Functions

Figure 1. Pin Configuration, Top View

**Pin Functions and Descriptions**

| PIN NO. | PIN NAME | ТҮРЕ             | DESCRIPTION                                          |

|---------|----------|------------------|------------------------------------------------------|

| 1       | VDD1     | High-side power  | High-side power supply, 3.0V to 5.5V relative to GNI |

| 2       | INP      | Analog input     | Noninverting analog input.                           |

| 3       | INN      | Analog input     | Inverting analog input.                              |

| 4       | GND1     | High-side ground | Ngn-side analog ground.                              |

| 5       | GND2     | Low-side ground  | Low-side analog ground.                              |

| 6       | OUTN     | Analog output    | Inverting analog output.                             |

| 7       | OUTP     | Analog o Itput   | Noninverting analog output.                          |

| 8       | VDD2     | Lov-side power   | Low-side power supply, 3.0V to 5.5V relative to GNE  |

| 2/8/    | Ners     |                  |                                                      |

## 2 Specifications

# 2.1 Absolute Maximum Ratings (1)

| Parameter                             | Symbol                                       | MIN      | MAX      | UNIT     |

|---------------------------------------|----------------------------------------------|----------|----------|----------|

| Power supply                          | VDD1 to GND1                                 | -0.3     | 6.5      | V        |

| Power supply                          | VDD2 to GND2                                 | -0.3     | 6.5      | V        |

| Input voltage                         | INP, INN                                     | GND1-6   | VDD1+0.5 | V        |

| Output voltage                        | OUTP, OUTN                                   | GND2-0.5 | VDD2+0.5 | <b>7</b> |

| Input current                         | Continuous, any pin except power-supply pins | -10      | 10       | mA       |

| Junction temperature, T <sub>J</sub>  | $T_J$                                        | -40      | 150      | °C       |

| Storage temperature, T <sub>stg</sub> | $T_{stg}$                                    | -65      | 150      | °C       |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 2.2 ESD Ratings

|                    |                         |                                                                       | VALUE | UNIT                                  |

|--------------------|-------------------------|-----------------------------------------------------------------------|-------|---------------------------------------|

| V                  | Flootrostatio dicabarga | Human-body model (HBM), per 4/NSI/ESDA/JEDEC JS-001 <sup>(1)</sup>    | ±2000 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1000 | V                                     |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 2.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

| Symbol                                            | Description               | MIN   | MAX      | UNIT |

|---------------------------------------------------|---------------------------|-------|----------|------|

| High side power supply                            | VDD1 to GND1              | 3.0   | 5.5      | V    |

| Low side power supply                             | VDD2 to GND2              | 3.0   | 5.5      | V    |

| Differential input voltage before clipping output | VIN = VINP — VINN         | -320  | 320      | mV   |

| Specified linear differential input full-scale    | VIN = VINP — VINN         | -250  | 250      | mV   |

| Absolute common-mode in out voltage (1)           | (VINP + VINN) / 2 to GND1 | -2    | VDD1     | V    |

| Operating common-mode input voltage               | (VINP + VINN) / 2 to GND1 | -0.16 | VDD1-2.1 |      |

| T <sub>A</sub>                                    | Ambient Temperature       | -40   | 125      | °C   |

<sup>(1)</sup> Steady-state voltage supported by the device in case of a system failure. See the specified common-mode input voltage  $V_{CM}$  for normal operation. Observe analog input voltage range as specified in the Absolute Maximum Ratings table.

## 2.4 The rmal Information

| Symbol                 | Parameter                                 | VALUE | UNIT |

|------------------------|-------------------------------------------|-------|------|

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance    | 85    | °C/W |

| R <sub>θJC (top)</sub> | Junction-to-case (top) thermal resistance | 26    | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance      | 43    | °C/W |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe maintacturing with a standard ESD control process.

## 2.5 Insulation Specifications

| Parameter | Description                | Test condition                                          | VALUE | UNIT |

|-----------|----------------------------|---------------------------------------------------------|-------|------|

| CLR       | External clearance         | Shortest pin-to-pin distance through air                | ≥8    | mm   |

| CPG       | External creepage          | Shortest pin-to-pin distance across the package surface | ≥ 8   | mm   |

| CTI       | Comparative tracking index | DIN EN 60112 (VDE 0303-11); IEC 60112                   | ≥ 600 | V    |

|           | Material group             | According to IEC 60664-1                                | 1     |      |

|           | Overvoltage category       | Rated mains voltage ≤ 300 V <sub>RMS</sub>              | I-IV  | 0    |

|           | Overvoitage category       | Rated mains voltage ≤ 600 V <sub>RMS</sub>              | I-Ui  |      |

### DIN V VDE V 0884-17 (VDE V 0884-17): 2021-10<sup>(2)</sup>

| Parameter         | Description                                                                                | Test condition                                                                                                                         | VALUE              | UNIT      |

|-------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|

| $V_{IORM}$        | Maximum repetitive peak isolation voltage                                                  | AC voltage                                                                                                                             | 2121               | $V_{PK}$  |

| \/                | Maximum working isolation                                                                  | AC voltage (sine wave)                                                                                                                 | 1500               | $V_{RMS}$ |

| $V_{IOWM}$        | voltage                                                                                    | DC voltage                                                                                                                             | 2121               | $V_{DC}$  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                                                        | $V_{TEST} = V_{IOTM}$ , $t = 60 \text{ sec}$ rualification)<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , $t = 1 \times (100\%$<br>production) | 7071               | $V_{PK}$  |

| $V_{IOSM}$        | Maximum surge isolation voltage (3)                                                        | Test method per IEC 62368-1, 1.2/50<br>μs wavefor η, V-EST = 1.6 × V <sub>IOSM</sub><br>(qualification)                                | 6250               | $V_{PK}$  |

|                   | Input to Output Test Voltage,<br>Method A                                                  | V <sub>IORN</sub> × 1 875 = Vpd (m), tini = 60 sec,<br>tr. = 10 sec, partial discharge < 5 pC                                          | 3977               | $V_{PK}$  |

| Vpd (m)           | After Environmental Tests Subgroup1 After input and/or Safety Test Subgroup2 and Subgroup1 | V <sub>IORM</sub> × 1.6 = Vpd (m), tini = 60 sec, tm<br>= 10 sec, partial discharge < 5 pC                                             | 3394               | $V_{PK}$  |

|                   | Method b1; At routine test<br>(100% production) and<br>preconditioning (type test) (4)     | V <sub>IORM</sub> × 1.2 = Vpd (m), tini =1 sec, tm = 1 sec, partial discharge < 5 pC                                                   | 2545               | $V_{PK}$  |

| $C_{IO}$          | Barrier capacitance, input to output (5)                                                   | $V_{IO} = 0.4 \sin(2\pi ft)$ , f =1 MHz                                                                                                | 1.2                | pF        |

|                   |                                                                                            | V <sub>IO</sub> = 500 V at T <sub>A</sub> = 25°C                                                                                       | > 10 <sup>12</sup> | Ω         |

| $R_{IO}$          | Isolation resistance, input to output (5)                                                  | V <sub>IO</sub> = 500 V at 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                              | > 10 <sup>11</sup> | Ω         |

|                   | output (4)                                                                                 | V <sub>IO</sub> = 500 V at T <sub>S</sub> =150°C                                                                                       | > 10 <sup>9</sup>  | Ω         |

| 5                 | Pollution degree                                                                           |                                                                                                                                        | 2                  |           |

| .7                | Climatic category                                                                          |                                                                                                                                        | 40/125/21          |           |

#### **UL 1577**

| Parameter        | Description       | Test condition                                                               | VALUE | UNIT             |

|------------------|-------------------|------------------------------------------------------------------------------|-------|------------------|

| V                | Withstand         | $V_{TEST} = V_{ISO} = 5000V_{RMS}$ , t = 60 sec.(qualification),             | 5000  | V                |

| V <sub>ISO</sub> | isolation voltage | $V_{TEST} = 1.2 \times V_{ISO} = 6000 V_{RMS}$ , t = 1 sec (100% production) | 5000  | V <sub>RMS</sub> |

<sup>(1)</sup> Apply creepage and clearance requirements according to the specific equipment isolation standards of an application. Care must be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed circuit board (PCB) do not reduce this distance. Creepage and clearance on a PCB become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a PCB are used to help increase these specifications.

- (2) This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety rating, shall be ensured by means of suitable protective circuits.

- (3) Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (5) All pins on each side of the barrier are tied together, creating a two-pin device.

#### 2.6 Safety-Related Certifications

| cqc | Certified according to GB<br>4943.1-2022                                                                  | Basic insulation at 1118V <sub>RMS</sub> (1580V <sub>PK</sub> )<br>Reinforced insulation at 557V <sub>RMS</sub> (788V, K)                                                                               | Pending        |

|-----|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| UL  | Recognized under UL 1577<br>Component Recognition<br>Program                                              | Single protection, 5kV <sub>RMS</sub>                                                                                                                                                                   | Pending        |

| VDE | Certified according to DIN V<br>VDE V 0884-17:2021-10,<br>and DIN EN 60950-1 (VDE<br>0805 Teil 1):2014-08 | Reinforced Insulation Maximum Transient Isolation voltage, 7071V <sub>PK</sub> ; Maximum Repetitive Peak Isolation Voltage, 2121V <sub>PK</sub> ; Maximum Surge Is all tion Voltage, 10kV <sub>PK</sub> | File: 40056491 |

## 2.7 Safety-Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

| Symbol | Description                     | Test condition                                                                           | MIN | TYP | MAX  | UNIT |

|--------|---------------------------------|------------------------------------------------------------------------------------------|-----|-----|------|------|

|        | Safety output supply current    | R <sub>0JA</sub> =85°C/W, T <sub>J</sub> =150°C,<br>T <sub>A</sub> =25°C, VDD1=VDD2=5.5V | ı   | ı   | 294  | mA   |

| Is     | Safety output supply current    | R <sub>0JA</sub> =85°C/W, T <sub>J</sub> =150°C,<br>T <sub>A</sub> =25°C, VDD1=VDD2=3.3V | -   | -   | 445  | mA   |

| Ps     | Safety supply power             | R <sub>0JA</sub> =85°C/W, T <sub>J</sub> =150°C,<br>T <sub>A</sub> =25°C                 |     |     | 1470 | mW   |

| Ts     | Maximum Safety<br>teat perature |                                                                                          |     |     | 150  | °C   |

The maximum safety temperature, TS, has the same value as the maximum junction temperature, TJ, specified for the device. The IS and PS par meters represent the safety current and safety power respectively. The maximum limits of IS and PS should not be exceeded. These limits vary with the ambient temperature, TA. The junction-to-air thermal resistance, R $\theta$ JA, in the Thermal Information table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter: TJ = TA + R $\theta$ JA × P, where P is the power dissipated in the device. TJ (max) = TS = TA + R $\theta$ JA × PS, where TJ (max) is the maximum allowed junction temperature. PS = IS × VI, where VI is the maximum input voltage.

# **3 Specifications**

### **3.1 Electrical Characteristics**

Minimum and maximum specifications of the Pai8300E apply from TA=-40°C to +125°C, VDD1=3.0V to 5.5V, VDD2=3.0V to 5.5V, INP=-250mV to +250mV, and INN=GND1=0V; typical specifications are at TA=25°C, VDD1=5V, and VDD2=3.3V (unless otherwise noted)

| Paramete         | r                                                            | Test condition                                                                                            | MIN        | TYP    | MAX   | UNIT              |

|------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------|--------|-------|-------------------|

| ANALOG I         | NPUT                                                         |                                                                                                           |            |        |       | 0                 |

|                  | Common-mode overvoltage detection level                      |                                                                                                           | VDD1-<br>2 |        | 310   | V                 |

| $V_{CMov}$       | Hysteresis of common-<br>mode overvoltage<br>detection level |                                                                                                           |            | 100    | 0     | mV                |

| Vos              | Input offset voltage (1)                                     | initial, at TA = 25°C,<br>V <sub>INP</sub> = V <sub>INN</sub> = GND1                                      | -0.2       | ±0 01  | 0.2   | mV                |

| TCVos            | Input offset drift (1)                                       |                                                                                                           | -0.9       | ±0.1   | 0.9   | μV/°C             |

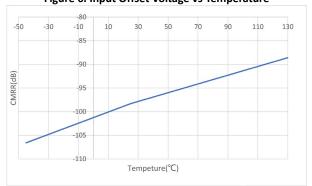

| CMRR             | Common-mode rejection ratio                                  | $f_{IN} = 0 \text{ Hz},$ $V_{CM} \text{ min} \le V_{CM} \le V_{CM} \text{ max}$ $f_{IN} = 10 \text{KHz},$ |            | 85     |       | dB                |

|                  |                                                              | $V_{CM}$ min $\leq V_{CM} \leq V_{CM}$ max                                                                |            | 85     |       | dB                |

| C <sub>IN</sub>  | Single-ended input capacitance                               | INN = GND1, f <sub>IN</sub> = 27,5kHz                                                                     |            | 25     |       | pF                |

| C <sub>IND</sub> | Differential input capacitance                               | f <sub>IN</sub> = 275kHz                                                                                  |            | 20     |       | pF                |

| R <sub>IN</sub>  | Single-ended input resistance                                | INN = GND1                                                                                                |            | 33     |       | kΩ                |

| R <sub>IND</sub> | Differential input resistance                                | K                                                                                                         |            | 39     |       | kΩ                |

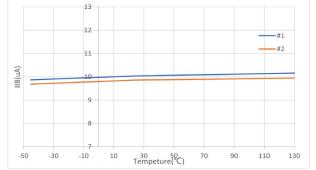

| I <sub>IB</sub>  | Input bias current                                           | INP = INN =GND1,<br>$I_{IB} = (I_{IBP} + I_{IBN}) / 2$                                                    | -13        | -10    | -7    | uA                |

| I <sub>IO</sub>  | Input offset current                                         |                                                                                                           |            | ±5     |       | nA                |

| ANALOG (         |                                                              |                                                                                                           | <b>.</b>   | T      | T     | 1                 |

|                  | Normal gain                                                  |                                                                                                           |            | 8.2    |       | V/V               |

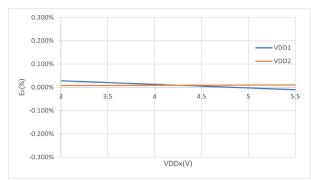

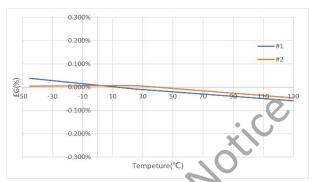

| E <sub>G</sub>   | Gain error <sup>(1)</sup>                                    | Initial, at T <sub>A</sub> = 25°C                                                                         | -0.3%      | ±0.05% | 0.3%  |                   |

| TCE <sub>G</sub> | Gain er or drift (1)                                         |                                                                                                           | -30        | ±5     | 30    | ppm/°C            |

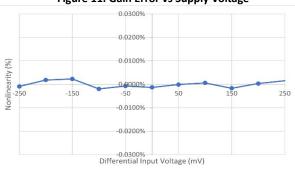

|                  | Nonlinearity (1)                                             |                                                                                                           | -0.03%     | ±0.01% | 0.03% |                   |

|                  | No linearity drift                                           |                                                                                                           |            | ±1     |       | ppm/°C            |

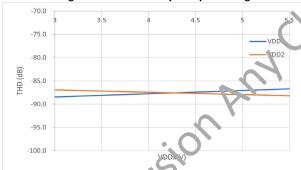

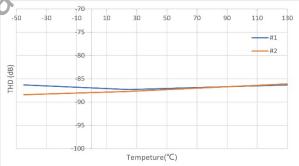

| THD              | lotal harmonic distortion                                    | $V_{IN} = 0.5V,$<br>$f_{IN} = 10kHz, BW = 100kHz$                                                         |            | -88    |       | dB                |

| V                | Output noise                                                 | $V_{INP} = V_{INN} = GND1,$<br>BW = 100kHz                                                                |            | 280    |       | uV <sub>RMS</sub> |

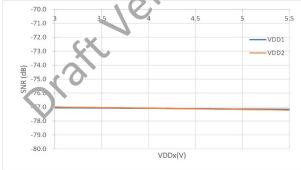

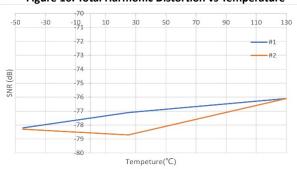

| SNR              | Signal-to-noise ratio                                        | $V_{IN} = 0.5V,$<br>$f_{IN} = 1kHz, BW = 10kHz$                                                           |            | 86     |       | dB                |

| SINU             | Signal-to-noise ratio                                        | V <sub>IN</sub> = 0.5V,<br>f <sub>IN</sub> = 10kHz, BW = 100kHz                                           |            | 77     |       | dB                |

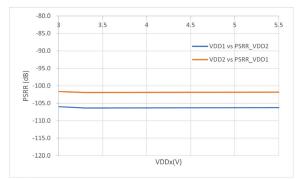

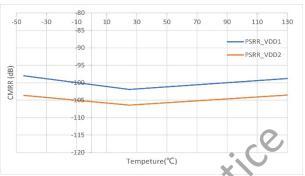

|                  | Power-supply rejection                                       | PSRR vs VDD1, at DC                                                                                       |            | -100   |       |                   |

| PSRR             | ratio (2)                                                    | PSRR vs VDD1,<br>100mV and 10kHz ripple                                                                   |            | -100   |       | dB                |

| Parameter             |                                                     | Test condition                          | MIN  | TYP  | UNIT |          |

|-----------------------|-----------------------------------------------------|-----------------------------------------|------|------|------|----------|

| ANALOG IN             | IPUT                                                |                                         |      | •    | •    |          |

|                       |                                                     | PSRR vs VDD2, at DC                     |      | -110 |      |          |

|                       |                                                     | PSRR vs VDD2,<br>100mV and 10kHz ripple |      | -100 |      |          |

| $V_{CMout}$           | Common-mode output voltage                          |                                         | 1.40 | 1.44 | 1.49 | ٧        |

| V <sub>FAILSAFE</sub> | Failsafe differential output voltage                |                                         |      | -2.6 | -2.5 | <b>%</b> |

| BW                    | Output bandwidth                                    |                                         | 250  | 310  | X    | kHz      |

| R <sub>OUT</sub>      | Output resistance                                   | On OUTP or OUTN                         |      | 0.2  | 0    | Ω        |

|                       | Output short-circuit current                        |                                         |      | ±13  |      | mA       |

| CMTI                  | Common-mode transient immunity                      | GND1 – GND2  = 1kV                      | 100  | 150  |      | kV/us    |

| POWER SU              | PPLY                                                |                                         |      |      |      |          |

| VDD1 <sub>UVLO</sub>  | VDD1 undervoltage detection threshold voltage       | VDD1 Rising                             | 2,3  | 2.5  | 2.7  | V        |

|                       | VDD1 undervoltage hysteresis                        | Hysteresis                              |      | 0.15 |      | V        |

| VDD2 <sub>UVLO</sub>  | VDD2 undervoltage<br>detection threshold<br>voltage | VDD2 Rising                             | 2.2  | 2.4  | 2.6  | V        |

| - ' <del>-</del>      | VDD2 undervoltage hysteresis                        | Hyste esis                              |      | 0.35 |      | V        |

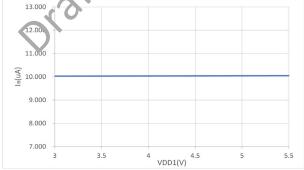

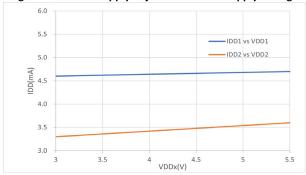

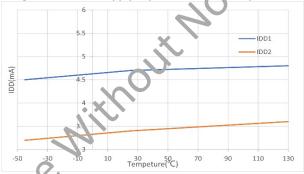

| IDD1                  | High-side supply current                            | 3.0V ≤ VDD1 ≤ 5.5V                      |      | 4    | 6    | mA       |

| IDD2                  | Low-side supply current                             | 3.cV ≤ VDD2 ≤ 5.5V                      |      | 3    | 5    | mA       |

<sup>(1)</sup> The typical value includes one sigma statistical variation.

<sup>(2)</sup> This parameter is output referred.

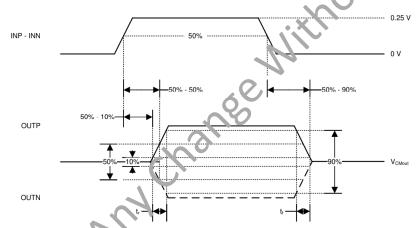

# 3.2 Switching Characteristics

over operating ambient temperature range (unless otherwise noted)

| PARAMETER       |                                                 | TEST CONDITION                                                          | MIN | TYP | MAX        | UNIT |

|-----------------|-------------------------------------------------|-------------------------------------------------------------------------|-----|-----|------------|------|

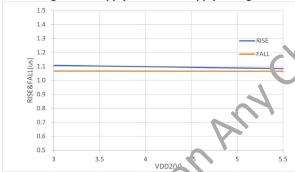

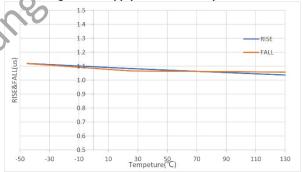

| tr              | Rise time of OUTP, OUTN                         | See Fig2                                                                |     | 1.0 |            | us   |

| t <sub>f</sub>  | Fall time of OUTP, OUTN                         | See Fig2                                                                |     | 1.0 |            | us   |

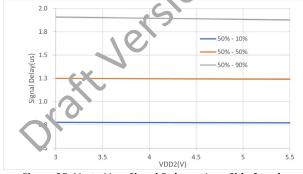

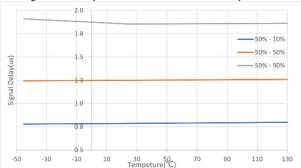

|                 | INP, INN to OUTP, OUTN signal delay (50% – 50%) | unfiltered output, see Fig2                                             |     | 1.2 | 1.5        | us   |

|                 | INP, INN to OUTP, OUTN signal delay (50% – 10%) | unfiltered output, see Fig2                                             |     | 0.7 | 1 (        | us   |

|                 | INP, INN to OUTP, OUTN signal delay (50% – 90%) | unfiltered output, see Fig2                                             |     | 1.7 | <b>O</b> 2 | us   |

| t <sub>AS</sub> | Analog settling time                            | VDD1 step to 3.0 V with VDD2 ≥ 3.0V, to OUTP, OUTN valid, 0.1% settling |     | 350 |            | us   |

Figure 2. Rise, Fall, and Delay Time Waveforms

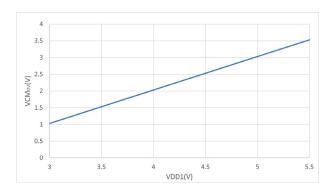

## 3.3 Typical Characteristics

at VDD1 = 5 V, VDD2 = 3.3 V,  $V_{INP}$  = -250 mV to 250 mV,  $V_{INN}$  = 0 V, and  $f_{IN}$  = 10 kHz (unless otherwise noted)

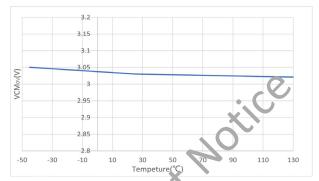

Figure 3. Common-Mode Overvoltage Detection Level vs High-Side Supply Voltage

Figure 4. Common-Mode Over roltage Detection Level vs

Temperature

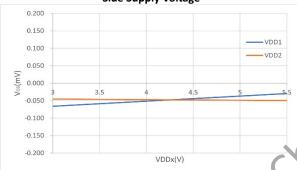

Figure 5. Input Offset Voltage vs Supply Voltage

Figure 6. Input Offset Voltage vs Temperature

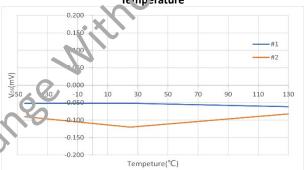

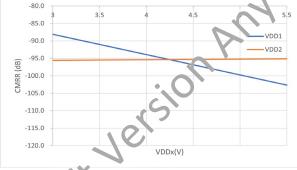

Figure 7. Common-Mode Rejection Ratio vs Supply Voltage

Figure 8. Common-Mode Rejection Ratio vs Temperature

Figure 9. Input Bias Current vs High-Side Supply Voltage

Figure 10. Input Bias Current vs Temperature

at VDD1 = 5 V, VDD2 = 3.3 V,  $V_{INP}$  = -250 mV to 250 mV,  $V_{INN}$  = 0 V, and  $f_{IN}$  = 10 kHz (unless otherwise noted)

Figure 11. Gain Error vs Supply Voltage

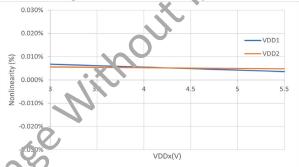

Figure 13. Nonlinearity vs Input Voltage

Figure 15. Total Harmonic Discortion vs Supply Voltage

Figure 17. Signal-to-Noise Ratio (10kHz) vs Supply Voltage

Figure 12. Gain Error vs 1 mperature

Figure 14. Nonlinearity vs Supply Voltage

Figure 16. Total Harmonic Distortion vs Temperature

Figure 18. Signal-to-Noise Ratio (10kHz) vs Temperature

Figure 19. Power-Supply Rejection Ratio vs Supply Voltage

Figure 21. Supply Current vs Supply Voltage

Figure 23. Output Rise and Fall Time vs Low-Side Supply

Figure 25.  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  Signal Delay vs Low-Side Supply Voltage

Figure 20. Power-Supply Rejection Ratio as iconperature

Figure 22. Supply Current vs Temperature

Figure 24. Output Rise and Fall Time vs Temperature

Figure 26.  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  Signal Delay vs Temperature

## 4 Detailed Description

#### 4.1 Overview

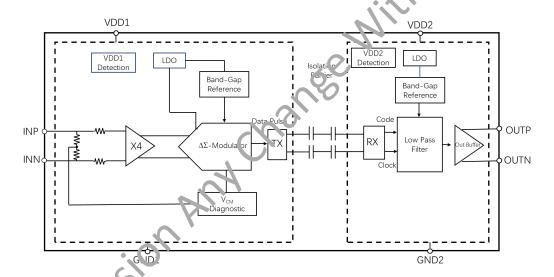

The Pai8300E is a fully-differential, precision, isolated amplifier. The input stage of the device consists of a fully differential amplifier that drives a second-order, delta-sigma ( $\Delta\Sigma$ ) modulator. The modulator generates data pulse. The drivers (called TX in the Functional Block Diagram) transfer the data pulse of the modulator across the isolation barrier. The received data pulse is synchronized and processed, as shown in the Functional Block Diagram by a low pass filter and out buffer on the low-side and presented as a differential output of the device.

Pai8300E adopts single channel transfer architecture and saves one clock channel, compared with current other amplifiers products, Pai8300E has the lowest power consumption. Pai8300E also uses In all and voltage divider technology (iDivider® technology) which is a new generation digital isolator technology invented by 2PaiSEMI to support a high level of magnetic field immunity.

#### 4.2 Function block diagram

## 4.3 Feature Description

## 4.3.1 Analog Input

The differential amplifier input stage of the Pai8300E feeds a second-order, switched-capacitor, feed-forward  $\Delta\Sigma$  modulato. The gain of the differential amplifier is set by internal precision resistors to a factor of 4 with a differential input impedance of 39k $\Omega$ . The modulator converts the analog signal into data pulse that is transferred across the isolation barrier, as described in patented iDivider® technology.

There are two restrictions on the analog input signals (VINP and VINN). First, if the input voltage exceeds the range GND1-6V to VDD1+0.5V, the input current must be limited to 10mA because the device input electrostatic discharge (ESD) diodes turn on. In addition, the linearity and noise performance of the device are ensured only when the analog input voltage remains within the specified linear full-scale range (FSR) and within the specified common-mode input voltage range.

#### 4.3.2 Isolation Channel Signal Transmission

The Pai8300E uses the patented iDivider® technology to transmit the modulator output data pulse across the  $SiO_2$  -based isolation barrier. The Pai8300E also uses special circuit techniques to maximize the CMTI performance and minimize the radiated emissions caused by the high-frequency carrier and IO buffer switching.

#### 4.3.3 Failsafe Output

The Pai8300E offers a fail-safe output that simplifies diagnostics on a system level. The fail-safe output is active in two cases:

- When the high-side supply VDD1 of the Pai8300E is missing.

- When the common-mode input voltage, that is  $V_{CM} = (V_{INP} + V_{INN})/2$ , exceeds the minimum common-mode overvoltage detection level  $V_{CMOV}$  of VDD1–2V.

Figure 27 and Figure 28 show the fail-safe output of the Pai8300E as a negative differential output voltage value that does not occur under normal device operation. Use the V<sub>FAILSAFE</sub> voltage specified in the Electrical Characteristics table as a reference value for the fail-safe detection on a system level.

Figure 27. Typical Negative Clipping Output of Pai8300E

Figure 28. Typical Fail-Safe Output of Pai8300E

#### 4.4 Device Functional Modes

The Pai8300E is operational when the power supplies VDD1 and VDD2 are applied, as specified in the Recommended Operating Conditions table in the Specifications section.

## **5 Application and Implementation**

## **5.1 Application Information**

The low input voltage range, very low nonlinearity, and temperature drift make the Pai8300E a high-performance solution for industrial applications where shunt-based current sensing with high common-mode voltage levels is required.

### 5.2 Typical Application

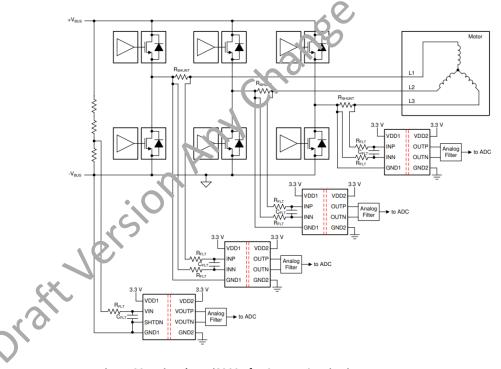

Isolated amplifiers are widely used in frequency inverters, which are critical parts of industrial motor drives, photovoltaic inverters, uninterruptible power supplies, and other industrial applications. The input structure of the Pai8300E is optimized for use with low-value shunt resistors in current sensing applications.

Figure 29 depicts a typical operation of the Pai8300E for current sensing in a frequency inverter application. Phase current measurement is accomplished through the shunt resistors, R<sub>SHUNT</sub> (in this case, a two-pin shunt). The differential input and the high common-mode transient immunity of the Paic300E ensure reliable and accurate operation even in high-noise environments (such as the power stage of the motor drive). The high impedance input and wide input voltage range make the Pai8300E suitable for DC bus voltage sensing.

Figure 29. Using the Pai8300E for Current Sensing in Frequency Inverters

### **5.2.1** Design Requirements

Table 1 lists the parameters for this typical application.

#### **Table1 Design Requirement**

| PARAMETER                                           | VALUE             |

|-----------------------------------------------------|-------------------|

| High-side supply voltage                            | 3.3V or 5V        |

| Low-side supply voltage                             | 3.3V or 5V        |

| Voltage drop across the shunt for a linear response | ± 250mV (maximum) |

| Signal delay (50% VIN to 90% OUTP, OUTN)            | 2μs (maximum)     |

#### 5.2.2 Detailed Design Procedure

The high-side power supply (VDD1) for the Pai8300E is derived from the power supply of the upper gate driver. Further details are provided in the Power Supply Recommendations section.

The floating ground reference (GND1) is derived from one of the ends of the shunt resultor that is connected to the negative input of the Pai8300E (INN). If a four-pin shunt is used, the inputs of the Pai8300E device are connected to the inner leads and GND1 is connected to one of the outer shunt leads.

Use Ohm's Law to calculate the voltage drop across the shunt resistor ( $V_{CH,VNT}$ ) for the desired measured current:  $V_{SHUNT} = I \times R_{SHUNT}$ .

Consider the following two restrictions to choose the proper value or the shunt resistor R<sub>SHUNT</sub>:

- The voltage drop caused by the nominal current range must not exceed the recommended differential input voltage range: V<sub>SHUNT</sub> ≤±250mV

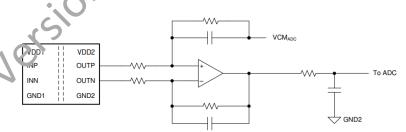

- The voltage drop caused by the maximum alloved overcurrent must not exceed the input voltage that causes a clipping output:  $V_{SHUNT} \leq V_{Clipping}$ . For system using single-ended input ADC, Figure 30 shows an example of an amplifier-based signal conversion and fillow chicult as used for recommended example. Tailor the bandwidth of this filter stage to the bandwidth requirement of the system and use NPO-type capacitors for best performance.

Figure 30. Connecting the Pai8300E Output to a Single-Ended Input ADC

#### 5.2.3 Application Curves

In frequency inverter applications, the power switches must be protected in case of an overcurrent condition. To allow for fast powering-off of the system, a low delay caused by the isolated amplifier is required. Figure 31 shows the typical full-scale step response of the Pai8300E. Consider the delay of the required window comparator and the micro control unit (MCU) to calculate the overall response time of the system.

Figure 31. Step Response of the Pai8300

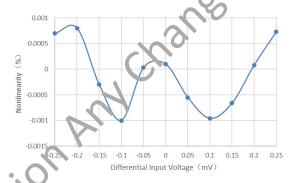

The high linearity and low temperature drift of offset and gain errors of the Pai8300E, as shown in Figure 32, allow design of motor drives with low torque ripple.

Figure 32. Typical Nonlinearity of the Pai8300E

## 5.3 What to Do and What Not to Do

Do not leave the inputs of the Pai8300E unconnected (floating) when the device is powered up. If both device inputs are left floating, the input bias current drives these inputs to the output common mode of the analog frontend approximately 2V. If the high-side supply voltage VDD1 is below 4 V, the internal common-mode overvoltage detector turns on and makes output -2.5V as described in the Fail-Safe Output section, which may lead to an undesired reaction on the system level.

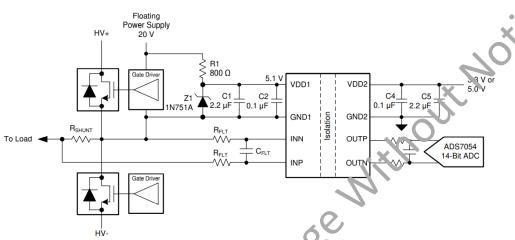

## **5.4 Power Supply Recommendations**

In a typical frequency inverter application, the high-side power supply (VDD1) for the device is directly derived from the floating power supply of the upper gate driver. For lowest system-level cost, a Zener diode can be used to limit the voltage to 5V or  $3.3V \pm 10\%$ . Alternatively, a low-cost low-dropout (LDO) regulator may be used to minimize noise

on the power supply. A low-ESR decoupling capacitor of 0.1  $\mu$ F to filter this power-supply path is recommended. Place this capacitor (C2 in Figure 33) as close as possible to the VDD1 pin of the Pai8300E for best performance. If better filtering is required, an additional 2.2  $\mu$ F capacitor may be used. The floating ground reference (GND1) is derived from the end of the shunt resistor, which is connected to the negative input (INN) of the device. If a four-pin shunt is used, the device inputs are connected to the inner leads, and GND1 is connected to one of the outer leads of the shunt. To decouple the low-side power supply on the controller side, use a 0.1  $\mu$ F capacitor placed as close to the VDD2 pin of the Pai8300E as possible, followed by an additional capacitor from 1  $\mu$ F to 10  $\mu$ F.

Figure 33. Zener-Diode-Based, ∷'gr. sir e Power Supply

### 5.5 Layout

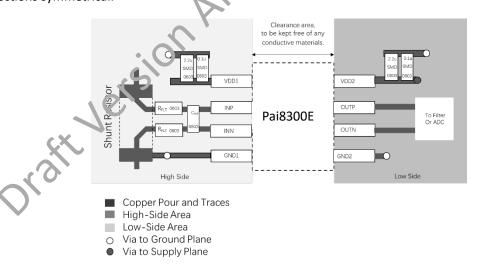

Figure 34 shows a layout recommendation with the critical placement of the decoupling capacitors (as close as possible to the Pai8300E supply pins) and placement of the other components required by the device. For best performance, place the shunt resistor close to the INP and INN inputs of the Pai8300E and keep the layout of both connections symmetrical.

Figure 34. Recommended Layout of the Pai8300

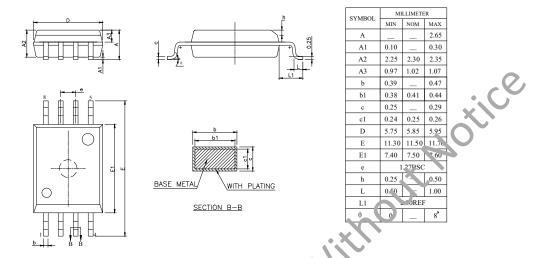

## **6 Outline Dimensions**

Figure 35. Outline Package

## 7 Land Patterns

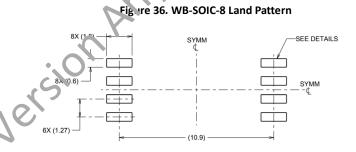

The Fig36 illustrates the recommended land pattern details for the Pai8300E in a wide-body SOIC-8 package.

Note: All feature sizes shown are at maximum material condition and a card fabrication tolerance of 0.05 mm is assumed.

# 8 Top Marking

Figure 37. Top Marking

| Line 1 | XXXXXXXX=Product name                     |

|--------|-------------------------------------------|

|        | YY = Work Year                            |

| Line 2 | WW = Work Week                            |

|        | ZZ=Manufacturing code from assembly house |

| Line 3 | XXXXX, no special meaning                 |

## **9 Reel Information**

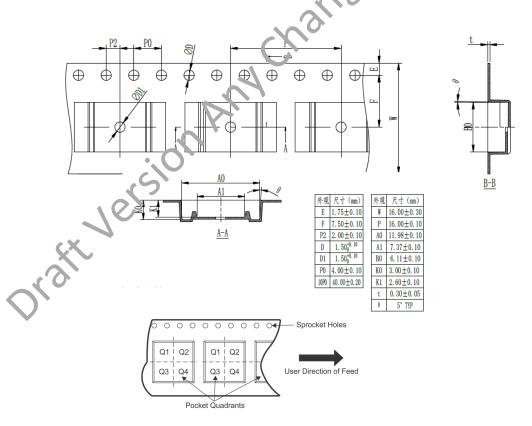

Figure 38. Reel Information

Note: The Pin 1of the chip is in the quadrant Q1

## 10 Ordering Guide

| Model   | Name <sup>1</sup> | Temperature Range | Withstand Voltage<br>Rating (kVRMS) | Package   | MSL Peak Temp 1     | Quantity<br>per Reel |

|---------|-------------------|-------------------|-------------------------------------|-----------|---------------------|----------------------|

| Pai8300 | 0E-W5R            | -40~125°C         | 5.0                                 | WB SOIC-8 | Level-3-260C-168 HR | 1000                 |

<sup>(1)</sup> The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

## 11 Important Notice and Disclaimer

2Pai semi intends to provide customers with the latest, accurate, and in-depth documentation. However, no responsibility is assumed by 2Pai semi for its use, nor for any infringements of patents of other rights of third parties that may result from its use. Characterization data, available modules, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only.2Pai semi reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information.2Pai semi shall have no liability for the consequences of use of the information supplied herein.

Trademarks and registered trademarks are the property of their respective owners. This document does not imply, or express copyright licenses granted hereunder to design of fairnate any integrated circuits.

Room 401/402/404A, 4th Floor, Building B, No. 112 Liangxiu Road, Pudong New Area, Shanghai, China 021-50850681

2Pai Semiconductor Co., Limited. All rights reserved.

http://www.rpsemi.com/

## **12 Revision History**

| Ver | Date       | Page | Change Record                                                                                                                                       |

|-----|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1 | 2022-06-09 | All  | Initial version.                                                                                                                                    |

| 0.2 | 2022-08-20 | All  | Add figures.                                                                                                                                        |

| 0.3 | 2022-09-19 | All  | Increase application items, package information.                                                                                                    |

| 0.4 | 2022-12-05 | All  | Update some format and modify figure sequence.                                                                                                      |

| 0.5 | 2023-07-11 | All  | Update Certifications, Input offset drift, gain error drift, CMRR, RIN, CIN, and sor is descriptions.                                               |

|     |            | ersi | Update some format and modify figure sequence.  Update Certifications, Input offset drift, gain error drift, CMRR, RIN, CIN, and some descriptions. |