4 to 40V Low-Cost High Side Gate Driver with OVP

## **GENERAL DESCRIPTION**

MX5014D22 Gate driver is designed for gate control of Nchannel, enhancement mode, power MOSFETs used as high side switches. The MX5014D22 can sustain an on-state output indefinitely. The MX5014D22 operates from 4V to 40V supply. An internal circuit will off the external FET to protect overvoltage. In high side configurations, the driver can control MOSFETs that switch loads of up to 40V.

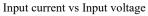

The MX5014D22 has a TTL compatible control input. The MX5014D22 features an internal charge pump that can sustain a gate voltage greater than the available supply voltage. The driver can turn on a logic level MOSFET from 3V supply or a standard MOSFET from a 5V supply. The gate to source output voltage is internally limited to approximately 12V. The MX5014D22 is available in plastic 6 pin DFN2\*2 package.

## **FEATURES**

- ♦ 4V to 40V operation supply voltage

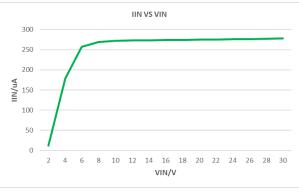

- ♦ 240uA typical supply current (24V supply)

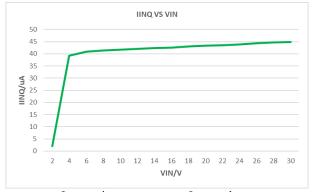

- ♦ 38uA typical off-state current (24V supply)

- Internal charge pump

- ♦ TTL compatible input

- ♦ Withstands 60V transient (load dump)

- ♦ Internal 12Vgate clamp protection

- ♦ Minimum external parts

- Operates in high side or low side configurations

- ♦ 1uA control EN input pull off

- Noninverting configuration

- ♦ Adjustable overvoltage protection

## **APPLICATIONS**

| Battery Management System |

|---------------------------|

| Lamp Control              |

| Heater Control            |

| Power Bus Switching       |

| Motor control             |

# **GENERAL INFORMATION**

### **Ordering information**

| Part Number                | Description |  |  |  |  |  |  |

|----------------------------|-------------|--|--|--|--|--|--|

| MX5014D22                  | DFN2*2-6L   |  |  |  |  |  |  |

| Package dissipation rating |             |  |  |  |  |  |  |

| Package                    | R0JA (°C/W) |  |  |  |  |  |  |

| DFN2*2-6L                  | 60          |  |  |  |  |  |  |

### Absolute maximum ratings

| Parameter                       | Value        |

|---------------------------------|--------------|

| Supply voltage                  | -0.7 to 60V  |

| EN, Source voltage              | -0.7 to VIN  |

| OVP voltage                     | -0.7 to 6.5V |

| Source current                  | 10mA         |

| Gate voltage                    | -0.7 to 55V  |

| Junction temperature            | 150°C        |

| Storage temperature, Tstg       | -55 to 150°C |

| Leading temperature (soldering, | 2(0%)        |

| 10secs)                         | 260°℃        |

| ESD Susceptibility HBM          | $\pm 2000 V$ |

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

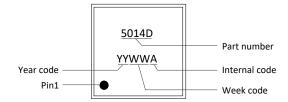

### **Marking information**

### **Recommended operating condition**

| Symbol      | Parameter         | Range     |

|-------------|-------------------|-----------|

| Supply      | Supply voltage    | 4-40V     |

| OVP         |                   | 0-5.5V    |

| Junction    |                   | -40~125°C |

| temperature |                   |           |

| PD          | Power dissipation | 0.6W      |

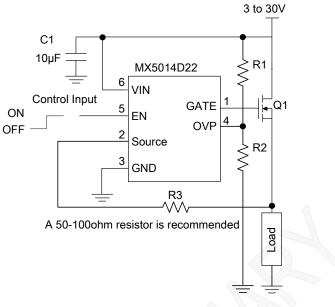

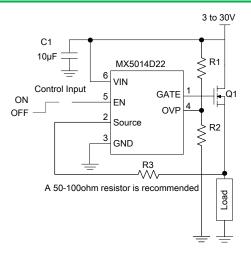

# **TYPICAL APPLICATION**

Typical application with high side NMOSFET driver

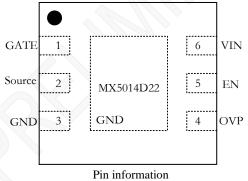

| PIN NO.    | PIN name | Description                                                                                       |

|------------|----------|---------------------------------------------------------------------------------------------------|

| 1          | GATE     | Drives and clamps the gate of the power MOSFET                                                    |

| 2          | Source   | Connects to source lead of power MOSFET and is the return for the gate clamp Zener. This pin must |

| 2          | Source   | connect at least a 50 $\Omega$ resistor between MOSFET when used as high side driver.             |

| 2          | GND      | Ground                                                                                            |

| 3          | GND      | All signals are referenced to this ground.                                                        |

| 4          | OVP      | External over voltage protection. This pin cannot be floating.                                    |

| 5          | EN       | Turns on power MOSFET when EN is up above threshold (1.5V typical). This pin requires ~ 1uA to    |

| 3          | LIN      | switch. The pin can be floating if not used.                                                      |

| 6          | VIN      | Supply. Must be decoupled to isolate from large transients caused by the power MOSFET drain.      |

| 6          | V IIN    | 10uF is recommended close to this pin to GND.                                                     |

| Thermal PA | D        | Ground                                                                                            |

## **BLOCK DIAGRAM**

## **Electrical characteristics**

( $T_A = 25^{\circ}C$ , VIN = 12V, EN floating, OVP = 0V, unless otherwise noted)

| Symbol                    | Parameter                                         | Test condition                                      | Min  | Тур. | Max  | Unit |

|---------------------------|---------------------------------------------------|-----------------------------------------------------|------|------|------|------|

|                           |                                                   | EN = Low                                            | 35   | 40   | 55   | μA   |

|                           | VIN = 40V                                         | EN floating                                         | 260  | 240  | 300  | μA   |

| Supply current            |                                                   | EN = Low                                            | 15   | 20   | 30   | μA   |

|                           | VIN = 4V                                          | EN floating                                         | 90   | 105  | 150  | μA   |

|                           | $3V \leq VIN \leq 6V$                             | EN threshold, falling                               |      |      | 1.05 | V    |

| EN141 1 11                | $3V \leq V \leq 0V$                               | EN threshold, rising                                | 1.10 |      |      | V    |

| EN threshold              |                                                   | EN threshold, falling                               |      |      | 1.10 | V    |

|                           | $6V \le VIN \le 30V$                              | EN threshold, rising                                | 2.10 |      |      | V    |

|                           |                                                   | EN = Low                                            | -2.0 |      | 0    | μA   |

| EN current                | $3.0V \le VIN \le 30V$                            | EN floating                                         | -2.0 | 1.0  | 2.0  | μA   |

| EN capacitance            |                                                   |                                                     |      | 5.0  |      | pF   |

| OVD thus the 14           | 2.0M - MDI - 20M                                  | OVP threshold                                       | 1.16 | 1.22 | 1.30 | V    |

| OVP threshold             | $3.0V \le VIN \le 30V$                            | OVP recovery                                        | 1.00 | 1.18 | 1.22 | V    |

| Gate enhancement          | VIN =4V                                           | EN floating                                         | 4.5  | 6.5  | 8.0  | V    |

| VGATE-VSOURCE             | $8.0V \leq VIN \leq 30V$                          | EN floating                                         | 10   | 12   | 15   | V    |

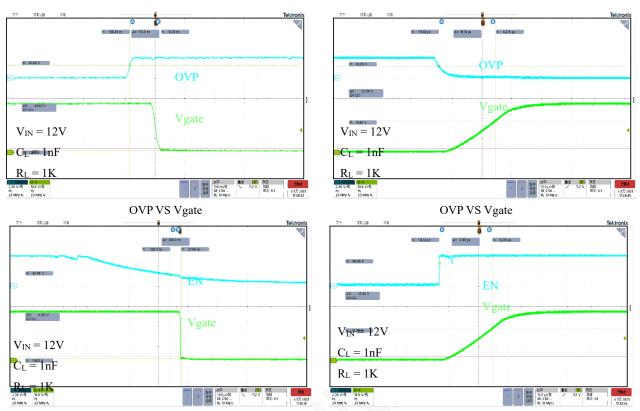

| Gate turn on time for     | VIN=4.5V, C <sub>L</sub> =1nF, R <sub>L</sub> =1K | OVP = Low, measure time to Vgate<br>= $V_{IN} + 4V$ |      | 13   | 20   | us   |

| OVP                       | VIN=12V, C <sub>L</sub> =1nF, R <sub>L</sub> =1K  | OVP = Low, measure time to Vgate<br>= $V_{IN} + 4V$ |      | 19   | 30   | us   |

| Gate turn off time for    | VIN=4.5V, CL=1nF, RL=1K                           | OVP = High, measure time to Vgate                   |      | 95   | 120  | ns   |

| OVP                       | VIN=12V, CL=1nF, RL=1K                            | = 1V                                                |      | 110  | 150  | ns   |

| Cata tum on time for EN   | VIN=4.5V, CL=1nF, RL=1K                           | EN = High, measure time to Vgate =                  |      | 15   | 30   | us   |

| Gate turn on time for EN  | VIN=12V, C <sub>L</sub> =1nF, R <sub>L</sub> =1K  | $V_{IN} + 4V$                                       |      | 18   | 30   | us   |

| Gate turn off time for EN | VIN=4.5V, CL=1nF, RL=1K                           | EN = Low, measure time to Vgate =                   |      | 30   | 60   | ns   |

| Gate turn on time for EN  | VIN=12V, CL=1nF, RL=1K                            | 1V                                                  |      | 360  | 450  | ns   |

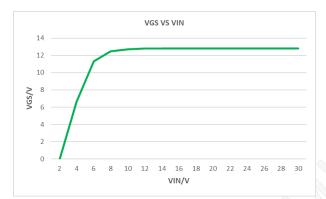

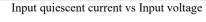

## **Characteristic plots**

### Vgate - Vsource vs Input voltage

WUXI MAXIN MICRO V11

### MX5014D22

### 4 to 40V Low-Cost High Side Gate Driver with OVP

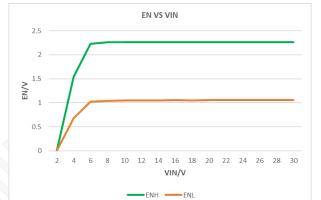

EN VS Vgate

EN VS Vgate

# 4 to 40V Low-Cost High Side Gate Driver with OVP

MX5014D22

## **Operation description**

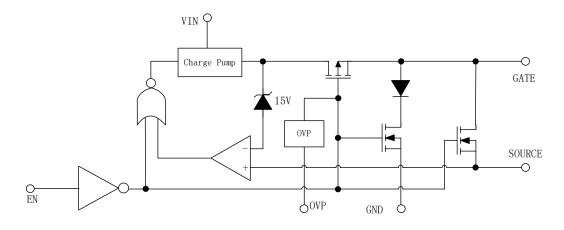

The internal functions of these devices are controlled via a logic block connected to the EN pin. When the EN is off, all functions are turned off, and the gate of the external power MOSFET is held low via two N-channel switches. This results in a very low standby current, 45uA typical, which is necessary to power an internal bandgap. When the EN is driven to the "ON" state, the N-channel switches are turned off, the charge pump is turned on, and the P-channel switch between the charge pump and the gate turns on, allowing the gate of the power MOSFET to be charged. The op amp and internal Zener from an active regulator which shuts off the charge pump when the gate voltage is high enough.

The charge pump incorporates a 100kHz oscillator and on chip pump capacitors capable of charging a 1000pF load in 90us typical. In addition to providing active regulation, the internal 12V Zener is included to prevent exceeding the GS rating of the power MOSFET at high supply voltages.

The over voltage protection can be set by an external resistor divider between VIN, OVP and GND. When the voltage of OVP pin exceed the internal reference voltage (1.22V typical), An internal circuit will off the external FET to protect overvoltage. This pin cannot be floating.

The MX5014D22 devices have been improved for greater ruggedness and durability.

#### **Construction Hints**

High current pulse circuits demand equipment and assembly techniques that are more stringent than normal, low current lab practices. The following are the sources of pitfalls most often encountered during prototyping: Supplies: Many bench power supplies have poor transient response. Circuits that are being pulse tested, or those that operate by pulse width modulation will produce strange results when used with a supply that has poor ripple rejection, or a peaked transient response. Always monitor the power supply voltage that appears at the drain of a high side driver (or the supply side of the load for a low side driver) with an oscilloscope. It is not uncommon to find bench power supplies in the 1kW class that overshoot or undershoot by as much as 50% when pulse loaded. Not only will the load current and voltage measurements be affected, but it is possible to overstress various components, especially electrolytic capacitors, with possible catastrophic results. A 10uF supply bypass capacitor at the chip is recommended. Residual resistances: resistances in circuit connections may also cause confusing results. For example, a circuit may employ a 50m  $\Omega$  power MOSFET for low voltage drop, but unless careful construction techniques are used, one could easily add 50 to 100m  $\Omega$  resistance. Do not use a socket for the MOSFET. If the MOSFET is a TO-220 type package, make high current connections to the drain tab. Wiring losses have profound effect on high current circuits. A floating million meter can identify connections that are contributing excess drop under load.

#### Low voltage testing

As the MX5014D22 has relatively high output impedances, a normal oscilloscope probe will load the device. This is especially pronounced at low voltage operation. It is recommended that a FET probe or unity gain buffer be used for all testing.

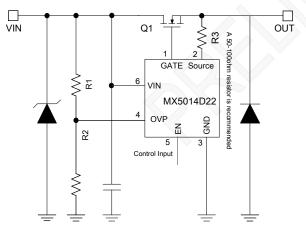

### **Circuit topologies**

The MX5014D22 is well suited for use with standard power MOSFETs in high side driver configurations. In addition, the lower supply voltage requirements of these devices make them ideal for use with logic level FETs in high side applications with a supply 3 to 5V. In addition, a standard IGBT can be driven using these devices.

Choice of one topology over another is usually based on speed vs. safety. The fastest topology is the low side driver; however, it is not usually considered as safe as high side driving as it is easier to accidentally short a load to ground than to VIN. The slowest, but safest topology is the high side driver; with speed being inversely proportional to supply voltage. It is the preferred topology for most military and automotive applications. Speed can be improved considerably by bootstrapping from the supply.

## MX5014D22 4 to 40V Low-Cost High Side Gate Driver with OVP

High side driver

### Application guidelines

The layout of MX5014D22 is critical to its performance and functionality. The MX5014D22 is available in a 2x2 DFN, which allows a low inductance connection to a FET.

Place a TVS as close as to the input end prevent parasitic inductance oscillation from damaging the circuit. And a Schottky is placed at the output end to release oscillation caused by the output lead inductance. A 50-100ohm resistor between the Source pin and output end to prevent damage from surge voltage, as the R3 shown in the figure below.

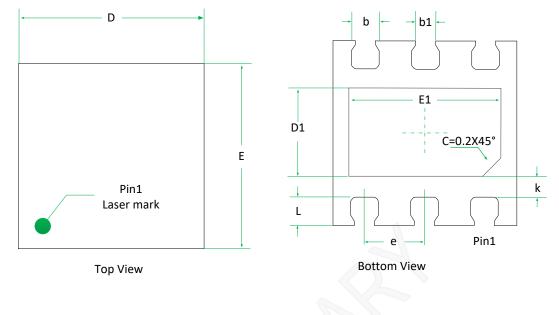

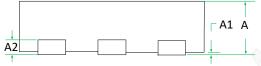

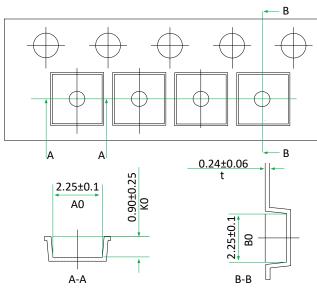

# Package information

Side View

| SVMDOI |       | MILLIMETER | S     |       | INCHES   |       |

|--------|-------|------------|-------|-------|----------|-------|

| SYMBOL | MIN   | NOM        | MAX   | MIN   | NOM      | МАХ   |

| А      | 0.50  | 0.55       | 0.60  | 0.02  | 0.022    | 0.024 |

| A1     | 0     | 0.025      | 0.050 | 0     | 0.001    | 0.002 |

| A2     |       | 0.152BSC   |       |       | 0.006BSC |       |

| D      | 1.900 | 2.000      | 2.100 | 0.075 | 0.078    | 0.083 |

| Е      | 1.900 | 2.000      | 2.100 | 0.075 | 0.078    | 0.083 |

| D1     | 0.860 | 0.960      | 1.060 | 0.034 | 0.038    | 0.042 |

| E1     | 1.550 | 1.650      | 1.750 | 0.061 | 0.065    | 0.069 |

| k      |       | 0.220BSC   |       |       | 0.008BSC |       |

| b      | 0.250 | 0.300      | 0.350 | 0.010 | 0.012    | 0.014 |

| b1     |       | 0.220BSC   |       |       | 0.008BSC |       |

| e      |       | 0.650BSC   |       |       | 0.026BSC |       |

| L      | 0.224 | 0.300      | 0.376 | 0.009 | 0.012    | 0.015 |

DFN2\*2-6L for MX5014D22

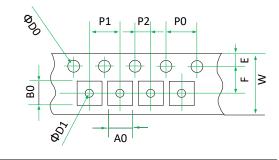

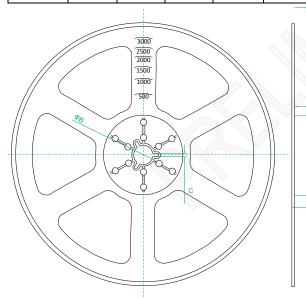

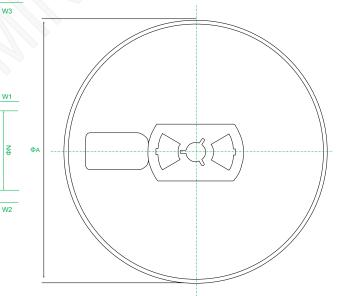

# Tape and Reel Information

| Symbol | W    | Е    | F    | ΦD0  | ФD1  | P0   | P1   | P2   | A0   | B0   | K0   | t    |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|

| MAX    | 8.10 | 1.85 | 3.55 | 1.60 | 1.10 | 4.10 | 4.10 | 2.05 | 2.38 | 2.38 | 1.15 | 0.28 |

| MIN    | 7.90 | 1.65 | 3.45 | 1.40 | 0.90 | 3.90 | 3.90 | 1.95 | 2.15 | 2.15 | 0.65 | 0.18 |

| Symbol | ФА  | ΦN | ΦB   | С    | W1  | W2 | W3  |

|--------|-----|----|------|------|-----|----|-----|

| MAX    | 180 | 56 | 13.5 | 2.50 | 9.9 | 12 | 1.8 |

| MIN    | 176 | 52 | 13.0 | 1.90 | 8.4 |    | 1.0 |

## **Restrictions on Product Use**

• MAXIN micro is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing MAXIN products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such MAXIN products could cause loss of human life, bodily injury, or damage to property.

• In developing your designs, please ensure that MAXIN products are used within specified operating ranges as set forth in the most recent MAXIN products specifications.

• The information contained herein is subject to change without notice.

V10 The original version (preliminary)

- V11 Added new waves and updated date.

- V12 Updated date and graphs.