Click here to ask an associate for production status of specific part numbers. Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

#### **General Description**

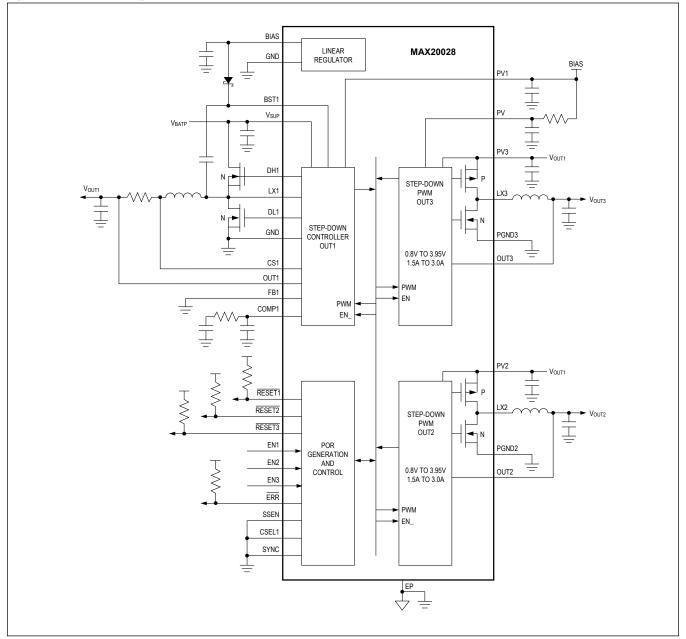

The MAX20028 power-management integrated circuit (PMIC) is a 2.1MHz, multichannel, DC-DC converter designed for automotive applications. The device integrates three supplies in a small footprint. The device includes one high-voltage step-down controller (OUT1) designed to run directly from a car battery, and two low-voltage step-down converters (OUT2/OUT3) cascaded from OUT1. Under no-load conditions, the MAX20028 consumes only 30µA of quiescent current, making it ideal for automotive applications.

The high-voltage synchronous step-down DC-DC controller (OUT1) operates from a voltage up to 36V continuous and is protected from load-dump transients up to 42V. There is a pin-selectable frequency option of either 2.1MHz or a factory-set frequency for 1.05MHz, 525kHz, 420kHz, or 350kHz. The low-voltage, synchronous stepdown DC-DC converters run directly from OUT1 and can supply output currents up to 3A.

The device provides a spread-spectrum enable input (SSEN) to provide quick improvement in electromagnetic interference when needed. There is also a SYNC I/O for providing either an input to synchronize to an external clock source or an output of the internally generated clock (see the <u>Selector Guide</u> for the different options available). The device includes overtemperature shutdown and overcurrent limiting. The device also includes individual RE-<u>SET</u> outputs and individual enable inputs. The individual RESET1 outputs provide voltage monitoring for all output channels.

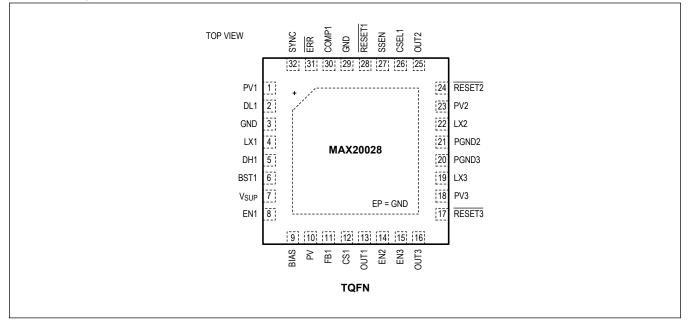

The MAX20028 is available in a 32-pin (5mm x 5mm x 0.75mm) side-wettable TQFN-EP package and is specified for operation over the -40°C to +125°C automotive temperature range.

### **Applications**

- Automotive

- Industrial

- ADAS

#### **Benefits and Features**

- High-Efficiency Voltage DC-DC Controller Saves

Power

- 3.5V to 36V Operating Supply Voltage

- Output Voltage: Pin Selectable, Fixed, or Resistor-Divider Adjustable

- 350kHz to 2.1MHz Operation

- 30µA Quiescent Current with DC-DC Controller Enabled

- Dual 2.1MHz DC-DC Converters with Integrated FETs Saves Space

- OUT2 and OUT3 Are Cascaded from OUT1, Improving Efficiency

- 3A Output Current

- 0.8V to 3.95V Output Voltage

- 25% Lower  $C_{OUT2}$  and  $C_{OUT3}$  Compared to the MAX16993

- · Fixed or Resistor-Divider-Adjustable Output Voltage

- 180° Out-of-Phase Operation

- High Accuracy to Meet ASIL Specification

- $\pm 1\%$  FB Accuracy,  $\pm 2\%$  Output-Voltage Accuracy, and  $\pm 0.5\%$  OV/UV Accuracy

- Excellent Load-Transient Performance

- Robust for the Automotive Environment

- Current-Mode Architecture with Forced-PWM and Skip Modes of Operations

- Frequency Synchronization Input/Output Reduces

System Noise

- Individual Enable Inputs and RESET1 Outputs

- Overtemperature and Short-Circuit Protection

- AEQ-100 Qualified

<u>Ordering Information</u> and <u>Selector Guide</u> appear at end of data sheet.

© 2023 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

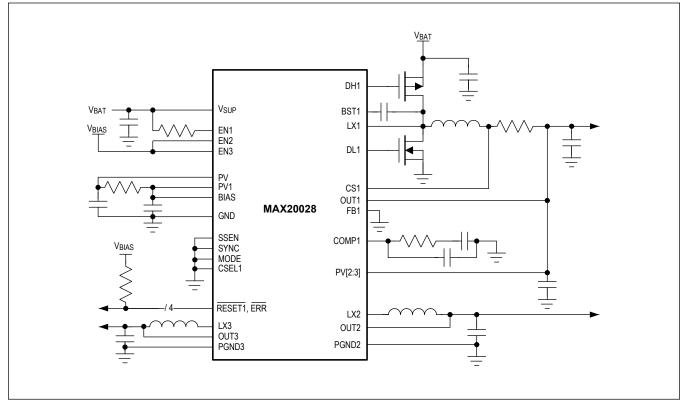

### **Simplified Schematic**

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

#### **Absolute Maximum Ratings**

| V <sub>SUP</sub> , EN1 to GND | -0.3V to +45V                   | FB1, EN2, EN3 to GND0.3V to +6.0V                                 |

|-------------------------------|---------------------------------|-------------------------------------------------------------------|

| PV to GND                     |                                 | RESET_, ERR to GND0.3V to +6.0V                                   |

| PV1 to GND                    | 0.3V to +6.0V                   | CS1 to OUT10.3V to +6.0V                                          |

| PV2 to GND, PV2 to PGND2      | 0.3V to +6.0V                   | CSEL1, SYNC, SSEN to GND0.3V to +6.0V                             |

| PV3 to GND, PV3 to PGND3      | 0.3V to +6.0V                   | COMP1 to GND0.3V to PV + 0.3V                                     |

| PGND2, PGND3 to GND           | 0.3V to +0.3V                   | LX2, LX3 Output Short-Circuit DurationContinuous                  |

| LX1 to GND                    | 6.0V to V <sub>SUP</sub> + 6.0V | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ , TQFN derate |

| BST1 to LX1                   | 0.3V to +6.0V                   | 34.5mW/°C above +70°C.)2758.6mW                                   |

| DH1 to LX1                    | 0.3V to PV1 + 0.3V              | Operating Temperature Range40°C to +125°C                         |

| LX2 to PGND2                  | 0.3V to PV2 + 0.3V              | Storage Temperature Range65°C to +150°C                           |

| LX3 to PGND3                  | 0.3V to PV3 + 0.3V              | Soldering Temperature (Reflow)+260°C                              |

| OUT1 - OUT3, CS1 to GND       | 0.3V to +6.0V                   | Lead Temperature (Soldering, 10s)+300°C                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 32 TQFN-EP

| Package Code                           | T3255Y+4C        |  |  |

|----------------------------------------|------------------|--|--|

| Outline Number                         | <u>21-100214</u> |  |  |

| Land Pattern Number                    | <u>90-100082</u> |  |  |

| THERMAL RESISTANCE                     |                  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 29°C/W           |  |  |

| Junction to Case $(\theta_{JC})$       | 1.7°C/W          |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

#### **Electrical Characteristics**

$(V_{SUP} = 14V, V_{PV} = V_{PV1} = V_{BIAS}, V_{PV2} = V_{PV3} = V_{OUT1}, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$  under normal conditions, unless otherwise noted. (Note 1))

| PARAMETER                     | SYMBOL            | CONDITIONS                                                                | MIN  | TYP | MAX  | UNITS |

|-------------------------------|-------------------|---------------------------------------------------------------------------|------|-----|------|-------|

| Supply Voltage Startup        | V <sub>SUP.</sub> | V <sub>SUP</sub> rising, MAX20028ATJ_                                     | 4.25 | 4.5 | 4.75 | v     |

| Threshold                     | STARTUP           | V <sub>SUP</sub> rising, MAX20028BATJ_                                    | 3.9  | 4.1 | 4.3  |       |

| Supply Voltage Range          | V <sub>SUP</sub>  | Normal operation, after Buck 1 startup                                    | 3.5  |     | 36   | V     |

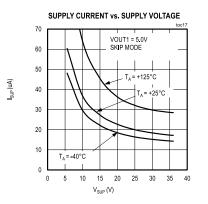

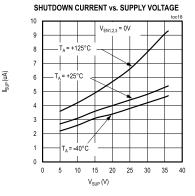

| Quantu Quanant                | I <sub>SUP</sub>  | $V_{EN1} = V_{EN2} = V_{EN3} = 0V$                                        |      | 4   | 15   |       |

| Supply Current                |                   | V <sub>EN1</sub> = 5V, V <sub>EN2</sub> = V <sub>EN3</sub> = 0V (no load) |      | 26  | 60   | μA    |

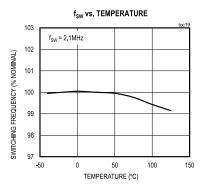

| Oscillator Frequency          | f <sub>SW</sub>   |                                                                           | 2.0  | 2.1 | 2.2  | MHz   |

| SYNC Input Frequency<br>Range |                   |                                                                           | 1.7  |     | 2.4  | MHz   |

| BIAS Regulator Voltage        | V <sub>BIAS</sub> | $6V \le V_{SUP} \le 42V$ , no switchover                                  | 4.5  | 5.0 | 5.5  | V     |

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

### **Electrical Characteristics (continued)**

$(V_{SUP} = 14V, V_{PV} = V_{PV1} = V_{BIAS}, V_{PV2} = V_{PV3} = V_{OUT1}, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$  under normal conditions, unless otherwise noted. (Note 1))

| PARAMETER                           | SYMBOL            | COND                                                              | ITIONS                                                     | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------|-------------------|-------------------------------------------------------------------|------------------------------------------------------------|-------|------|-------|-------|

|                                     |                   | V <sub>BIAS</sub> falling, MAX20                                  | 2.5                                                        | 2.7   | 2.9  |       |       |

| PV_Power-On Reset                   |                   | Hysteresis, MAX200                                                |                                                            | 0.45  |      | V     |       |

|                                     |                   | V <sub>BIAS</sub> falling, MAX20                                  | 0028BATJ_                                                  | 2.5   | 2.7  | 2.95  |       |

| PV_Power-On Reset                   |                   | Hysteresis, MAX200                                                | 28BATJ_                                                    |       | 0.55 |       | V     |

| OUT1: HIGH-VOLTAGE                  | SYNCHRONOU        | S STEP-DOWN DC-DO                                                 | CONTROLLER                                                 |       |      |       | 1     |

|                                     |                   |                                                                   | V <sub>CSEL1</sub> = V <sub>GND</sub>                      |       | 2100 |       |       |

|                                     |                   |                                                                   | V <sub>CSEL1</sub> = V <sub>BIAS</sub><br>(factory option) |       | 1050 |       | -     |

| OUT1 Switching<br>Frequency         | fsw1              | Internally generated (see the                                     | V <sub>CSEL1</sub> = V <sub>BIAS</sub><br>(factory option) |       | 525  |       | kHz   |

| requency                            |                   | Selector Guide)                                                   | VCSEL1 = VBIAS<br>(factory option)                         |       | 420  |       |       |

|                                     |                   |                                                                   | V <sub>CSEL1</sub> = V <sub>BIAS</sub><br>(factory option) |       | 350  |       |       |

|                                     | Maximi            | Fixed option (see                                                 | V <sub>FB1</sub> = V <sub>BIAS</sub><br>(factory option)   | 4.9   | 5.0  | 5.1   | - v   |

| Voltage                             | V <sub>OUT1</sub> | the Selector Guide)                                               | V <sub>FB1</sub> = V <sub>GND</sub><br>(factory option)    | 3.25  | 3.3  | 3.35  |       |

| FB1 Regulation Voltage              |                   | Adjustable option (se<br>Guide)                                   | ee the Selector                                            | 0.985 | 1    | 1.015 | v     |

| Error-Amplifier<br>Transconductance | <b>9</b> меа      |                                                                   |                                                            | 300   | 700  | 1200  | μS    |

| Voltage Accuracy                    | V <sub>OUT1</sub> | 5.5V ≤ V <sub>SUP</sub> ≤<br>18V, 0 < V <sub>LIM1</sub> <<br>75mV | PWM mode                                                   | -2.0  |      | +2.0  | %     |

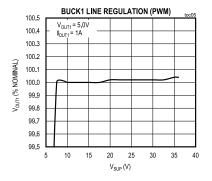

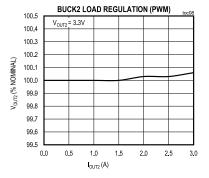

| DC Load Regulation                  |                   | PWM mode                                                          |                                                            |       | 0.02 |       | %/A   |

| DC Line Regulation                  |                   | PWM mode                                                          |                                                            |       | 0.03 |       | %/V   |

| OUT1 Discharge<br>Resistance        |                   | V <sub>EN1</sub> = V <sub>GND</sub> or V <sub>SI</sub>            | UP                                                         |       | 100  | 200   | Ω     |

| High-Side Output-Drive              |                   | V <sub>DH1</sub> rising, I <sub>DH1</sub> =                       | 100mA                                                      |       | 2    | 4     | 0     |

| Resistance                          |                   | V <sub>DH1</sub> falling, I <sub>DH1</sub> =                      | 100mA                                                      |       | 1    | 4     | Ω     |

| Low-Side Output- Drive              |                   | V <sub>DL1</sub> rising, I <sub>DL1</sub> = 1                     | 00mA                                                       |       | 2.5  | 5     | 0     |

| Resistance                          |                   | V <sub>DL1</sub> falling, I <sub>DL1</sub> = 7                    | 100mA                                                      |       | 1.5  | 3     | Ω     |

| Output Current-Limit<br>Threshold   | V <sub>LIM1</sub> | CS1 - OUT1                                                        |                                                            | 100   | 120  | 150   | mV    |

| Skip-Current Threshold              | I <sub>SKIP</sub> | CS1 - OUT1, no load                                               | t                                                          | 10    | 35   | 60    | mV    |

| Soft-Start Ramp Time                |                   |                                                                   |                                                            |       | 4    |       | ms    |

| LX_Leakage Current                  |                   | V <sub>LX1</sub> = V <sub>SUP</sub> , T <sub>A</sub> = +          | +25°C                                                      |       | 0.01 |       | μA    |

| Maximum Duty Cycle                  |                   | PWM mode                                                          |                                                            |       | 97.2 |       | %     |

| Minimum On-Time                     |                   |                                                                   |                                                            |       | 30   |       | ns    |

| OUT2 AND OUT3: LOW-                 | VOLTAGE SYN       | CHRONOUS STEP-DO                                                  | OWN DC-DC CONVER                                           | RTERS |      |       | 1     |

| Supply Voltage Range                | V <sub>SUP</sub>  |                                                                   |                                                            | 2.7   |      | 5.5   | V     |

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

### **Electrical Characteristics (continued)**

$(V_{SUP} = 14V, V_{PV} = V_{PV1} = V_{BIAS}, V_{PV2} = V_{PV3} = V_{OUT1}, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$  under normal conditions, unless otherwise noted. (Note 1))

| PARAMETER                      |                   |                                                                                 | MIN   | TYP                        | MAX   | UNITS |

|--------------------------------|-------------------|---------------------------------------------------------------------------------|-------|----------------------------|-------|-------|

| Supply Current                 | I <sub>PV</sub> _ | V <sub>EN</sub> _ = 5V, no load                                                 |       | 0.1                        | 5     | μA    |

| Skip-Mode Peak Current         |                   |                                                                                 |       | 0.2 x<br>I <sub>LMAX</sub> |       | mA    |

| Voltage Accuracy               | V <sub>OUT</sub>  | PWM mode, $0A \le I_{LOAD} \le I_{MAX}$ ,<br>Including line and load regulation | -1.8  |                            | +1.8  | %     |

| Feedback Voltage               |                   | Adjustable mode, I <sub>OUT</sub> = 0mA                                         | 0.790 | 0.802                      | 0.814 | V     |

| LX_On-Resistance<br>High       |                   | I <sub>LX</sub> = -800mA                                                        |       | 70                         | 110   | mΩ    |

| LX_ On-Resistance Low          |                   | I <sub>LX_</sub> = 800mA                                                        |       | 50                         | 90    | mΩ    |

| Current Limit Threehold        |                   | Option 1 (3.0A DC)                                                              | 5.0   | 5.6                        |       |       |

| Current-Limit Threshold        | I <sub>LMAX</sub> | Option 2 (1.5A DC)                                                              | 2.5   | 3.0                        |       | A     |

| LX_Rise/Fall Time              |                   | $PV_2 = PV_3 = 3.3V, I_{OUT} = 2A$                                              |       | 4                          |       | ns    |

| Soft-Start Ramp Time           |                   |                                                                                 |       | 2.5                        |       | ms    |

| LX_Leakage Current             |                   | T <sub>A</sub> = +25°C                                                          |       | 0.01                       |       | μA    |

| Duty-Cycle Range               |                   | PWM mode                                                                        | 15    |                            | 100   | %     |

| LX_ Discharge<br>Resistance    |                   |                                                                                 |       | 22                         | 48    | Ω     |

| RESET OUTPUTS (RESE            | T1 - RESET3)      |                                                                                 |       |                            |       |       |

| OV_Threshold                   |                   | Rising (external feedback divider)                                              | 105.7 | 107                        | 108.3 | - %   |

|                                |                   | Rising (internal feedback divider)                                              | 106.2 | 107                        | 108   |       |

|                                |                   | Falling (relative to nominal output voltage) (internal feedback divider)        | 94.5  | 95.5                       | 96.6  | 0/    |

| UV_ Threshold                  |                   | Falling (relative to nominal output voltage) (external feedback divider)        | 94.2  | 95.5                       | 96.9  | - %   |

| UV_ Hysteresis                 |                   |                                                                                 |       | 2.5                        |       | %     |

|                                |                   | See the Selector Guide (16,384 clocks)                                          |       | 7.8                        |       |       |

| OUT1 Active Timeout            |                   | See the Selector Guide (8192 clocks)                                            |       | 3.9                        |       | 1     |

| Period                         |                   | See the Selector Guide (4096 clocks)                                            |       | 1.9                        |       | ms    |

|                                |                   | See the Selector Guide (256 clocks)                                             |       | 0.1                        |       | 1     |

|                                |                   | See the Selector Guide (16,384 clocks)                                          |       | 7.8                        |       |       |

| OUT2, OUT3 Active              |                   | See the Selector Guide (8192 clocks)                                            |       | 3.9                        |       | 1     |

| Timeout Period                 |                   | See the Selector Guide (4096 clocks)                                            |       | 1.9                        |       | ms    |

|                                |                   | See the Selector Guide (256 clocks)                                             |       | 0.1                        |       | 1     |

| Output Low Level               |                   | I <sub>SINK</sub> = 3mA                                                         |       | 0.1                        | 0.2   | V     |

| Propagation Time               |                   | OUT <sub>1</sub> –OUT <sub>3</sub> , 5% below threshold                         | 4     |                            |       | μs    |

| ERROR STATUS OUTPU             | T (ERR)           |                                                                                 | 1     |                            |       |       |

| Output Low Level               |                   | I <sub>SINK</sub> = 3mA                                                         |       | 0.1                        | 0.2   | V     |

| THERMAL OVERLOAD               |                   |                                                                                 | 1     |                            |       |       |

| Thermal-Warning<br>Temperature |                   |                                                                                 |       | +150                       |       | °C    |

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

### **Electrical Characteristics (continued)**

$(V_{SUP} = 14V, V_{PV} = V_{PV1} = V_{BIAS}, V_{PV2} = V_{PV3} = V_{OUT1}, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C under normal conditions, unless otherwise noted. (Note 1))

| PARAMETER                       | PARAMETER SYMBOL CONDITIONS |                                                                              | MIN | TYP  | MAX | UNITS |

|---------------------------------|-----------------------------|------------------------------------------------------------------------------|-----|------|-----|-------|

| Thermal-Shutdown<br>Temperature |                             |                                                                              |     | +170 |     | °C    |

| Thermal-Shutdown<br>Hysteresis  |                             |                                                                              |     | 15   |     | °C    |

| ENABLE INPUTS (EN1-             | -EN3)                       |                                                                              | ŀ   |      |     |       |

| Input High                      |                             | V <sub>EN</sub> _ rising                                                     | 1.6 | 1.8  | 2.0 | V     |

| Hysteresis                      |                             |                                                                              |     | 0.2  |     | V     |

| EN_ Input Current               |                             | V <sub>EN_</sub> = 5V                                                        | 0.5 | 1.0  | 2.0 | μA    |

| SYNCHRONIZATION I/              | O (SYNC)                    |                                                                              | ·   |      |     |       |

| Input High                      |                             | SYNC input option (see the Selector Guide)                                   |     | 1.8  |     | V     |

| Input Low                       |                             | SYNC input option (see the Selector Guide)                                   |     | 0.8  |     | V     |

| Input Current                   |                             | SYNC input option (see the Selector<br>Guide); V <sub>SYNC</sub> = 5V        |     | 50   | 80  | μA    |

| Output High Level               |                             | SYNC output option (see the Selector Guide); $V_{PV}$ = 5V, $I_{SINK}$ = 1mA | 4.9 | 4.98 |     | V     |

| Output Low Level                |                             | SYNC output option (see the Selector<br>Guide), I <sub>SINK</sub> = 1mA      |     | 0.02 | 0.1 | V     |

| Pulldown Resistance             |                             |                                                                              |     | 100  |     | kΩ    |

| LOGIC INPUT (CSEL1)             |                             |                                                                              |     |      |     |       |

| Input High                      |                             |                                                                              |     | 1.4  |     | V     |

| Input Low                       |                             |                                                                              |     | 0.5  |     | V     |

| Input Current                   |                             | T <sub>A</sub> = +25°C                                                       |     | 2    |     | μA    |

**Note 1:** All units are 100% production tested at  $T_A = +25^{\circ}C$ . All temperature limits are guaranteed by design.

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

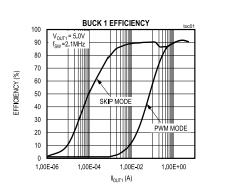

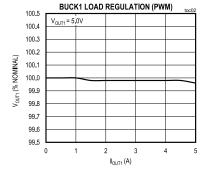

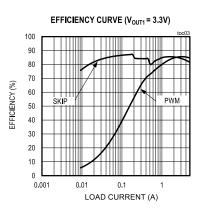

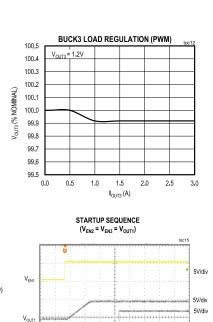

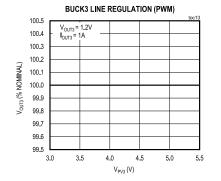

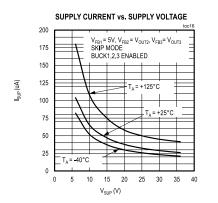

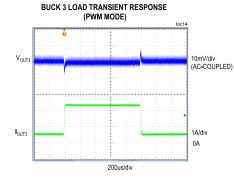

### **Typical Operating Characteristics**

(V<sub>SUP</sub> = 14V,  $T_A$  = +25°C, unless otherwise noted)

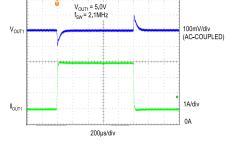

BUCK 1 LOAD TRANSIENT RESPONSE (PWM MODE)

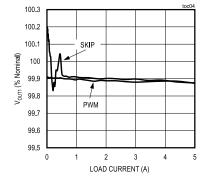

LOAD REGULATION (V<sub>OUT1</sub> = 3.3V)

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

VRESET

V<sub>OUT2</sub>

V<sub>OUT3</sub>

V<sub>RESET2</sub>

V<sub>RESET3</sub>

### **Typical Operating Characteristics (continued)**

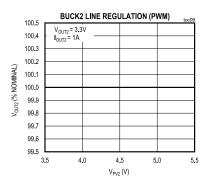

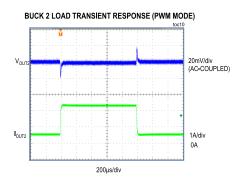

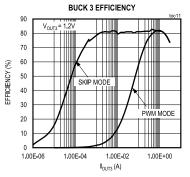

(V<sub>SUP</sub> = 14V,  $T_A$  = +25°C, unless otherwise noted)

2ms/div

5V/div

5V/div

5V/div

5V/div

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

### **Typical Operating Characteristics (continued)**

(V<sub>SUP</sub> = 14V,  $T_A$  = +25°C, unless otherwise noted)

### **Pin Configuration**

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PV1  | Supply Input for Buck 1 Low-Side Gate Drive. Connect a ceramic bypass capacitor of at least 0.1µF from PV1 to GND.                                      |

| 2   | DL1  | Low-Side Gate-Drive Output for Buck 1. DL1 output voltage swings from V <sub>GND</sub> to V <sub>PV1</sub> .                                            |

| 3   | GND  | Power Ground for Buck 1                                                                                                                                 |

| 4   | LX1  | Inductor Connection for Buck 1. Connect LX1 to the switched side of the inductor. LX1 serves as the lower supply rail for the DH1 high-side gate drive. |

| 5   | DH1  | High-Side Gate-Drive Output for Buck 1. DH1 output voltage swings from $V_{LX1}$ to $V_{BST1}$ .                                                        |

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

# **Pin Description (continued)**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | BST1             | Bootstrap Capacitor Connection for High-Side Gate Drive of Buck 1. Connect a high-voltage diode between BIAS and BST1. Connect a ceramic capacitor between BST1 and LX1. See the <i>High-Side Gate-Drive Supply (BST1)</i> section.                                                                                                                                                                                                                                                            |

| 7   | V <sub>SUP</sub> | Supply Input. Bypass $V_{SUP}$ with a minimum 0.1µF capacitor as close as possible to the device.                                                                                                                                                                                                                                                                                                                                                                                              |

| 8   | EN1              | High-Voltage Tolerant, Active-High Digital Enable Input for Buck 1. Driving EN1 high enables Buck 1.                                                                                                                                                                                                                                                                                                                                                                                           |

| 9   | BIAS             | 5V Internal Linear Regulator Output. Bypass BIAS to GND with a low-ESR ceramic capacitor of 2.2µF minimum value. BIAS provides the power to the internal circuitry. See the <i>Linear Regulator</i> ( <i>BIAS</i> ) section.                                                                                                                                                                                                                                                                   |

| 10  | PV               | Analog Supply. Connect PV to BIAS through a $10\Omega$ resistor and connect a $1\mu F$ ceramic capacitor from PV to ground.                                                                                                                                                                                                                                                                                                                                                                    |

| 11  | FB1              | Feedback Input for Buck 1. For the fixed output-voltage option, connect FB1 to BIAS for the factory-trimmed (3.0V to 3.75V or 4.6V to 5.35V) fixed output. Connect FB1 to GND for the 3.3V fixed output. For the resistor-divider-adjustable output-voltage option, connect FB1 to a resistive divider between OUT1 and GND to adjust the output voltage between 3.0V and 5.5V. In adjustable mode, FB1 regulates to 1.0V (typ). See the <i>OUT1 Adjustable Output-Voltage Option</i> section. |

| 12  | CS1              | Positive Current-Sense Input for Buck 1. Connect CS1 to the positive terminal of the current-sense resistor. See the <i>Current-Limit/Short-Circuit Protection and Current-Sense Measurement</i> sections.                                                                                                                                                                                                                                                                                     |

| 13  | OUT1             | Output Sense and Negative Current-Sense Input for Buck 1. The buck uses OUT1 to sense the output voltage. Connect OUT1 to the negative terminal of the current-sense resistor. See the <i>Current-Limit/Short-Circuit Protection</i> and <i>Current-Sense Measurement</i> sections.                                                                                                                                                                                                            |

| 14  | EN2              | Active-High Digital Enable Input for Buck 2. Driving EN2 high enables Buck 2.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15  | EN3              | Active-High Digital Enable Input for Buck 3. Driving EN3 high enables Buck 3.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16  | OUT3             | Buck Converter 3 Voltage-Sense Input. Connect OUT3 to the output of Buck 3. Connect OUT3 to an external feedback divider when setting DC-DC3 voltage externally. See the <i>OUT2/OUT3 Adjustable Output-Voltage Option</i> section.                                                                                                                                                                                                                                                            |

| 17  | RESET3           | Open-Drain Buck 3 Reset Output. RESET3 remains low for a fixed time after the output of Buck 3 has reached its regulation level (see the <i>Selector Guide</i> ). To obtain a logic signal, pull up RESET3 with an external resistor connected to a positive voltage lower than 5V.                                                                                                                                                                                                            |

| 18  | PV3              | Buck 3 Voltage Input. Connect a 2.2µF or larger ceramic capacitor from PV3 to PGND3. Connect PV3 to OUT1.                                                                                                                                                                                                                                                                                                                                                                                      |

| 19  | LX3              | Buck 3 Switching Node. LX3 is high impedance when the device is off.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20  | PGND3            | Power Ground for Buck 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 21  | PGND2            | Power Ground for Buck 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 22  | LX2              | Buck 2 Switching Node. LX2 is high impedance when the device is off.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 23  | PV2              | Buck 2 Voltage Input. Connect a 2.2µF or larger ceramic capacitor from PV2 to PGND2. Connect PV2 to OUT1.                                                                                                                                                                                                                                                                                                                                                                                      |

| 24  | RESET2           | Open-Drain Buck 2 Reset Output. RESET2 remains low for a fixed time after the output of Buck 2 has reached its regulation level (see the <i>Selector Guide</i> ). To obtain a logic signal, pull up RESET2 with an external resistor connected to a positive voltage lower than 5V.                                                                                                                                                                                                            |

| 25  | OUT2             | Buck Converter 2 Voltage-Sense Input. Connect OUT2 to the output of Buck 2. Connect OUT2 to an external feedback divider when setting DC-DC2 voltage externally. See the <i>OUT2/OUT3 Adjustable Output-Voltage Option</i> section.                                                                                                                                                                                                                                                            |

| 26  | CSEL1            | Buck 1 Clock Select. Connect CSEL1 to GND for 2.1MHz operation. Connect CSEL1 to BIAS for an OTP-programmable divide-down operation. See the <i>Selector Guide</i> for the f <sub>SW1</sub> divide ratio.                                                                                                                                                                                                                                                                                      |

| 27  | SSEN             | Spread-Spectrum Enable. Connect SSEN to GND for standard oscillator operation. Connect SSEN to BIAS to enable the spread-spectrum oscillator.                                                                                                                                                                                                                                                                                                                                                  |

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

# **Pin Description (continued)**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28  | RESET1 | Open-Drain Buck 1 Reset Output. $\overline{\text{RESET1}}$ remains low for a fixed time after the output of Buck 1 has reached its regulation level (see the <i>Selector Guide</i> ). To obtain a logic signal, pull up $\overline{\text{RESET1}}$ with an external resistor connected to an appropriate voltage.                                                 |

| 29  | GND    | Analog Ground                                                                                                                                                                                                                                                                                                                                                     |

| 30  | COMP1  | Compensation for Buck 1. See the Compensation Network section.                                                                                                                                                                                                                                                                                                    |

| 31  | ERR    | Open-Drain Error-Status Output. ERR signals a thermal-warning/shutdown condition. To obtain a logic signal, pull up ERR with an external resistor connected to a positive voltage lower than 5V.                                                                                                                                                                  |

| 32  | SYNC   | Synchronization Input/Output. SYNC allows the device to synchronize to other supplies. Connect SYNC to GND or leave unconnected to enable skip-mode operation under light loads. Connect SYNC to BIAS or an external clock to enable fixed-frequency forced-PWM-mode operation. When configured as an output, SYNC outputs the internally generated 2.1MHz clock. |

| _   | EP     | Exposed Pad. Connect the exposed pad to ground. Connecting the exposed pad to ground does not remove the requirement for proper ground connections to PGND2–PGND3 and GND. The exposed pad is attached with epoxy to the substrate of the die, making it an excellent path to remove heat from the IC.                                                            |

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

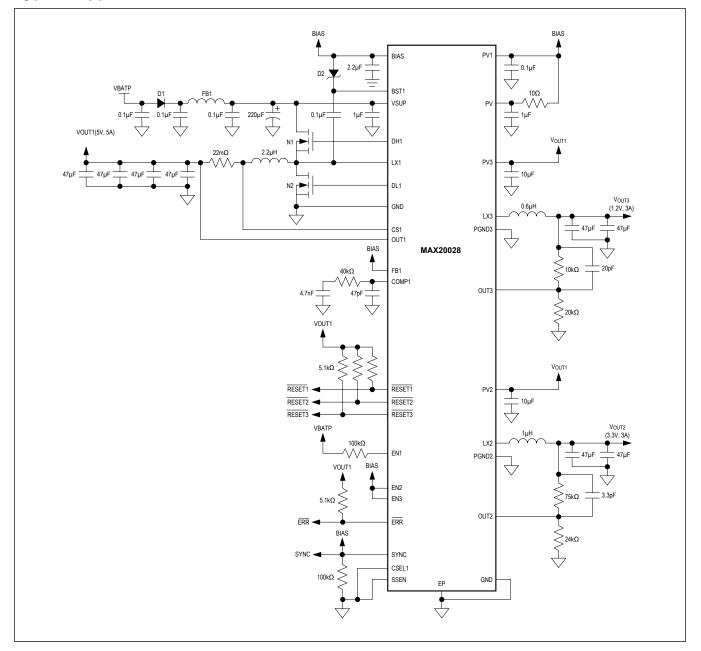

### **Typical Operating Circuit**

### Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

#### **Detailed Description**

The MAX20028 PMIC is a 2.1MHz, multichannel, DC-DC converter designed for automotive applications. The device includes one high-voltage step-down controller (OUT1) designed to run directly from a car battery, and two low-voltage step-down converters (OUT2/OUT3) cascaded from OUT1.

The 2.1MHz, high-voltage buck controller operates with a 3.5V to 36V input voltage range and is protected from loaddump transients up to 42V. The high-frequency operation eliminates AM band interference and reduces the solution footprint. It can provide an output voltage between 3.0V and 5.5V set at the factory or with external resistors. The device has two pin-selectable frequency options, 2.1MHz or a lower frequency based on the factory setting. Available factoryset frequencies are 1.05MHz, 525kHz, 420kHz, or 350kHz. Under no-load conditions, the device consumes only 30µA of quiescent current with OUT1 enabled.

The dual buck converters can deliver 1.5A or 3.0A of load current per output. They operate directly from OUT1 and provide 0.8V to 3.95V output voltage range. Factory-trimmed output voltages achieve  $\pm 1.8\%$  output voltage over load, line, and temperature without using expensive  $\pm 0.1\%$  resistors. In addition, adjustable output-voltage versions can be set to any desired values between 0.8V and 3.6V using an external resistive divider. On-board low R<sub>DS(ON)</sub> switches help minimize efficiency losses at heavy loads and reduce critical/parasitic inductance, making the layout a much simpler task with respect to discrete solutions. Following a simple layout and footprint ensures first-pass success in new designs (see the <u>PCB Layout Guidelines</u> section).

The device features either a SYNC input or a SYNC output (see the <u>Synchronization Input/Output (SYNC)</u> section and the <u>Selector Guide</u>). Optional spread-spectrum frequency modulation minimizes radiated electromagnetic emissions due to the switching frequency; factory-programmable synchronization I/O (SYNC) allows <u>better</u> noise immunity. Additional features include 4ms fixed soft-start for OUT1 and 2.5ms for OUT2/OUT3, individual RESET\_ outputs, and overcurrent/ overtemperature protections. See the <u>Selector Guide</u> for the available options.

#### Enable Inputs (EN1-EN3)

All three regulators have their own enable input. When EN1 exceeds the EN1 high threshold, the internal linear regulator is switched on. When  $V_{SUP}$  exceeds the  $V_{SUP,STARTUP}$  threshold, Buck 1 is enabled and OUT1 starts to ramp up with a 4ms soft-start. Once the Buck 1 soft-start is complete, Buck 2 and Buck 3 can be enabled. When either Buck 2 or Buck 3 is enabled, the corresponding output ramps up with a 2.5ms soft-start. When an enable input is pulled low, the converter is switched off and the corresponding OUT\_ and RESET\_ are driven low. If EN1 is low, all regulators are disabled.

#### Reset Outputs (RESET1 - RESET3)

The device features individual open-drain  $\overline{\text{RESET}}$  outputs for each buck output that asserts when the buck output voltage drops 6% below the regulated voltage.  $\overline{\text{RESET}}$  remains asserted for a fixed timeout period after the buck output rises up to its regulated voltage. The fixed timeout period is programmable between 0.1ms and 7.4ms (see the <u>Selector</u> <u>Guide</u>). To obtain a logic signal, pull up RESET\_ with an external resistor connected to a positive voltage lower than 5V.

#### Linear Regulator (BIAS)

The device features a 5V internal linear regulator (BIAS). Connect BIAS to PV, which acts as a supply for internal circuitry. Also connect BIAS to PV1, which acts as a supply for the low-side gate driver of Buck 1. Bypass BIAS with a  $2.2\mu$ F or larger ceramic capacitor as close as possible to the device. BIAS can provide up to 125mA (max), but is not designed to supply external loads.

After OUT1 completes soft-start, and depending on the OUT1 voltage setting, BIAS LDO can be turned off with the BIAS pin internally shorted to the OUT1 pin to power up internal circuits and provide gate drive for the Buck 1 low-side FET. This BIAS switchover is allowed for internally set OUT1 voltages above 4.2V (both in FPWM and skip modes of operation), and for internally set OUT1 voltages below 4.2V when in skip mode of operation. BIAS switchover is not allowed if external divider option is used for OUT1.

#### **Internal Oscillator**

#### Buck 1 Clock Select (CSEL1)

The device offers a Buck 1 clock-select input. Connect CSEL1 to GND for 2.1MHz operation. Connect CSEL1 to BIAS to divide down the Buck 1 clock frequency by 2, 4, 5, or 6 (see the <u>Selector Guide</u>). Buck 2 and Buck 3 switch at 2.1MHz (typ) and are not controlled by CSEL1.

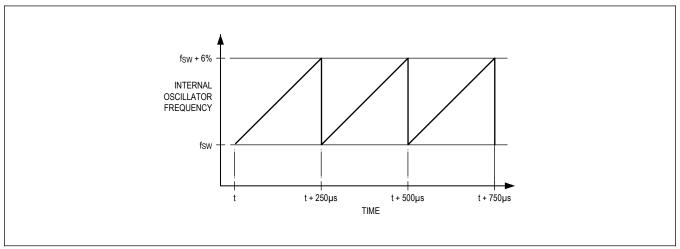

#### Spread-Spectrum Enable (SSEN)

The device features a spread-spectrum enable (SSEN) input that can quickly enable spread-spectrum operation to reduce radiated emissions. Connect SSEN to BIAS to enable the spread-spectrum oscillator. Connect SSEN to GND for standard oscillator operation. When spread spectrum is enabled, the internal oscillator frequency is varied between  $f_{SW}$  and ( $f_{SW}$  + 6%). The change in frequency has a sawtooth shape and a frequency of 4kHz (see Figure 1). This function does not apply to externally applied oscillation frequency. See the <u>Selector Guide</u> for available options.

Figure 1. Effect of Spread Spectrum on Internal Oscillator

#### Synchronization Input/Output (SYNC)

SYNC is a factory-programmable I/O. See the <u>Selector Guide</u> for available options. When configured as an input, a logichigh on SYNC enables fixed-frequency, forced-PWM mode. Apply an external clock on the SYNC input to synchronize the internal oscillator to an external clock. The SYNC input accepts signal frequencies in the range of 1.7MHz <  $f_{SYNC}$  < 2.4MHz. The external clock should have a duty cycle of 50%. A logic-low at the SYNC input enables the device to enter a low-power skip mode under light-load conditions. When configured as an output, SYNC outputs the internally generated 2.1MHz clock that switches from V<sub>PV</sub> to V<sub>GND</sub>. All converters operate in forced-PWM mode when SYNC is configured as an output.

#### **Common Protection Features**

#### Undervoltage Lockout

The device offers an undervoltage-lockout feature. Undervoltage detection is performed on the PV input. If  $V_{SUP}$  decreases to the point where Buck 1 is in dropout, PV begins to decrease. If PV falls below the UVLO threshold (2.7V, typ), all three converters switch off and the RESET\_ outputs assert low. Once the device has been switched off,  $V_{SUP}$  must exceed the  $V_{SUP,STARTUP}$  threshold before Buck 1 turns back on.

#### **Output Overvoltage Protection**

The device features overvoltage protection on the buck converter <u>outputs</u>. If the FB1 input exceeds the output overvoltage threshold, a discharge current is switched on at OUT1 and RESET1 asserts low.

### Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

#### Soft-Start

The device includes a 4ms fixed soft-start time on OUT1 and 2.5ms fixed soft-start time on OUT2/OUT3. Soft-start time limits startup inrush current by forcing the output voltage to ramp up towards its regulation point. If OUT1 is prebiased above 1.25V, all three buck converters do not start up until the prebias has been removed. Once the prebias has been removed, OUT1 self-discharges to GND and then goes into soft-start. For the MAX20028BATJ\_ option, the prebias output protection has been disabled.

#### **Thermal Warning and Overtemperature Protection**

The device features an open-drain, thermal-warning indicator ( $\overline{ERR}$ ).  $\overline{ERR}$  asserts low when the junction temperature exceeds +145°C (typ). For a logic signal, connect a pullup resistor from  $\overline{ERR}$  to a supply less than or equal to 5V. When the junction temperature exceeds +170°C (typ), an internal thermal sensor shuts down the buck converters, allowing the device to cool. The thermal sensor turns the device on again after the junction temperature cools by 30°C (typ).

#### Buck 1 (OUT1)

Buck controller 1 uses a PWM current-mode-control scheme. An internal transconductance amplifier establishes an integrated error voltage. The heart of the PWM controller is an open-loop comparator that compares the integrated voltage-feedback signal against the amplified current-sense signal plus the slope-compensation ramp, which are summed into the main PWM comparator to preserve inner-loop stability and eliminate inductor staircasing. At each rising edge of the internal clock, the high-side MOSFET turns on until the PWM comparator trips, or the maximum duty cycle is reached, or the peak current limit is reached. During this on-time, current ramps up through the inductor, storing energy in a magnetic field and sourcing current to the output. The current-mode feedback system regulates the peak inductor current as a function of the output voltage error signal. The circuit acts as a switch-mode transconductance amplifier and pushes the output LC filter pole normally found in a voltage-mode PWM to a higher frequency.

During the second half of the cycle, the high-side MOSFET turns off and the low-side MOSFET turns on. The inductor releases the stored energy as the current ramps down, providing current to the output. The output capacitor stores charge when the inductor current exceeds the required load current and discharges when the inductor current is lower, smoothing the voltage across the load. Under soft-overload conditions, when the peak inductor current exceeds the selected current limit (see the <u>Current-Limit/Short-Circuit Protection</u> section), the high-side MOSFET is turned off immediately and the low-side MOSFET is turned on and remains on to let the inductor current ramp down until the next clock cycle.

#### **PWM/Skip Modes**

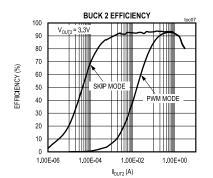

The device features a synchronization input that puts all the buck regulators either in skip mode or forced-PWM mode of operation (see the <u>Synchronization Input/Output (SYNC)</u> section). In PWM mode of operation, the regulator switches at a constant frequency with variable on-time. In skip mode of operation, the regulator's switching frequency is load dependent until the output load reaches a certain threshold. At higher load current, the switching frequency does not change and the operating mode is similar to the PWM mode. Skip mode helps improve efficiency in light-load applications by allowing the regulator to turn on the high-side switch only when the output voltage falls below a set threshold. As such, the regulator does not switch MOSFETs on and off as often as is the case in PWM mode. Consequently, the gate charge and switching losses are much lower in skip mode.

#### Minimum On-Time and Duty Cycle

The high-side gate driver for Buck 1 has a minimum on-time of 30ns (typ). This helps ensure no skipped pulses when operating the device in PWM mode at 2.1MHz with supply voltage up to 36V and output voltage down to 3.3V (see the *Electrical Characteristics* table).

#### **Current-Limit/Short-Circuit Protection**

OUT1 offers a current-limit feature that protects Buck 1 against short-circuit and overload conditions on the buck controller. Buck 1 offers a current-limit sense input (CS1). Place a sense resistor in the path of the channel 1 current flow. Connect CS1 to the high side of the sense resistor and OUT1 to the low side of the sense resistor. Current-limit protection activates once the voltage across the sense resistor increases above the 120mV (typ) current-limit threshold. In the event of a short-circuit or overload condition, the high-side MOSFET remains on until the inductor current reaches the current-limit threshold. The converter then turns on the low-side MOSFET and the inductor current ramps down. The

### Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

converter allows the high-side MOSFET to turn on only when the voltage across the current-sense resistor ramps down to below 120mV (typ). This cycle repeats until the short or overload condition is removed.

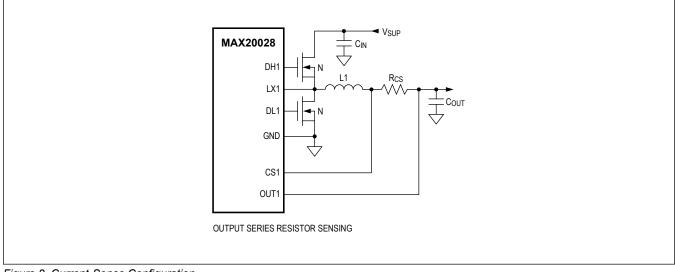

#### **Current-Sense Measurement**

For the best current-sense accuracy and overcurrent protection, use a 1% tolerance current-sense resistor between the inductor and output, as shown in <u>Figure 2</u>. This configuration constantly monitors the inductor current, allowing accurate current-limit protection. Use low-inductance current-sense resistors for accurate measurement.

#### Figure 2. Current-Sense Configuration

#### High-Side Gate-Drive Supply (BST1)

The high-side MOSFET is turned on by closing an internal switch between BST1 and DH1 and transferring the bootstrap capacitor's charge (at BST1) to the gate of the high-side MOSFET. This charge refreshes when the high-side MOSFET turns off and the LX1 voltage drops down to ground potential, taking the negative terminal of the capacitor to the same potential. At this time, the bootstrap diode recharges the positive terminal of the bootstrap capacitor. The selected n-channel high-side MOSFET determines the appropriate boost capacitance values (CBST1 in the <u>Typical Operating</u> <u>Circuit</u>) according to the following equation:

$$C_{\text{BST1}} = \frac{Q_G}{\Delta V_{\text{BST1}}}$$

where  $Q_G$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST1}$  is the voltage variation allowed on the high-side MOSFET driver after turn-on. Choose  $\Delta V_{BST1}$  such that the available gate-drive voltage is not significantly degraded (e.g.,  $\Delta V_{BST1}$  = 100mV to 300mV) when determining CBST1. Use a Schottky diode when efficiency is most important, as this maximizes the gate-drive voltage. If the quiescent current at high temperature is important, a low-leakage switching diode should be used.

The boost capacitor should be a low-ESR ceramic capacitor. A minimum value of 100nF works in most cases. A minimum value of 470nF is recommended when using a Schottky diode.

#### Dropout

When OUT1 input voltage is lower than the desired output voltage, the converter is in dropout mode. Buck 1 continuously draws current from the bootstrap capacitor when the high-side switch is on. Therefore, the bootstrap capacitor needs to be refreshed periodically. When in dropout, the Buck 1 high-side gate drive shuts off every 8µs, at which point the low-side gate drive turns on for 120ns.

### Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

#### Buck 2 and Buck 3 (OUT2 and OUT3)

Buck converters 2 and 3 are high-efficiency, low-voltage converters with integrated FETs. They use a PWM currentmode-control scheme operated at 2.1MHz to optimize component size and efficiency, while eliminating AM band interference. The buck converters can be configured to deliver 1.5A or 3.0A per channel. They operate directly from OUT1 and have either fixed or resistor-programmable output voltages that range from 0.8V to 3.95V (see the <u>Selector</u> <u>Guide</u>). Buck 2 and Buck 3 feature low on-resistance internal FETs that contribute to high efficiency and smaller system cost and board space. Integration of the p-channel high-side FET enables both channels to operate with 100% duty cycle when the input voltage falls to near the output voltage. They feature a programmable active timeout period (see the <u>Selector Guide</u>) that adds a fixed delay before the corresponding RESET\_ can go high.

#### FPWM/Skip Modes

The device features a synchronization input (SYNC) that puts the converter either in skip mode or forced-PWM (FPWM) mode of operation. See the <u>Internal Oscillator</u> section. In FPWM mode, the converter switches at a constant frequency with variable on-time. In skip mode, the converter's switching frequency is load-dependent until the output load reaches a certain threshold. At higher load current, the switching frequency does not change and the operating mode is similar to the FPWM mode.

Skip mode helps improve efficiency in light-load applications by allowing the converters to turn on the high-side switch only when the output voltage falls below a set threshold. As such, the converter does not switch MOSFETs on and off, as often is the case in FPWM mode. Consequently, the gate charge and switching losses are much lower in skip mode.

#### **Current-Limit/Short-Circuit Protection**

Buck converters 2 and 3 feature current-limit protection that protects the device against short-circuit and overload conditions at their outputs. The current-limit value is dependent on the version selected, 1.5A or 3.0A (max) DC current. See the <u>Selector Guide</u> for the current-limit value of the chosen option and the <u>Electrical Characteristics</u> table for the corresponding current limit. In the event of a short-circuit or overload condition at an output, the high-side MOSFET remains on until the inductor current reaches the high-side MOSFET's current-limit threshold. The converter then turns on the low-side MOSFET and the inductor current ramps down.

The converter allows the low-side MOSFET to turn off only when the inductor current ramps down to the low-side MOSFET's current threshold. This cycle repeats until the short or overload condition is removed.

# Selector Guide

|        | BUCK 1                            |                                        |                                     |                                   | BUCK 2                          |                                     |                                   | BUCK 3                          |                                                            |       |  |

|--------|-----------------------------------|----------------------------------------|-------------------------------------|-----------------------------------|---------------------------------|-------------------------------------|-----------------------------------|---------------------------------|------------------------------------------------------------|-------|--|

| OPTION | FIXED<br>OUTPUT<br>VOLTAGE<br>(V) | fsw1<br>DIVIDE<br>RATIO<br>FROM<br>fsw | ACTIVE<br>TIMEOUT<br>PERIOD<br>(ms) | FIXED<br>OUTPUT<br>VOLTAGE<br>(V) | MAX<br>OUTPUT<br>CURRENT<br>(A) | ACTIVE<br>TIMEOUT<br>PERIOD<br>(ms) | FIXED<br>OUTPUT<br>VOLTAGE<br>(V) | MAX<br>OUTPUT<br>CURRENT<br>(A) | ACTIVE<br>TIMEOUT<br>PERIOD<br>(SAME AS<br>BUCK 2)<br>(ms) | SYNC  |  |

| A      | 3.3/5                             | ÷5                                     | 3.9                                 | ADJ                               | 3.0                             | 3.9                                 | ADJ                               | 3.0                             | 3.9                                                        | Input |  |

| В      | 3.3/5                             | ÷5                                     | 3.9                                 | ADJ                               | 1.5                             | 3.9                                 | ADJ                               | 1.5                             | 3.9                                                        | Input |  |

| С      | ADJ                               | ÷5                                     | 3.9                                 | ADJ                               | 1.5                             | 3.9                                 | ADJ                               | 1.50                            | 3.9                                                        | Input |  |

### **Applications Information**

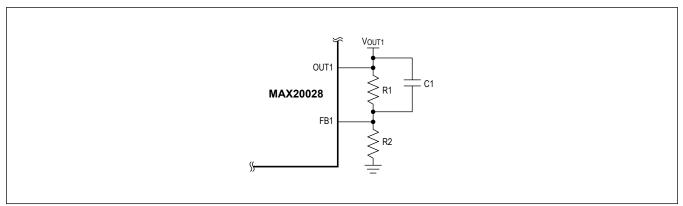

#### **OUT1 Adjustable Output-Voltage Option**

The device's adjustable output-voltage version (see the <u>Selector Guide</u> for details) allows the customer to set OUT1 voltage between 3.0V and 5.5V. Connect a resistive divider from OUT1 to FB1 to GND to set the output voltage (Figure 3). Select R<sub>2</sub> (FB1 to GND resistor) less than or equal to  $100k\Omega$ . Calculate R<sub>1</sub> (V<sub>OUT1</sub> to FB1 resistor) with the following equation:

$$R_1 = R_2 \left[ \frac{V_{\text{OUT1}}}{V_{\text{FB1}}} - 1 \right]$$

where  $V_{FB1} = 1V$  (see the <u>Electrical Characteristics</u> table).

The external feedback resistive divider must be frequency compensated for proper operation. Place a capacitor across  $R_1$  in the resistive divider network. Use the following equation to determine the value of the capacitor:

if  $R_2/R_1 > 1$ ,  $C_1 = C(R_2/R_1)$  else,  $C_1 = C$ , where C = 10pF.

For fixed-output options, connect FB1 to BIAS for the factory-programmed, fixed-output voltage. Connect FB1 to GND for a fixed 3.3V output voltage.

Figure 3. Adjustable OUT1 Voltage Configuration

#### **OUT1 Current-Sense Resistor Selection**

Choose the current-sense resistor based on the maximum inductor current ripple factor ( $K_{INDMAX}$ ) and minimum current-limit threshold across current-sense resistor ( $V_{LIM1MIN} = 0.1V$ ).

The formula for calculating the current-sense resistor is:

$$R_{\text{CSMAX}} = \frac{V_{\text{LIM1MIN}}}{I_{\text{OUTMAX}} \times \left(1 + \frac{K_{\text{INDMAX}}}{2}\right)}$$

where  $I_{OUTMAX}$  is the maximum load current for Buck 1 and  $K_{INDMAX}$  is the maximum inductor current ripple factor. The maximum inductor current ripple factor is a function of the inductor chosen, as well as the operating conditions, and is typically chosen between 0.3 and 0.4:

$$K_{\text{INDMAX}} = \frac{\left(V_{\text{SUP}} - V_{\text{OUT}}\right) \times D}{I_{\text{OUTMAX}} \times \left(1 + \frac{K_{\text{INDMAX}}}{2}\right)}$$

where D is the duty cycle. Below is a numerical example to calculate the current-sense resistor in Figure 3. The maximum inductor current ripple factor is chosen at the maximum supply voltage (36V) to be 0.4:

### Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

$$R_{\text{CSMAX}} = \frac{0.1}{I_{\text{OUTMAX}} * f_{\text{SW1}}[\text{MHz}] * L[\mu\text{H}]} = \frac{0.1}{5 * \left(1 + \frac{0.4}{2}\right)} = 0.0166\Omega$$

#### **OUT1 Inductor Selection**

Three key inductor parameters must be specified for operation with the device: inductance value (L), inductor saturation current ( $I_{SAT}$ ), and DC resistance ( $R_{DCR}$ ). Use the following formulas to determine the minimum inductor value:

$$L_{\text{MIN1}}[H] = 1.3 \times \left(V_{\text{SUPMAX}} - V_{\text{OUT1}}\right) \times \left(\frac{V_{\text{OUT1}}}{V_{\text{SUPMAX}}}\right) \times \left(\frac{1}{f_{\text{SW1}} \times f_{\text{OUTMAX}} \times K_{\text{INDMAX}}}\right)$$

where f<sub>SW1</sub> is the operating frequency and 1.3 is a coefficient that accounts for inductance initial precision. or:

$$L_{\text{MIN2}}[\mu\text{H}] = 1.3 \times \frac{V_{\text{OUT1}}}{0.8} \times R_{\text{CS}} \times A_{\text{V}_{\text{CS}}} \times \frac{2.1 \times 10^6}{f_{\text{SW1}}}$$

where  $A_{V_CS}$  is current-sense amplifier gain (8V/V, typ). For proper operation, the chosen inductor value must be greater than or equal to  $L_{MIN1}$  and  $L_{MIN2}$ . The maximum inductor value recommended is twice the chosen value from the above formulas.

Table 1 lists some of the inductor values for 5A output current and several switching frequencies and output voltages.

#### Table 1. Inductor Values vs. (V<sub>SUPMAX</sub>, V<sub>OUT1</sub>)

| V <sub>SUPMAX</sub> to V <sub>OUT1</sub> (V) | V <sub>SUPMAX</sub> = 36V, V <sub>OUT1</sub> = 5V |      |       |       |      | V <sub>SUP</sub> | MAX = 36 | SV, V <sub>OUT1</sub> | = 3.3V |       |

|----------------------------------------------|---------------------------------------------------|------|-------|-------|------|------------------|----------|-----------------------|--------|-------|

| f <sub>SW1</sub> (MHz)                       | 2.1                                               | 1.05 | 0.525 | 0.420 | 0.35 | 2.1              | 1.05     | 0.525                 | 0.420  | 0.350 |

| INDUCTOR (µH), I <sub>LOAD</sub> = 5A        | 1.5                                               | 3.3  | 5.6   | 6.8   | 8.2  | 1.0              | 2.2      | 4.7                   | 4.7    | 6.8   |

#### **Buck 1 Input Capacitor**

The device is designed to operate with a single  $0.1\mu$ F capacitor on the V<sub>SUP</sub> input and a single  $0.1\mu$ F capacitor on the PV1 input. Place these capacitors as close as possible to their corresponding inputs to ensure the best EMI and jitter performance.

#### **OUT1 Output Capacitor**

The primary purpose of the OUT1 output capacitor is to reduce the change in V<sub>OUT1</sub> during load transient conditions. The minimum capacitor depends on the output voltage, maximum current, and load regulation accuracy. Use the following formula to determine the minimum output capacitor for Buck 1:

$$C_{\text{OUT}} \ge \frac{I_{\text{OUT1(MAX)}}}{2\pi \times f_{\text{CO}} \times \Delta V_{\text{OUT1}}}$$

where  $f_{CO}$  is the crossover frequency set by  $R_C$  and  $C_C$ , and  $\Delta V_{OUT1}$  is the allowable undershoot/overshoot voltage during a load-transient condition measured in volts (V).

For proper functionality, ceramic capacitors must be used. To avoid instability, make sure that the self-resonance of the ceramic capacitors is above 1MHz.

#### **Buck 1 MOSFET Selection**

Buck 1 drives two external logic-level n-channel MOSFETs as the circuit switch elements. The key selection parameters to choose these MOSFETs are:

- On-resistance (R<sub>DS(ON)</sub>)

- Maximum drain-to-source voltage (V<sub>DS(MAX)</sub>)

- Minimum threshold voltage (V<sub>TH(MIN)</sub>)

- Total gate charge (Q<sub>G</sub>)

- Reverse transfer capacitance (C<sub>RSS</sub>)

- Power dissipation

# Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

Both n-channel MOSFETs must be logic-level types with guaranteed on-resistance specifications at  $V_{GS}$  = 4.5V when  $V_{OUT1}$  is set to 5V or  $V_{GS}$  = 3V when  $V_{OUT1}$  is set to 3.3V. The conduction losses at minimum input voltage should not exceed MOSFET package thermal limits or violate the overall thermal budget. Also, ensure that the conduction losses plus switching losses at the maximum input voltage do not exceed package ratings or violate the overall thermal budget. In particular, check that the dV/dt caused by DH1 turning on does not pull up the DL1 gate through its drain-to-gate capacitance. This is the most frequent cause of cross-conduction problems.

Gate-charge losses are dissipated by the driver and do not heat the MOSFET; therefore, the power dissipation in the device due to drive losses must be checked. Both MOSFETs must be selected so that their total gate charge is low enough; therefore, PV1/V<sub>OUT1</sub> can power both drivers without overheating the device:

#### $P_{\text{DRIVE}} = V_{\text{OUT1}} \times (Q_{\text{GTOTH}} + Q_{\text{GTOTL}}) \times f_{\text{SW1}}$

where  $Q_{GTOTL}$  is the low-side MOSFET total gate charge and  $Q_{GTOTH}$  is the high-side MOSFET total gate charge. Select MOSFETs with a  $Q_{G}$  total of less than 10nC. The n-channel MOSFETs must deliver the average current to the load and the peak current during switching. Dual MOSFETs in a single package can be an economical solution. To reduce switching noise for smaller MOSFETs, use a series resistor in the DH1 path and additional gate capacitance. Contact the factory for guidance using gate resistors.

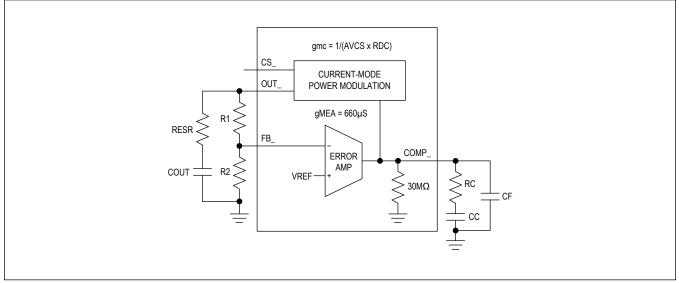

#### **Compensation Network**

The device uses a current-mode-control scheme that regulates the output voltage by forcing the required current through the external inductor, so the controller uses the voltage drop across the DC resistance of the inductor or the alternate series current-sense resistor to measure the inductor current. Current-mode control eliminates the double pole in the feedback loop caused by the inductor and output capacitor, resulting in a smaller phase shift, and requiring less elaborate error-amplifier compensation than voltage-mode control. A single series resistor ( $R_C$ ) and capacitor ( $C_C$ ) is all that is required to have a stable, high-bandwidth loop in applications where ceramic capacitors are used for output filtering (see Figure 4). For other types of capacitors, due to the higher capacitance and ESR, the frequency of the zero created by the capacitance and ESR is lower than the desired closed-loop crossover frequency. To stabilize a non-ceramic output capacitor loop, add another compensation capacitor ( $C_F$ ) from COMP1 to GND to cancel this ESR zero.

The basic regulator loop is modeled as a power modulator, output feedback divider, and an error amplifier (see Figure 4). The power modulator has a DC gain set by  $g_{mc} \times R_{LOAD}$ , with a pole and zero pair set by  $R_{LOAD}$ , the output capacitor ( $C_{OUT}$ ), and its ESR. The loop response is set by the following equation:

#### $GAIN_{MOD(dc)} = g_{mc} \times R_{LOAD}$

where  $R_{LOAD} = V_{OUT}/I_{OUT(MAX)}$  in ohms ( $\Omega$ ) and  $g_{mc} = 1/(A_{V_CS} \times R_{DC})$  in Siemens (S).  $A_{V_CS}$  is the voltage gain of the current-sense amplifier and is typically 8V/V.  $R_{DC}$  is the DC resistance of the inductor or the current-sense resistor in ohms ( $\Omega$ ).

In a current-mode step-down converter, the output capacitor and load resistance introduce a pole at the following frequency:

$f_{\text{pMOD}} = \frac{1}{2\pi \times C_{\text{OUT}} \times R_{\text{LOAD}}}$

The unity-gain frequency of the power stage is set by C<sub>OUT</sub> and g<sub>mc</sub>:

$f_{\text{UGAINpMOD}} = \frac{g_{\text{mc}}}{2\pi \times \text{ESR} \times C_{\text{OUT}}}$

The output capacitor and its ESR also introduce a zero at:

$$f_{\rm ZMOD} = \frac{1}{2\pi \times \text{ESR} \times C_{\rm OUT}}$$

When  $C_{OUT}$  is composed of "n" identical capacitors in parallel, the resulting  $C_{OUT} = n \times C_{OUT(EACH)}$ , and ESR = ESR<sub>(EACH)</sub>/n. Note that the capacitor zero for a parallel combination of like-value capacitors is the same as for an individual capacitor.

The feedback voltage-divider has a gain of  $GAIN_{FB} = V_{FB}/V_{OUT}$ , where  $V_{FB}$  is 1V (typ).

The transconductance error amplifier has a DC gain of GAIN<sub>EA(DC)</sub> = g<sub>m,EA</sub> x R<sub>OUT,EA</sub>, where g<sub>m,EA</sub> is the error-

### Step-Down Controller with Dual 2.1 MHz Step-Down DC-DC Converters

amplifier transconductance, which is 660 $\mu$ S (typ), and R<sub>OUT,EA</sub> is the output resistance of the error amplifier, which is 30M $\Omega$  (typ).

A dominant pole ( $f_{dpEA}$ ) is set by the compensation capacitor ( $C_C$ ) and the amplifier output resistance ( $R_{OUT,EA}$ ). A zero ( $f_{ZEA}$ ) is set by the compensation resistor ( $R_C$ ) and the compensation capacitor ( $C_C$ ). There is an optional pole ( $f_{PEA}$ ) set by  $C_F$  and  $R_C$  to cancel the output capacitor ESR zero if it occurs near the crossover frequency ( $f_C$ , where the loop gain equals 1 (0dB)).

Thus:

$$f_{dpEA} = \frac{1}{2\pi \times C_C \times (R_{OUT, EA} + R_C)}$$

$$f_{zEA} = \frac{1}{2\pi \times C_C \times R_C}$$

$$f_{pEA} = \frac{1}{2\pi \times C_F |R_C|}$$

The loop-gain crossover frequency ( $f_C$ ) should be set below 1/5 of the switching frequency and much higher than the power-modulator pole ( $f_{pMOD}$ ). Select a value for  $f_C$  in the range:

$f_{\text{pMOD}} < < f_C \le \frac{f_{\text{SW}}}{10}$

At the crossover frequency, the total loop gain must be equal to 1.

Thus:

$$GAIN_{MOD(f_C)} \times \frac{V_{FB}}{V_{OUT}} \times GAIN_{EA(f_C)} = 1$$

$GAIN_{EA(f_C)} = g_{m, EA} \times R_C$

$$GAIN_{MOD(f_{C})} = GAIN_{MOD(dc)} \times \frac{f_{pMOD}}{f_{C}}$$

Therefore:

$$GAIN_{MOD(f_C)} \times \frac{V_{FB}}{V_{OUT}} \times g_{m, EA} \times R = 1$$

Solving for R<sub>C</sub>:

$$R_{C} = \frac{V_{OUT}}{g_{m, EA} \times V_{FB} \times GAIN_{MOD}(f_{C})}$$

Set the error-amplifier compensation zero formed by R<sub>C</sub> and C<sub>C</sub> at the f<sub>pMOD</sub>. Calculate the value of C<sub>C</sub> as follows:

$$C_C = \frac{1}{2\pi \times f_{\text{pMOD}} \times R_C}$$

If  $f_{zMOD}$  is less than 5 x  $f_C$ , add a second capacitor  $C_F$  from COMP1 to GND. The value of  $C_F$  is:

$$C_F = \frac{1}{2\pi \times f_{zMOD} \times R_C}$$

As the load current decreases, the modulator pole also decreases; however, the modulator gain increases accordingly and the crossover frequency remains the same.

Below is a numerical example to calculate the compensation-network component values of Figure 4:

$$A_{V CS} = 8V/V$$

$R_{\rm DCR} = 22 m \Omega$

$$\begin{split} g_{\rm mc} &= \frac{1}{\left(A_{\rm V\_CS} \times R_{\rm DC}\right)} = \frac{1}{(8 \times 0.022)} = 5.68 \\ V_{\rm OUT} &= 5V \\ I_{\rm OUT(MAX)} &= 5A \\ R_{\rm LOAD} &= \frac{V_{\rm OUT}}{I_{\rm OUT(MAX)}} = \frac{5V}{6A} = 0.833\Omega \\ C_{\rm OUT} &= 4 \times 47 \mu \text{F} = 188 \mu \text{F} \\ \text{ESR} &= \frac{9 \text{m}\Omega}{4} = 2.25 \text{m}\Omega \\ f_{\rm SW} &= 0.420 \text{MHz} \\ \text{GAIN}_{\rm MOD(dc)} &= 5.68 \times 0.833 = 4.73 \\ f_{\rm pMOD} &= \frac{1}{2\pi \times 188 \mu \text{F} \times 0.833} \approx 376 \text{kHz} \\ \text{Since } f_{z\text{MOD}} > f_{c}: \\ R_{C} &\approx 33 \text{k}\Omega \\ C_{C} &\approx 4.7 \text{nF} \\ C_{F} &\approx 12 \text{pF} \end{split}$$

Figure 4. Compensation Network

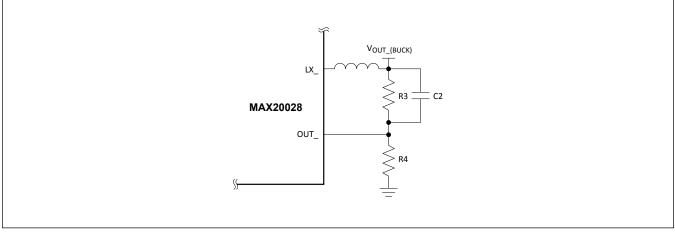

#### **OUT2/OUT3 Adjustable Output-Voltage Option**