# Dual Channel High Speed Low Side Driver with Negative Input Capability (24V Supply, 5A peak source and sink)

#### 1 FEATURES

- 5A Peak Source Current and 5A Peak Sink Current

- 4.5V 24V Wide Supply Voltage Range

- Down to -5V Negative Input Voltage Capability

- Fast Propagation Delay: 14ns

- Fast Rising and Falling Time: 8ns and 6ns

- TTL Input-Logic Threshold

- Under Voltage Lock Out Protection

- Low Quiescent Current: 64uA

- Output Low When Input Floating

- Independent Enable logic for Each Channel

- Available in SOIC-8L Package

## 2 APPLICATIONS

- Power MOSFET Gate Driver

- IGBT Gate Driver

- Switching Power Supply

- Motor Control, Solar Power

# 3 ORDERING INFORMATION

|   | ТҮРЕ        | MARKING | PACKAGE   |

|---|-------------|---------|-----------|

| > | GBI7254SMBR | 7254    | SOIC-8L   |

|   | GBI7254MMAR | 7254    | EMSOP-8L  |

|   | GBI7254NMCR | 7254    | DFN3*3-8L |

#### 4 DISCRIPTION

The GBI7254, dual channel high speed low side gate driver, provides 5A peak source and sink current along with rail-to-rail driving capability for MOSFET, IGBT, and GaN power device. The device features a minimum 14ns input to output propagation delay and 24V power supply rail makes it suitable for high frequency power converter application. The negative input is acceptable down to -5V for enhancing the input noise immunity. The wide input hysteresis is compatible for both TTL and CMOS low voltage logic. Each channel of the device adopts non-overlap driver design to avoid the shoot-through of output stage. It operates over a wide temperature range -40°C to 150°C. The GBI7254 is available in SOIC-8L Package.

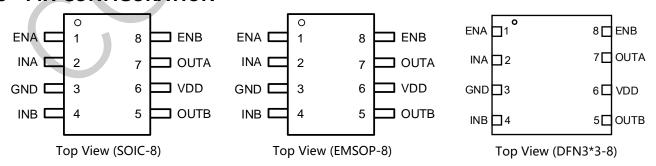

#### 5 PIN CONFIGURATION

**Table 1. GBI7254 PIN CONFIGURATION**

| PIN OUT |     | 1/0 | DIAL FUNCTION                                                                                                                                     |

|---------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0 | PIN FUNCTION                                                                                                                                      |

| ENA     | 1   | I   | Channel A Enable Input.  ENA biased low disables Channel A output regardless of INA state.  ENA biased high or floating enables Channel A output. |

| INA     | 2   | I   | Channel A Input                                                                                                                                   |

| GND     | 3   | -   | Power Ground                                                                                                                                      |

| INB     | 4   | I   | Channel B Input                                                                                                                                   |

| OUTB    | 5   | 0   | Channel B Output                                                                                                                                  |

| VDD     | 6   | I   | System Power Supply.                                                                                                                              |

| OUTA    | 7   | 0   | Channel A Output                                                                                                                                  |

| ENB     | 8   | I   | Channel B Enable Input.  ENB biased low disables Channel B output regardless of INA state.  ENB biased high or floating enables Channel B output. |

# **6 SPECIFICATIONS**

# **6.1 ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature unless otherwise noted

| DESCRIPTION                    | SYMBOL             | MIN  | MAX | UNIT |

|--------------------------------|--------------------|------|-----|------|

| Logic Input & Input Enable     | INA, INB, ENA, ENB | -5   | 26  | V    |

| Gate Driver Output             | OUTA, OUTB         | -0.3 | 26  | V    |

| Supply Voltage                 | VDD                | -0.3 | 26  | V    |

| Operating junction temperature | $T_{\mathtt{J}}$   | -40  | 150 | °C   |

| Storage temperature            | $T_{STG}$          | -65  | 150 | °C   |

## **6.2 ESD RATINGS**

| PARAMETER        | DEFINITION                                                                         | MIN   | MAX | UNIT |

|------------------|------------------------------------------------------------------------------------|-------|-----|------|

| V <sub>ESD</sub> | Human Body Model (HBM), per ANSI-JEDEC-JS-001-<br>2014 specification, all pins (1) | -2    | +2  | kV   |

|                  | Charged Device Model (CDM), per ANSI-JEDEC-JS-                                     | 1     | 11  | kV   |

|                  | 002-2014 specification, all pins (1)                                               | -1 +1 |     | ΚV   |

<sup>(1)</sup> HBM and CDM stressing are done in accordance with the ANSI/ESDA/JEDEC JS-001-2014 specification

## **6.3 RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range unless otherwise noted

| PARAMETER DEFINITION             |                                | MIN | MAX | UNIT |

|----------------------------------|--------------------------------|-----|-----|------|

| $V_{DD}$                         | Supply voltage range           | 4.5 | 24  | V    |

| V <sub>INA</sub> , INB, ENA, ENB | Input & Enable voltage range   | -5  | 24  | V    |

| T <sub>J</sub>                   | Operating junction temperature | -40 | 150 | °C   |

# **6.4 THERMAL INFORMATION**

| PARAMETER       | THERMAL METRIC                               | SOIC-8 | UNIT |

|-----------------|----------------------------------------------|--------|------|

| $R_{\theta JA}$ | Junction to ambient thermal resistance       | 130.9  | °C/W |

| $R_{\theta JC}$ | Junction to case thermal resistance          | 80     | °C/W |

| Ψл              | Junction to top characterization parameter   | 21.9   | °C/W |

| Ψлв             | Junction to board characterization parameter | 70.9   | °C/W |

# **6.5 ELECTRICAL CHARACTERISTICS**

V<sub>DD</sub>=12V, T<sub>J</sub>=-40°C~125°C, typical values are tested under 25°C.

| SYMBOL         | PARAMETER                | TEST CONDITION         | MIN | TYP | MAX | UNIT |

|----------------|--------------------------|------------------------|-----|-----|-----|------|

| Power Supply   |                          |                        |     |     |     |      |

| $V_{DD}$       | Operating supply voltage |                        | 4.5 |     | 24  | V    |

| V              | Input UVLO               | V <sub>DD</sub> rising |     | 4.2 | 4.5 | V    |

| $V_{DD\_UVLO}$ | Hysteresis               |                        |     | 300 |     | mV   |

| IQ             | Quiescent current        | INA=INB=GND,           |     | 64  |     | uA   |

| SYMBOL                                | PARAMETER                                    | TEST CONDITION                                 | MIN | TYP | MAX | UNIT |

|---------------------------------------|----------------------------------------------|------------------------------------------------|-----|-----|-----|------|

|                                       |                                              | V <sub>DD</sub> =3.5V,                         |     |     |     |      |

|                                       |                                              | ENA=ENB= Floating                              |     |     |     |      |

|                                       |                                              | INA=INB=GND,                                   |     |     |     |      |

|                                       |                                              | V <sub>DD</sub> =12V,                          |     | 124 |     | uA   |

|                                       |                                              | ENA=ENB= Floating                              |     |     |     |      |

| INPUTS                                |                                              |                                                |     |     |     |      |

| V <sub>INA, INB</sub>                 | Input+ logic high threshold                  |                                                |     | 2.1 |     | V    |

| V <sub>INA, INB</sub>                 | Input+ logic low threshold                   |                                                |     | 1   |     |      |

| V <sub>IN Hys</sub>                   | Hysteresis                                   |                                                |     | 1.1 |     | V    |

| V <sub>ENA_H</sub> , <sub>ENB_H</sub> | Enable logic high threshold                  |                                                |     | 2.1 |     | V    |

| V <sub>ENA_L</sub> , <sub>ENB_L</sub> | Enable logic low threshold                   |                                                |     | 1.2 |     | V    |

| V <sub>ENHys</sub>                    | Hysteresis                                   |                                                |     | 0.9 |     | V    |

| OUTPUT                                |                                              |                                                |     |     |     |      |

| I <sub>SINK/SRC</sub>                 | Output Sink/Source peak current              | C <sub>Load</sub> =10nF, F <sub>sw</sub> =1kHz |     | 5   |     | А    |

| R <sub>OH</sub>                       | Output pull high resistance                  | I <sub>OUT</sub> = - 10mA                      |     | 10  |     | Ω    |

| R <sub>OL</sub>                       | Output pull low resistance                   | I <sub>OUT</sub> = 10mA                        |     | 0.6 |     | Ω    |

| Timing                                |                                              |                                                |     |     |     |      |

| T <sub>R</sub>                        | Output rising time                           | C <sub>Load</sub> =1nF                         |     | 8   |     | ns   |

| T <sub>F</sub>                        | Output falling time                          | C <sub>Load</sub> =1nF                         |     | 6   |     | ns   |

| т                                     | IN to output propagation delay, Rising edge  | C <sub>Load</sub> =1nF                         |     | 14  |     | ns   |

| $T_{D\_IN}$                           | IN to output propagation delay, Falling edge | C <sub>Load</sub> =1nF                         |     | 15  |     | ns   |

| T                                     | Enable to output propagation delay, Rising   | C <sub>Load</sub> =1nF                         |     | 16  |     | ns   |

| $T_{D_{EN}}$                          | Enable to output propagation delay, Falling  | C <sub>Load</sub> =1nF                         |     | 17  |     | ns   |

| T <sub>MIN_ON</sub>                   | Minimum input pulse width                    | C <sub>Load</sub> =1nF                         |     | 15  |     | ns   |

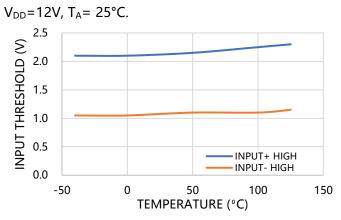

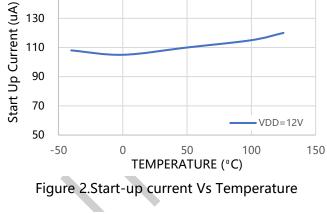

## 7 TYPICAL CHARACTERISTICS

Figure 1. Input Threshold Vs Temperature

150

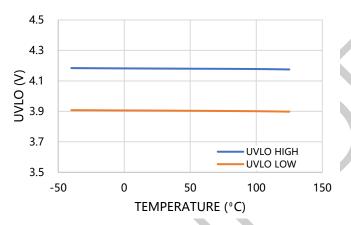

Figure 3.UVLO Vs Temperature

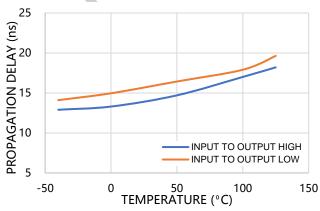

Figure 4. Input to Output Propagation Delay vs

Temperature

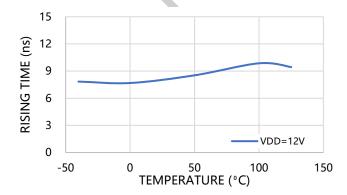

Figure 5.Output Rising Time Vs Temperature

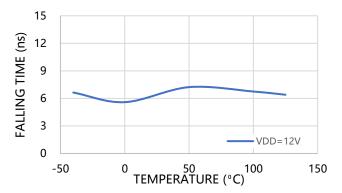

Figure 6.Output Falling Time Vs Temperature

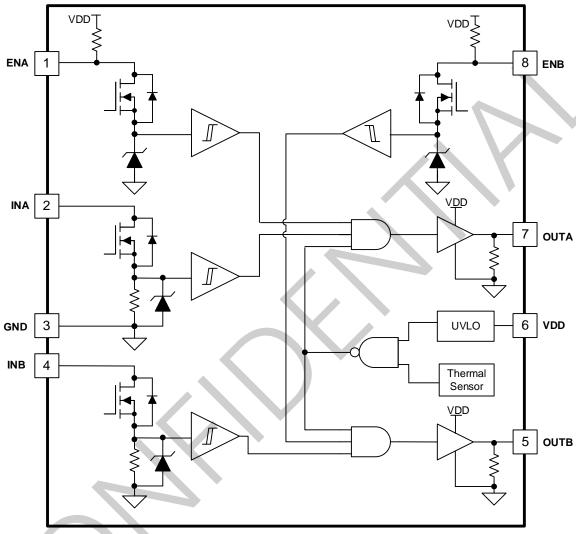

# 8 FUNCTIONAL BLOCK DIAGRAM

Figure 7. GBI7254 Block Diagram

#### 9 DISCRIPTION

#### 9.1 Overview

The GBI7254 is a dual channel, high speed, low side gate driver for power MOSFET, IGBT and GaN HMET with up to 24V wide supply and 5A source/sink peak current each channel along with the minimum input to output propagation delay of 14ns. The GBI7254 supports non-invertible outputs. The input is able to be down to -5V DC which enhances the driver input stage noise immunity.

The 24V rail-to-rail output improves the GBI7254 output stage robustness during the switching load fast transition.

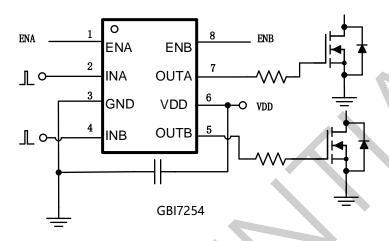

# 9.2 VDD Power Supply

The GBI7254 operates under a supply voltage range between 4.5V to 24V. It's recommended to put two VDD bypass capacitor in parallel to prevent noise problems on supply VDD. It has to put a 0.1uF SMT ceramic capacitor as close as possible between the VDD pin to the GND pin. To avoid the unexpected VDD glitch, a large capacitor (ex. 1uF or 10uF) with relatively low ESR must be connected in parallel with that 0.1uF capacitor. This parallel combination of capacitors presents a low impedance characteristic for the expected current levels and switching frequencies in the application.

# 9.3 VDD Under Voltage Lock Out (UVLO)

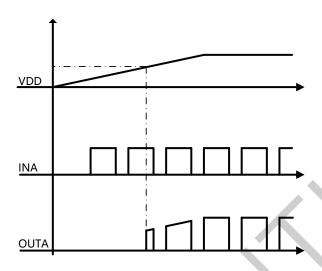

The GBI7254 implements the Under Voltage Lock Out (UVLO) with rising threshold of typically 4.2 V along with 300mV typical hysteresis. The VDD voltage which is able to down to 4.5V is especially suitable for driving wide band gap power device, like GaN.

The UVLO holds the output low regardless of the input status when VDD is rising but the level is below the UVLO threshold. The hysteresis prevents output bouncing caused by the noise impact on the power supply. During power up, the driver output remains low until the VDD voltage reaches the UVLO threshold. The magnitude of the OUT signal rises with VDD till VDD steady state reached.

Figure 8. GBI7254 Output Vs VDD

# 9.4 Input Stage

The GBI7254 input is compatible on TTL logic which is independent of the VDD supply voltage. The typical threshold is 2.1-V (high) and 1.0-V (low), which make the device easily driven by PWM control signals derived from 3.3-V and 5-V digital power-controller devices. The device features wider hysteresis compared to typical threshold of 0.5V which offers enhanced noise immunity. It also implements tight control of the input threshold voltage that ensures stable operation across temperature. The low input capacitance on the input pins increases switching speed and reduces the propagation delay.

#### 9.5 Enable Function

The GBI7254 features dedicated enable pins ENA and ENB for independent external control of each channel. The device will be enabled when the Enable signal voltage level is higher than its Enable logic high threshold, and it will be disabled when the Enable signal is lower than its Enable logic low threshold.

The enable input is compatible with TTL and CMOS logic adaptive with 3.3V or 5V microcontrollers. The GBI7254 enables all functions and starts gate driver operation when the EN input voltage is higher than the EN threshold (typical 2.1V). The enable pins are pulled up to the VDD internally with pull up resistors, thus allow the device enabled in the default state. In application without any enable feature, the enable pins could be left floating or disconnected.

# 9.6 Device Logic

The GBI7254 operates properly with different logic combination. The device logic is easily checked with following device logic table.

Table 2. GBI7254 Device Logic

| ENA      | ENB      | INA      | INB      | OUTA | OUTB |

|----------|----------|----------|----------|------|------|

| Н        | Н        | L        | L        | L    | L    |

| Н        | Н        | L        | Н        | L    | Н    |

| Н        | Н        | Н        | L        | Н    | L    |

| Н        | Н        | Н        | Н        | Ξ    | Н    |

| L        | L        | Any      | Any      | L    | L    |

| Any      | Any      | Floating | Floating |      | L    |

| Floating | Floating | L        | L        | L    | L    |

| Floating | Floating | L        | Н        | L    | Н    |

| Floating | Floating | Н        | L        | Н    | L    |

| Floating | Floating | Н        | Н        | Н    | Н    |

### 10 APPLICATION INFORMATION

#### **Typical Application**

**Figure 9. Typical Application Diagram**

## **Driver Power Dissipation**

Generally, the power dissipation depends on the gate charge required of the power device (Qg), switching frequency, and use of external gate resistors. The GBI7254 is designed with very low quiescent currents and internal logic to eliminate any output-stage shoot-through.

The power loss of GBI7254 caused by pure capacitive load is:

$$P_G = C_{Load} * V_{DD}^2 * f_{SW} \tag{1}$$

Where

- V<sub>DD</sub> is supply voltage

- C<sub>Load</sub> is the output capacitance

- f<sub>SW</sub> is the switching frequency

This equation (1) is also able to be adopted to calculate the switching load of power MOSFET, where gate charge Qg determines the capacitor charges.

$$Q_a = C_{LOAD} \times V_{DD} \tag{2}$$

Normally power device Manufacturers provide specifications with the typical and maximum Qg, in nC, to switch the device under specified conditions.

$$P_G = Q_g * V_{DD} * f_{SW} \tag{3}$$

#### Where

- Q<sub>g</sub> is the gate charge of the power device

- f<sub>SW</sub> is the switching frequency

- V<sub>DD</sub> is the supply voltage

Sometimes, circuit designers put a resistor R<sub>GATE</sub> between the driver output pin and the gate terminal of power device to slow down the power device transition. The power dissipation of the driver shows as below:

$$P_{G} = \frac{1}{2} * Q_{g} * V_{DD} * f_{SW} * \left( \frac{R_{L}}{R_{L} + R_{GATE}} + \frac{R_{H}}{R_{H} + R_{GATE}} \right)$$

(3)

#### Where

- R<sub>H</sub> is the equivalent pull up resistance of GBI7254

- R<sub>L</sub> is the pull-down resistance of GBI7254

- RGATE is the gate resistance between driver output and gate of power device.

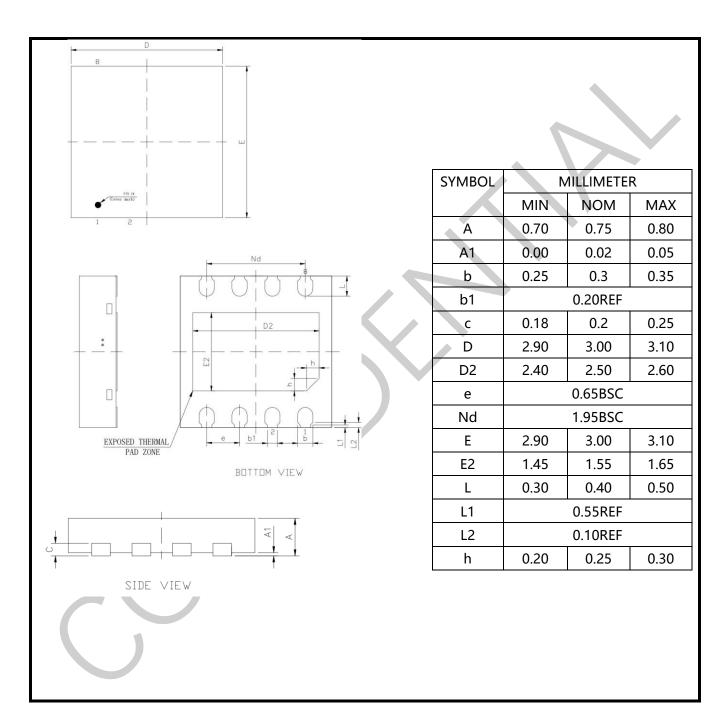

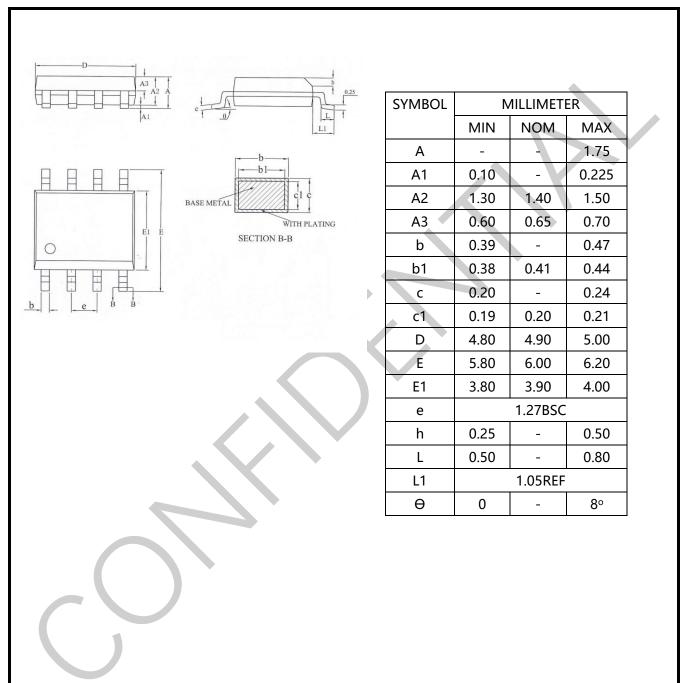

# PACKAGE INFORMATION-SOIC-8L

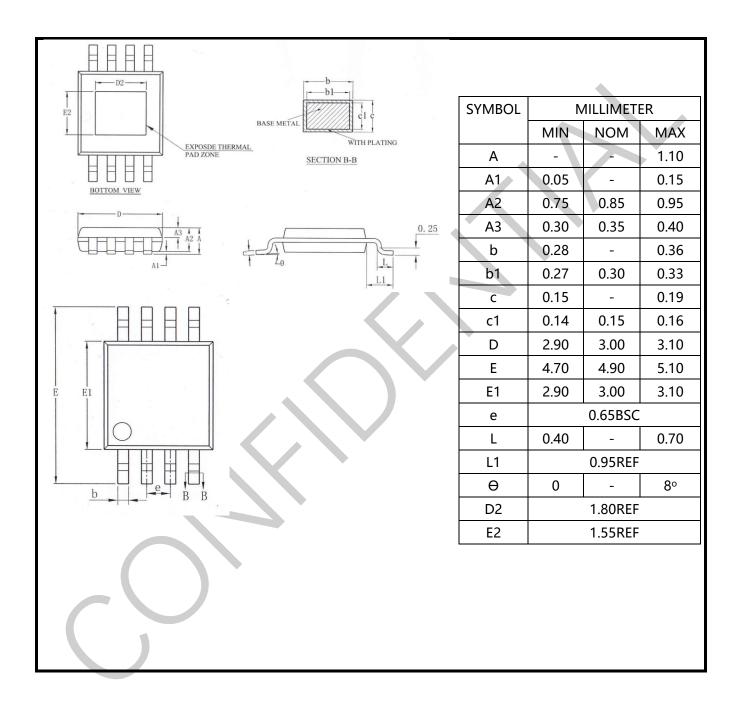

## PACKAGE INFORMATION-EMSOP-8L

## PACKAGE INFORMATION-DFN3\*3-8L