# 128K x 36, 3.3V Synchronous *IDT71V546S* SRAM with ZBT™ Feature Burst Counter and Pipelined Outputs

### **Features**

- ◆ 128K x 36 memory configuration, pipelined outputs

- Supports high performance system speed 133 MHz (4.2 ns Clock-to-Data Access)

- ▼ ZBT<sup>TM</sup> Feature No dead cycles between write and read cycles

- Internally synchronized registered outputs eliminate the need to control OE

- ◆ Single R/W (READ/WRITE) control pin

- Positive clock-edge triggered address, data, and control signal registers for fully pipelined applications

- 4-word burst capability (interleaved or linear)

- ◆ Individual byte write (BW1 BW4) control (May tie active)

- Three chip enables for simple depth expansion

- Single 3.3V power supply (±5%)

- Packaged in a JEDEC standard 100-pin TQFP package

- Green parts available, see Ordering Information

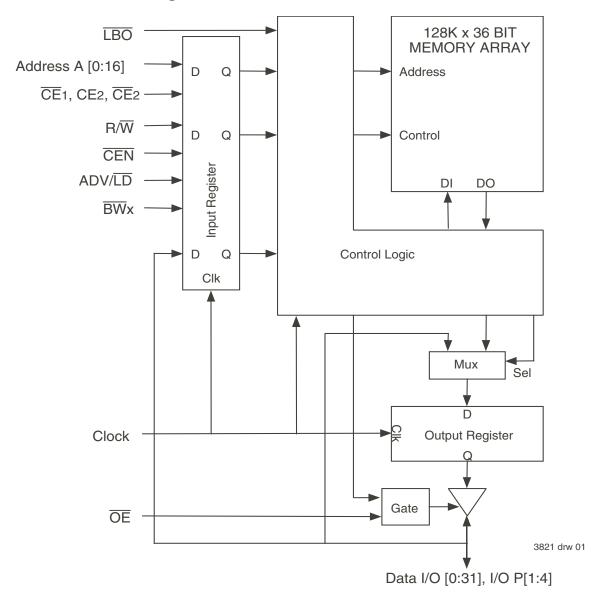

# Functional Block Diagram

ZBT and Zero Bus Turnaround are trademarks of Integrated Device Technology, Inc. and the architecture is supported by Micron Technology and Motorola Inc.

AUGUST 2017

### Description

The IDT71V546 is a 3.3V high-speed 4,718,592-bit (4.5 Megabit) synchronous SRAM organized as 128K x 36 bits. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Thus it has been given the name  $ZBT^{\text{TM}}$ , or Zero Bus Turn-around.

Address and control signals are applied to the SRAM during one clock cycle, and two cycles later its associated data cycle occurs, be it read or write.

The IDT71V546 contains data I/O, address and control signal registers. Output enable is the only asynchronous signal and can be used to disable the outputs at any given time.

A Clock Enable ( $\overline{\text{CEN}}$ ) pin allows operation of the IDT71V546 to be suspended as long as necessary. All synchronous inputs are ignored when  $\overline{\text{CEN}}$  is high and the internal device registers will hold their previous values.

There are three chip enable pins  $(\overline{CE}_1, CE_2, \overline{CE}_2)$  that allow the user to deselect the device when desired. If any one of these three is not active when ADV/ $\overline{LD}$  is low, no new memory operation can be initiated and any burst that was in progress is stopped. However, any pending data transfers (reads or writes) will be completed. The data bus will tri-state two cycles after the chip is deselected or a write initiated.

The IDT71V546 has an on-chip burst counter. In the burst mode, the IDT71V546 can provide four cycles of data for a single address presented to the SRAM. The order of the burst sequence is defined by the  $\overline{LBO}$  input pin. The  $\overline{LBO}$  pin selects between linear and interleaved burst sequence. The ADV/ $\overline{LD}$  signal is used to load a new external address (ADV/ $\overline{LD}$  = LOW) or increment the internal burst counter (ADV/ $\overline{LD}$  = HIGH).

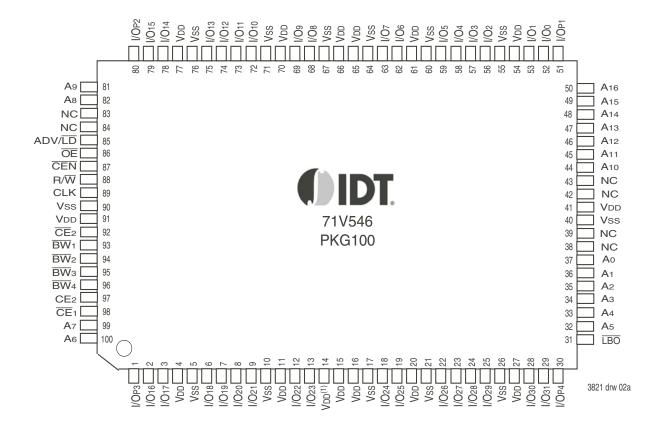

The IDT71V546 SRAM utilizes a high-performance, high-volume 3.3V CMOS process, and is packaged in a JEDEC standard 14mm x 20mm 100-pin thin plastic quad flatpack (TQFP) for high board density.

### Pin Description Summary

| A0 - A16                                                                      | Address Inputs                           | Input  | Synchronous  |

|-------------------------------------------------------------------------------|------------------------------------------|--------|--------------|

| ŌĒ1, CE2, ŌĒ2                                                                 | Three Chip Enables                       | Input  | Synchronous  |

| ŌĒ                                                                            | Output Enable                            | Input  | Asynchronous |

| R/W                                                                           | Read/Write Signal                        | Input  | Synchronous  |

| CEN                                                                           | Clock Enable                             | Input  | Synchronous  |

| $\overline{BW}_1$ , $\overline{BW}_2$ , $\overline{BW}_3$ , $\overline{BW}_4$ | Individual Byte Write Selects            | Input  | Synchronous  |

| CLK                                                                           | Clock                                    | Input  | N/A          |

| ADV/LD                                                                        | Advance Burst Address / Load New Address | Input  | Synchronous  |

| LBO                                                                           | Linear / Interleaved Burst Order         | Input  | Static       |

| I/O0 - I/O31, I/OP1 - I/OP4                                                   | Data Input/Output                        | l/O    | Synchronous  |

| VDD                                                                           | 3.3V Power                               | Supply | Static       |

| Vss                                                                           | Ground                                   | Supply | Static       |

# Pin Definitions<sup>(1)</sup>

| Symbol                    | Pin Function                     | I/O | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|---------------------------|----------------------------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A0 - A16                  | Address Inputs                   | I   | N/A    | Synchronous Address inputs. The address register is triggered by a combination of the rising edge of CLK and ADV/LD Low, CEN Low and true chip enables.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| ADV/LD                    | Address/Load                     | I   | N/A    | ADV/LD is a synchronous input that is used to load the internal registers with new address and control when it is sampled low at the rising edge of clock with the chip selected. When ADV/LD is low with the chip deselected, any burst in progress is terminated. When ADV/LD is sampled high then the internal burst counter is advanced for any burst that was in progress. The external addresses are ignored when ADV/LD is sampled high.                                                                    |  |  |  |

| R/W                       | Read/Write                       | I   | N/A    | $R\overline{W}$ signal is a synchronous input that identified whether the current load cycle initiated is a Read or Write access to the memory array. The data bus activity for the current cycle takes place two clock cycles later.                                                                                                                                                                                                                                                                              |  |  |  |

| CEN                       | Clock Enable                     | I   | LOW    | Synchronous Clock Enable Input. When $\overline{\text{CEN}}$ is sampled high, all other synchronous <u>inputs</u> , including clock are ignored and outputs remain unchanged. The effect of $\overline{\text{CEN}}$ sampled high on the device outputs is as if the low to high clock transition did not occur. For normal operation, $\overline{\text{CEN}}$ must be sampled low at rising edge of clock.                                                                                                         |  |  |  |

| BW1 - BW4                 | Individual Byte<br>Write Enables | I   | LOW    | Synchronous byte write enables. Enable 9-bit byte has its own active low byte write enable. On load write cycles (When R/W and ADV/LD are sampled low) the appropriate byte write signal (BWi - BW4) must be valid. The byte write signal must also be valid on each cycle of a burst write. Byte Write signals are ignored when R/W is sampled high. The appropriate byte(s) of data are written into the device two cycles later. BWi - BW4 can all be tied low if always doing write to the entire 36-bit word. |  |  |  |

| ŌĒ₁, ŌĒ₂                  | Chip Enables                     | ı   | LOW    | Synchronous active low chip enable. $\overline{CE}_1$ and $\overline{CE}_2$ are used with CE2 to enable the IDI771V546. $\overline{(CE}_1$ or $\overline{CE}_2$ sampled high or CE2 sampled low) and ADV/ $\overline{LD}$ low at the rising edge of clock, initiates a deselect cycle. the ZBTTM has a two cycle deselect, i.e., the data bus will tri-state two clock cycles after deselect is initiated.                                                                                                         |  |  |  |

| CE2                       | Chip Enable                      | I   | HIGH   | Synchronout active high chip enable. CE2 is used with $\overline{\text{CE}}_1$ and $\overline{\text{CE}}_2$ to enable the chip. CE2 has inverted polarity but otherwise identical to $\overline{\text{CE}}_1$ and $\overline{\text{CE}}_2$ .                                                                                                                                                                                                                                                                       |  |  |  |

| CLK                       | Clock                            | I   | N/A    | This is the clock input to the IDT71V546. Except for $\overline{\text{OE}}$ , all timing references for the device are made with respect to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| VO0 - VO31<br>VOP1 - VOP4 | Data Input/Output                | 1/0 | N/A    | Synchronous data input/output (I/O) pins. Both the data input path and data output path are registered and triggered by the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| LBO                       | Linear Burst<br>Order            | I   | LOW    | Burst order selection input. When $\overline{\text{LBO}}$ is high the Interleaved burst sequence is selected. When $\overline{\text{LBO}}$ is low the Linear burst sequence is selected. $\overline{\text{LBO}}$ is a static DC input.                                                                                                                                                                                                                                                                             |  |  |  |

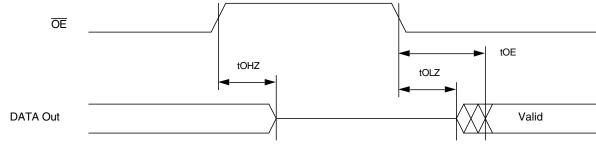

| ŌĒ                        | Output Enable                    | I   | LOW    | Asynchronous output enable. $\overline{OE}$ must be low to read data from the 71V546. When $\overline{OE}$ is high the I/O pins are in a high-impedance state. $\overline{OE}$ does not need to be actively controlled for read and write cycles. In normal operation, $\overline{OE}$ can be tied low.                                                                                                                                                                                                            |  |  |  |

| VDD                       | Power Supply                     | N/A | N/A    | 3.3V power supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Vss                       | Ground                           | N/A | N/A    | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

NOTE:

1. All synchronous inputs must meet specified setup and hold times with respect to CLK.

# Pin Configuration — 128K X 36

# 100 TQFP Top View

### NOTE:

1. Pin 14 does not have to be connected directly to VDD as long as the input voltage is  $\geq$  VIH.

# Absolute Maximum Ratings(1)

| Symbol               | Rating                                         | Commercial & Industrial Values | Unit |

|----------------------|------------------------------------------------|--------------------------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with Respect to GND           | -0.5 to +4.6                   | V    |

| VTERM <sup>(3)</sup> | Terminal Voltage with Respect to GND           | -0.5 to VDD+0.5                | V    |

| TA <sup>(4)</sup>    | Commercial<br>Operating Ambient<br>Temperature | 0 to +70                       | °C   |

| IA <sup>vy</sup>     | Industrial<br>Operating Ambient<br>Temperature | -40 to +85                     | °C   |

| TBIAS                | Temperature Under Bias                         | -55 to +125                    | °C   |

| Tstg                 | Storage Temperature                            | -55 to +125                    | °C   |

| Рт                   | Power Dissipation                              | 2.0                            | W    |

| Іоит                 | DC Output Current                              | 50                             | mA   |

### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only

and functional operation of the device at these or any other conditions above

those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may

affect reliability.

- 2. VDD and Input terminals only.

- 3. I/O terminals.

- 4. During production testing, the case temperature equals the ambient temperature.

# Recommended DC Operating Conditions

| Symbol                         | Parameter                   | Min.                | Тур. | Max.                                | Unit |

|--------------------------------|-----------------------------|---------------------|------|-------------------------------------|------|

| V <sub>DD</sub> <sup>(3)</sup> | Supply Voltage              | 3.135               | 3.3  | 3.465                               | ٧    |

| Vss                            | Ground                      | 0                   | 0    | 0                                   | V    |

| Vн                             | Input High Voltage - Inputs | 2.0                 | _    | 4.6                                 | V    |

| Vн                             | Input High Voltage - I/O    | 2.0                 | _    | V <sub>DD</sub> +0.3 <sup>(2)</sup> | V    |

| VIL                            | Input Low Voltage           | -0.5 <sup>(1)</sup> |      | 0.8                                 | V    |

### NOTES:

3821 tbl 04

- 1.  $V_{IL}$  (min.) = -1.0V for pulse width less than tcyc/2, once per cycle.

- 2. ViH (max.) = +6.0V for pulse width less than tcyc/2, once per cycle.

- 3. VDD needs to be ramped up smoothly to the operating level. If there are any glitches on VDD that cause the voltage level to drop below 2.0 volts then the device needs to be reset by holding VDD to 0.0 volts for a minimum of 100 ms.

# Recommended Operating Temperature and Supply Voltage

|            |                                       | 1 2 |             |

|------------|---------------------------------------|-----|-------------|

| Grade      | Ambient<br>Temperature <sup>(1)</sup> | Vss | <b>V</b> DD |

| Commercial | 0°C to +70°C                          | 0V  | 3.3V±5%     |

| Industrial | -40°C to +85°C                        | 0V  | 3.3V±5%     |

### 3821 tbl 03

NOTES:

1. During production testing, the case temperature equals the ambient temperature.

# 100 TQFP Capacitance

$(TA = +25^{\circ}C, f = 1.0MHz, TQFP package)$

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| Cin    | Input Capacitance        | VIN = 3dV  | 5    | pF   |

| Ci/o   | I/O Capacitance          | Vout = 3dV | 7    | pF   |

### 3821 tbl 06

### NOTE:

1. This parameter is guaranteed by device characterization, but not production tested.

## Synchronous Truth Table<sup>(1)</sup>

| CEN | R/W | Chip <sup>(5)</sup><br>Enable | ADV/LD | B₩x   | ADDRESS<br>USED | PREVIOUIS CYCLE            | CURRENT CYCLE                                         | I/O<br>(2 cycles later) |

|-----|-----|-------------------------------|--------|-------|-----------------|----------------------------|-------------------------------------------------------|-------------------------|

| L   | L   | Select                        | L      | Valid | External        | X                          | LOAD WRITE                                            | D <sup>(7)</sup>        |

| L   | Н   | Select                        | L      | Χ     | External        | Х                          | LOAD READ                                             | Q <sup>(7)</sup>        |

| L   | Х   | Х                             | Н      | Valid | Internal        | LOAD WRITE/<br>BURST WRITE | BURST WRITE<br>(Advance Burst Counter) <sup>(2)</sup> | D <sub>(2)</sub>        |

| L   | Х   | Х                             | Н      | Х     | Internal        | LOAD READ/<br>BURST READ   | BURST READ<br>(Advance Burst Counter) <sup>(2)</sup>  | O <sub>(1)</sub>        |

| L   | Χ   | Deselect                      | L      | Х     | Х               | Х                          | DESELECT or STOP <sup>(3)</sup>                       | HiZ                     |

| L   | Χ   | Х                             | Н      | Х     | Х               | DESELECT / NOOP            | NOOP                                                  | HiZ                     |

| Н   | Х   | Х                             | Χ      | Χ     | Χ               | Х                          | SUSPEND <sup>(4)</sup>                                | Previous Value          |

NOTES:

3821 tbl 07

- 1.  $L = V_{IL}$ ,  $H = V_{IH}$ , X = Don't Care.

- 2. When ADV/LD signal is sampled high, the internal burst counter is incremented. The R/W signal is ignored when the counter is advanced. Therefore the nature of the burst cycle (Read or Write) is determined by the status of the  $R/\overline{W}$  signal when the first address is loaded at the beginning of the burst cycle.

3. Deselect cycle is initiated when either  $(\overline{CE}1, \text{ or } \overline{CE}2)$  is sampled high or  $\overline{CE}2$  is sampled low) and  $\overline{ADV/LD}$  is sampled low at rising edge of clock. The data bus will

- tri-state two cycles after deselect is initiated.

- 4. When CEN is sampled high at the rising edge of clock, that clock edge is blocked from propagating through the part. The state of all the internal registers and the I/Os remains unchanged.

- 5. To select the chip requires  $\overline{CE}_1 = L$ ,  $\overline{CE}_2 = L$ ,  $\overline{CE}_2 = L$  on these chip enables. Chip is deselected if either one of the chip enables is false.

- 6. Device Outputs are ensured to be in High-Z after the first rising edge of clock upon power-up.

- 7. Q Data read from the device, D data written to the device.

### Partial Truth Table for Writes(1)

| Operation                                                    | R/W | <b>BW</b> ₁ | <del>BW</del> 2 | <b>BW</b> ₃ | BW <sub>4</sub> |

|--------------------------------------------------------------|-----|-------------|-----------------|-------------|-----------------|

| READ                                                         | Н   | X           | X               | X           | X               |

| WRITE ALL BYTES                                              | L   | L           | L               | L           | L               |

| WRITE BYTE 1 (I/O [0:7], I/Op1) <sup>(2)</sup>               | L   | L           | Н               | Н           | Н               |

| WRITE BYTE 2 (I/O [8:15], I/O <sub>P2</sub> ) <sup>(2)</sup> | L   | Н           | L               | Н           | Н               |

| WRITE BYTE 3 (I/O [16:23], I/Op3) <sup>(2)</sup>             | L   | Н           | Н               | L           | Н               |

| WRITE BYTE 4 (I/O [24:31], I/OP4) <sup>(2)</sup>             | L   | Н           | Н               | Н           | L               |

| NO WRITE                                                     | L   | Н           | Н               | Н           | Н               |

- NOTES:

- 1.  $L = V_{IL}$ ,  $H = V_{IH}$ , X = Don't Care.

- 2. Multiple bytes may be selected during the same cycle.

Interleaved Burst Sequence Table (**LBO**=VDD)

|                               | Se         |    | S | Seque | ence 2 | Sequence 3 Sequence 4 |    |    | ience 4 |

|-------------------------------|------------|----|---|-------|--------|-----------------------|----|----|---------|

|                               | <b>A</b> 1 | A0 |   | A1    | A0     | A1                    | A0 | A1 | A0      |

| First Address                 | 0          | 0  |   | 0     | 1      | 1                     | 0  | 1  | 1       |

| Second Address                | 0          | 1  |   | 0     | 0      | 1                     | 1  | 1  | 0       |

| Third Address                 | 1          | 0  |   | 1     | 1      | 0                     | 0  | 0  | 1       |

| Fourth Address <sup>(1)</sup> | 1          | 1  |   | 1     | 0      | 0                     | 1  | 0  | 0       |

### NOTE:

3821 tbl 09

Linear Burst Sequence Table (**LBO**=Vss)

|                               | Sequence 1 | Sequence 2 | Sequence 3 | Sequence 4 |  |

|-------------------------------|------------|------------|------------|------------|--|

|                               | A1 A0      | A1 A0      | A1 A0      | A1 A0      |  |

| First Address                 | 0 0        | 0 1        | 1 0        | 1 1        |  |

| Second Address                | 0 1        | 1 0        | 1 1        | 0 0        |  |

| Third Address                 | 1 0        | 1 1        | 0 0        | 0 1        |  |

| Fourth Address <sup>(1)</sup> | 1 1        | 0 0        | 0 1        | 1 0        |  |

### NOTE:

3821 tbl 10

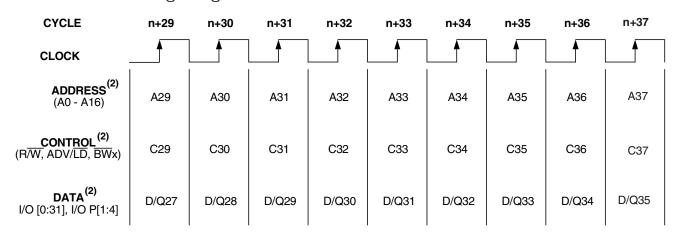

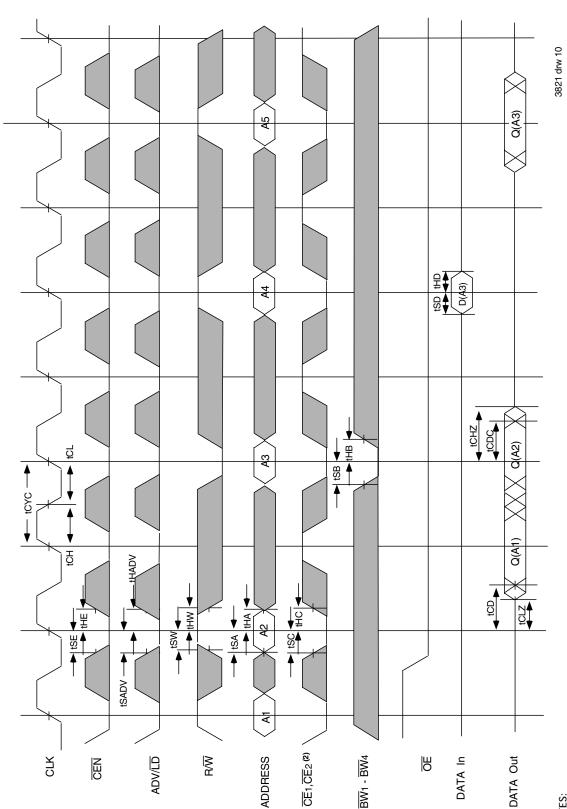

# Functional Timing Diagram<sup>(1)</sup>

### NOTES:

3821 drw 03

2. All Address, Control and Data\_in are only required to meet set-up and hold time with respect to the rising edge of clock. Data\_Out is valid after a clock-to-data delay from the rising edge of clock.

<sup>1.</sup> Upon completion of the Burst sequence the counter wraps around to its initial state and continues counting.

<sup>1.</sup> Upon completion of the Burst sequence the counter wraps around to its initial state and continues counting

<sup>1.</sup> This assumes  $\overline{\text{CEN}}$ ,  $\overline{\text{CE}}$ 1, CE2,  $\overline{\text{CE}}$ 2 are all true.

# Device Operation - Showing Mixed Load, Burst, Deselect and NOOP Cycles<sup>(2)</sup>

| Cycle | Address    | R/W | ADV/LD | <u>C</u> E <sup>(1)</sup> | CEN | B₩x | ŌĒ | I/O  | Comments         |

|-------|------------|-----|--------|---------------------------|-----|-----|----|------|------------------|

| n     | A0         | Н   | L      | L                         | L   | Х   | Х  | Х    | Load read        |

| n+1   | Х          | Х   | Н      | Х                         | L   | Х   | Χ  | Х    | Burst read       |

| n+2   | A1         | Н   | L      | L                         | L   | Х   | L  | Q0   | Load read        |

| n+3   | Х          | Х   | L      | Н                         | L   | Х   | L  | Q0+1 | Deselect or STOP |

| n+4   | Х          | Х   | Н      | Х                         | L   | Х   | L  | Q1   | NOOP             |

| n+5   | A2         | Н   | L      | ┙                         | L   | Х   | Χ  | Z    | Load read        |

| n+6   | Х          | Х   | Н      | Х                         | L   | Х   | Χ  | Z    | Burst read       |

| n+7   | Х          | Х   | L      | Н                         | L   | Х   | L  | Q2   | Deselect or STOP |

| n+8   | A3         | L   | L      | L                         | L   | L   | L  | Q2+1 | Load write       |

| n+9   | Х          | Х   | Н      | Х                         | L   | L   | Χ  | Z    | Burst write      |

| n+10  | A4         | L   | L      | L                         | L   | L   | Χ  | D3   | Load write       |

| n+11  | Х          | Х   | L      | Н                         | L   | Х   | Χ  | D3+1 | Deselect or STOP |

| n+12  | Х          | Х   | Н      | Х                         | L   | Х   | Χ  | D4   | NOOP             |

| n+13  | <b>A</b> 5 | L   | L      | L                         | L   | L   | Х  | Z    | Load write       |

| n+14  | A6         | Н   | L      | L                         | L   | Х   | Χ  | Z    | Load read        |

| n+15  | A7         | L   | L      | ┙                         | L   | L   | Χ  | D5   | Load write       |

| n+16  | Х          | Х   | Н      | Χ                         | L   | L   | L  | Q6   | Burst write      |

| n+17  | A8         | Н   | L      | L                         | L   | Х   | Х  | D7   | Load read        |

| n+18  | Х          | Х   | Н      | Χ                         | L   | Х   | Χ  | D7+1 | Burst read       |

| n+19  | А9         | L   | L      | L                         | L   | L   | L  | Q8   | Load write       |

NOTES

1.  $\overline{CE}$  = L is defined as  $\overline{CE}$ 1 = L,  $\overline{CE}$ 2 = L and CE2 = H. CE = H is defined as  $\overline{CE}$ 1 = H,  $\overline{CE}$ 2 = H or CE2 = L.

<sup>2.</sup> H = High; L = Low; X = Don't Care; Z = High Impedance.

# Read Operation<sup>(1)</sup>

| Cycle | Address | R/W | ADV/LD | CE(2) | CEN | B₩x | ŌĒ | I/O | Comments                        |

|-------|---------|-----|--------|-------|-----|-----|----|-----|---------------------------------|

| n     | A0      | Н   | L      | L     | L   | Х   | Х  | Х   | Address and Control meet setup  |

| n+1   | Х       | Х   | Х      | Х     | L   | Х   | Х  | Х   | Clock Setup Valid               |

| n+2   | Х       | X   | X      | Χ     | Χ   | X   | L  | Q0  | Contents of Address A0 Read Out |

### NOTES:

3821 tbl 12

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance.

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}1 = L$ ,  $\overline{CE}2 = L$  and  $\overline{CE}2 = H$ .  $\overline{CE} = H$  is defined as  $\overline{CE}1 = H$ ,  $\overline{CE}2 = H$  or  $\overline{CE}2 = L$ .

# Burst Read Operation(1)

| Cycle | Address | R/₩ | ADV/LD | CE(2) | CEN | ₩x | ŌĒ | I/O  | Comments                                               |

|-------|---------|-----|--------|-------|-----|----|----|------|--------------------------------------------------------|

| n     | A0      | Н   | L      | L     | L   | Х  | Χ  | Х    | Address and Control meet setup                         |

| n+1   | Х       | Х   | Н      | Х     | L   | Х  | Χ  | Х    | Clock Setup Valid, Advance Counter                     |

| n+2   | Х       | Х   | Н      | Х     | L   | Х  | L  | Q0   | Address A0 Read Out, Inc. Count                        |

| n+3   | Х       | Х   | Н      | Х     | L   | Х  | L  | Q0+1 | Address A <sub>0+1</sub> Read Out, Inc. Count          |

| n+4   | Х       | Х   | Н      | Х     | L   | Х  | L  | Q0+2 | Address A <sub>0+2</sub> Read Out, Inc. Count          |

| n+5   | A1      | Н   | L      | L     | L   | Х  | L  | Q0+3 | Address A <sub>0+3</sub> Read Out, Load A1             |

| n+6   | Х       | Х   | Н      | Х     | L   | Х  | L  | Q0   | Address A0 Read Out, Inc. Count                        |

| n+7   | Х       | Х   | Н      | Х     | L   | Х  | L  | Q1   | Address A1 Read Out, Inc. Count                        |

| n+8   | A2      | Н   | L      | L     | L   | Х  | L  | Q1+1 | Address A <sub>1+1</sub> Read Out, Load A <sub>2</sub> |

- H = High; L = Low; X = Don't Care; Z = High Impedance..

\overline{CE} = L is defined as \overline{CE}1 = L, \overline{CE}2 = L and CE2 = H. CE = H is defined as \overline{CE}1 = H, \overline{CE}2 = H or CE2 = L.

# Write Operation<sup>(1)</sup>

| Cycle | Address | R/W | ADV/LD | CE <sup>(2)</sup> | CEN | B₩x | ŌĒ | I/O | Comments                       |

|-------|---------|-----|--------|-------------------|-----|-----|----|-----|--------------------------------|

| n     | A0      | L   | L      | L                 | L   | L   | Χ  | Х   | Address and Control meet setup |

| n+1   | Х       | Х   | Х      | Х                 | L   | Х   | Χ  | Х   | Clock Setup Valid              |

| n+2   | Χ       | Х   | Х      | Χ                 | L   | Χ   | Χ  | D0  | Write to Address A0            |

NOTES:

3821 tbl 14

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance.

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}1 = L$ ,  $\overline{CE}2 = L$  and  $\overline{CE}2 = H$ .  $\overline{CE} = H$  is defined as  $\overline{CE}1 = H$ ,  $\overline{CE}2 = H$  or  $\overline{CE}2 = L$ .

# Burst Write Operation(1)

| Cycle | Address | R/W | ADV/LD | CE(2) | CEN | ₩x | ŌĒ | I/O  | Comments                                            |

|-------|---------|-----|--------|-------|-----|----|----|------|-----------------------------------------------------|

| n     | A0      | L   | L      | L     | L   | L  | Χ  | Х    | Address and Control meet setup                      |

| n+1   | Χ       | Х   | Н      | Χ     | L   | L  | Χ  | Х    | Clock Setup Valid, Inc. Count                       |

| n+2   | Х       | Х   | Н      | Χ     | L   | L  | Χ  | D0   | Address A0 Write, Inc. Count                        |

| n+3   | Х       | Х   | Н      | Χ     | L   | L  | Χ  | D0+1 | Address A <sub>0+1</sub> Write, Inc. Count          |

| n+4   | Х       | Х   | Н      | Х     | L   | L  | Χ  | D0+2 | Address A <sub>0+2</sub> Write, Inc. Count          |

| n+5   | A1      | L   | L      | L     | L   | L  | Х  | D0+3 | Address A <sub>0+3</sub> Write, Load A <sub>1</sub> |

| n+6   | Х       | Х   | Н      | Χ     | L   | L  | Χ  | D0   | Address A0 Write, Inc. Count                        |

| n+7   | Х       | Х   | Н      | Χ     | L   | L  | Χ  | D1   | Address A1 Write, Inc. Count                        |

| n+8   | A2      | L   | L      | L     | L   | L  | Χ  | D1+1 | Address A <sub>1+1</sub> Write, Load A <sub>2</sub> |

- 1. H = High; L = Low; X = Don't Care; ? = Don't Know; Z = High Impedance.2.  $\overline{CE} = L$  is defined as  $\overline{CE}1 = L$ ,  $\overline{CE}2 = L$  and  $\overline{CE}2 = L$  and  $\overline{CE}2 = L$  is defined as  $\overline{CE}1 = L$ .

# Read Operation With Clock Enable Used(1)

| Cycle | Address | R/W | ADV/LD | CE <sup>(2)</sup> | CEN | B₩x | ŌĒ | I/O | Comments                             |

|-------|---------|-----|--------|-------------------|-----|-----|----|-----|--------------------------------------|

| n     | A0      | Н   | L      | L                 | L   | Χ   | Χ  | Χ   | Address and Control meet setup       |

| n+1   | Х       | Х   | Х      | Х                 | Н   | Χ   | Х  | Х   | Clock n+1 Ignored                    |

| n+2   | A1      | Н   | L      | L                 | L   | Х   | Х  | Х   | Clock Valid                          |

| n+3   | Х       | Х   | Х      | Χ                 | Н   | Χ   | L  | Q0  | Clock Ignored. Data Q0 is on the bus |

| n+4   | Х       | Х   | Х      | Χ                 | Н   | Χ   | L  | Q0  | Clock Ignored. Data Q0 is on the bus |

| n+5   | A2      | Н   | L      | L                 | L   | Χ   | L  | Q0  | Address A0 Read out (but trans.)     |

| n+6   | А3      | Н   | L      | L                 | L   | Χ   | L  | Q1  | Address A1 Read out (bus trans.)     |

| n+7   | A4      | Н   | L      | L                 | L   | Х   | L  | Q2  | Address A2 Read out (bus trans.)     |

### NOTES:

3821 tbl 16

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance.

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}1 = L$ ,  $\overline{CE}2 = L$  and  $\overline{CE}2 = H$ .  $\overline{CE} = H$  is defined as  $\overline{CE}1 = H$ ,  $\overline{CE}2 = H$  or  $\overline{CE}2 = L$ .

# Write Operation with Clock Enable Used(1)

| Cycle | Address | R/W | ADV/LD | CE(2) | CEN | ₩x | ŌĒ | I/O | Comments                       |

|-------|---------|-----|--------|-------|-----|----|----|-----|--------------------------------|

| n     | A0      | L   | L      | L     | L   | L  | Х  | Х   | Address and Control meet setup |

| n+1   | Х       | Χ   | Х      | Х     | Н   | Х  | Χ  | Х   | Clock n+1 Ignored              |

| n+2   | A1      | L   | L      | L     | L   | L  | Х  | Х   | Clock Valid                    |

| n+3   | Х       | Χ   | Х      | Х     | Н   | Х  | Х  | Х   | Clock Ignored                  |

| n+4   | Х       | Х   | Х      | Х     | Н   | Х  | Х  | Х   | Clock Ignored                  |

| n+5   | A2      | L   | L      | L     | L   | L  | Х  | D0  | Write data D0                  |

| n+6   | A3      | L   | L      | L     | L   | L  | Χ  | D1  | Write data D1                  |

| n+7   | A4      | L   | L      | L     | L   | L  | Χ  | D2  | Write data D2                  |

### 3821 tbl 17

### NOTES:

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance.2.  $\overline{CE} = L$  is defined as  $\overline{CE}1 = L$ ,  $\overline{CE}2 = L$  and CE2 = H.  $\overline{CE} = H$  is defined as  $\overline{CE}1 = H$ ,  $\overline{CE}2 = H$  or CE2 = L.

# Read Operation With Chip Enable Used(1)

| Cycle | Address | R/W | ADV/LD | <u>C</u> E <sup>(1)</sup> | CEN | B₩x | ŌĒ | I/O | Comments                        |

|-------|---------|-----|--------|---------------------------|-----|-----|----|-----|---------------------------------|

| n     | Х       | Х   | L      | Н                         | L   | Х   | Χ  | ?   | Deselected                      |

| n+1   | Х       | Х   | L      | Н                         | L   | Х   | Χ  | ?   | Deselected                      |

| n+2   | A0      | Н   | L      | L                         | L   | Х   | Х  | Z   | Address and Control meet setup  |

| n+3   | Х       | Х   | L      | Н                         | L   | Х   | Х  | Z   | Deselected or STOP              |

| n+4   | A1      | Н   | L      | L                         | L   | Х   | L  | Q0  | Address A0 read out. Load A1    |

| n+5   | Х       | Х   | L      | Н                         | L   | Χ   | Χ  | Z   | Deselected or STOP              |

| n+6   | Х       | Х   | L      | Н                         | L   | Х   | L  | Q1  | Address A1 Read out. Deselected |

| n+7   | A2      | Н   | L      | L                         | L   | Х   | Х  | Z   | Address and Control meet setup  |

| n+8   | Х       | Х   | L      | Н                         | L   | Χ   | Χ  | Z   | Deselected or STOP              |

| n+9   | Х       | Х   | L      | Н                         | L   | Χ   | L  | Q2  | Address A2 read out. Deselected |

NOTES: 3821 tbl 18

- 1. H = High; L = Low; X = Don't Care; ? = Don't Know; Z = High Impedance.

- 2.  $\overline{CE}$  = L is defined as  $\overline{CE}$ 1 = L,  $\overline{CE}$ 2 = L and CE2 = H.  $\overline{CE}$  = H is defined as  $\overline{CE}$ 1 = H,  $\overline{CE}$ 2 = H or CE2 = L.

- 3. Device Outputs are ensured to be in High-Z after the first rising edge of clock upon power-up.

# Write Operation With Chip Enable Used(1)

| Cycle | Address | R/W | ADV/LD | <u>C</u> E <sup>(1)</sup> | CEN | B₩x | ŌĒ | I/O | Comments                        |

|-------|---------|-----|--------|---------------------------|-----|-----|----|-----|---------------------------------|

| n     | Х       | Χ   | L      | Н                         | L   | Χ   | Х  | ?   | Deselected                      |

| n+1   | Х       | Х   | L      | Н                         | L   | Х   | Х  | ?   | Deselected                      |

| n+2   | A0      | L   | L      | L                         | L   | L   | Х  | Z   | Address and Control meet setup  |

| n+3   | Х       | Χ   | L      | Н                         | L   | Χ   | Х  | Z   | Deselected or STOP              |

| n+4   | A1      | L   | L      | L                         | L   | L   | Х  | D0  | Address D0 Write In. Load A1    |

| n+5   | Х       | Х   | L      | Н                         | L   | Χ   | Χ  | Z   | Deselected or STOP              |

| n+6   | Х       | Х   | L      | Н                         | L   | Χ   | Х  | D1  | Address D1 Write In. Deselected |

| n+7   | A2      | L   | L      | L                         | L   | L   | Х  | Z   | Address and Control meet setup  |

| n+8   | Х       | Χ   | L      | Н                         | L   | Χ   | Х  | Z   | Deselected or STOP              |

| n+9   | Х       | Х   | Ĺ      | Н                         | L   | Χ   | Х  | D2  | Address D2 Write In. Deselected |

NOTES:

- 1. H = High; L = Low; X = Don't Care; ? = Don't Know; Z = High Impedance.

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}1 = L$ ,  $\overline{CE}2 = L$  and  $\overline{CE}2 = H$ .  $\overline{CE} = H$  is defined as  $\overline{CE}1 = H$ ,  $\overline{CE}2 = H$  or  $\overline{CE}2 = L$ .

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 3.3V +/-5%)

| Symbol      | Parameter                    | Test Conditions                                                                                              | Min. | Max. | Unit |

|-------------|------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|

| lu          | Input Leakage Current        | VDD = Max., VIN = 0V to VDD                                                                                  | _    | 5    | μΑ   |

| ILI         | LBO Input Leakage Current(1) | VDD = Max., VIN = 0V to VDD                                                                                  | _    | 30   | μΑ   |

| <b>I</b> LO | Output Leakage Current       | $\overline{CE} \geq \text{Vih or } \overline{OE} \geq \text{Vih, Vout} = \text{OV toVdd, Vdd} = \text{Max}.$ | -    | 5    | μΑ   |

| Vol         | Output Low Voltage           | IOL = 5mA, VDD = Min.                                                                                        | -    | 0.4  | V    |

| Voh         | Output High Voltage          | IOH = -5mA, VDD = Min.                                                                                       | 2.4  | _    | V    |

### NOTE:

3821 tbl 20

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1)</sup> (VDD = 3.3V +/-5%, VHD = VDD-0.2V, VLD = 0.2V)

|        |                                       |                                                                                                              | S133  |     | S1    |     |      |

|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----|------|

| Symbol | Parameter                             | Test Conditions                                                                                              | Com'l | Ind | Com'l | Ind | Unit |

| ldd    | Operating Power<br>Supply Current     | Device Selected, Outputs Open, ADV/LD = X, VDD = Max., VIN $\geq$ VIH or $\leq$ VIL, f = fmax <sup>(2)</sup> | 300   | 310 | 250   | 260 | mA   |

| ISB1   | CMOS Standby Power<br>Supply Current  | Device Deselected, Outputs Open, $VDD = Max., VIN \ge VHD$ or $\le VLD, f = 0^{(2)}$                         | 40    | 45  | 40    | 45  | mA   |

| ISB2   | Clock Running Power<br>Supply Current | Device Deselected, Outputs Open, Vdd = Max., Vin $\geq$ VHD or $\leq$ VLD, f = fMax $^{(2)}$                 | 110   | 120 | 100   | 110 | mA   |

| ISB3   | Idle Power<br>Supply Current          | Device Selected, Outputs Open, CEN $\geq$ VIH VDD = Max., VIN $\geq$ VHD or $\leq$ VLD, f = fMAX $^{(2)}$    | 40    | 45  | 40    | 45  | mA   |

3821 tbl 21

### NOTES:

- 1. All values are maximum guaranteed values.

- 2. At f = fmax, inputs are cycling at the maximum frequency of read cycles of 1/tcyc; f=0 means no input lines are changing.

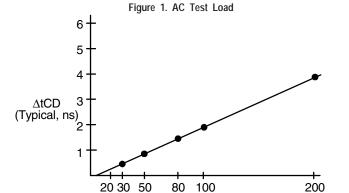

# AC Test Loads $1/00 - \underbrace{Z_0 = 50\Omega}_{2921 \text{ day} \Omega}$

Figure 2. Lumped Capacitive Load, Typical Derating

Capacitance (pF)

### AC Test Conditions

| Input Pulse Levels             | 0 to 3V       |

|--------------------------------|---------------|

| Input Rise/Fall Times          | 2ns           |

| Input Timing Reference Levels  | 1.5V          |

| Output Timing Reference Levels | 1.5V          |

| AC Test Load                   | See Figures 1 |

3821 tbl 22

3821 drw 05

<sup>1.</sup> The LBO pin will be internally pulled to VDD if it is not actively driven in the application.

### AC Electrical Characteristics

(VDD = 3.3V +/-5%, Commercial and Industrial Temperature Ranges)

|                         |                                    | 71 <b>V</b> 54 | 6S133 | 71V546 | S100 |      |

|-------------------------|------------------------------------|----------------|-------|--------|------|------|

| Symbol                  | Parameter                          | Min.           | Max.  | Min.   | Max. | Unit |

| Clock Paramet           | ers                                | •              |       | •      | •    | •    |

| tcyc                    | Clock Cycle Time                   | 7.5            |       | 10     |      | ns   |

| tF <sup>(1)</sup>       | Clock Frequency                    |                | 133   |        | 100  | MHz  |

| tсн <sup>(2)</sup>      | Clock High Pulse Width             | 2.5            |       | 3.5    |      | ns   |

| tcl <sup>(2)</sup>      | Clock Low Pulse Width              | 2.5            |       | 3.6    |      | ns   |

| Output Parame           | eters                              | •              |       |        | •    |      |

| tcd                     | Clock High to Valid Data           |                | 4.2   |        | 5    | ns   |

| tcdc                    | Clock High to Data Change          | 1.5            |       | 1.5    |      | ns   |

| tclz <sup>(3,4,5)</sup> | Clock High to Output Active        | 1.5            |       | 1.5    |      | ns   |

| tchz <sup>(3,4,5)</sup> | Clock High to Data High-Z          | 1.5            | 3.5   | 1.5    | 3.5  | ns   |

| toe                     | Output Enable Access Time          |                | 4.2   |        | 5    | ns   |

| tolz <sup>(3,4)</sup>   | Output Enable Low to Data Active   | 0              |       | 0      |      | ns   |

| tонz <sup>(3.4)</sup>   | Output Enable High to Data High-Z  |                | 3.5   |        | 3.5  | ns   |

| Setup Times             | •                                  | •              | •     | •      | •    | •    |

| tse                     | Clock Enable Setup Time            | 2.0            |       | 2.2    |      | ns   |

| tsa                     | Address Setup Time                 | 2.0            |       | 2.2    |      | ns   |

| tsd                     | Data in Setup Time                 | 1.7            |       | 2.0    |      | ns   |

| tsw                     | Read/Write (R/W) Setup Time        | 2.0            |       | 2.2    |      | ns   |

| tsadv                   | Advance/Load (ADV/LD) Setup Time   | 2.0            |       | 2.2    |      | ns   |

| tsc                     | Chip Enable/Select Setup Time      | 2.0            |       | 2.2    |      | ns   |

| tsb                     | Byte Write Enable (BWx) Setup Time | 2.0            |       | 2.2    |      | ns   |

| Hold Times              |                                    |                |       |        |      |      |

| the                     | Clock Enable Hold Time             | 0.5            |       | 0.5    |      | ns   |

| tна                     | Address Hold Time                  | 0.5            |       | 0.5    |      | ns   |

| thd                     | Data in Hold Time                  | 0.5            |       | 0.5    |      | ns   |

| thw                     | Read/Write (R/W) Hold Time         | 0.5            |       | 0.5    |      | ns   |

| thadv                   | Advance/Load (ADV/LD) Hold Time    | 0.5            |       | 0.5    |      | ns   |

| tнc                     | Chip Enable/Select Hold Time       | 0.5            |       | 0.5    |      | ns   |

| tнв                     | Byte Write Enable (BWx) Hold Time  | 0.5            |       | 0.5    |      | ns   |

### NOTES:

- 1.  $t_F = 1/t_{CYC}$ .

- 2. Measured as HIGH above 2.0V and LOW below 0.8V.

- 3. Transition is measured  $\pm 200 \text{mV}$  from steady-state.

- 4. These parameters are guaranteed with the AC load (Figure 1) by device characterization. They are not production tested.

- 5. To avoid bus contention, the output buffers are designed such that tCHZ (device turn-off) is about 2 ns faster than tCLZ (device turn-on) at a given temperature and voltage. The specs as shown do not imply bus contention because tCLZ is a Min. parameter that is worse case at totally different test conditions (0 deg. C, 3.465V) than tCHZ, which is a Max. parameter (worse case at 70 deg. C, 3.135V).

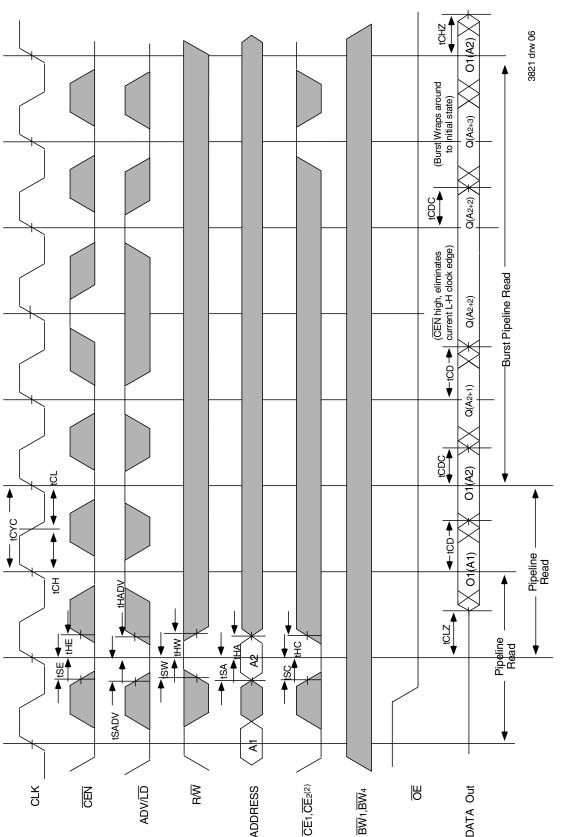

# Timing Waveform of Read Cycle<sup>(1,2,3,4)</sup>

- $\Omega$  (A1) represents the first output from the external address A1.  $\Omega$  (A2) represents the first output from the external address A1.  $\Omega$  (A2) represents the first output from the external address A2, etc. where address bits A0 and A1 are advancing for the four word burst in the sequence defined by the state of the  $\overline{LBO}$  input. CE2 timing transitions are identical but inverted to the  $\overline{CE}_1$  and  $\overline{CE}_2$  signals. For example, when  $\overline{CE}_1$  and  $\overline{CE}_2$  are LOW on this waveform, CE2 is HIGH.

- Burst ends when new address and control are loaded into the SRAM by sampling ADVILD LOW.

RIW is don't care when the SRAM is bursting (ADVILD sampled HIGH). The nature of the burst access (Read or Write) is fixed by the state of the RIW signal when new address and control are loaded into the SRAM.

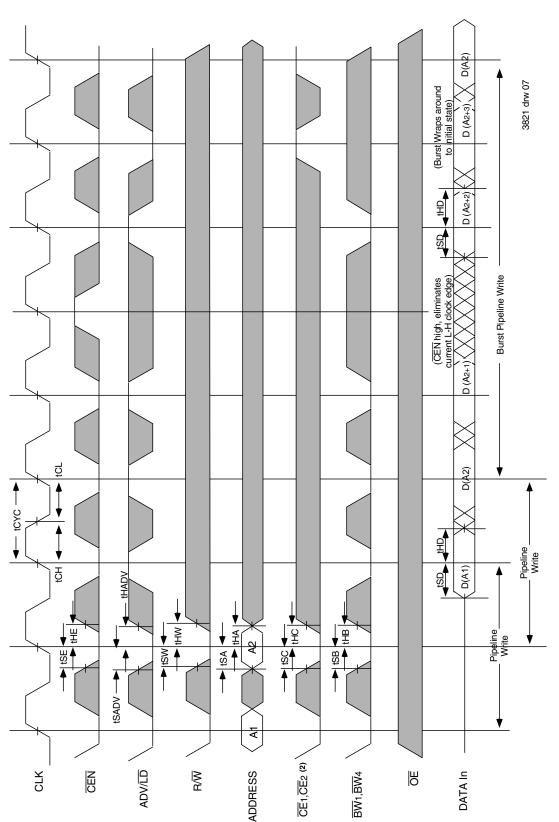

# Timing Waveform of Write Cycles<sup>(1,2,3,4,5)</sup>

- 1. D (A1) represents the first input to the external address A1. D (A2) represents the first input to the external address A2; D (A2+1) represents the next input data in the burst sequence of the base address A2, etc. where address bits A0 and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input.

2. CE2 timing transitions are identical but inverted to the CE1 and CE2 signals. For example, when CE1 and CE2 are LOW on this waveform, CE2 is HIGH.

- Burst ends when new address and control are loaded into the SRAM by sampling ADV/LD LOW.

R/W is don't care when the SRAM is bursting (ADV/LD sampled HIGH). The nature of the burst access (Read or Write) is fixed by the state of the R/W signal when new address 4.

- and control are loaded into the SRAM. In the SRAM and burst-write cycles. A write cycle is initiated when R/W signal is sampled LOW. The byte write information comes in two cycles before the actual data is presented to the SRAM.

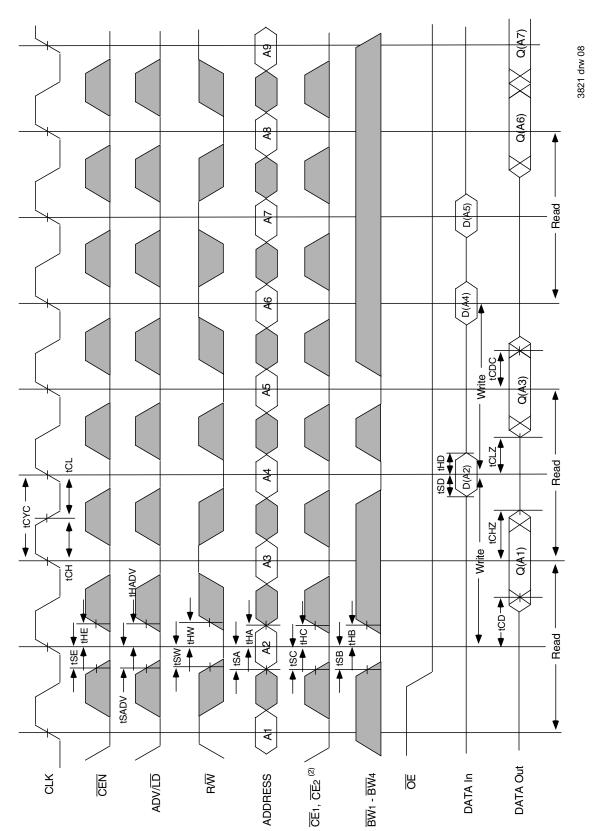

# Timing Waveform of Combined Read and Write Cycles (1,2,3)

- Q(A1) represents the first output from the external address A1. D (A2) represents the input data to the SRAM corresponding to address A2.

CE2 timing transitions are identical but inverted to the CE1 and CE2 signals. For example, when CE1 and CE2 are LOW on this waveform, CE2 is HIGH.

Individual Byte Write signals (BWx) must be valid on all write and burst-write cycles. A write cycle is initiated when R\overline{W} signal is sampled LOW. The byte write information comes in two cycles before the actual data is presented to the SRAM.

1. Q (A1) represents the first output from the external address A1. D (A2) represents the input data to the SRAM corresponding to address A2.

CE2 timing transitions are identical but inverted to the CE1 and CE2 signals. For example, when CE1 and CE2 are LOW on this waveform, CE2 is HIGH..

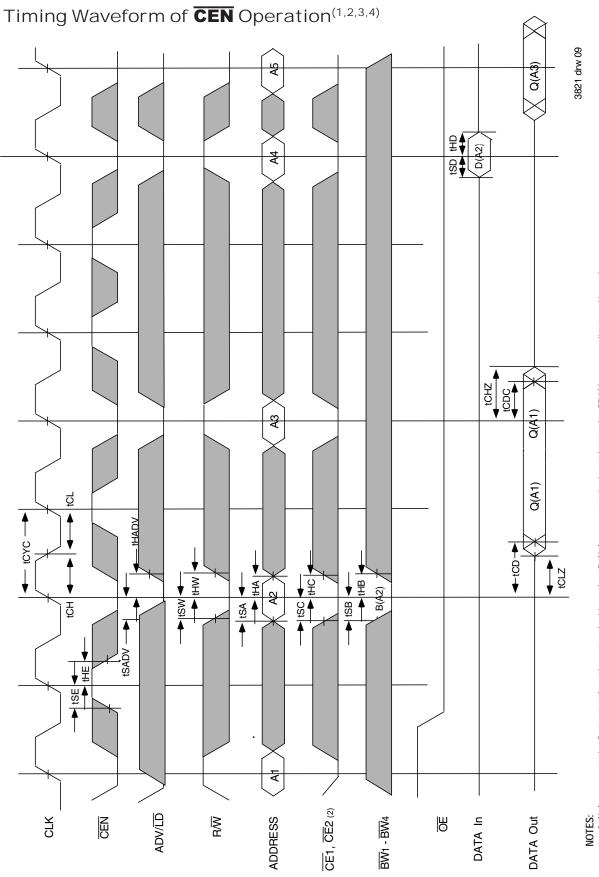

CEN when Sampled high on the rising edge of clock will block that L-H transition of the clock from propagating into the SRAM. The part will behave as if the L-H clock transition of droccur. All internal

registers in the SRAM will retain their previous state. Individual Byte Write signals (BWx) must be valid on all write and burst-write cycles. A write cycle is initiated when R/W signal is sampled LOW. The byte write information comes in two cycles before the actual data is presented to the SRAM.

# Timing Waveform of **CS** Operation<sup>(1,2,3,4)</sup>

Q (A1) represents the first output from the external address A1. D (A3) represents the input data to the SRAM corresponding to address A3 etc.

CE2 timing transitions are identical but inverted to the CE1 and CE2 signals. For example, when CE1 and CE2 are LOW on this waveform, CE2 is HIGH.

When either one of the Chip enables (CE1, CE2, CE2) is sampled inactive at the rising clock edge, a deselect cycle is initiated. The data-bus tri-states two cycles after the initiation

The byte write information of the deselect cycle. This allows for any pending data transfers (reads or writes) to be completed. Individual Byte Write signals (BWx) must be valid on all write and burst-write cycles. A write cycle is initiated when R/W signal is sampled LOW. comes in two cycles before the actual data is presented to the SRAM.

# Timing Waveform of **OE** Operation<sup>(1)</sup>

NOTE:

3821 drw 11

1. A read operation is assumed to be in progress.

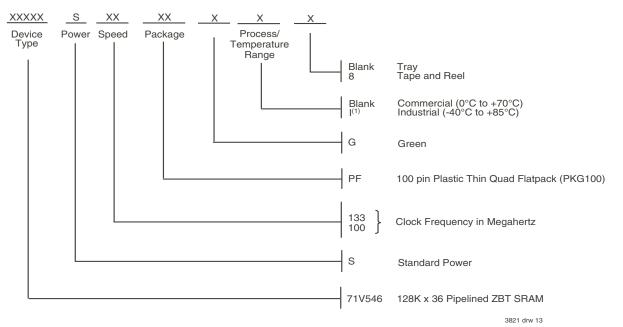

# Ordering Information

### NOTES:

### Orderable Part Information

| Speed (ns) | Orderable Part ID | Pkg.<br>Code | Pkg.<br>Type | Temp.<br>Grade |

|------------|-------------------|--------------|--------------|----------------|

| 100        | 71V546S100PFG     | PKG100       | TQFP         | С              |

|            | 71V546S100PFG8    | PKG100       | TQFP         | С              |

|            | 71V546S100PFGI    | PKG100       | TQFP         | I              |

|            | 71V546S100PFGI8   | PKG100       | TQFP         | I              |

| 133        | 71V546S133PFG     | PKG100       | TQFP         | С              |

|            | 71V546S133PFG8    | PKG100       | TQFP         | С              |

|            | 71V546S133PFGI    | PKG100       | TQFP         | I              |

|            | 71V546S133PFGI8   | PKG100       | TQFP         | I              |

3821t25.tbl

$<sup>1. \</sup> Contact your local sales of fice for Industrial temprange for other speeds, packages and powers.\\$

# Datasheet Document History

| 6/15/99  |                   | Updated to new format                                                                        |

|----------|-------------------|----------------------------------------------------------------------------------------------|

| 9/13/99  | Pg. 12            | Corrected ISB3 conditions                                                                    |

|          | Pg. 20            | Added Datasheet Document History                                                             |

| 12/31/99 | Pg. 3, 12, 13, 19 | Added Industrial Temperature range offerings                                                 |

| 11/22/05 | Pg. 3,4           | Moved Operating temperature & DC operating tables from page 3 to new page 5. Moved Absolute  |

|          |                   | rating & Capacitance tables from page 4 to new page 5. Add clarification note to Recommended |

|          |                   | Operating Temperature and Absolute Max Ratings tables.                                       |

|          | Pg. 20            | Updated order information with "Restricted hazardous substance device"                       |

| 02/23/07 | Pg. 20            | Added X generation die step to data sheet ordering information                               |

| 10/18/08 | Pg. 20            | Removed "IDT" for orderable part number                                                      |

| 08/18/17 | Pg. 1             | Removed all information for 71V546XS                                                         |

|          |                   | In Features: Added text: "Green parts available, see Ordering Information"                   |

|          |                   | Moved the FBD from page 3 to page 1 in accordance with our standard datasheet format         |

|          | Pg. 2             | Removed the IDT in reference to fabrication                                                  |

|          | Pg. 4             | Updated the TQFP pin configuration by rotating package pin labels and pin numbers 90 degrees |

|          |                   | counter clockwise added IDT logo & in accordance with the packaging code, changed the PK100  |

|          |                   | designation to PKG100, changed the text to be in alignment with new diagram marking specs    |

|          |                   | Removed footnote 2 and the 2 annotation for NC pins 83 & 84 in the TQFP pin configuration    |

|          | Pg. 13            | Removed 117 MHz speed grade offering from the DC Electrical table                            |

|          | Pg. 14            | Removed 117 MHz speed grade offering from the AC Electrical table                            |

|          | Pg. 20            | Removed Tube indicator, updated "Restricted hazardous substance" device to "Green"           |

|          |                   | Updated package code in Ordering Information from PK100 to PKG100 and removed the            |

|          |                   | 117 MHz speed grade offering                                                                 |

|          |                   | Added Orderable Part Information                                                             |

|          |                   | Removed the 100 Thin Quad Flatpack Packaging Table                                           |

|          |                   |                                                                                              |

### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/