## **General description**

The MX5069 high-side N\_FET driver works with an external MOSFET and acts as an ideal diode rectifier when connected in series with the power supply. This controller enables MOSFETs to replace diode rectifiers in power distribution networks, reducing power loss and voltage drop. The MX5069 controller provides charge pump gate drive for an external N-channel MOSFET and fast response comparator to turn off the FET when current flows in reverse.

The current limit in the external series pass N-Channel MOSFET are programmable. The input undervoltage and overvoltage lockout levels are programmabled by resistance divider networks. The MX5069 automatically restarts at a fixed duty cycle. MX5069 is available in 10-pin DFN3\*3 and MSOP10L package.

### **Features**

- ♦ Wide operating range: 5V to 85V

- ♦ Adjustable current limit

- ♦ Circuit breaker function for severe overcurrent events

- ♦ Internal high side charge pump and gate driver for external N-channel MOSFET

- ♦ 50ns fast response to current reversal

- ♦ Adjustable undervoltage lockout (UVLO)

- ♦ Adjustable overvoltage lockout (OVP)

- ♦ Active low open drain POWER GOOD output

- ♦ Available with automatic restart

- ♦ 10-Pin DFN3\*3-10L and MSOP10 package

## **Applications**

- ♦ Server backplane systems

- ♦ Base station power distribution systems

- ♦ Solid state circuit breaker

- ♦ 24V and 48V Industrial systems

## **General information**

### **Ordering information**

| Part Number | Description |

|-------------|-------------|

| MX5069D     | DFN3*3-10L  |

| MX5069MS    | MSOP10L     |

| MPQ         | 3000pcs     |

### Package dissipation rating

| Package    | RθJA (°C/W) |

|------------|-------------|

| DFN3*3-10L | 50          |

| MSOP10     | 156         |

### Absolute maximum ratings

| Parameter                             | Value         |

|---------------------------------------|---------------|

| VIN to GND                            | -0.3 to 90V   |

| SENSE, OUT to GND                     | -0.3 to 90V   |

| GATE to GND                           | -0.3 to 100V  |

| OUT to GND (1ms transient)            | -0.3 to 95V   |

| UVLO to GND                           | -0.3 to 90V   |

| OVP, PGD to GND                       | -0.3 to 7V    |

| VIN to SENSE                          | -0.3 to 0.3V  |

| ILIM to GND                           | -0.3V to 3.5V |

| Maximum junction temperature,         | 150℃          |

| T <sub>JMAX</sub>                     | 130 C         |

| Storage temperature, T <sub>stg</sub> | -65 to 150°C  |

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

## **Recommended operating condition**

| Symbol               | Range       |

|----------------------|-------------|

| Supply voltage       | 5 to 85V    |

| PGD off voltage      | 0 to 5V     |

| ILIM voltage         | 2.7V max    |

| Junction temperature | -40 to 125℃ |

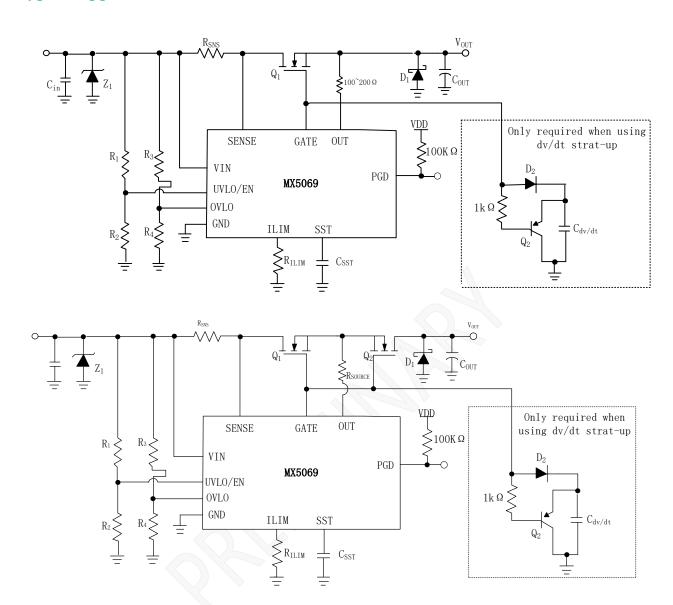

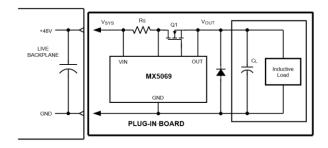

## **Typical application**

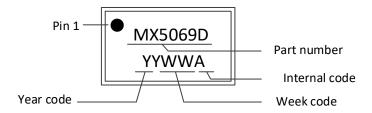

# **Marking information**

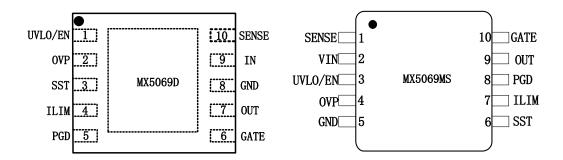

# **Terminal assignments**

| PIN NO. |        | PIN name   | Description                                                                                                                                                                                                                 |  |  |

|---------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MSOP 10 | DFN3*3 | - FIN hame | Description                                                                                                                                                                                                                 |  |  |

| 1       | 10     | SENSE      | Current sense input: The voltage across the current sense resistor (RS) is measured from VIN to this pin.                                                                                                                   |  |  |

| 2       | 9      | VIN        | Positive supply input: A small ceramic bypass capacitor close to this pin is recommended to suppress transients which occur when the load current is switched off.                                                          |  |  |

| 3       | 1      | UVLO/EN    | This is a dual function control pin. When used as an ENABLE pin and pulled down, it shuts off the internal pass MOSFET.  As an UVLO pin, it can be used to program different UVLO trip point via external resistor divider. |  |  |

| 4       | 2      | OVP        | Overvoltage lockout: An external resistor divider from the system input voltage sets the overvoltage turnoff threshold. The disabled threshold at the pin is 1.23V.                                                         |  |  |

| 5       | 8      | GND        | Circuit ground                                                                                                                                                                                                              |  |  |

| 6       | 3      | SST        | A capacitor from this pin to GND sets output voltage slew rate.                                                                                                                                                             |  |  |

| 7       | 4      | ILIM       | Current limit set: An external resistor connected to this pin, combined with a current detection resistor to achieve overcurrent protection.                                                                                |  |  |

| 8       | 5      | PGD        | Power Good indicator: An open drain output.                                                                                                                                                                                 |  |  |

| 9       | 7      | OUT        | Output feedback: Connect to the output rail (external MOSFET source).                                                                                                                                                       |  |  |

| 10      | 6      | GATE       | Gate drive output: Connect to the external MOSFET's gate. This pin's voltage is typically 12V above the OUT pin when enabled.                                                                                               |  |  |

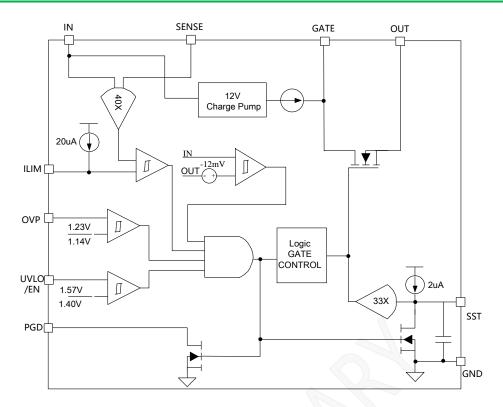

# **Block diagram**

## **Electrical characteristics**

VIN = 12V, UVLO=2V, OVP = GND,  $T_J = 25$ °C, unless otherwise noted.

| Symbol                        | PARAMETER                  | TEST CONDITIONS                 | MIN  | TYP  | MAX  | UNIT       |  |

|-------------------------------|----------------------------|---------------------------------|------|------|------|------------|--|

| INPUT (VI                     | N PIN)                     |                                 |      |      |      |            |  |

| VIN                           |                            |                                 | 5    |      | 85   | V          |  |

| IQ <sub>ON</sub>              | S. I.                      | Enabled: EN/UVLO = 2V           | 0.50 | 0.70 | 0.9  | mA         |  |

| IQ <sub>OFF</sub>             | Supply current             | EN/UVLO = 0V                    | 0.50 | 0.60 | 0.70 | mA         |  |

| EN/UVLO                       |                            |                                 |      |      |      |            |  |

| UVLOR                         | UVLO Threshold voltage     | rising                          |      | 1.57 |      | V          |  |

| UVLOF                         | UVLO Threshold voltage     | falling                         |      | 1.40 |      | V          |  |

| I <sub>UVLO</sub>             | UVLO leakage current       | EN/UVLO = 0V                    |      | -2.6 |      | uA         |  |

| t <sub>DUVLO</sub> UVLO delay | 177.0.11                   | Delay to GATE high              |      | 840  |      | us         |  |

|                               | UVLO delay                 | Delay to GATE low               |      | 3.4  |      | us         |  |

| OVP PINS                      |                            |                                 |      |      |      |            |  |

| OVPR                          | OVP Threshold voltage      | Rising                          |      | 1.23 |      | V          |  |

| OVPF                          | OVP Threshold voltage      | Falling                         |      | 1.14 |      | V          |  |

| toorn                         | OVP delay                  | Delay to GATE high              |      | 13.8 |      | 110        |  |

| tDOVP OVP delay               | OVF delay                  | Delay to GATE low               |      | 4.4  |      | μs         |  |

| Iovp                          | OVP bias current           |                                 | 0    |      | 2    | μA         |  |

| OUT PIN                       |                            |                                 |      |      |      |            |  |

| I <sub>OUT-EN</sub>           | OUT bias current, enabled  | OUT = VIN                       |      | 10   |      |            |  |

| I <sub>OUT-DIS</sub>          | OUT bias current, disabled | Disabled, OUT = 0V, SENSE = VIN |      | 22   |      | <u>μ</u> Α |  |

| GATE CO                       | NTROL (GATE PIN)           |                                 |      |      |      |            |  |

|                               | Source current             | Normal operation                | 1    | 32   | 40   | μA         |  |

|                               |                            |                                 |      |      |      |            |  |

| I <sub>GATE</sub>    | Sin1                                                                                               | UVLO < 1.40V                       |     | 0.1 |     | uA    |

|----------------------|----------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|-------|

|                      | Sink current                                                                                       | VIN to SENSE = 150mV               |     | 2   |     | A     |

| $V_{GATE}$           | Gate output voltage in normal operation                                                            | GATE-OUT voltage                   | 8   | 10  | 14  | V     |

| V <sub>SD(REV)</sub> | $ \begin{array}{c cccc} Reverse & V_{SD} & Threshold & V_{IN} & < \\ & V_{OUT} & & & \end{array} $ | V <sub>IN</sub> - V <sub>OUT</sub> | -20 | -12 | -1  | mV    |

| t <sub>SD(REV)</sub> | Gate turn off time for reverse                                                                     |                                    |     | 36  |     | ns    |

| CURRENT              | LIMIT                                                                                              |                                    |     |     |     |       |

| I <sub>ILIM</sub>    | ILIM Charge current                                                                                |                                    |     | 20  |     | uA    |

| KA                   |                                                                                                    |                                    |     | 40  |     | mV/mV |

| SST (SST P           | IN)                                                                                                |                                    |     |     |     |       |

| I <sub>SST</sub>     | SST Charging current                                                                               | Normal operation                   | 0   | 2   | 5   | uA    |

| Rsst                 | SST Discharging resistance                                                                         |                                    | 60  | 75  | 90  | Ω     |

| V <sub>SSTmax</sub>  | SST max capacitor voltage                                                                          |                                    |     | 5.2 |     | V     |

| GAIN <sub>SST</sub>  | SST to GATE gain                                                                                   |                                    |     | 33  |     | V/V   |

| PGD                  |                                                                                                    |                                    |     |     |     |       |

| $V_{PGD}$            | Output low voltage                                                                                 | $I_{SINK} = 2mA$                   |     | 140 | 180 | mV    |

| I <sub>PGD</sub>     | Off leakage current                                                                                | $V_{PGD} = 5V$                     | 0   | •   |     | μΑ    |

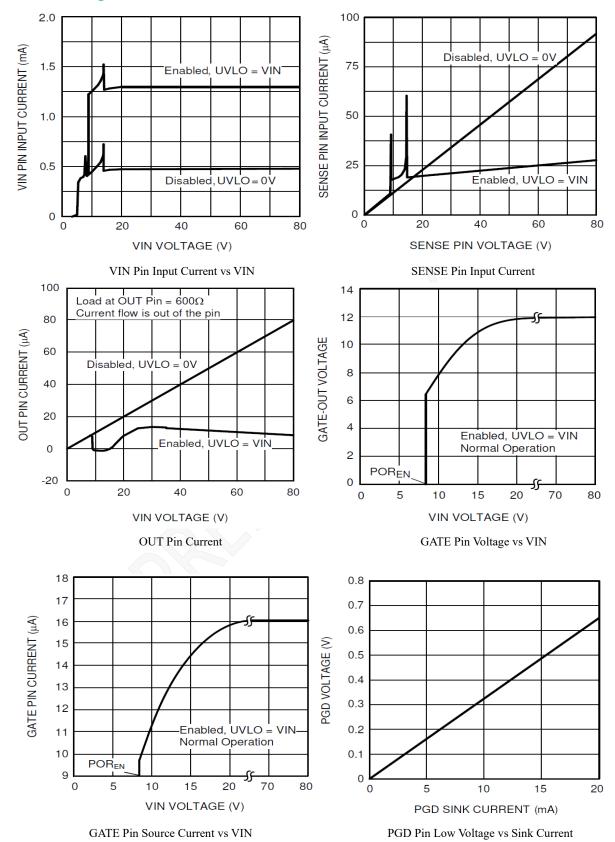

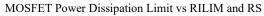

## **Characteristic plots**

GATE Pulldown Current, Circuit Breaker vs GATE Voltage

## **Detailed description**

### **Overview**

MX5069 have programmable current limit, current limiting for an extended period results in the shutdown of the series pass device. In this event, the MX5069 retries an infinite number of times to recover after the fault is removed. The circuit breaker function quickly switches off the series pass device upon detection of a severe overcurrent condition. Programmable undervoltage lockout (UVLO) and overvoltage lockout (OVP) circuits shut down the MX5069 when the system input voltage is outside the desired operating range.

### **Current Limit**

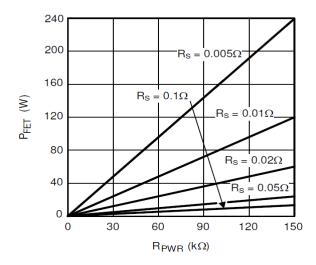

When the voltage across the sense resistor  $R_S$  (VIN to SENSE) is multiplied by 40 times reaches the voltage of  $R_{ILIM}$ , the overcurrent protection is triggered. In the current limiting condition, the GATE voltage is controlled to limit the current in MOSFET Q1. While the current limit circuit is active, the fault SST is actived. For proper operation, the RS resistor value must be no larger than  $100m\Omega$ .

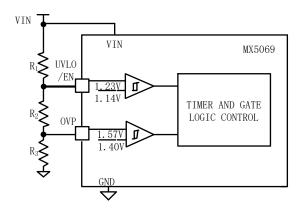

#### **Undervoltage Lockout (UVLO)**

As an input pin, it controls the ON/OFF state of the internal MOSFET. In its high state, the internal MOSFET is enabled. A low on this pin will turn off the internal MOSFET. High and Low levels are specified in the parametric table of the datasheet. The EN/UVLO pin is also used to clear a thermal shutdown latch by toggling this pin high to low.

The internal de-glitch delay on EN/UVLO falling edge is intentionally kept low (1us typical) for quick detection of power failure. When used with a resistor divider connected between IN, UVLO, OVP and GND pins of the device, powerfail detection on EN/UVLO helps in quick turn-off of the FET driver, thereby stopping the flow of reverse current. For applications where a higher de-glitch delay on EN/UVLO is

desired, or when the supply is particularly noisy, it is recommended to use an external bypass capacitor from EN/UVLO to GND.

### Overvoltage Lockout (OVP)

The over voltage protection can be set by a external resistor divider. When the voltage of OVP pin exceed the internal reference voltage (1.23V typical), the internal MOSFET will be turned off quickly. When the voltage of this pin returns to the hysteresis voltage, the internal MOSFET will be reopened after the dVdT time.

### **Power Good Pin**

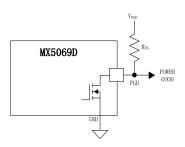

During turn-on, the Power Good pin (PGD) is high until the voltage at VIN increases above  $\approx 5$ V. PGD then switches low, remaining low as the VIN voltage increases. When the voltage at OUT increases to within 1.25V of the SENSE pin (VDS <1.25V), PGD switches high. PGD switches low if the VDS of Q1 increases above 2.5V. A pullup resistor is required at PGD as shown in the following figure. The pullup voltage (VPGD) can be as high as 5V.

Power Good Output

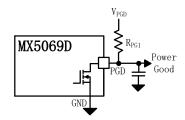

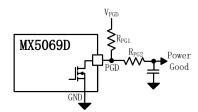

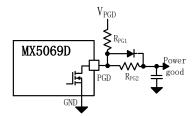

If a delay is required at PGD, suggested circuits are shown in the following figure. In figure a), capacitor  $C_{PG}$  adds delay to the rising edge, but not to the falling edge. In figure b), the rising edge is delayed by  $R_{PG1} + R_{PG2}$  and  $C_{PG}$ , while the falling edge is delayed a lesser amount by  $R_{PG2}$  and  $C_{PG}$ . In figure c), adding a diode across  $R_{PG2}$  allows for equal delays at the two edges, or a short delay at the rising edge and a long delay at the falling edge.

a) Delay Rising Edge Only

b) Long delay at rising edge, short delay at falling edge

Short Delay at Rising Edge and Long Delay at Falling

Edge or Equal Delays

Adding delay to the power good output pin

#### **Gate control**

A charge pump provides internal bias voltage above the output voltage (OUT pin) to enhance the N-Channel MOSFET's gate. The gate-to-source voltage is limited by an internal 12V Zener diode. During normal operating conditions the gate of Q1 is held charged by an internal  $32\mu A$  current source to approximately 12V above OUT.

## **Application and Implementation**

### **Design Requirements**

When charging the output capacitor through the MOSFET, the FET's total energy dissipation equals the total energy stored in the output capacitor (½CV2). Thus, both the input voltage and output capacitance determine the stress experienced by the MOSFET. The maximum load current drives the current limit

and sense resistor selection. In addition, the maximum load current, maximum ambient temperature, and the thermal properties of the PCB (R $\theta$ CA) drive the selection of the MOSFET RDSON and the number of MOSFETs used. R $\theta$ CA is a strong function of the layout and the amount of copper that is connected to the drain of the MOSFET. Note that the drain is not electrically connected to the ground plane and thus the ground plane cannot be used to help with heat dissipation. It's a good practice to measure the R $\theta$ CA of a given design after the physical PCBs are available.

### **Detailed Design Procedure**

#### Select RSNS and CL setting

The MX5069 monitors the current in the external MOSFET (Q1) by measuring the voltage across the sense resistor (Rs), connected from VIN to SENSE. The voltage at both ends of the RS is amplified and compared with the voltage at both ends of the R<sub>ILIM</sub>. If it is greater than the voltage at both ends of the R<sub>ILIM</sub>, the overcurrent protection is triggered, the gate is pulled to the ground, and external MOSFET is turned off.

Typically sense resistors are only available in discrete value.

We choose the next smallest discrete value.

#### **MOSFET Selection**

The important MOSFET electrical parameters are the maximum continuous Drain current  $I_D$ , the maximum Source current (that is, body diode)  $I_S$ , the maximum drain-to-source voltage  $V_{DS(MAX)}$ , the gate-to-source threshold voltage  $V_{GS(TH)}$ , the drain-to-source reverse breakdown voltage  $V_{(BR)DSS}$ , and the drain-to-source on resistance  $R_{DS(ON)}$ .

The maximum continuous drain current,  $I_D$ , rating must exceed the maximum continuous load current. The rating for the maximum current through the body diode,  $I_S$ , is typically rated the same as, or slightly higher than the drain current, but body diode current only flows while the MOSFET gate is being charged to  $V_{GS(TH)}$ .

Gate Charge Time =  $Qg / I_{GATE(ON)}$

1. The maximum drain-to-source voltage,  $V_{DS(MAX)}$ , must be high enough to withstand the highest differential voltage

seen in the application. This would include any anticipated fault conditions.

- 2. The drain-to-source reverse breakdown voltage,  $V_{(BR)DSS}$ , may provide some transient protection to the OUT pin in low voltage applications by allowing conduction back to the IN pin during positive transients at the OUT pin.

- 3. The gate-to-source threshold voltage,  $V_{GS(TH)}$ , should be compatible with the MX5069 gate drive capabilities. Logic level MOSFETs, with  $R_{DS(ON)}$  rated at  $V_{GS(TH)}$  at 5V, are recommended, but sub-Logic level MOSFETs having  $R_{DS(ON)}$  rated at  $V_{GS(TH)}$  at 2.5V, can also be used.

- 4. The dominate MOSFET loss for the MX5069 active ORing controller is conduction loss due to source-to-drain current to the output load, and the  $R_{DS(ON)}$  of the MOSFET. This conduction loss could be reduced by using a MOSFET with the lowest possible  $R_{DS(ON)}$ . However, contrary to popular belief, arbitrarily selecting a MOSFET based solely on having low  $R_{DS(ON)}$  may not always give desirable results for several reasons:

- Reverse transition detection. Higher R<sub>DS(ON)</sub> will provide increased voltage information to the MX5069 Reverse Comparator at a lower reverse current level. This will give an earlier MOSFET turnoff condition should the input voltage become shorted to ground. This will minimize any disturbance of the redundant bus.

- 2. Reverse current leakage. In cases where multiple input supplies are closely matched it may be possible for some small current to flow continuously through the MOSFET drain to source (that is, reverse) without activating the MX5069 Reverse Comparator. Higher  $R_{DS(ON)}$  will reduce this reverse current level.

- 3. Cost. Generally, as the  $R_{DS(ON)}$  rating goes lower, the cost of the MOSFET goes higher.

- 4. The dominate MOSFET loss for the MX5069 active ORing controller is conduction loss due to source-to-drain current to the output load, and the  $R_{DS(ON)}$  of the MOSFET. This conduction loss could be reduced by using a MOSFET with the lowest possible  $R_{DS(ON)}$ . However, contrary to popular belief, arbitrarily selecting a MOSFET based solely on having low  $R_{DS(ON)}$  may not always give desirable results for several reasons:

- a. It is suggested that R<sub>DS(ON)</sub> be selected to provide no

more than 100mV, at the nominal load current.

$$R_{DS(ON)} \le (100 \text{mV} / I_D)$$

b. The thermal resistance of the MOSFET package should also be considered against the anticipated dissipation in the MOSFET to ensure that the junction temperature (T<sub>J</sub>) is reasonably well controlled, because the R<sub>DS(ON)</sub> of the MOSFET increases as the junction temperature increases.

$$P_{\rm DISS} = I_{\rm D}^2 \times (R_{\rm DS(ON)})$$

- 5. Operating with a maximum ambient temperature  $(T_{A(MAX)})$  of 35°C, a load current of 10 A, and an  $R_{DS(ON)}$  of 10 m $\Omega$ , and desiring to keep the junction temperature under 100°C, the maximum junction-to-ambient thermal resistance rating  $(R\theta_{JA})$  must be:

- a.  $R_{\theta JA} \leq (T_{J(MAX)} T_{A(MAX)}) / (I_D^2 \times R_{DS(ON)})$

- b.  $R_{\theta JA} \le (100^{\circ}C 35^{\circ}C) / (10A \times 10A \times 0.01\Omega)$

- c.  $R_{\theta JA} \leq 65^{\circ} C/W$ .

### Set Undervoltage and Overvoltage Threshold

By programming the UVLO and OVP thresholds the MX5069 enables the series pass device (Q1) when the input supply voltage (VIN) is within the desired operational range. If VIN is below the UVLO threshold, or above the OVP threshold, Q1 is switched off, denying power to the load. Hysteresis is provided for each threshold. The OVP function can be disabled by grounding the OVP pin.

#### Option A

The configuration shown in the following figure requires three resistors (R1  $\sim$  R3) to set the thresholds.

The undervoltage lockout (UVLO) and overvoltage trip point are adjusted using an external voltage divider network of R1,

R2 and R3 connected between IN, UVLO, OVP and GND pins of the device. The values required for setting the undervoltage and overvoltage are calculated by the following equation:

$$V_{UVLOR} = \frac{R_2 + R_3}{R_1 + R_2 + R_3} \cdot V_{UVL}$$

$$V_{OVPR} = \frac{R_3}{R_1 + R_2 + R_3} \cdot V_{OVH}$$

Where  $V_{UVLOR} = 1.46V$  and  $V_{OVPR} = 1.23V$ .

Since R1 , R2 and R3 will leak the current from input supply VIN, these resistors should be selected based on the acceptable leakage current from input power supply VIN. The current drawn by R1 , R2 and R3 from the power supply  $\{I_{R123} = VIN / (R1 + R2 + R3)\}$ .

However, leakage currents due to external active components connected to the resistor string can add error to these calculations. So, the resistor string current,  $I_{R123}$  must be chosen to be 20x greater than the leakage current of EN/UVLO and OVP pins.

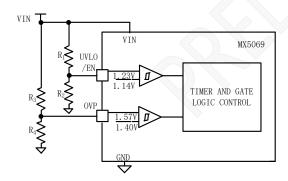

#### Option B

If all four thresholds must be accurately defined, the configuration in the following figure can be used.

The four resistor values are calculated as follows:

$$R2 = \frac{1.46V \times R1}{(V_{UVL} - 1.46V)}$$

$$R4 = \frac{1.23V \times R3}{(V_{OVH} - 1.23V)}$$

Where the R1 ~ R4 resistor values are known, the threshold voltages and hysteresis are calculated by the following equations:

$$V_{UVL} = \frac{1.46V \times (R1 + R2)}{R2}$$

$$V_{OVH} = \frac{1.23V \times (R3 + R4)}{R4}$$

#### **Input and Output Protection**

Proper operation of the MX5069 hot swap circuit requires a voltage clamping element present on the supply side of the connector into which the hot swap circuit is plugged in. A TVS is ideal, as depicted in Typical application. The TVS is necessary to absorb the voltage transient generated whenever the hot swap circuit shuts off the load current. This effect is the most severe during a hot-short when a large current is suddenly interrupted when the FET shuts off. The TVS must be chosen to have minimal leakage current at V<sub>INMAX</sub> and to clamp the voltage to under 30V during hot-short events. A 100~200ohm resistor should be palced between OUT pin and Source of external MOSFET to prevent damage from surge voltage, as the R<sub>SOURCE</sub> shown in the Typical application.

## **Power Supply Recommendations**

In general, the MX5069 behavior is more reliable if it is supplied from a very regulated power supply. However, high-frequency transients on a backplane are not uncommon due to adjacent card insertions or faults. If this is expected in the end system, Maxin recommends placing a  $1\mu F$  ceramic capacitor to ground close to the drain of the hot swap MOSFET. This reduces the common mode voltage seen by VIN and SENSE. Additional filtering may be necessary to avoid nuisance trips.

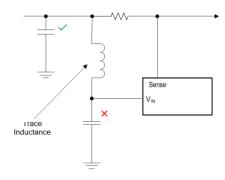

## **Layout Guidelines**

The following guidelines must be followed when designing the PC board for the MX5069:

Place the MX5069 close to the board's input connector

WUXI MAXIN MICRO 11 / 15 无锡明芯微电子有限公司

to minimize trace inductance from the connector to the FET.

• Note that special care must be taken when placing the bypass capacitor for the VIN pin. During hot shorts, there is a very large dv/dt on input voltage after the MOSFET turns off. If the bypass capacitor is placed right next to the pin and the trace from Rsns to the pin is long, an LC filter is formed. As a result, a large differential voltage can develop between VIN and SENSE. To avoid this, place the bypass capacitor close to Rsns instead of the VIN pin.

Layout Trace Inductance

- The sense resistor (Rs) must be close to the MX5069, and connected to it using the Kelvin techniques.

- The high current path from the board's input to the load (via Q1), and the return path, must be parallel and close to each other to minimize loop inductance.

- The ground connection for the various components around the MX5069 must be connected directly to each other, and to the MX5069's GND pin, and then connected to the system ground at one point. Do not connect the various component grounds to each other through the high current ground line.

- Provide adequate heat sinking for the series pass device

(Q1) to help reduce stresses during turnon and turnoff.

- The board's edge connector can be designed to shut off

the MX5069 as the board is removed, before the supply voltage is disconnected from the MX5069. When the board is inserted into the edge connector, the system voltage is applied to the MX5069's VIN pin before the UVLO voltage is taken high.

## **System Considerations**

- A) Continued proper operation of the MX5069 hot swap circuit requires capacitance be present on the supply side of the connector into which the hot swap circuit is plugged in, as depicted in the following figure. The capacitor in the Live Backplane section is necessary to absorb the transient generated whenever the hot swap circuit shuts off the load current. If the capacitance is not present, inductance in the supply lines generate a voltage transient at shut-off which can exceed the absolute maximum rating of the MX5069, resulting in its destruction.

- B) If the load powered via the MX5069 hot swap circuit has inductive characteristics, a diode is required across the MX5069's output. The diode provides a recirculating path for the load's current when the MX5069 shuts off that current. Adding the diode prevents possible damage to the MX5069 as the OUT pin is taken below ground by the inductive load at shutoff.

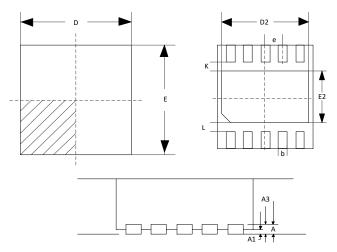

# Package information DFN3\*3-10L

DFN3\*3-10L for MX5069D

| SYMBOL  | MILLIMETERS    |         |      |  |

|---------|----------------|---------|------|--|

| STWIDOL | MIN            | NOM     | MAX  |  |

| A       | 0.70           | 0.75    | 0.80 |  |

| A1      | 0.00           | 0.03    | 0.05 |  |

| A3      |                | 0.20REF |      |  |

| b       | 0.18           | 0.24    | 0.30 |  |

| D       | 3.00BSC        |         |      |  |

| D2      | 2.45 2.50 2.55 |         |      |  |

| Е       | 3.00BSC        |         |      |  |

| E2      | 1.75           | 1.80    | 1.85 |  |

| e       | 0.50BSC        |         |      |  |

| K       | 0.19TYP        |         |      |  |

| θ       | 0.35           | 0.40    | 0.45 |  |

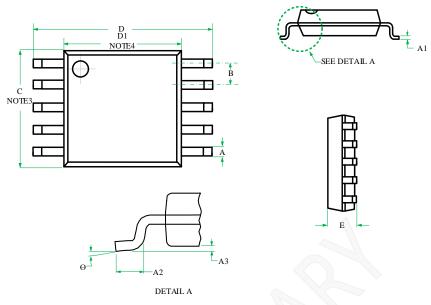

## Package information MSOP 3\*3-10L

MSOP3\*3-10L for MX5069MS

| SYMBOL | MILLIMETERS |      |  |

|--------|-------------|------|--|

| SIMBOL | MIN         | MAX  |  |

| A      | 0.17        | 0.27 |  |

| A1     | 0.13        | 0.23 |  |

| A2     | 0.4         | 0.7  |  |

| A3     | 0.05        | 0.15 |  |

| В      | 0.5         | typ  |  |

| C      | 2.9         | 3.1  |  |

| D      | 4.75        | 5.05 |  |

| D1     | 2.9         | 3.1  |  |

| E      | 1.1max      |      |  |

| θ      | 0°          | 8°   |  |

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

## **Restrictions on Product Use**

- ♦ MAXIN micro is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing MAXIN products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such MAXIN products could cause loss of human life, bodily injury or damage to property.

- ◆ In developing your designs, please ensure that MAXIN products are used within specified operating ranges as set forth in the most recent MAXIN products specifications.

- ◆ The information contained herein is subject to change without notice.

Version update record:

V10 The original version (preliminary)

V11 Update electrical characteristics and optimize detailed description.