# Fully Integrated Proximity and Ambient Light Sensor With Infrared Emitter, I<sup>2</sup>C Interface, and Interrupt Function (with multiple slave addresses)

www.vishay.com

## LINKS TO ADDITIONAL RESOURCES

## DESCRIPTION

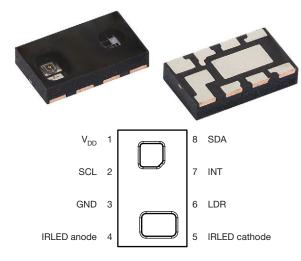

VCNL4030X01 integrates a proximity sensor (PS), ambient light sensor (ALS), and a high power IRED into one small package. It incorporates photodiodes, amplifiers, and analog to digital converting circuits into a single chip by CMOS process. The 16-bit high resolution ALS for excellent sensing capabilities with sufficient selections to fulfill most applications whether dark or high transparency lens design. Both ALS and PS offer a programmable interrupt with individual high and low thresholds offers the power savings on the microcontroller.

The proximity sensor features an intelligent cancellation scheme, so that cross talk is eliminated effectively. The proximity's smart persistence feature prevents the misjudgment of proximity sensing with a fast response time. Active force mode, one time trigger by one instruction, offers more design flexibility to fulfill different kinds of applications with more power savings.

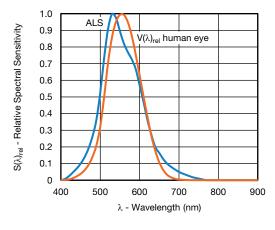

The adoption of patented Filtron<sup>TM</sup> technology achieves the closest ambient light spectral sensitivity to real human eye responses and offers the best background light cancellation capability (including sunlight) without utilizing the microcontrollers' resources. VCNL4030X01 provides an excellent temperature compensation capability for keeping the output stable over temperature. ALS and PS functions are easily operated via the simple command format of I<sup>2</sup>C (SMBus compatible) interface protocol. Operating voltage ranges from 2.5 V to 3.6 V. VCNL4030X01 is packaged in a lead-free 8-pin QFN package, which offers the best market-proven reliability quality.

## FEATURES

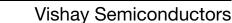

- Package type: surface-mount

- Dimensions (L x W x H in mm): 4.0 x 2.36 x 0.75 AEC-Q101 gualified Integrated modules: infrared emitter (IRED),

- ambient light sensor (ALS), proximity sensor (PS), and signal conditioning IC

- · Operates ALS and PS in parallel structure

- Filtron<sup>TM</sup> technology adoption for robust background light cancellation

- power Low consumption I<sup>2</sup>C (SMBus compatible) interface

- Orderable in four different slave addresses

- Output type: I<sup>2</sup>C bus (ALS / PS)

- Operation voltage: 2.5 V to 3.6 V

- Floor life: 168 h, MSL 3, according to J-STD-020

- · Material categorization: for definitions of compliance please see www.vishay.com/doc?99912

## **PROXIMITY FUNCTION**

- Immunity to red glow (940 nm IRED)

- Programmable IRED sink current

- Intelligent cancellation to reduce cross talk phenomenon

- Smart persistence scheme to reduce PS response time

- Selectable for 12- / 16-bit PS output data

#### **AMBIENT LIGHT FUNCTION**

- High accuracy of ALS ± 10 %

- Fluorescent light flicker immunity

- · Spectrum close to real human eye responses

### INTERRUPT

- · Programmable interrupt function for ALS and PS with upper and lower thresholds

- Adjustable persistence to prevent false triggers for ALS and PS

### APPLICATIONS

- · Proximity sensor for

- Mobile devices (e.g. smart phones, tablets) for touch screen locking, power saving etc. - Automotive for presence detection

- Integrated ambient light function for display / keypad contrast control and dimming of mobile devices

- Collision detection in robots and toys

- Proximity / optical switch for consumer, computing, automotive and industrial devices, and displays (like notebooks, tablet PCs, and automotive touch panels)

- · Dimming control for consumer, computing, industrial, and automotive displays

Rev. 1.3, 07-Jul-2023

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

FREE **GREEN** (5-2008)

| PRODUCT        | PRODUCT SUMMARY            |                                      |            |                                              |                 |                                        |                          |                                                |  |  |

|----------------|----------------------------|--------------------------------------|------------|----------------------------------------------|-----------------|----------------------------------------|--------------------------|------------------------------------------------|--|--|

| PART<br>NUMBER | OPERATING<br>RANGE<br>(mm) | OPERATING<br>VOLTAGE<br>RANGE<br>(V) | VOLTACE    | IRED PULSE<br>CURRENT <sup>(1)</sup><br>(mA) |                 | AMBIENT<br>LIGHT<br>RESOLUTION<br>(lx) | OUTPUT<br>CODE           | ADC RESOLUTION<br>PROXIMITY /<br>AMBIENT LIGHT |  |  |

| VCNL4030X01    | 0 to 300                   | 2.5 to 3.6                           | 1.8 to 5.5 | 200                                          | 0.004 to 16 768 | 0.004                                  | 16 bit, I <sup>2</sup> C | 16 bit / 16 bit                                |  |  |

Note

<sup>(1)</sup> Adjustable through I<sup>2</sup>C interface

| ORDERING INFORMATION |               |                 |                            |

|----------------------|---------------|-----------------|----------------------------|

| ORDERING CODE        | PACKAGING     | VOLUME (1)      | REMARKS                    |

| VCNL4030X01-GS08     |               | MOQ: 3300 pcs   |                            |

| VCNL4030X01-GS18     |               | MOQ: 13 000 pcs |                            |

| VCNL40301X01-GS08    |               | MOQ: 3300 pcs   |                            |

| VCNL40301X01-GS18    | Tana and real | MOQ: 13 000 pcs | 4.0 mm x 2.36 mm x 0.75 mm |

| VCNL40302X01-GS08    | Tape and reel | MOQ: 3300 pcs   | 4.0 mm x 2.30 mm x 0.75 mm |

| VCNL40302X01-GS18    |               | MOQ: 13 000 pcs |                            |

| VCNL40303X01-GS08    |               | MOQ: 3300 pcs   |                            |

| VCNL40303X01-GS18    |               | MOQ: 13 000 pcs | ]                          |

Note

<sup>(1)</sup> MOQ: minimum order quantity

| SLAVE ADDRESS OPTIONS |                       |  |  |  |  |  |  |

|-----------------------|-----------------------|--|--|--|--|--|--|

| ORDERING CODE         | SLAVE ADDRESS (7 bit) |  |  |  |  |  |  |

| VCNL4030X01-GS08      | 0x60                  |  |  |  |  |  |  |

| VCNL4030X01-GS18      | 000                   |  |  |  |  |  |  |

| VCNL40301X01-GS08     | 0x51                  |  |  |  |  |  |  |

| VCNL40301X01-GS18     | 0251                  |  |  |  |  |  |  |

| VCNL40302X01-GS08     | 0x40                  |  |  |  |  |  |  |

| VCNL40302X01-GS18     | 0,,40                 |  |  |  |  |  |  |

| VCNL40303X01-GS08     | 0x41                  |  |  |  |  |  |  |

| VCNL40303X01-GS18     | 0.24 1                |  |  |  |  |  |  |

| <b>ABSOLUTE MAXIMUM RATINGS</b> ( $T_{amb} = 25 \text{ °C}$ , unless otherwise specified) |                |                  |      |      |      |  |  |  |  |

|-------------------------------------------------------------------------------------------|----------------|------------------|------|------|------|--|--|--|--|

| PARAMETER                                                                                 | TEST CONDITION | SYMBOL           | MIN. | MAX. | UNIT |  |  |  |  |

| Supply voltage                                                                            |                | V <sub>DD</sub>  | 2.5  | 3.6  | V    |  |  |  |  |

| Operation temperature range                                                               |                | T <sub>amb</sub> | -40  | +105 | °C   |  |  |  |  |

| Storage temperature range                                                                 |                | T <sub>stg</sub> | -40  | +110 | °C   |  |  |  |  |

| <b>RECOMMENDED OPERATING CONDITIONS</b> ( $T_{amb} = 25 \text{ °C}$ , unless otherwise specified) |                |                       |      |      |      |  |  |  |  |

|---------------------------------------------------------------------------------------------------|----------------|-----------------------|------|------|------|--|--|--|--|

| PARAMETER                                                                                         | TEST CONDITION | SYMBOL                | MIN. | MAX. | UNIT |  |  |  |  |

| Supply voltage                                                                                    |                | V <sub>DD</sub>       | 2.5  | 3.6  | V    |  |  |  |  |

| Operation temperature range                                                                       |                | T <sub>amb</sub>      | -40  | +105 | °C   |  |  |  |  |

| I <sup>2</sup> C bus operating frequency                                                          |                | f <sub>(I2CCLK)</sub> | 10   | 400  | kHz  |  |  |  |  |

Rev. 1.3, 07-Jul-2023

2

Document Number: 84250

www.vishay.com

# Vishay Semiconductors

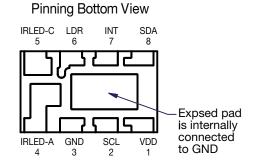

| PIN DESCRIPTIONS |                 |                    |                                               |  |  |  |  |  |

|------------------|-----------------|--------------------|-----------------------------------------------|--|--|--|--|--|

| PIN ASSIGNMENT   | SYMBOL          | TYPE               | FUNCTION                                      |  |  |  |  |  |

| 1                | V <sub>DD</sub> | -                  | Power supply input                            |  |  |  |  |  |

| 2                | SCL             | I                  | I <sup>2</sup> C digital bus clock input      |  |  |  |  |  |

| 3                | GND             | -                  | Ground                                        |  |  |  |  |  |

| 4                | IR ANODE        | I                  | Anode for IRED                                |  |  |  |  |  |

| 5                | IR CATHODE      | I                  | Cathode (IRED) connection                     |  |  |  |  |  |

| 6                | LDR             | I                  | IRED driver input                             |  |  |  |  |  |

| 7                | INT             | 0                  | Interrupt pin                                 |  |  |  |  |  |

| 8                | SDA             | I / O (open drain) | I <sup>2</sup> C data bus data input / output |  |  |  |  |  |

#### **BLOCK DIAGRAM**

Fig. 1 - Detailed Block Diagram

## **Vishay Semiconductors**

| PARAMETER                          |                | TEST CONDITION                                    | SYMBOL               | MIN. | TYP.   | MAX.          | UNIT     |  |

|------------------------------------|----------------|---------------------------------------------------|----------------------|------|--------|---------------|----------|--|

| Supply voltage                     |                |                                                   | V <sub>DD</sub>      | 2.5  | -      | 3.6           | V        |  |

| Cupply current                     |                | Excluded LED driving                              | I <sub>DD</sub>      | -    | 300    | -             | μA       |  |

| Supply current                     |                | Light condition = dark, $V_{DD}$ = 3.3 V          | I <sub>DD</sub> (SD) | -    | 0.2    | -             | μA       |  |

| I <sup>2</sup> C supply voltage    |                |                                                   | V <sub>PULL UP</sub> | 1.8  | -      | 5.5           | V        |  |

| ALS shut down                      |                | ALS disable, PS enable                            | I <sub>ALSSD</sub>   | -    | 200    | -             | μA       |  |

| PS shut down                       |                | ALS enable, PS disable                            | I <sub>PSSD</sub>    | -    | 260    | -             | μA       |  |

|                                    | Logic high     | N 22N                                             | V <sub>IH</sub>      | 1.55 | -      | -             | V        |  |

| 12C aignal innut                   | Logic low      | V <sub>DD</sub> = 3.3 V                           | V <sub>IL</sub>      | -    | -      | 0.4           | V        |  |

| I <sup>2</sup> C signal input      | Logic high     | N 0.0N                                            | V <sub>IH</sub>      | 1.4  | -      | -             | V        |  |

|                                    | Logic low      | V <sub>DD</sub> = 2.6 V                           | V <sub>IL</sub>      | -    | -      | 0.4           | v        |  |

| Peak sensitivity wavelength of ALS |                |                                                   | λ <sub>p</sub>       | -    | 550    | -             | nm       |  |

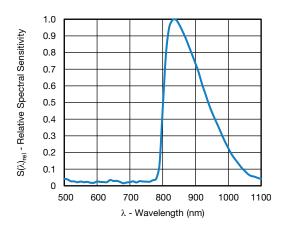

| Peak sensitivity wa                | velength of PS |                                                   | λ <sub>p</sub>       | -    | 850    | -             | nm       |  |

| Full ALS counts                    |                | 16-bit resolution                                 |                      | -    | -      | 65 535        | steps    |  |

| Full PS counts                     |                | 12-bit / 16-bit resolution                        |                      | -    | -      | 4096 / 65 535 | steps    |  |

| ALS sensing tolera                 | nce            | White LED light source                            |                      | -    | -      | ± 10          | %        |  |

| Detectable                         | Minimum        | ALS_IT = 800 ms, 1 step <sup>(1)(2)</sup>         |                      | -    | 0.004  | -             | <b>.</b> |  |

| intensity                          | Maximum        | ALS_IT = 50 ms, 65 535 step <sup>(1)(2)</sup>     |                      | -    | 16 768 | -             | lx       |  |

| ALS dark offset                    |                | ALS_IT = 50 ms, normal sensitivity <sup>(1)</sup> |                      | 0    | -      | 3             | steps    |  |

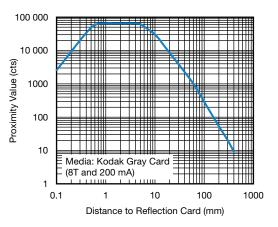

| PS detection range                 |                | Kodak gray card                                   |                      | 0    | -      | 300           | mm       |  |

| Operating temperature range        |                |                                                   | T <sub>amb</sub>     | -40  | -      | +105          | °C       |  |

| LED_Anode voltage                  | Э              |                                                   |                      | -    | -      | 5.5           | V        |  |

| IRED driving curren                | nt             | (3)                                               |                      | -    | 200    | -             | mA       |  |

#### Notes

$^{(1)}\,$  Test condition:  $V_{DD}$  = 3.3 V, temperature: 25  $^{\circ}C$

<sup>(2)</sup> Maximum detection range to ambient light can be determined by ALS refresh time adjustment and two sensitivity bits (ALS\_HD and ALS\_NS). Refer to table "ALS Resolution and Maximum Detection Range"

<sup>(3)</sup> Programmable between 50 mA and 200 mA; based on IRED on / off duty ratio = 1/40, 1/80, 1/160, and 1/320

# Vishay Semiconductors

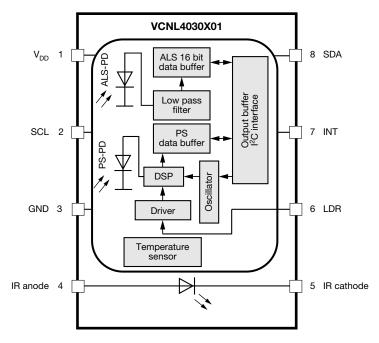

| I <sup>2</sup> C BUS TIMING CHARACTERISTICS (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                       |        |         |      |      |      |  |  |

|----------------------------------------------------------------------------------------------------|-----------------------|--------|---------|------|------|------|--|--|

| PARAMETER                                                                                          | SYMBOL                | STANDA | RD MODE | FAST | MODE | UNIT |  |  |

| PARAMETER                                                                                          | STIVIDOL              | MIN.   | MAX.    | MIN. | MAX. | UNIT |  |  |

| Clock frequency                                                                                    | f <sub>(I2CCLK)</sub> | 10     | 100     | 10   | 400  | kHz  |  |  |

| Bus free time between start and stop condition                                                     | t <sub>(BUF)</sub>    | 4.7    | -       | 1.3  | -    | μs   |  |  |

| Hold time after (repeated) start condition;<br>after this period, the first clock is generated     | t <sub>(HDSTA)</sub>  | 4.0    | -       | 0.6  | -    | μs   |  |  |

| Repeated start condition setup time                                                                | t <sub>(SUSTA)</sub>  | 4.7    | -       | 0.6  | -    | μs   |  |  |

| Stop condition setup time                                                                          | t <sub>(SUSTO)</sub>  | 4.0    | -       | 0.6  | -    | μs   |  |  |

| Data hold time                                                                                     | t <sub>(HDDAT)</sub>  | -      | 3450    | -    | 900  | ns   |  |  |

| Data setup time                                                                                    | t <sub>(SUDAT)</sub>  | 250    | -       | 100  | -    | ns   |  |  |

| I <sup>2</sup> C clock (SCK) low period                                                            | t <sub>(LOW)</sub>    | 4.7    | -       | 1.3  | -    | μs   |  |  |

| I <sup>2</sup> C clock (SCK) high period                                                           | t <sub>(HIGH)</sub>   | 4.0    | -       | 0.6  | -    | μs   |  |  |

| Clock / data fall time                                                                             | t <sub>f</sub>        | -      | 300     | -    | 300  | ns   |  |  |

| Clock / data rise time                                                                             | t <sub>r</sub>        | -      | 1000    | -    | 300  | ns   |  |  |

### PARAMETER TIMING INFORMATION

www.vishay.com

ISHAY

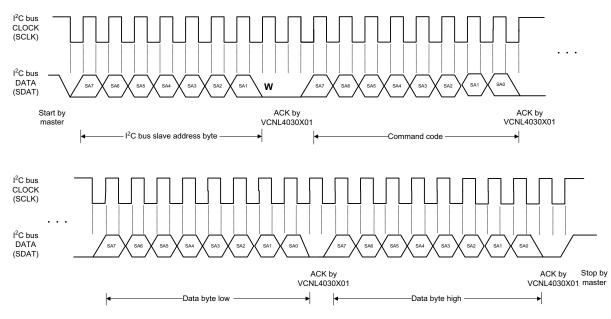

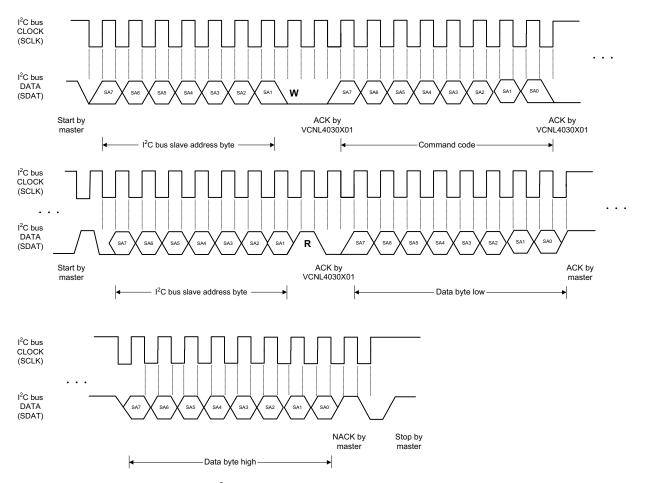

Fig. 3 - I<sup>2</sup>C Bus Timing for Sending Word Command Format

Fig. 4 - I<sup>2</sup>C Bus Timing for Receiving Word Command Format

## **TYPICAL PERFORMANCE CHARACTERISTICS** ( $T_{amb} = 25 \text{ °C}$ , unless otherwise specified)

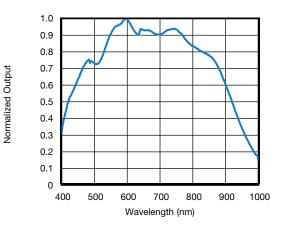

Fig. 6 - Normalized Spectral Response (PS channel)

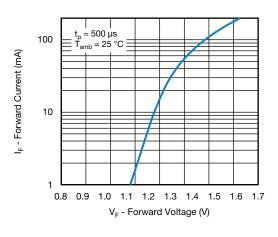

Fig. 7 - Forward Current  $I_F = f(V_F)$  for LED

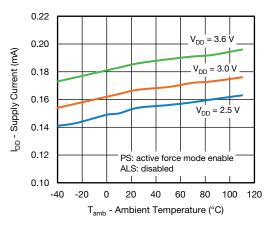

Fig. 8 - Supply Current vs. Ambient Temperature With Only PS = Active

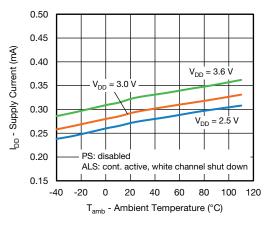

Fig. 9 - Supply Current vs. Ambient Temperature With Only ALS = Active

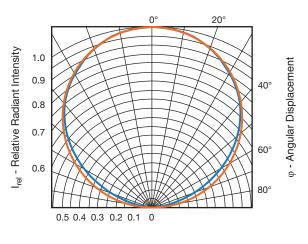

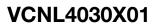

Fig. 10 - Relative Radiant Intensity Emitter vs. Angular Displacement

Rev. 1.3, 07-Jul-2023

7 For technical questions, contact: <u>sensorstechsupport@vishay.com</u> Document Number: 84250

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

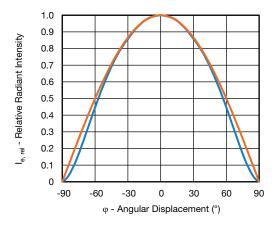

Fig. 11 - Relative Radiant Intensity Emitter vs. Angular Displacement

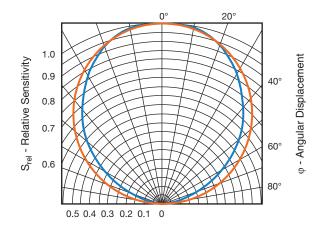

Fig. 12 - Relative Sensitivity vs. Angular Displacement (ALS)

Fig. 13 - Relative Sensitivity vs. Angular Displacement

Fig. 14 - White Channel Spectral Response

Fig. 15 - Proximity Value vs. Distance to Reflecting Card

8

For technical questions, contact: <u>sensorstechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

## **APPLICATION INFORMATION**

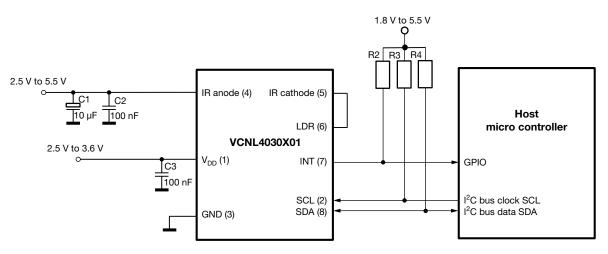

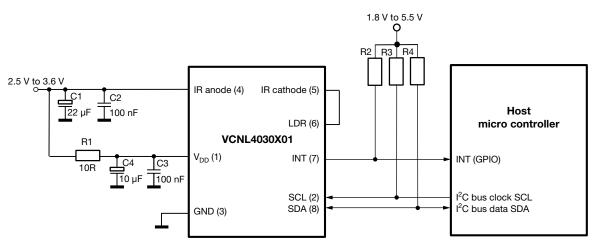

#### **Pin Connection with the Host**

VCNL4030X01 integrates proximity sensor, ambient light Sensor, and IRED all together with I<sup>2</sup>C interface. It is very easy for the baseband (CPU) to access PS and ALS output data via I<sup>2</sup>C interface without extra software algorithms. The hardware schematic is shown in the following diagram.

Two additional capacitors in the circuit can be used for the following purposes: (1) the 0.1 µF capacitor near the V<sub>DD</sub> pin is used for power supply noise rejection, (2) the 2.2 µF capacitor - connected to the anode - is used to prevent the IRED voltage from instantly dropping when the IRED is turned on, and (3) 2.2 k $\Omega$  is suitable for the pull up resistor of I<sup>2</sup>C except for the 8.2 k $\Omega$ applied on the INT pin.

#### Note

· IR cathode and LDR: pins need to be connected together externally

Fig. 16 - Circuitry with Two Separate Power Supply Sources

#### **Digital Interface**

VCNL4030X01 is available in four different salve addresses (0x60, 0x51, 0x40, and 0x41). Please refer to the table "Salve Address Options" at the beginning of the datasheet for an overview of the corresponding ordering codes. All operations can be controlled by the command register. The simple command structure helps users easily program the operation setting and latch the light data from VCNL4030X01. As Fig. 17 shows, VCNL4030X01's I<sup>2</sup>C command format is simple for read and write operations between VCNL4030X01 and the host. The white sections indicate host activity and the gray sections indicate VCNL4030X01's acknowledgement of the host access activity. Write word and read word protocol is suitable for accessing registers particularly for 16-bit data ALS and 12-bit / 16-bit PS data. Interrupt can be cleared by reading data out from register: INT\_Flag. All command codes should follow read word and write word protocols.

| Sen                     | nd Byte → Write Co                                                                         | mm    | and   | to VCNL4030X01 |       |      |                |     |     |      |               |   |   |                  |   |   |

|-------------------------|--------------------------------------------------------------------------------------------|-------|-------|----------------|-------|------|----------------|-----|-----|------|---------------|---|---|------------------|---|---|

| 1                       | 7                                                                                          | 1     | 1     | 8              | 1     |      | 8              | 1   |     |      | 8             | 1 | 1 |                  |   |   |

| s                       | Slave Address                                                                              | Wr    | A     | Command Code   | A     |      | Data Byte Low  | А   |     | Da   | ita Byte High | А | Ρ |                  |   |   |

|                         |                                                                                            |       |       |                |       |      |                |     |     |      |               |   |   |                  |   |   |

| Rec                     | ceive Byte $\rightarrow$ Read                                                              | Data  | a fro | om VCNL4030X01 |       |      |                |     |     |      |               |   |   |                  |   |   |

| 1                       | 7                                                                                          | 1     | 1     | 8              | 1     | 1    | 7              |     | 1   | 1    | 8             |   | 1 | 1 8              | 1 | 1 |

| s                       | Slave Address                                                                              | Wr    | А     | Command Code   | А     | s    | Slave Address  |     | Rd  | А    | Data Byte Lo  | w | 4 | A Data Byte High | Ν | Ρ |

| P = s<br>A = a<br>N = i | start condition<br>stop condition<br>acknowledge<br>no acknowledge<br>ded area = VCNL4030) | (01 a | ackn  | wledge         |       |      |                |     |     |      |               |   |   |                  |   |   |

|                         |                                                                                            |       |       | Ū              | 7 - V | Vrit | e Word and Rea | d V | /or | d Pi | rotocol       |   |   |                  |   |   |

#### **Function Description**

VCNL4030X01 applies a 16-bit high resolution ALS that provides the best ambient light sensing capability down to 0.004 lux/step which works well under a low transmittance lens design (dark lens). A flexible interrupt function of ALS (register: ALS\_CONF) is also supported. The INT signal will not be asserted by VCNL4030X01 if the ALS value is not over high INT threshold window level, or lower than low INT threshold window level of ALS. As long as the ALS INT is asserted, the host can read the data from VCNL4030X01. VCNL4030X01 detects different light sources such as fluorescent light, incandescent light, sunlight, and white LED with high accuracy ALS data output after detecting algorithm is implemented.

For proximity sensor function, VCNL4030X01 supports different kinds of mechanical designs to achieve the best proximity detection performance for any color of object with more flexibility. The basic PS function settings, such as duty ratio, integration time, interrupt, and PS enable / disable, and persistence, are handled by the register: PS\_CONF1. Duty ratio controls the PS response time. Integration time represents the duration of the energy being received. The interrupt is asserted when the PS detection levels over the high threshold level setting (register: PS\_THDH) or lower than low threshold (register: PS\_THDL). If the interrupt function is enabled, the host reads the PS output data from VCNL4030X01 that saves host loading from periodically reading PS data. More than that, INT flag (register: INT\_Flag) indicates the behavior of INT triggered under different conditions. PS persistence (PS\_PERS) sets up the PS INT asserted conditions as long as the PS output value continually exceeds the threshold level. The intelligent cancellation level can be set on register: PS\_CANC to reduce the cross talk phenomenon.

VCNL4030X01 also supports an easy use of proximity detection logic output mode that outputs just high / low levels saving loading from the host. Normal operation mode or proximity detection logic output mode can be selected on the register: PS\_MS. A smart persistence is provided to get faster PS response time and prevent false trigger for PS. Descriptions of each slave address operation are shown in table 1

www.vishay.com

| COMMAND<br>CODE | DATE BYTE<br>LOW / HIGH | REGISTER<br>NAME | R/W | DEFAULT<br>VALUE | FUNCTION DESCRIPTION                                                                                                                             |

|-----------------|-------------------------|------------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00            | L                       | ALS_CONF1        | R/W | 0x01             | ALS integration time, ALS dynamic range, persistence, interrupt, and function enable / disable                                                   |

|                 | Н                       | ALS_CONF2        | R/W | 0x01             | ALS sensitivity, white channel enable / disable                                                                                                  |

| 0x01            | L                       | ALS_THDH_L       | R/W | 0x00             | ALS high interrupt threshold LSB byte                                                                                                            |

| 0x01            | Н                       | ALS_THDH_M       | R/W | 0x00             | ALS high interrupt threshold MSB byte                                                                                                            |

| 0x02            | L                       | ALS_THDL_L       | R/W | 0x00             | ALS low interrupt threshold LSB byte                                                                                                             |

| 0x02            | Н                       | ALS_THDL_M       | R/W | 0x00             | ALS low interrupt threshold MSB byte                                                                                                             |

| 0x03            | L                       | PS_CONF1         | R/W | 0x01             | PS duty ratio, integration time, persistence, and PS enable / disable                                                                            |

| 0x03            | Н                       | PS_CONF2         | R/W | 0x00             | PS gain, PS output resolution, PS interrupt trigger                                                                                              |

| 0x04            | L                       | PS_CONF3         | R/W | 0x00             | PS smart persistence, active force mode                                                                                                          |

| 0x04            | Н                       | PS_MS            | R/W | 0x00             | LED current selection                                                                                                                            |

| 0x05            | L                       | PS_CANC_L        | R/W | 0x00             | PS cancellation level setting                                                                                                                    |

| 0x05            | Н                       | PS_CANC_M        | R/W | 0x00             | PS cancellation level setting                                                                                                                    |

| 0x06            | L                       | PS_THDL_L        | R/W | 0x00             | PS low interrupt threshold setting LSB byte                                                                                                      |

| 0x00            | Н                       | PS_THDL_M        | R/W | 0x00             | PS low interrupt threshold setting MSB byte                                                                                                      |

| 0x07            | L                       | PS_THDH_L        | R/W | 0x00             | PS high interrupt threshold setting LSB byte                                                                                                     |

| 0.07            | Н                       | PS_THDH_M        | R/W | 0x00             | PS high interrupt threshold setting MSB byte                                                                                                     |

| 0x08            | L                       | PS_Data_L        | R   | 0x00             | PS LSB output data                                                                                                                               |

| 0.000           | Н                       | PS_Data_M        | R   | 0x00             | PS MSB output data                                                                                                                               |

| 0x09            | L                       | Reserved         | R   | 0x00             | Reserved                                                                                                                                         |

| 0.09            | Н                       | Reserved         | R   | 0x00             | Reserved                                                                                                                                         |

| 0x0A            | L                       | Reserved         | R   | 0x00             | Reserved                                                                                                                                         |

| UXUA            | Н                       | Reserved         | R   | 0x00             | Reserved                                                                                                                                         |

| 0x0B            | L                       | ALS_Data_L       | R   | 0x00             | ALS LSB output data                                                                                                                              |

| UXUB            | Н                       | ALS_Data_M       | R   | 0x00             | ALS MSB output data                                                                                                                              |

| 0x0C            | L                       | White_Data_L     | R   | 0x00             | White LSB output data                                                                                                                            |

|                 | Н                       | White_Data_M     | R   | 0x00             | White MSB output data                                                                                                                            |

| 0x0D            | L                       | Reserved         | R   | 0x00             | Reserved                                                                                                                                         |

|                 | Н                       | INT_Flag         | R   | 0x00             | ALS, PS interrupt flags, PS sunlight protection mode flag                                                                                        |

|                 | L                       | ID_L             | R   | 0x80             | Device ID LSB                                                                                                                                    |

| 0x0E            | н                       | ID_M             | R   | 0x00             | For version with 0x60 as device address; 0x10 for version with 0x51, 0:<br>for version with 0x40 and 0x30 for version with 0x41 as device addres |

#### Note

• All of reserved register are used for internal test. Please keep as default setting

#### **Command Register Format**

VCNL4030X01 provides an 8-bit command register for ALS and PS controlling independently. The description of each command format is shown in following tables.

| TABLE 2 - RE  | TABLE 2 - REGISTER: ALS_CONF1 DESCRIPTION |                                           |                                                                                                                                                                                           |                |                |          |  |  |  |  |

|---------------|-------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------|--|--|--|--|

| REGISTER NAME |                                           | COMMAND CODE: 0x00_L (0x00 DATA BYTE LOW) |                                                                                                                                                                                           |                |                |          |  |  |  |  |

| Command       | Bit                                       | 7                                         | 7 6 5 4 3 2 1 0                                                                                                                                                                           |                |                |          |  |  |  |  |

|               |                                           | COMMAND CODE: 0x00_L (0x00 DATA BYTE LOW) |                                                                                                                                                                                           |                |                |          |  |  |  |  |

| Command       | Bit                                       |                                           | Description                                                                                                                                                                               |                |                |          |  |  |  |  |

| ALS_IT        | 7:5                                       |                                           | (0:0:0) = 50 ms; $(0:0:1) = 100$ ms; $(0:1:0) = 200$ ms; $(0:1:1) = 400$ ms; $(1:0:0)$ to $(1:1:1) = 800$ ms ALS integration time setting, longer integration time has higher sensitivity |                |                |          |  |  |  |  |

| ALS_HD        | 4                                         | 0 = typical                               | dynamic rang                                                                                                                                                                              | e x 1, 1 = typ | ical dynamic r | ange x 2 |  |  |  |  |

| ALS_PERS      | 3:2                                       |                                           | (0 : 0) = 1, (0 : 1) = 2, (1 : 0) = 4, (1 : 1) = 8<br>ALS interrupt persistence setting                                                                                                   |                |                |          |  |  |  |  |

| ALS_INT_EN    | 1                                         | 0 = ALS int                               | 0 = ALS interrupt disable, 1 = ALS interrupt enable                                                                                                                                       |                |                |          |  |  |  |  |

| ALS_SD        | 0                                         | 0 = ALS po                                | wer on, 1 = A                                                                                                                                                                             | LS shut dowr   | n, default = 1 |          |  |  |  |  |

11

www.vishay.com

# Vishay Semiconductors

| TABLE 3 - R                                | TABLE 3 - REGISTER: ALS_CONF2 DESCRIPTION |                                                                      |  |  |  |  |  |  |  |

|--------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|

| COMMAND CODE: 0x00_H (0x00 DATA BYTE HIGH) |                                           |                                                                      |  |  |  |  |  |  |  |

| Command                                    | Bit                                       | Description                                                          |  |  |  |  |  |  |  |

| Reserved                                   | 7:2                                       | Default = (0 : 0 : 0 : 0 : 0 : 0)                                    |  |  |  |  |  |  |  |

| ALS_NS                                     | 1                                         | 0 = typical sensitivity x 2, 1 = typical sensitivity x 1             |  |  |  |  |  |  |  |

| WHITE_SD                                   | 0                                         | 0 = WHITE channel power on, 1 = WHITE channel shut down, default = 1 |  |  |  |  |  |  |  |

| TABLE 4 - REGISTER ALS_THDH_L AND ALS_THDH_M DESCRIPTION |                                                                           |                                                       |  |  |  |  |  |  |

|----------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

|                                                          | COMMAND CODE: 0x01_L (0x01 DATA BYTE LOW) OR 0x01_H (0x01 DATA BYTE HIGH) |                                                       |  |  |  |  |  |  |

| Register Bit Description                                 |                                                                           |                                                       |  |  |  |  |  |  |

| ALS_THDH_L                                               | 7:0                                                                       | 0 0x00 to 0xFF, ALS high interrupt threshold LSB byte |  |  |  |  |  |  |

| ALS_THDH_M                                               |                                                                           |                                                       |  |  |  |  |  |  |

| TABLE 5 - REGISTER: ALS_THDL_L AND ALS_THDL_M DESCRIPTION |                                                                            |                                                    |  |  |  |  |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|

|                                                           | COMMAND CODE: 0x02_L (0x02 DATA BYTE LOW) AND 0x02_H (0x02 DATA BYTE HIGH) |                                                    |  |  |  |  |  |  |

| Register                                                  | Bit Description                                                            |                                                    |  |  |  |  |  |  |

| ALS_THDL_L                                                | 7:0                                                                        | 0x00 to 0xFF, ALS low interrupt threshold LSB byte |  |  |  |  |  |  |

| ALS_THDL_M                                                | 7:0                                                                        | 0x00 to 0xFF, ALS low interrupt threshold MSB byte |  |  |  |  |  |  |

| TABLE 6 - REGISTER: PS_CONF1 DESCRIPTION |      |                                                                                                                                                   |  |  |  |  |  |  |

|------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| REGISTER: PS_CO                          | ONF1 | COMMAND CODE: 0x03_L (0x03 DATA BYTE LOW)                                                                                                         |  |  |  |  |  |  |

| Command                                  | Bit  | Description                                                                                                                                       |  |  |  |  |  |  |

| PS_Duty                                  | 7:6  | (0 : 0) = 1/40, (0 : 1) = 1/80, (1 : 0) = 1/160, (1 : 1) = 1/320<br>PS IRED on / off duty ratio setting                                           |  |  |  |  |  |  |

| PS_PERS                                  | 5:4  | (0 : 0) = 1, (0 : 1) = 2, (1 : 0) = 3, (1 : 1) = 4<br>PS interrupt persistence setting                                                            |  |  |  |  |  |  |

| PS_IT                                    | 3:1  | (0:0:0) = 1T, (0:0:1) = 1.5T, (0:1:0) = 2T, (0:1:1) = 2.5T, (1:0:0) = 3T, (1:0:1) = 3.5T, (1:1:0) = 4T, (1:1:1) = 8T, PS integration time setting |  |  |  |  |  |  |

| PS_SD                                    | 0    | 0 = PS power on, 1 = PS shut down, default = 1                                                                                                    |  |  |  |  |  |  |

| TABLE 7 - REGISTER: PS_CONF2 DESCRIPTION |      |                                                                                                                            |  |  |  |  |  |  |

|------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| REGISTER: PS_C                           | ONF2 | COMMAND CODE: 0x03_H (0x03 DATA BYTE HIGH)                                                                                 |  |  |  |  |  |  |

| Command                                  | Bit  | Description                                                                                                                |  |  |  |  |  |  |

| Reserved                                 | 7:6  | : 0), reserved                                                                                                             |  |  |  |  |  |  |

| PS_Gain                                  | 5:4  | 0 : 0) and (0 : 1) = two step mode, (1 : 0) = single mode x 8, (1 : 1) = single mode x 1                                   |  |  |  |  |  |  |

| PS_HD                                    | 3    | = PS output is 12 bits, 1 = PS output is 16 bits                                                                           |  |  |  |  |  |  |

| PS_NS                                    | 2    | = typical sensitivity (two step mode x 4), 1 = typical sensitivity mode (two step mode)                                    |  |  |  |  |  |  |

| PS_INT                                   | 1:0  | (0 : 0) = interrupt disable, (0 : 1) = trigger by closing, (1 : 0)= trigger by away, (1 : 1) = trigger by closing and away |  |  |  |  |  |  |

www.vishay.com

# VCNL4030X01

# Vishay Semiconductors

| TABLE 8 - REGISTER: PS_CONF3 DESCRIPTION |     |                                                                                                                                                                                     |  |  |  |  |  |  |  |

|------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| REGISTER: PS_CO                          | NF3 | COMMAND CODE: 0x04_L (0x04 DATA BYTE LOW)                                                                                                                                           |  |  |  |  |  |  |  |

| Command                                  | Bit | Description                                                                                                                                                                         |  |  |  |  |  |  |  |

| LED_I_LOW                                | 7   | 0 = disabled = normal current, 1 = enabled = 1/10 of normal current,<br>with that the current is accordingly: 5 mA, 7.5 mA, 10 mA, 12 mA, 14 mA, 16 mA, 18 mA, 20 mA                |  |  |  |  |  |  |  |

| Reserved                                 | 6:5 | 0 : 0)                                                                                                                                                                              |  |  |  |  |  |  |  |

| PS_SMART_PERS                            | 4   | 0 = disable; 1 = enable PS smart persistence                                                                                                                                        |  |  |  |  |  |  |  |

| PS_AF                                    | 3   | = active force mode disable (normal mode), 1 = active force mode enable                                                                                                             |  |  |  |  |  |  |  |

| PS_TRIG                                  | 2   | = no PS active force mode trigger, 1 = trigger one time cycle<br>CNL4030X01 output one cycle data every time host writes in '1' to sensor.The state returns to '0'<br>tromatically. |  |  |  |  |  |  |  |

| PS_MS                                    | 1   | = proximity normal operation with interrupt function, 1 = proximity detection logic output mode enable                                                                              |  |  |  |  |  |  |  |

| PS_SC_EN                                 | 0   | 0 = turn off sunlight cancel; 1 = turn on sunlight cancel<br>PS sunlight cancel function enable setting                                                                             |  |  |  |  |  |  |  |

| TABLE 9 - R                                                | TABLE 9 - REGISTER: PS_MS DESCRIPTION |                                                                                                                                                                                                                 |  |  |  |  |  |

|------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| REGISTER: PS_MS COMMAND CODE: 0x04_H (0x04 DATA BYTE HIGH) |                                       |                                                                                                                                                                                                                 |  |  |  |  |  |

| Command                                                    | Command Bit Description               |                                                                                                                                                                                                                 |  |  |  |  |  |

| Reserved                                                   | 7                                     | 0                                                                                                                                                                                                               |  |  |  |  |  |

| PS_SC_CUR                                                  | 6:5                                   | : 0) = 1 x typical sunlight cancel current, (0 : 1) = 2 x typical sunlight cancel current,<br>: 0) = 4 x typical sunlight cancel current, (1 : 1) = 8 x typical sunlight cancel current                         |  |  |  |  |  |

| PS_SP                                                      | 4                                     | 0 = typical sunlight capability, 1 = 1.5 x typical sunlight capability                                                                                                                                          |  |  |  |  |  |

| PS_SPO                                                     | 3                                     | = output is 00h in sunlight protect mode, 1 = output is FFh in sunlight protect mode,                                                                                                                           |  |  |  |  |  |

| LED_I                                                      | 2:0                                   | (0 : 0 : 0) = 50 mA; (0 : 0 : 1) = 75 mA; (0 : 1 : 0) = 100 mA; (0 : 1 : 1) = 120 mA<br>(1 : 0 : 0) = 140 mA; (1 : 0 : 1) = 160 mA; (1 : 1 : 0) = 180 mA; (1 : 1 : 1) = 200 mA<br>LED current selection setting |  |  |  |  |  |

| TABLE 10 - REGISTER PS_CANC_L AND PS_CANC_M DESCRIPTION |                                                                            |                                                      |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|--|

|                                                         | COMMAND CODE: 0x05_L (0x05 DATA BYTE LOW) AND 0x05_H (0x05 DATA BYTE HIGH) |                                                      |  |  |  |  |  |

| Register Bit Description                                |                                                                            |                                                      |  |  |  |  |  |

| PS_CANC_L                                               | _CANC_L 7:0 0x00 to 0xFF, PS cancellation level setting_LSB byte           |                                                      |  |  |  |  |  |

| PS_CANC_M                                               | 7:0                                                                        | 0x00 to 0xFF, PS cancellation level setting_MSB byte |  |  |  |  |  |

| TABLE 11 - REGISTER: PS_THDL_L AND PS_THDL_M DESCRIPTION |                                                                            |                                                           |  |  |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

|                                                          | COMMAND CODE: 0x06_L (0x06 DATA BYTE LOW) AND 0x06_H (0x06 DATA BYTE HIGH) |                                                           |  |  |  |  |  |  |

| Register                                                 | Bit                                                                        | Description                                               |  |  |  |  |  |  |

| PS_THDL_L                                                | 7:0                                                                        | 00 to 0xFF, PS interrupt low threshold setting_LSB byte   |  |  |  |  |  |  |

| PS_THDL_M                                                | 7:0                                                                        | 0x00 to 0xFF, PS interrupt low threshold setting_MSB byte |  |  |  |  |  |  |

| TABLE 12 - REGISTER: PS_THDH_L AND PS_THDH_M DESCRIPTION |                                                                            |                                                          |  |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

|                                                          | COMMAND CODE: 0x07_L (0x07 DATA BYTE LOW) AND 0x07_H (0x07 DATA BYTE HIGH) |                                                          |  |  |  |  |  |

| Register                                                 | Bit                                                                        | Description                                              |  |  |  |  |  |

| PS_THDH_L                                                | 7:0                                                                        | 00 to 0xFF, PS interrupt high threshold setting_LSB byte |  |  |  |  |  |

| PS_THDH_M                                                | THDH_M 7:0 0x00 to 0xFF, PS interrupt high threshold setting_MSB byte      |                                                          |  |  |  |  |  |

Rev. 1.3, 07-Jul-2023

13

Document Number: 84250

For technical questions, contact: <u>sensorstechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

| TABLE 13 - READ OUT REGISTER DESCRIPTION |                              |                                      |                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------------------------------|------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Register                                 | Command Code                 | Bit                                  | Description                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| PS_Data_L                                | 0x08_L (0x08 data byte low)  | 7:0                                  | 0x00 to 0xFF, PS1 LSB output data                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| PS_Data_M                                | 0x08_H (0x08 data byte high) | 7:0                                  | 0x00 to 0xFF, PS1 MSB output data                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Reserved                                 | 0x09_L (0x09 data byte low)  | 7:0                                  | Reserved                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Reserved                                 | 0x09_H (0x09 data byte high) | 7:0                                  | Reserved                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Reserved                                 | 0x0A_L (0x0A data byte low)  | 7:0                                  | Reserved                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Reserved                                 | 0x0A_H (0x0A data byte high) | 7:0                                  | Reserved                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| ALS_Data_L                               | 0x0B_L (0x0B data byte low)  | 7:0                                  | 0x00 to 0xFF, ALS LSB output data                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| ALS_Data_M                               | 0x0B_H (0x0B data byte high) | 7:0                                  | 0x00 to 0xFF, ALS MSB output data                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| White_Data_L                             | 0x0C_L (0x0C data byte low)  | 7:0                                  | 0x00 to 0xFF, white LSB output data                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| White_Data_M                             | 0x0C_H (0x0C data byte high) | 7:0                                  | 0x00 to 0xFF, white LSB output data                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Reserved                                 | 0x0D_L (0x0D data byte low)  | 7:0                                  | Default = 0x00                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| INT_Flag                                 | 0x0D_H (0x0D data byte high) | 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | Reserved<br>Reserved<br>ALS_IF_L, ALS crossing low THD INT trigger event<br>ALS_IF_H, ALS crossing high THD INT trigger event<br>Reserved<br>PS_SPFLAG, PS entering sunlight protection mode<br>PS_IF_CLOSE, PS rises above PS_THDH INT trigger event<br>PS_IF_AWAY, PS drops below PS_THDL INT trigger event |  |  |  |  |  |  |

| ID_L                                     | 0x0E_H (0x0E data byte low)  | 7:0                                  | 0x80                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                                          |                              | 7:6                                  | (0:0)                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| ID_M                                     | 0x0E_H (0x0E data byte high) | 5:4                                  | $\begin{array}{l} (0:0) = \text{slave address} = 0x60 \ (7\text{-bit}) \\ (0:1) = \text{slave address} = 0x51 \ (7\text{-bit}) \\ (1:0) = \text{slave address} = 0x40 \ (7\text{-bit}) \\ (1:1) = \text{slave address} = 0x41 \ (7\text{-bit}) \end{array}$                                                   |  |  |  |  |  |  |

|                                          |                              | 3:0                                  | Version code (0 : 0 : 0 : 0)                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

#### Adjustable Sampling Time

VCNL4030X01's embedded LED driver drives the internal IRED with the "LDR" pin by a pulsed duty cycle. The IRED on / off duty ratio is programmable by I<sup>2</sup>C command at register: PS\_Duty which is related to the current consumption and PS response time. The higher the duty ratio adopted, the faster response time achieved with higher power consumption. For example, PS\_Duty = 1/320, peak IRED current = 100 mA, averaged current consumption is 100 mA/320 = 0.3125 mA.

#### Initialization

VCNL4030X01 includes default values for each register. As long as power is on, it is ready to be controlled by host via I<sup>2</sup>C bus.

#### Threshold Window Setting

• ALS Threshold Window Setting (Applying ALS INT)

Register: ALS\_THDH\_L and ALS\_THDH\_M defines 16-bit ALS high threshold data for LSB byte and MSB byte. Register: ALS\_THDL\_L and ALS\_THDL\_M defines 16-bit ALS low threshold data for LSB byte and MSB byte. As long as ALS INT function is enabled, INT will be asserted once the ALS data exceeds ALS\_THDH or goes below ALS\_THDL. To easily define the threshold range, multiply the value of the resolution (lux/step) by the threshold level (refer to table 14).

| TABLE 14 - ALS RESOLUTION AND MAXIMUM DETECTION RANGE |                            |                   |                            |  |  |  |  |  |  |

|-------------------------------------------------------|----------------------------|-------------------|----------------------------|--|--|--|--|--|--|

| AL                                                    | S_IT                       | SENSITIVITY       | MAXIMUM DETECTION<br>RANGE |  |  |  |  |  |  |

| ALS_IT<br>(7 : 5)                                     | INTEGRATION TIME<br>(typ.) | UNIT<br>(lx/step) | UNIT<br>(lx)               |  |  |  |  |  |  |

| (0, 0, 0)                                             | 50 ms                      | 0.064             | 4192                       |  |  |  |  |  |  |

| (0, 0, 1)                                             | 100 ms                     | 0.032             | 2096                       |  |  |  |  |  |  |

| (0, 1, 0)                                             | 200 ms                     | 0.016             | 1048                       |  |  |  |  |  |  |

| (0, 1, 1)                                             | 400 ms                     | 0.008             | 524                        |  |  |  |  |  |  |

| (1, 0, 0) to (1, 1, 1)                                | 800 ms                     | 0.004             | 262                        |  |  |  |  |  |  |

• ALS HD and ALS\_NS

These two options enhance the dynamic range by a factor of two each. With this the sensitivity shown within table 14 will be reduced by the factor 2, but the maximum possible detection range will be doubled for both options. With this the max. detection range goes up to 4192 kx 2 x 2 = 16768 kx

ALS Persistence

The ALS INT is asserted as long as the ALS value is higher or lower than the threshold window when ALS\_PERS (1, 2, 4, 8 times) is set to one time. If ALS\_PERS is set to four times, then the ALS INT will not be asserted if the ALS value is not over (or lower) than the threshold window for four continued refresh times (integration time)

• Programmable PS Threshold

VCNL4030X01 provides both high and low thresholds for PS (register: PS\_THDL, PS\_THDH)

PS Persistence

The PS persistence function (PS\_PERS, 1, 2, 3, 4) helps to avoid false trigger of the PS INT. For example, if PS\_PERS = 3 times, the PS INT will not be asserted unless the PS value is greater than the PS threshold (PS\_THDH) value for three periods of time continuously

• PS Active Force mode

An extreme power saving way to use PS is to apply PS active force (register: PS\_CONF3 command: PS\_FOR = 1) mode. Anytime host would like to read out just one of PS data, write in '1' at register: PS\_CONF3 command: PS\_FOR\_Trig. Without commands placed, there is no PS data output. VCNL4030X01 stays in standby mode constantly

PS detection object

Any color of object is detectable by VCNL4030X01

#### Data Access

All of VCNL4030X01 command registers are readable. To access 16-bit high resolution ALS output data, it is suitable to use read word protocol to read out data by just one command at register: ALS\_DataL and ALS\_DataM. To represent the 16-bit data of ALS, it has to apply two bytes. One byte is for LSB, and the other byte is for MSB as shown in table 18. In terms of reading out 8-bit PS data, it is also very convenient to read PS at register: PS\_Data.

| TABLE 15 - 16-BIT ALS DATA FORMAT |    |    |    |       |       |    |   |       |        |   |   |      |       |   |   |   |

|-----------------------------------|----|----|----|-------|-------|----|---|-------|--------|---|---|------|-------|---|---|---|

|                                   |    |    |    |       |       |    |   | VCNL4 | 030X01 |   |   |      |       |   |   |   |

| Bit                               | 15 | 14 | 13 | 12    | 11    | 10 | 9 | 8     | 7      | 6 | 5 | 4    | 3     | 2 | 1 | 0 |

| Register                          |    |    |    | ALS_[ | DataM |    |   |       |        |   |   | ALS_ | DataL |   |   |   |

#### Intelligent Cancellation

VCNL4030X01 provides an intelligent cancellation method to reduce cross talk phenomenon for the proximity sensor. The output data will be subtracted by the input value on register: PS\_CANC.

#### Interruption (INT)

VCNL4030X01 has ALS and PS interrupt feature operated by a single pin "INT". The purpose of the interrupt feature is to actively inform the host once INT has been asserted. With the interrupt function applied, the host does not need to be constantly pulling data from the sensor, but to read data from the sensor while receiving interrupt request from the sensor. As long as the host enables ALS interrupt (register: ALS\_INT\_EN) or PS interrupt (register: PS\_INT) function, the level of INT pin (pin 7) is pulled low once INT asserted. All registers are accessible even if INT is asserted.

ALS INT asserted when ALS value cross over the value set by register: ALS\_THDH or lower than the value set by register: ALS\_THDL. To effectively adopt PS INT function, it is recommended to use PS detection mechanism at register: PS\_INTT = 1 for the best PS detection performance which can be adjusted by high / low THD level of PS. PS INT trigger way is defined by register: PS\_INT.

#### Interruption Flag

Register: INT\_Flag represents all of interrupt trigger status for ALS and PS. Any flag value changes from '0' to '1' state, the level of INT pin will be pulled low. As long as host reads INT\_Flag data, the bit will change from '1' state to '0' state after reading out, the INT level will be returned to high afterwards.

### **PROXIMITY DETECTION LOGIC OUTPUT MODE**

VCNL4030X01 provides a proximity detection logic output mode that uses INT pin (pin 7) as a proximity detection logic high / low output (register: PS\_MS). When this mode is selected, the PS output (pin 7; INT/P<sub>out</sub>) is pulled low when an object is closing to be detected and returned to level high when the object moves away. Register: PS\_THDH / PS\_THDL defines how sensitive PS detection is.

One thing to be stated is that whenever proximity detection logic mode applied, INT pin is only used as a logic high / low output. If host would like to use ALS with INT function, register:  $PS_MS$  has to be selected to normal operation mode ( $PS_MS = 0$ ). Meanwhile, host has to simulate the GPIO pin as an INT pin function. If not, host needs to periodically reading the state of INT at this GPIO pin.

#### **PROXIMITY DETECTION HYSTERESIS**

A PS detection hysteresis is important that keeps PS state in a certain range of detection distance. For example, PS INT asserts when PS value over PS\_THDH. Host switches off panel backlight and then clears INT. When PS value is less than PS\_THDL, host switches on panel backlight. Any PS value lower than PS\_THDH or higher than PS\_THDL, PS INT will not be asserted. Host does keep the same state.

### APPLICATION CIRCUIT BLOCK REFERENCE

Fig. 18 - Circuitry with Just One Common Power Supply Source

www.vishay.com

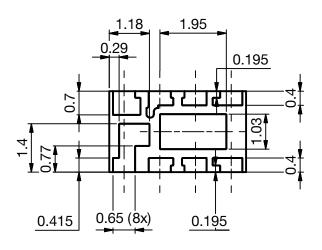

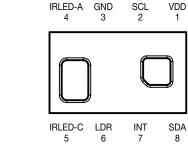

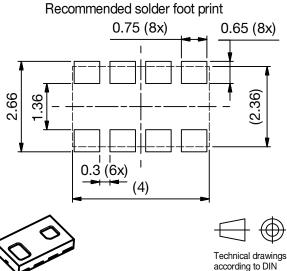

## **PACKAGE DIMENSIONS** in millimeters

Pinning Top View

1.05 (3x)

Drawing No.: 6.550-5326.01-4 Issue: 2, 27.07.2020

0.15

Not indicated tolerances  $\pm$  0.1 mm

according to DIN specification.

17

0.75

Non tolerated dimensions ± 0.1 mm

www.vishay.com

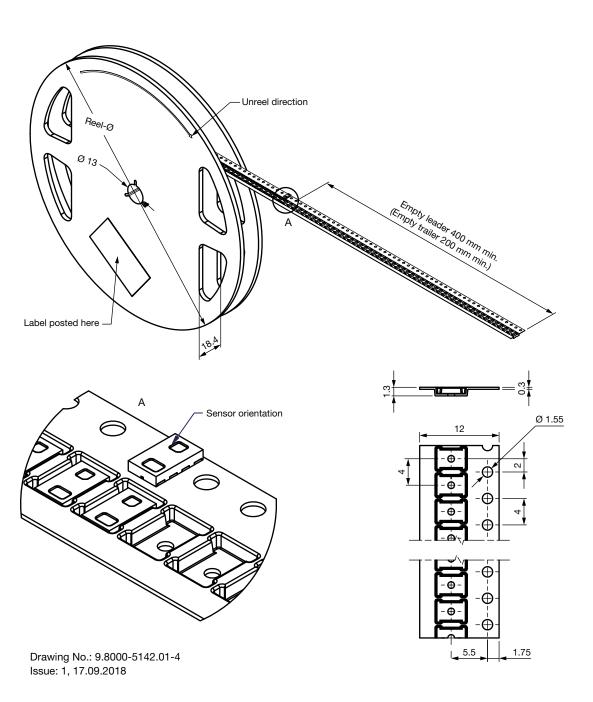

### TAPE AND REEL DIMENSIONS in millimeters

Reel-Size: GS 08: Ø 180 mm  $\pm$  2 mm = 3300 pcs. GS 18: Ø 330 mm  $\pm$  2 mm = 13 000 pcs. Reel-design is representative for different types

For technical questions, contact: <u>sensorstechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

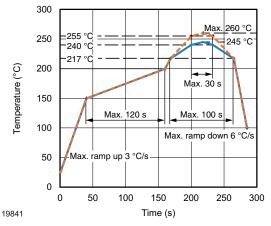

## SOLDER PROFILE

www.vishay.com

#### DRYPACK

Devices are packed in moisture barrier bags (MBB) to prevent the products from moisture absorption during transportation and storage. Each bag contains a desiccant.

### FLOOR LIFE

Floor life (time between soldering and removing from MBB) must not exceed the time indicated on MBB label:

Floor life: 168 h

Conditions:  $T_{amb}$  < 30 °C, RH < 60 %

Moisture sensitivity level 3, according to J-STD-020.

#### DRYING

In case of moisture absorption devices should be baked before soldering. Conditions see J-STD-020 or label. Devices taped on reel dry using recommended conditions 192 h at 40 °C (+ 5 °C), RH < 5 %.

Vishay

# Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.