### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

### **General Description**

**Features**

DeepCover® embedded security solutions cloak sensitive data under multiple layers of advanced physical security to provide the most secure key storage possible.

The DeepCover Secure Authenticator (DS2465) is a SHA-256 coprocessor with built-in 1-Wire® master that provides the SHA-256 and memory functionality required by a host system to communicate with and operate a 1-Wire SHA-256 slave. In addition, it performs protocol conversion between the I<sup>2</sup>C master and any attached 1-Wire SHA-256 slaves. For 1-Wire line driving, internal user-adjustable timers relieve the system host processor from generating time-critical 1-Wire waveforms, supporting both standard and overdrive 1-Wire communication speeds. The 1-Wire line can be powered down under software control. Strong pullup features support 1-Wire power delivery to 1-Wire devices such as EEPROMs. When not in use, the DS2465 can be put in sleep mode where power consumption is minimal.

Ordering Information appears at end of data sheet.

♦ SHA-256 Engine to Operate a Symmetric-Key-Based Bidirectional Secure Authentication Model

- ♦ Two 32-Byte Pages of User EEPROM with Multiple Programmable Protection Options

- ◆ 1-Wire Master Port with Selectable Active or Passive 1-Wire Pullup

- ♦ Strong 1-Wire Pullup Provided by an Internal Low-Impedance Signal Path

- ♦ 1-Wire Port Can Be Powered Down Under Software Control

- ♦ I2C Operating (Pullup) Voltage: 3.3V ±10%

- ♦ ±8kV ESD Protection on IO to GND (JESD22-A114 HBM, Typical)

- ♦ Operating Range: 3.3V ±10%, -40°C to +85°C

- ♦ 6-Pin TSOC Package

#### **Applications**

Authentication of Consumables Secure Feature Control

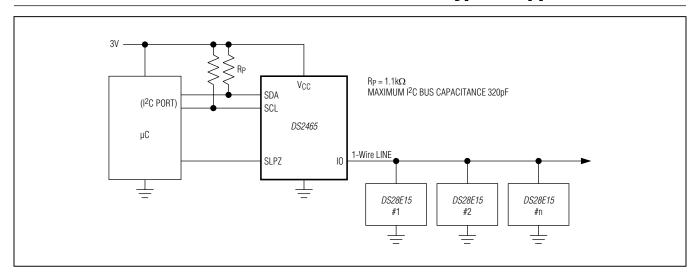

### **Typical Application Circuit**

DeepCover and 1-Wire are registered trademarks of Maxim Integrated Products, Inc.

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to GND0.5V to +4.0V | Storage Temperature Range55°C to +125°C |

|-------------------------------------------------------|-----------------------------------------|

| Maximum Current into Any Pin20mA                      | Lead Temperature (soldering, 10s)+300°C |

| Operating Temperature Range40°C to +85°C              | Soldering Temperature (reflow)+260°C    |

| Junction Temperature+150°C                            |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                          | SYMBOL            | CONDITIONS                                         | MIN                      | TYP                        | MAX                      | UNITS |  |

|------------------------------------|-------------------|----------------------------------------------------|--------------------------|----------------------------|--------------------------|-------|--|

| Supply Voltage                     | V <sub>CC</sub>   |                                                    | 2.97                     | 3.3                        | 3.63                     | V     |  |

| Control of Comment                 |                   | (Note 2)                                           |                          |                            | 750                      |       |  |

| Supply Current                     | Icc               | Sleep mode (SLPZ pin low), V <sub>CC</sub> = 3.63V |                          | 0.5                        | 1.0                      | μΑ    |  |

| Power-On Reset Trip Point          | V <sub>POR</sub>  | (Note 3)                                           |                          | 1.0                        | 1.4                      | V     |  |

| 1-Wire Input High                  | V <sub>IH1</sub>  |                                                    | 0.6 x<br>V <sub>CC</sub> |                            |                          | V     |  |

| 1-Wire Input Low                   | V <sub>IL1</sub>  |                                                    |                          |                            | 0.2 x<br>V <sub>CC</sub> | V     |  |

| 1-Wire Weak Pullup Resistor        | D                 | Low range                                          | 375                      | 500                        | 750                      | Ω     |  |

| (Notes 3, 4)                       | R <sub>WPU</sub>  | High range                                         | 750                      | 1000                       | 1350                     | 22    |  |

| 1-Wire Output Low                  | V <sub>OL1</sub>  | V <sub>CC</sub> = 2.97V, 8mA sink current          |                          |                            | 0.25                     |       |  |

| Active Pullup On Threshold         | V <sub>IAPO</sub> | (Note 3)                                           |                          | 0.95                       | 1.2                      | V     |  |

|                                    | t <sub>APU</sub>  | 1-Wire time slot                                   |                          | Equal to t <sub>REC0</sub> |                          |       |  |

| Active Pullup On Time (Notes 3, 5) |                   | 1-Wire reset standard speed                        | 2.375                    | 2.5                        | 2.625                    | 5 µs  |  |

|                                    |                   | 1-Wire reset overdrive speed                       | 0.475                    | 0.5                        | 0.525                    |       |  |

| Active Pullup Impedance            | R <sub>APU</sub>  | V <sub>CC</sub> = 2.97V, 4mA load (Note 3)         |                          |                            | 60                       | Ω     |  |

| 1-Wire Output Fall Time (Note 3)   |                   | Standard 0.25                                      |                          |                            | 1                        |       |  |

| 1-Wire Output Fall Time (Note 3)   | t <sub>F</sub>    | Overdrive                                          | 0.05                     |                            | 0.2                      | μs    |  |

| IO PIN: 1-Wire TIMING (Note 6)     |                   |                                                    |                          |                            |                          |       |  |

| Depart Law Times                   |                   | Standard                                           | F.0/                     | See                        | . 00/                    |       |  |

| Reset Low Time                     | <sup>t</sup> RSTL | Overdrive                                          | -5%                      | Table 6                    | +9%                      | μs    |  |

| Reset High Time                    | t <sub>RSTH</sub> | Standard and overdrive                             | 1                        | Equal to t <sub>Rs</sub>   | STL                      | μs    |  |

| December 1                         |                   | Standard                                           | F0/                      | See                        | . 00/                    |       |  |

| Presence-Detect Sample Time        | t <sub>MSP</sub>  | Overdrive                                          | -5%                      | Table 6                    | +9%                      | μs    |  |

|                                    |                   | Standard                                           | 7.6                      | 8                          | 8.72                     |       |  |

| Sampling for Short and Interrupt   | tsı               | Overdrive                                          | 1.9                      | 2                          | 2.18                     | μs    |  |

|                                    |                   | Standard                                           | 7.6                      | 8                          | 8.72                     |       |  |

| Write-1/Read Low Time              | t <sub>W1L</sub>  | Overdrive                                          | -5%                      | See<br>Table 6             | +9%                      | μs    |  |

## **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                                                                                                    | SYMBOL            | CONDITIONS                            | MIN                       | TYP                    | MAX                    | UNITS |

|--------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|---------------------------|------------------------|------------------------|-------|

| Dood Cample Tir                                                                                              |                   | Standard                              | 11.4                      | 12                     | 13.1                   |       |

| Read Sample Time                                                                                             | tMSR              | Overdrive                             | 1.4                       | 1.5                    | 1.64                   | μs    |

| Write-0 Low Time                                                                                             | <b>.</b>          | Standard                              | E9/                       | See                    | . 00/                  |       |

| Write-o Low Time                                                                                             | twoL              | Overdrive                             | -5%                       | Table 6                | +9%                    | μs    |

| Write-0 Recovery Time                                                                                        | t <sub>REC0</sub> | Standard and overdrive                | -5%                       | See<br>Table 6         | +9%                    | μs    |

| 1-Wire Time Slot                                                                                             | t <sub>slot</sub> | Standard and overdrive                | Equa                      | al to t <sub>WOL</sub> | + t <sub>REC0</sub>    | μs    |

| SHA-256 ENGINE                                                                                               |                   |                                       |                           |                        |                        |       |

| Computation Current                                                                                          | ICSHA             | Defeate the full det                  | a abaat                   |                        |                        | mA    |

| Computation Time                                                                                             | tCSHA             | Refer to the full dat                 | a Sneet.                  |                        |                        | ms    |

| EEPROM                                                                                                       |                   |                                       |                           |                        |                        |       |

| Programming Current                                                                                          | I <sub>PROG</sub> | (Notes 3, 7)                          |                           |                        | 2                      | mA    |

| Programming Time for a 32-Bit Segment                                                                        | t <sub>PROG</sub> |                                       |                           |                        | 10                     | ms    |

| Write/Erase Cycling Endurance                                                                                | N <sub>CY</sub>   | T <sub>A</sub> = +85°C (Notes 8, 9)   | 100k                      |                        |                        | _     |

| Data Retention                                                                                               | t <sub>DR</sub>   | T <sub>A</sub> = +85°C (Notes 10, 11) | 10                        |                        |                        | Years |

| SLPZ PIN                                                                                                     | 1                 |                                       |                           |                        |                        |       |

| Low Level Input Voltage                                                                                      | V <sub>IL</sub>   |                                       | -0.5                      |                        | 0.3 x V <sub>CC</sub>  | V     |

| High Level Input Voltage                                                                                     | V <sub>IH</sub>   |                                       | 0.7 x<br>V <sub>CC</sub>  |                        | V <sub>CC</sub> + 0.5V | V     |

| Input Leakage Current                                                                                        | l <sub>l</sub>    | Pin at 3.63V (Note 3)                 |                           |                        | 0.1                    | μΑ    |

| Wake-Up Time from Sleep Mode                                                                                 | tswup             | (Note 12)                             |                           |                        | 200                    | μs    |

| I <sup>2</sup> C SCL AND SDA PINS (Note 13                                                                   |                   |                                       |                           |                        |                        |       |

| Low Level Input Voltage                                                                                      | V <sub>IL</sub>   |                                       | -0.5                      |                        | 0.3 x V <sub>CC</sub>  | V     |

| · · · · · · · · ·                                                                                            |                   |                                       | 0.7 x                     |                        | V <sub>CC(MAX)</sub>   | .,    |

| High Level Input Voltage                                                                                     | V <sub>IH</sub>   |                                       | V <sub>CC</sub>           |                        | + 0.5V                 | V     |

| Hysteresis of Schmitt Trigger Inputs                                                                         | V <sub>HYS</sub>  | (Note 3)                              | 0.05 x<br>V <sub>CC</sub> |                        |                        | V     |

| Low Level Output Voltage at 3mA<br>Sink Current                                                              | V <sub>OL</sub>   |                                       |                           |                        | 0.4                    | V     |

| Output Fall Time from V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> with a Bus Capacitance from 10pF to 400pF | t <sub>OF</sub>   | (Note 3)                              | 60                        |                        | 250                    | ns    |

| Pulse Width of Spikes That Are<br>Suppressed by the Input Filter                                             | t <sub>SP</sub>   | (Note 3)                              |                           |                        | 50                     | ns    |

| Input Current with an Input<br>Voltage Between 0.1V <sub>CC(MAX)</sub><br>and 0.9V <sub>CC(MAX)</sub>        | II                | (Notes 3, 14)                         | -10                       |                        | +10                    | μΑ    |

### **DS2465**

## DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) \text{ (Note 1)}$

| PARAMETER                                                                                         | SYMBOL              | CONDITIONS        | MIN | TYP | MAX | UNITS |

|---------------------------------------------------------------------------------------------------|---------------------|-------------------|-----|-----|-----|-------|

| Input Capacitance                                                                                 | C <sub>I</sub>      | (Note 3)          |     |     | 10  | pF    |

| SCL Clock Frequency                                                                               | f <sub>SCL</sub>    |                   | 0   |     | 400 | kHz   |

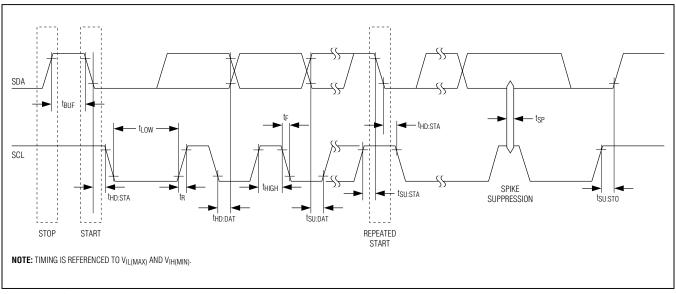

| Hold Time (Repeated) START<br>Condition; After this Period, the<br>First Clock Pulse is Generated | <sup>†</sup> HD:STA | (Note 3)          | 0.6 |     |     | μs    |

| Low Period of the SCL Clock                                                                       | t <sub>LOW</sub>    | (Note 3)          | 1.3 |     |     | μs    |

| High Period of the SCL Clock                                                                      | tHIGH               | (Note 3)          | 0.6 |     |     | μs    |

| Setup Time for a Repeated START Condition                                                         | t <sub>SU:STA</sub> | (Note 3)          | 0.6 |     |     | μs    |

| Data Hold Time                                                                                    | t <sub>HD:DAT</sub> | (Notes 3, 15, 16) |     |     | 0.9 | μs    |

| Data Setup Time                                                                                   | t <sub>SU:DAT</sub> | (Notes 3, 17)     | 250 |     |     | ns    |

| Setup Time for STOP Condition                                                                     | tsu:sto             | (Note 3)          | 0.6 |     |     | μs    |

| Bus Free Time Between a STOP and START Condition                                                  | t <sub>BUF</sub>    | (Note 3)          | 1.3 |     |     | μs    |

| Capacitive Load for Each Bus Line                                                                 | C <sub>B</sub>      | (Notes 3, 18)     |     |     | 400 | pF    |

| Oscillator Warmup Time                                                                            | toscwup             | (Note 12)         |     |     | 200 | μs    |

- **Note 1:** Limits are 100% production tested at  $T_A = +25^{\circ}C$  and/or  $T_A = +85^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.

- **Note 2:** Operating current with 1-Wire write byte sequence followed by continuous read of 1-Wire Master Status register at 400kHz in overdrive.

- **Note 3:** Guaranteed by design and/or characterization only. Not production tested.

- **Note 4:** Active pullup or resistive pullup and range are configurable.

- Note 5: The active pullup does not apply to the rising edge of a presence pulse outside of a 1-Wire Reset Pulse command or during the recovery after a short on the 1-Wire line.

- Note 6: All 1-Wire timing specifications are derived from the same timing circuit.

- Note 7: Current drawn from V<sub>CC</sub> during the EEPROM programming interval or SHA-256 computation.

- Note 8: Write-cycle endurance is tested in compliance with JESD47G.

- Note 9: Not 100% production tested; guaranteed by reliability monitor sampling.

- Note 10: Data retention is tested in compliance with JESD47G.

- **Note 11:** Guaranteed by 100% production test at elevated temperature for a shorter time; equivalence of this production test to the data sheet limit at operating temperature range is established by reliability testing.

- Note 12: I<sup>2</sup>C communication should not take place for the max t<sub>OSCWUP</sub> or t<sub>SWUP</sub> time following a power-on reset or a wake-up from sleep mode.

- Note 13: All I<sup>2</sup>C timing values are referred to  $V_{IH(MIN)}$  and  $V_{IL(MAX)}$  levels.

- Note 14: I/O pins of the DS2465 do not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- Note 15: The DS2465 provides a hold time of at least 300ns for the SDA signal (referenced to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 16: The maximum t<sub>HD:DAT</sub> has only to be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the setup time before it releases the clock (I<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

- Note 17: A fast-mode I²C bus device can be used in a standard-mode I²C-bus system, but the requirement t<sub>SU:DAT</sub> ≥ 250ns must then be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line t<sub>R(MAX)</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns (according to the standard-mode I²C bus specification) before the SCL line is released. Also the acknowledge timing must meet this setup time (I²C bus specification Rev. 03, 19 June 2007).

- Note 18:  $C_B$  = Total capacitance of one bus line in pF. The maximum bus capacitance allowable may vary from this value depending on the actual operating voltage and frequency of the application (I<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

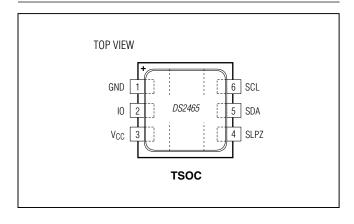

#### **Pin Configuration**

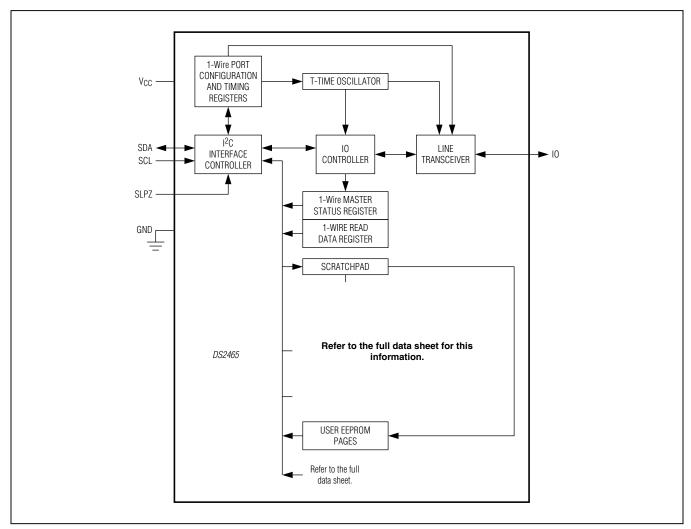

### **Detailed Description**

1-Wire master and two pages of user memory.

#### Refer to the full data sheet for this information.

The DS2465 is a SHA-256 coprocessor with built-in

### **Pin Description**

| PIN   | NAME            | FUNCTION                                                                                                                                                                             |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND             | Ground Reference                                                                                                                                                                     |

| 2     | 10              | I/O Driver for 1-Wire Line                                                                                                                                                           |

| 3     | V <sub>CC</sub> | Power-Supply Input                                                                                                                                                                   |

| 4     | SLPZ            | Active-Low Control Input. Activates the low-power sleep mode and issues a device reset of the SHA-coprocessor and the 1-Wire master (equivalent to the 1-Wire Master Reset command). |

| 5 SDA |                 | I <sup>2</sup> C Serial-Data Input/Output. Must be connected to V <sub>CC</sub> through a pullup resistor.                                                                           |

| 6     | SCL             | I <sup>2</sup> C Serial-Clock Input. Must be connected to V <sub>CC</sub> through a pullup resistor.                                                                                 |

The self-timed 1-Wire master function supports advanced 1-Wire waveform features including standard and overdrive speeds, active pullup, and strong pullup for power delivery. The active pullup affects rising edges on the 1-Wire side. The strong pullup function uses the same pullup transistor as the active pullup, but with a different control algorithm. Once supplied with command and data, the input/output controller of the DS2465 performs time-critical 1-Wire communication functions such as reset/presence-detect cycle, read-byte, write-byte, single-bit R/W, and triplet for ROM Search, without requiring interaction with the host processor. The host obtains feedback (completion of a 1-Wire function, presence pulse, 1-Wire short, and search direction taken) through the 1-Wire Master Status register and data through the 1-Wire Read Data register. All registers, the user memory and a scratchpad are located in a linear address space for direct access. The DS2465 communicates with a host processor through its I<sup>2</sup>C bus interface in standard mode or in fast mode. See Figure 1 for a block diagram.

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

Figure 1. Block Diagram

#### **Memory**

<u>Figure 2</u> shows the memory organization of the DS2465. The memory begins at address 00h with the input scratchpad. The register section follows at address 60h. Addresses 00 to 6F

are implemented as volatile SRAM. The 1-Wire port configuration settings have default values that are loaded automatically during power-on. The address range 70h and higher is non-

volatile. It contains factory-programmed device identification data, a personality byte, and the user memory pages.

Refer to the full data sheet for this information.

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

| ADDRESS<br>RANGE | TYPE     | ACCESS         | DESCRIPTION                                 |

|------------------|----------|----------------|---------------------------------------------|

| 00h to 4Bh       | SRAM     | R/W            | Input scratchpad                            |

| 4Ch to 5Fh       | _        | _              | (Reserved)                                  |

| 60h              | _        | W              | Command register                            |

| 61h              | SRAM     | R              | 1-Wire Master Status register               |

| 62h              | SRAM     | R              | 1-Wire Read Data register                   |

|                  | 1        | Refer to the 1 | full data sheet.                            |

| 66h              | <u> </u> | _              | (Reserved)                                  |

| 67h              | SRAM     | R/W            | 1-Wire Master Configuration register        |

| 68h              | SRAM     | R/W            | 1-Wire Port Configuration t <sub>RSTL</sub> |

| 69h              | SRAM     | R/W            | 1-Wire Port Configuration t <sub>MSP</sub>  |

| 6Ah              | SRAM     | R/W            | 1-Wire Port Configuration tWOL              |

| 6Bh              | SRAM     | R/W            | 1-Wire Port Configuration t <sub>REC0</sub> |

| 6Ch              | SRAM     | R/W            | 1-Wire Port Configuration RWPU              |

| 6Dh              | SRAM     | R/W            | 1-Wire Port Configuration Overdrive tw1L    |

| 6Eh to 6Fh       | _        | _              | (Reserved)                                  |

| 70h              | ROM      | R              | Factory byte                                |

|                  | ı        | Refer to the f | full data sheet.                            |

| 73h              | ROM      | R              | Personality byte                            |

| 74h to 7Fh       |          | _              | (Reserved)                                  |

| 80h to 9Fh       | EEPROM   | (R)/(W)        | User memory page 0                          |

| A0h to BFh       | EEPROM   | (R)/(W)        | User memory page 1                          |

| C0h to FFh       | _        | _              | (Reserved)                                  |

Figure 2. Memory Map

### **Device Registers**

The registers of the DS2465 fall into three categories: write-only, read-only and read/write. Write-only applies to the command register. Status registers, the 1-Wire read data register , are read-only. The configuration registers can be read and written; they also have defined power-on default settings. The factory byte, Manufacturer ID, and Personality byte are read-only.

#### **Command Register (60h)**

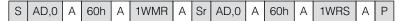

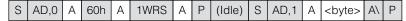

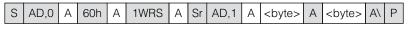

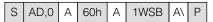

To execute a 1-Wire function, the DS2465 needs to receive a command from the I<sup>2</sup>C host. Commands are written one at a time to the Command register. Most commands consist of a command code and a parameter byte. The command code indicates the type of instruction and the position of the read pointer for the next I<sup>2</sup>C read-access. See section *Function Commands* for details.

### **DS2465**

## DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

#### 1-Wire Master Status Register (61h)

The 1-Wire Master Status register is the general means for the DS2465 to report bit-type data from the 1-Wire side, 1-Wire busy status, and its own reset status to the host processor (Table 1). All 1-Wire communication commands and the 1-Wire Master Reset command position the read pointer at the Status register for the host processor to read with minimal protocol overhead. Status information is updated during the execution of certain commands only. Details are given in the description of the various status bits that follow.

#### **Table 1. 1-Wire Master Status Bit Assignment**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DIR   | TSB   | SBR   | RST   | LL    | SD    | PPD   | 1WB   |

**Bit 7: Branch Direction Taken (DIR).** Whenever a 1-Wire Triplet command is executed, this bit reports to the host processor the search direction that was chosen by the third bit of the triplet. The power-on default of DIR is 0. This bit is updated only with a 1-Wire Triplet command and has no function with other commands. For additional information, see the description of the 1-Wire Triplet command and Application Note 187: 1-Wire Search Algorithm.

**Bit 6: Triplet Second Bit (TSB).** The TSB bit reports the logic state of the active 1-Wire line sampled at t<sub>MSR</sub> of the second bit of a 1-Wire Triplet command. The power-on default of TSB is 0. This bit is updated only with a 1-Wire Triplet command and has no function with other commands.

**Bit 5: Single Bit Result (SBR).** The SBR bit reports the logic state of the active 1-Wire line sampled at t<sub>MSR</sub> of a 1-Wire Single Bit command or the first bit of a 1-Wire Triplet command. The power-on default of SBR is 0. If the 1-Wire Single Bit command sends a 0 bit, SBR should be 0. With a 1-Wire Triplet command, SBR could be 0 as well as 1, depending on the response of the 1-Wire devices connected. The same result applies to a 1-Wire Single Bit command that sends a 1 bit

**Bit 4: Device Reset (RST).** If the RST bit is 1, the DS2465 has performed an internal reset cycle, either caused by a power-on reset, a low pulse at SLPZ, or from executing the Device Reset command. The RST bit is cleared automatically when the 1-Wire Master Configuration register is updated by the host processor.

**Bit 3: Logic Level (LL).** The LL bit reports the logic state of the active 1-Wire line without initiating any 1-Wire communication. The 1-Wire line is sampled for this purpose every time the 1-Wire Master Status register is read. The sampling and updating of the LL bit takes place when the host processor has addressed the DS2465 in read mode (during the acknowledge cycle), provided that the read pointer is positioned at the 1-Wire Master Status register.

**Bit 2: Short Detected (SD).** The SD bit is updated with every 1-Wire Reset command. If the DS2465 detects a logic 0 on the 1-Wire line at t<sub>Sl</sub> during the presence-detect cycle, the SD bit is set to 1. This bit returns to its default 0 with a subsequent 1-Wire Reset command provided that the short has been removed.

**Bit 1: Presence-Pulse Detect (PPD).** The PPD bit is updated with every 1-Wire Reset command. If the DS2465 detects a presence pulse from a 1-Wire device at t<sub>MSP</sub> during the presence-detect cycle, the PPD bit is set to 1. This bit returns to its default 0 if there is no presence pulse or if the 1-Wire line is shorted during a subsequent 1-Wire Reset command.

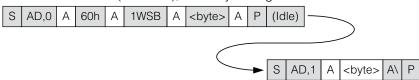

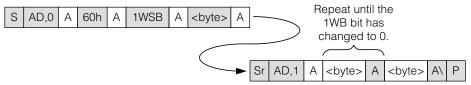

**Bit 0: 1-Wire Busy (1WB).** The 1WB bit reports to the host processor whether the 1-Wire line is busy. During 1-Wire communication 1WB is 1; once the command is completed, 1WB returns to its default 0. Details on when 1WB changes state and for how long it remains at 1 are found in the *Function Commands* section.

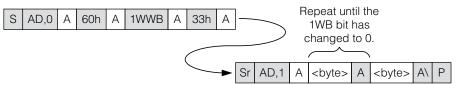

#### 1-Wire Read Data Register (62h)

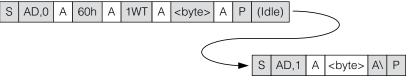

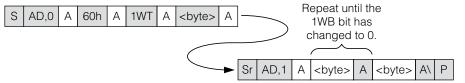

When the DS2465 completes a 1-Wire Read Byte command, it puts the data read from the 1-Wire slave into the 1-Wire Read Data register. While the command is being executed, the I<sup>2</sup>C host checks the 1WB bit in the 1-Wire Master Status register. When the 1-Wire line is no longer busy, the I<sup>2</sup>C host performs a dummy write to address 62h and then accesses the DS2465 in read mode to read the data byte.

### **DS2465**

## DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

#### 1-Wire Master Configuration Register (67h)

The DS2465 supports four 1-Wire features that are enabled or selected through the 1-Wire Master Configuration register (Table 3). These features are: Active Pullup (APU), 1-Wire Power-Down (PDN), Strong Pullup (SPU), 1-Wire Speed (1WS). APU, SPU and 1WS can be selected in any combination. While APU and 1WS maintain their state, SPU returns to its inactive state as soon as the strong pullup has ended.

After a device reset (power-up cycle, a low pulse at SLPZ, or initiated by the 1-Wire Master Reset command), the 1-Wire Master Configuration register reads 00h. When writing to the register, the new data is accepted only if the upper nibble (bits 7 to 4) is the one's complement of the lower nibble (bits 3 to 0). When read, the upper nibble is always 0h.

**Table 3. 1-Wire Master Configuration Bit Assignment**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 1WS   | SPU   | PDN   | ĀPŪ   | 1WS   | SPU   | PDN   | APU   |

**Bit 3: 1-Wire Speed (1WS).** The 1WS bit determines the timing of any 1-Wire communication generated by the DS2465. Most 1-Wire slave devices support standard speed (1WS = 0). Many 1-Wire devices can also communicate at a higher data rate, called overdrive speed. Some 1-Wire devices, including the DeepCover SHA-256 family of slave devices, only support overdrive and 1WS should always be programmed high for these devices. To change from standard to overdrive speed, a 1-Wire device needs to receive an Overdrive-Skip ROM or Overdrive-Match ROM command, as explained in the 1-Wire device data sheets. The change in speed occurs immediately after the 1-Wire device has received the speed-changing command code. The DS2465 must take part in this speed change to stay synchronized. This is accomplished by writing to the 1-Wire Master Configuration register with the 1WS bit as 1 immediately after the 1-Wire Byte command that changes the speed of a 1-Wire device. Writing to the 1-Wire Master Configuration register with the 1WS bit as 0, followed by a 1-Wire Reset command, changes the DS2465 and any 1-Wire devices on the active 1-Wire line back to standard speed.

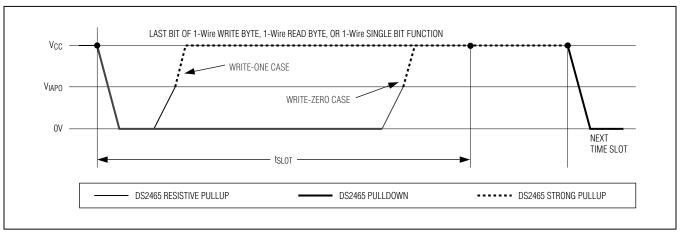

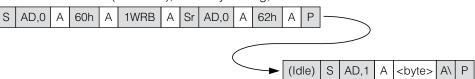

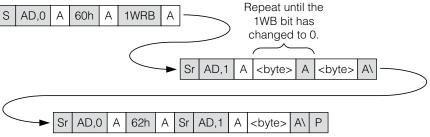

**Bit 2: Strong Pullup (SPU).** The SPU bit is used to activate the strong pullup function prior to a 1-Wire Write Byte, 1-Wire Read Byte, or 1-Wire Single Bit command. Strong pullup is commonly used with 1-Wire EEPROM devices when copying scratchpad data to the main memory or when performing a SHA computation. The respective device data sheets specify the location in the communications protocol after which the strong pullup should be applied. The SPU bit must be set immediately prior to issuing the command that puts the 1-Wire device into the state where it needs the extra power. The strong pullup uses the same internal pullup transistor as the active pullup feature. See the RAPU parameter in the <u>Electrical Characteristics</u> to determine whether the voltage drop is low enough to maintain the required 1-Wire voltage at a given load current and supply voltage.

If SPU is 1, the DS2465 treats the rising edge of the time slot in which the strong pullup starts as if the active pullup was activated. However, in contrast to the active pullup, the strong pullup, i.e., the internal pullup transistor, remains conducting, as shown in Figure 3, until one of four events occurs: the DS2465 receives a command that generates 1-Wire communication (the typical case); the SPU bit in the 1-Wire Master Configuration register is written to 0; the PDN bit in the 1-Wire Master Configuration register is written to 1; or the DS2465 receives the 1-Wire Master Reset command. When the strong pullup ends, the SPU bit is automatically reset to 0. Using the strong pullup feature does not change the state of the APU bit in the 1-Wire Master Configuration register.

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

Figure 3. Low-Impedance Pullup Timing

**Bit 1: 1-Wire Power-Down (PDN).** The PDN bit is used to remove power from the 1-Wire port, e.g., to force a 1-Wire slave to perform a power-on reset. PDN interacts with the sleep mode, which is controlled by the SLPZ pin (Table 4). The default state of PDN is 0, enabling normal operation. When PDN is changed to 1, no 1-Wire communication is possible. To end the 1-Wire power-down state, the PDN bit needs to be changed to 0. To exit the DS2465 from sleep mode, change the SLPZ pin state from 0 to 1. This forces the DS2465 to perform a power-on reset and clears PDN to 0 for normal operation.

Table 4. Interaction of PDN and SLPZ

|          | SLPZ PIN IS AT LOGIC 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SLPZ PIN IS AT LOGIC 1                                                                                                                                                |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PDN is 0 | R <sub>WPU</sub> is disconnected;    O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along to less name.   O is at 0 / coupling the along | <ul> <li>R<sub>WPU</sub> is connected;</li> <li>IO is at V<sub>CC</sub>, keeping the slaves powered.</li> <li>The DS2465 is powered up (normal operation).</li> </ul> |  |  |  |  |

| PDN is 1 | IO is at 0V, causing the slaves to lose power.  • The DS2465 is powered down (sleep mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>R<sub>WPU</sub> is disconnected;</li> <li>IO is at 0V, causing the slaves to lose power.</li> <li>The DS2465 is powered up.</li> </ul>                       |  |  |  |  |

**Bit 0: Active Pullup (APU).** The APU bit controls whether an active pullup (low impedance transistor) or a passive pullup (R<sub>WPU</sub> resistor) is used to drive a 1-Wire line from low to high. When APU = 0, active pullup is disabled (resistor mode). Enabling active pullup is generally recommended for best 1-Wire performance. The active pullup does not apply to the rising edge of a recovery after a short on the 1-Wire line. If enabled, a fixed-duration active pullup (nominally 2.5µs standard speed, 0.5µs overdrive speed) also applies in a reset/presence detect cycle on the rising edges after t<sub>RSTI</sub> and after t<sub>PDI</sub>.

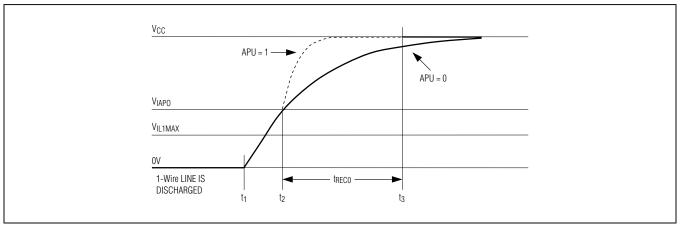

The circuit that controls rising edges (Figure 4) operates as follows: At  $t_1$ , the pulldown (from DS2465 or 1-Wire slave) ends. From this point on the 1-Wire line is pulled high through  $R_{WPU}$  internal to the DS2465.  $V_{CC}$  and the capacitive load of the 1-Wire line determine the slope. In case that active pullup is disabled (APU = 0), the resistive pullup continues, as represented by the solid line. With active pullup enabled (APU = 1), and when at  $t_2$  the voltage has reached the  $V_{IAPO}$  threshold, the DS2465 activates a low-impedance pullup transistor, as represented by the dashed line. The active pullup remains active until the end of the time slot ( $t_3$ ), after which the resistive pullup continues. The shortest duration of the active pullup is  $t_{REC0}$  in a write-zero time slot and the longest duration is  $t_{WOL} + t_{REC0} - t_{W1L}$  in a write-one time slot. In a read data time slot, the active pullup duration is slave dependent. See the strong pullup (SPU) section for a way to keep the pullup transistor conducting beyond  $t_3$ .

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

Figure 4. Rising Edge Pullup During a Time Slot

#### 1-Wire Port Configurations

The DS2465 allows adapting several timing parameters and the pullup resistor to the application's needs. Each of these parameters has its own 1-Wire Port Configuration register, located in the address range from 68h to 6Dh (<u>Table 5</u>). For t<sub>RSTL</sub>, t<sub>MSP</sub> and t<sub>WOL</sub> the values for standard and overdrive speed can be adjusted independently. The lower nibble applies to standard speed, the upper nibble to overdrive speed. The t<sub>REC0</sub> and R<sub>WPU</sub> settings apply at both 1-Wire speeds. The parameter t<sub>W1L</sub> can be adjusted for overdrive speed only; the standard speed value us fixed. For t<sub>REC0</sub>, R<sub>WPU</sub> and t<sub>W1L</sub> the upper nibble has no function. See <u>Table 6</u> for the conversion between binary code and parameter value.

After a device reset (power-up cycle, a low pulse at SLPZ, or initiated by the 1-Wire Master Reset command), the 1-Wire Port Configuration registers are initialized to their default values. To change a port configuration, access the respective register in I<sup>2</sup>C write mode and provide the new code as data byte. Starting at address 68h all port configurations can be adjusted in a single write access. The new setting applies on the rising SCL edge of the data byte acknowledge bit, provided that the 1-Wire line is not busy (1WB = 0). The upper 4 bits of the registers at 6Bh to 6Dh are not used. They can be written, byte their value has no effect on the device operation.

**Table 5. 1-Wire Port Configuration Address Details**

| ADDRESS | BIT 7                     | BIT 6                      | BIT 5                                                | BIT 4                                  | BIT 3                                                          | BIT 2                     | BIT 1        | BIT 0 |  |

|---------|---------------------------|----------------------------|------------------------------------------------------|----------------------------------------|----------------------------------------------------------------|---------------------------|--------------|-------|--|

| 68h     |                           | t <sub>RSTL</sub> Overdriv | e Speed (OD)                                         | t <sub>RSTL</sub> Standard Speed (STD) |                                                                |                           |              |       |  |

| 69h     |                           | t <sub>MSP</sub> Overdriv  | e Speed (OD)                                         |                                        |                                                                | t <sub>MSP</sub> Standard | Speed (STD)  |       |  |

| 6Ah     |                           | t <sub>WOL</sub> Overdriv  | e Speed (OD)                                         |                                        | t <sub>WOL</sub> Standard Speed (STD)                          |                           |              |       |  |

| 6Bh     |                           | (not used, de              | default 0000b) t <sub>REC0</sub> (speed independent) |                                        |                                                                |                           |              |       |  |

| 6Ch     | (not used, default 0000b) |                            |                                                      |                                        | (not used, default 0000b) R <sub>WPU</sub> (speed independent) |                           |              |       |  |

| 6Dh     | (not used, default 0000b) |                            |                                                      |                                        |                                                                | t <sub>W1L</sub> Overdriv | e Speed (OD) |       |  |

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

Table 6. Conversion between parameter value code and typical parameter value

| PARAMETER VALUE CODE | t <sub>RS</sub> |    |     | SP<br>E IN µs | t <sub>W</sub> |     | t <sub>REC0</sub><br>VALUE IN µs | $R_{WPU}$ VALUE IN $\Omega$ | t <sub>W1L</sub><br>VALUE IN µs |

|----------------------|-----------------|----|-----|---------------|----------------|-----|----------------------------------|-----------------------------|---------------------------------|

|                      | STD             | OD | STD | OD            | STD            | OD  | STD, OD                          | STD, OD                     | OD                              |

| 0000b                | 440             | 44 | 58  | 5.5           | 52             | 5.0 | 2.5                              | 500                         | do not use                      |

| 0001b                | 460             | 46 | 58  | 5.5           | 54             | 5.5 | 2.5                              | 500                         | 0.25                            |

| 0010b                | 480             | 48 | 60  | 6.0           | 56             | 6.0 | 2.5                              | 500                         | 0.50                            |

| 0011b                | 500             | 50 | 62  | 6.5           | 58             | 6.5 | 2.5                              | 500                         | 0.75                            |

| 0100b                | 520             | 52 | 64  | 7.0           | 60             | 7.0 | 2.5                              | 500                         | 1.00                            |

| 0101b                | 540             | 54 | 66  | 7.5           | 62             | 7.5 | 2.5                              | 500                         | 1.25                            |

| 0110b                | 560             | 56 | 68  | 8.0           | 64             | 8.0 | 5.0                              | 1000                        | 1.50                            |

| 0111b                | 580             | 58 | 70  | 8.5           | 66             | 8.5 | 7.5                              | 1000                        | 1.75                            |

| 1000b                | 600             | 60 | 72  | 9.0           | 68             | 9.0 | 10.0                             | 1000                        | 2.00                            |

| 1001b                | 620             | 62 | 74  | 9.5           | 70             | 9.5 | 12.5                             | 1000                        | 2.25                            |

| 1010b                | 640             | 64 | 76  | 10.0          | 70             | 10  | 15.0                             | 1000                        | 2.50                            |

| 1011b                | 660             | 66 | 76  | 10.5          | 70             | 10  | 17.5                             | 1000                        | 2.75                            |

| 1100b                | 680             | 68 | 76  | 11.0          | 70             | 10  | 20.0                             | 1000                        | 3.00                            |

| 1101b                | 700             | 70 | 76  | 11.0          | 70             | 10  | 22.5                             | 1000                        | 3.25                            |

| 1110b                | 720             | 72 | 76  | 11.0          | 70             | 10  | 25.0                             | 1000                        | 3.50                            |

| 1111b                | 740             | 74 | 76  | 11.0          | 70             | 10  | 25.0                             | 1000                        | 3.75                            |

Note: The power-on default values are bold.

Factory Byte (70h)

This byte reads 55h.

Refer to the full data sheet for this information.

Personality Byte (73h)

This byte reads 00h.

**Function Commands**

The DS2465 understands

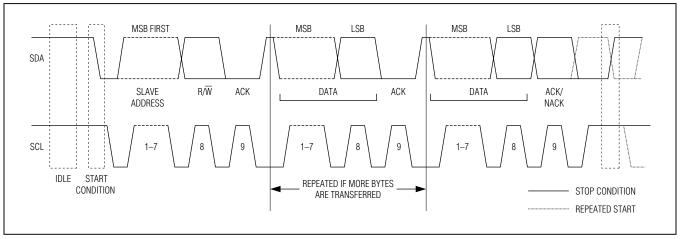

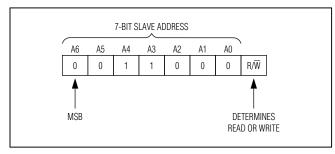

function commands. The feedback path to the host is controlled by a read pointer, which is set automatically by each function command for the host to efficiently access relevant information. The host processor sends these commands and applicable parameters as strings of one or two bytes using the I<sup>2</sup>C interface. The I<sup>2</sup>C protocol requires that each byte be acknowledged by the receiving party to confirm acceptance or not be acknowledged to indicate an error condition (invalid code or parameter) or to end the communication. See the I<sup>2</sup>C Interface section for details of the I<sup>2</sup>C protocol including acknowledge. The function commands are as follows:

Refer to the full data sheet for this information.

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

Refer to the full data sheet for this information.

The subsequent pages describe the function commands in a concise, table-like fashion.

| Copy Scratchpad                     |                                                                                                                                                                                                                                                  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Code                        | 5Ah                                                                                                                                                                                                                                              |

| Parameter Byte                      | Data destination, segment number (Table 7)                                                                                                                                                                                                       |

| Usage                               | Transferring scratchpad data to user EEPROM pages;                                                                                                                                                                                               |

| Other Notes                         | If the target memory is write-protected, this command cannot not complete successfully. Data is taken from the scratchpad location that corresponds to the segment number. Example: segment 0 corresponds to SP+0 to SP+3, addresses 00h to 03h. |

| Command Restrictions                | The data must first be written to the scratchpad. The target memory must not be write-protected (locked).                                                                                                                                        |

| Error Conditions (Error Response)   | If the target memory is write protected, the memory write cycles do not take place. In that case the device is not busy and acknowledges its I <sup>2</sup> C address immediately when accessed.                                                 |

| MAC Notes                           | Refer to the full data sheet.                                                                                                                                                                                                                    |

| I <sup>2</sup> C Busy Duration      | For 1 x t <sub>PROG</sub> or 8 x t <sub>PROG</sub> depending on the parameter byte, counted from the rising SCL edge of the parameter byte acknowledge bit.                                                                                      |

| Command Duration                    | I <sup>2</sup> C busy duration + 1.09µs                                                                                                                                                                                                          |

| 1-Wire Activity                     | None                                                                                                                                                                                                                                             |

| Read Pointer Position               | 1-Wire Master Status register                                                                                                                                                                                                                    |

| Master Status Bits Affected         | None                                                                                                                                                                                                                                             |

| Master Configurations Affected      | None                                                                                                                                                                                                                                             |

| 1-Wire Port Configurations Affected | None                                                                                                                                                                                                                                             |

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

#### **Table 7. Parameter Byte Bitmap**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| S/U   | X     | Т     | T     | F/S   | SEG#  |       |       |

X = Don't care

#### Refer to the full data sheet for this information.

Bits 5:4: Target (TT). These bits specify the user memory page number (S/U = 1) to which the scratchpad data is to be copied.

For S/U = 1, the assignments are:

- 00 User page 0

- 01 User page 1

- 10 (reserved)

- 11 (reserved)

**Bit 3: Full or segment copy (F/S).** This bit is relevant only is S/U = 1. It specifies whether the entire page is programmed or only the segment selected by SEG#. If F/S = 0, the entire page is programmed. If F/S = 1, only the selected segment is programmed. If one block of a targeted page is write protected then the F/S bit is forced to 1.

**Bits 2:0: Segment Number (SEG#).** These bits are relevant only if (S/U = 1) and (F/S = 1). They specify the segment of the selected user memory page to be programmed with scratchpad data. All codes are valid. The code 000b refers to the first four bytes of the page, etc.

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

| 1-Wire Master Reset                 |                                                                                                                                                          |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Code                        | F0h                                                                                                                                                      |

| Parameter Byte                      | N/A                                                                                                                                                      |

| Usage                               | Device initialization after power-up; re-initialization (reset) as desired.                                                                              |

| Other Notes                         | Performs a global reset of device state machine logic. Terminates any ongoing 1-Wire communication.                                                      |

| Command Restrictions                | The command must be followed by a 1-Wire Reset Pulse command.                                                                                            |

| Error Conditions (Error Response)   | None                                                                                                                                                     |

| MAC Notes                           | N/A                                                                                                                                                      |

| I <sup>2</sup> C Busy Duration      | None                                                                                                                                                     |

| Command Duration                    | Maximum 1.635µs. Counted from rising SCL edge of the command code acknowledge bit.                                                                       |

| 1-Wire Activity                     | Ends maximum 1.09µs after the rising SCL edge of the command code acknowledge bit.                                                                       |

| Read Pointer Position               | (N/A)                                                                                                                                                    |

| Master Status Bits Affected         | RST set to 1; 1WB, PPD, SD, SBR, TSB, DIR set to 0.                                                                                                      |

| Master Configurations Affected      | 1WS, APU, PDN, SPU set to 0.                                                                                                                             |

| 1-Wire Port Configurations Affected | t <sub>RSTL</sub> , t <sub>MSP</sub> , t <sub>W0L</sub> , t <sub>W1L</sub> , t <sub>REC0</sub> , and R <sub>WPU</sub> are reset to their default values. |

| 1-Wire Reset Pulse                  |                                                                                                                                                                                                                                                              |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Code                        | B4h                                                                                                                                                                                                                                                          |

| Parameter Byte                      | N/A                                                                                                                                                                                                                                                          |

| Usage                               | To initiate or end any 1-Wire communication sequence. To finish a 1-Wire Master Reset command.                                                                                                                                                               |

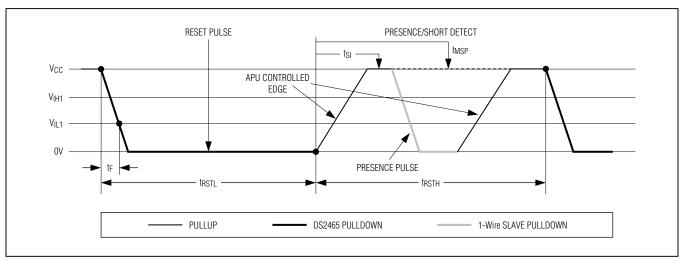

| Other Notes                         | Generates a 1-Wire reset/presence-detect cycle (Figure 5) at the 1-Wire line. The state of the 1-Wire line is sampled at $t_{SI}$ and $t_{MSP}$ and the result is reported to the host processor through the 1-Wire Master Status Register, bits PPD and SD. |

| Command Restrictions                | 1-Wire activity must have ended before the DS2465 can process this command.                                                                                                                                                                                  |

| Error Conditions (Error Response)   | Command code is not acknowledged if 1WB = 1 at the time the command code is received and the command is ignored.                                                                                                                                             |

| MAC Notes                           | N/A                                                                                                                                                                                                                                                          |

| I <sup>2</sup> C Busy Duration      | None                                                                                                                                                                                                                                                         |

| Command Duration                    | $2 \times t_{\mbox{RSTL}}$ + maximum 1.09µs, counted from the rising SCL edge of the command code acknowledge bit.                                                                                                                                           |

| 1-Wire Activity                     | Begins maximum 1.09µs after the rising SCL edge of the command code acknowledge bit.                                                                                                                                                                         |

| Read Pointer Position               | 1-Wire Master Status register (for busy polling).                                                                                                                                                                                                            |

| Master Status Bits Affected         | 1WB (set to 1 for 2 x $t_{RSTL}$ ), PPD is updated at $t_{RSTL}$ + $t_{MSP}$ , SD is updated at $t_{RSTL}$ + $t_{SI}$ .                                                                                                                                      |

| Master Configurations Affected      | 1WS and APU apply.                                                                                                                                                                                                                                           |

| 1-Wire Port Configurations Affected | t <sub>RSTL</sub> , t <sub>MSP</sub> , and R <sub>WPU</sub> current values apply.                                                                                                                                                                            |

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

Figure 5. 1-Wire Reset/Presence-Detect Cycle

| 1-Wire Single Bit                   |                                                                                                                                                                                      |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Code                        | 87h                                                                                                                                                                                  |

| Parameter Byte                      | Type of time slot (Table 21)                                                                                                                                                         |

| Usage                               | To perform single-bit writes or reads at the 1-Wire line when single bit communication is necessary (the exception).                                                                 |

| Other Notes                         | Generates a single 1-Wire time slot as specified by the parameter byte at the 1-Wire line; reads the logic level at the 1-Wire line at t <sub>MSR</sub> and updates SBR accordingly. |

| Command Restrictions                | 1-Wire activity must have ended before the DS2465 can process this command.                                                                                                          |

| Error Conditions (Error Response)   | Command code is not acknowledged if 1WB = 1 at the time the command code is received and the command is ignored.                                                                     |

| MAC Notes                           | N/A                                                                                                                                                                                  |

| I <sup>2</sup> C Busy Duration      | None                                                                                                                                                                                 |

| Command Duration                    | $t_{\mbox{SLOT}}$ + maximum 1.09 $\mu$ s, counted from the rising SCL edge of the parameter byte acknowledge bit.                                                                    |

| 1-Wire Activity                     | Begins maximum 1.09µs after the rising SCL edge of the parameter byte acknowledge bit.                                                                                               |

| Read Pointer Position               | 1-Wire Master Status register (for busy polling and data reading).                                                                                                                   |

| Master Status Bits Affected         | 1WB (set to 1 for t <sub>SLOT</sub> ), SBR is updated at t <sub>MSR</sub> , DIR (may change its state).                                                                              |

| Master Configurations Affected      | 1WS, APU, SPU apply.                                                                                                                                                                 |

| 1-Wire Port Configurations Affected | t <sub>WOL</sub> , t <sub>W1L</sub> , t <sub>REC0</sub> , and R <sub>WPU</sub> current values apply.                                                                                 |

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

**Table 21. Parameter Byte Bitmap**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| V     | X     | X     | X     | X     | X     | X     | X     |

X = Don't care

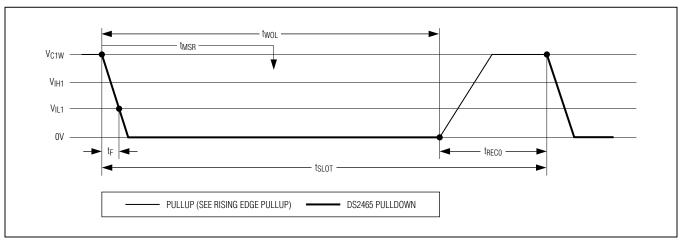

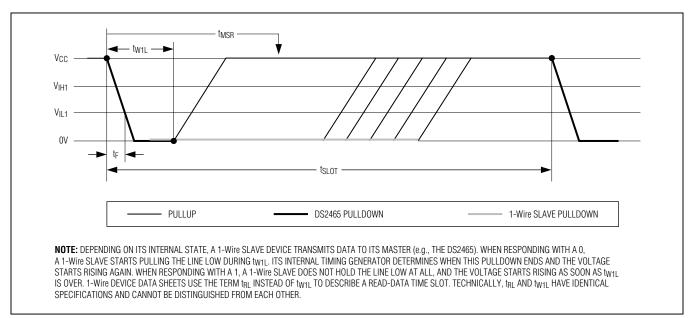

Bit 7: Bit value (V). This bit specifies the type of time slot to be generated. If V = 0, a write-zero time slot (Figure 6) is generated. If V = 1, a write-one time slot (Figure 7) is generated, which also functions as a read-data time slot.

Figure 6. Write-Zero Time Slot

Figure 7. Write-One and Read-Data Time Slot

### **DS2465**

# DeepCover Secure Authenticator with SHA-256 Coprocessor and 1-Wire Master Function

| 1-Wire Write Byte                   |                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Code                        | A5h                                                                                                                                                                                                                                                                                                                         |

| Parameter Byte                      | Data byte (Table 22)                                                                                                                                                                                                                                                                                                        |