# High Power Positive Hot-Swap Controller with Power Monitor via PMBus

### **FEATURES**

- ▶ Wide operating voltage range: 8.5 V to 80 V

- ▶ Monitors currents, voltages, and power with ADC

- Adjustable, 5% accurate current limit: 6 mV to 20 mV

- Current foldback limits MOSFET power dissipation for overstress protection

- Monitors V<sub>GS</sub> and V<sub>DS</sub> for MOSFET health

- ▶ Peak detect registers for current, voltage, and power

- ▶ Reports input or output power

- Remote temperature sensing with programmable warning and shutdown thresholds

- ▶ ±1% accurate, 12-bit ADC for I<sub>OUT</sub>, V<sub>IN</sub>, and V<sub>OUT</sub>

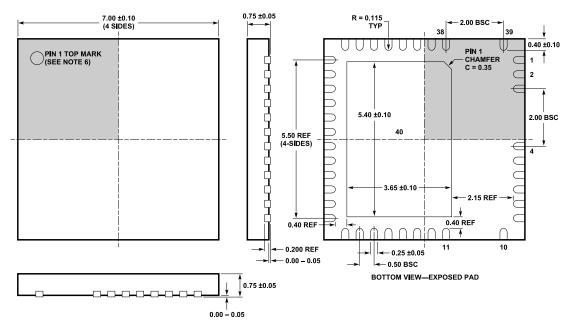

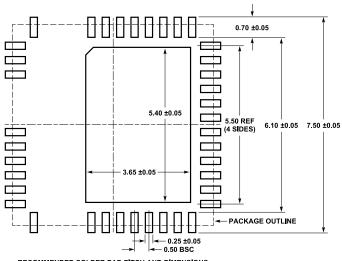

- ▶ Available in 39-lead, 7 mm x 7 mm, QFN package

#### **APPLICATIONS**

- ▶ High availability server backplane systems

- ▶ 12 V/24 V/48 V/54 V Distributed power systems

- Industrial

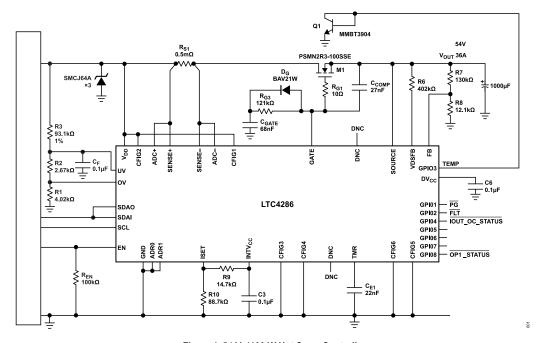

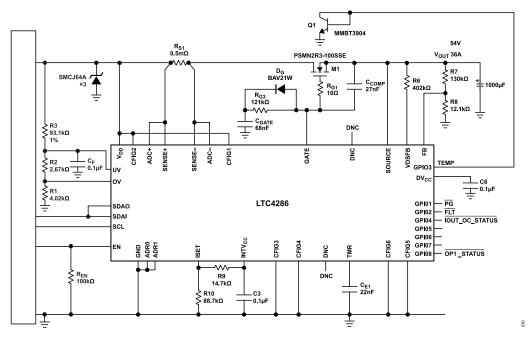

# **TYPICAL APPLICATION**

### **GENERAL DESCRIPTION**

The LTC4286 is an integrated solution for hot-swap applications allowing a board to be safely inserted and removed from a live backplane. The circuit breaker timer protects against metal-oxide semiconductor field-effect transistor (MOSFET) overheating, enabling reliable protection against overstress.

The SMBus 3.1 interface, PMBus command structure, and onboard analog-to-digital converter (ADC) with selectable averaging and speed allow monitoring of board current, voltage, power, temperature, and fault status.

The LTC4286 has additional features to respond to input undervoltage (UV) and overvoltage (OV): interrupts the host when a fault occurs, notifies when output power is good, detects insertion of a board, and auto-reboot after a programmable delay following a host commanded turn off.

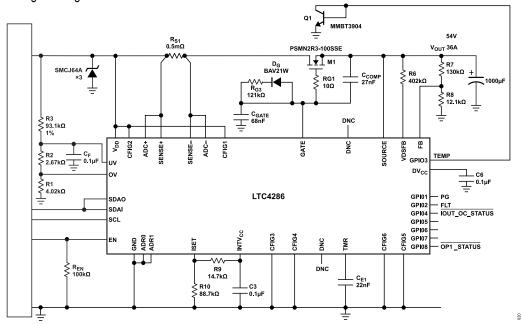

Figure 1. 54 V, 1100 W Hot-Swap Controller

# **TABLE OF CONTENTS**

| Features                                    | ′  |

|---------------------------------------------|----|

| Applications                                |    |

| General Description                         |    |

| Typical Application                         |    |

| Electrical Characteristics                  |    |

| Absolute Maximum Ratings                    |    |

| ESD Caution                                 |    |

| Pin Configuration and Function Descriptions |    |

| Typical Performance Characteristics         |    |

| Theory of Operation                         |    |

| Applications Information                    |    |

| Overview                                    |    |

| Turn-On Sequence                            | 16 |

| Turn-Off Sequence                           |    |

| MOSFET SOA-Timer Capacitor       | 16 |

|----------------------------------|----|

| Data Converters                  | 18 |

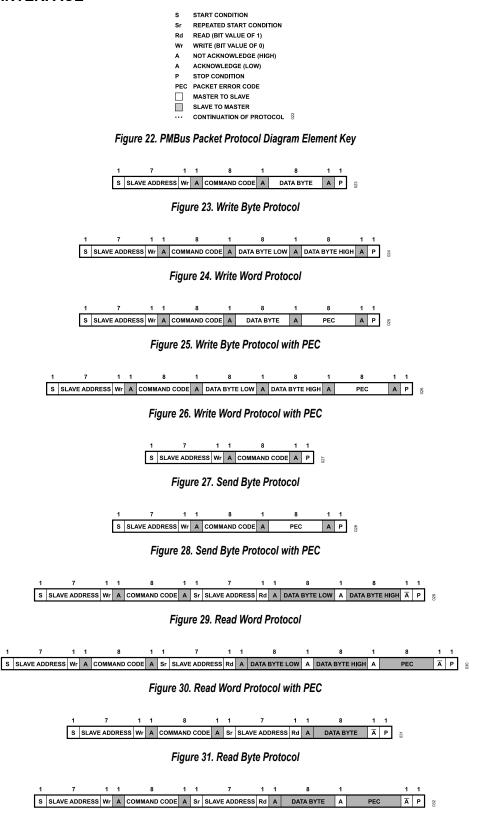

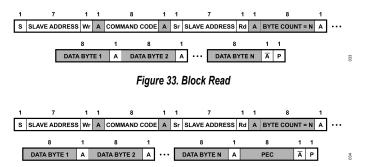

| SMBus Serial Interface           | 20 |

| PMBus Command Summary            | 22 |

| ADC-Related Commands and Aliases | 26 |

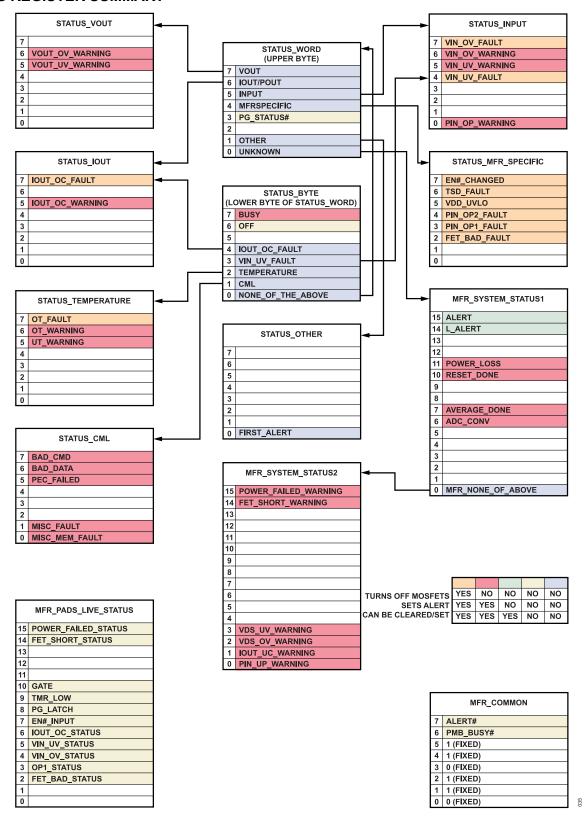

| Status Register Summary          | 29 |

| Latched Status and Mask Commands | 30 |

| GPIO Output Selection            | 40 |

| Typical Application              | 42 |

| Related Parts                    | 42 |

| Outline Dimensions               | 43 |

| Ordering Guide                   | 44 |

| Evaluation Boards                | 44 |

# **REVISION HISTORY**

1/2023—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 44

# **ELECTRICAL CHARACTERISTICS**

Specifications apply over the full operating temperature range, unless otherwise noted. All currents into pins are positive and all voltages are referenced to GND, unless otherwise specified.

Table 1. Electrical Characteristics

| Parameter                                                                                                                               | Test Conditions/Comments                                                                                                    | Min   | Тур   | Max             | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------|------|

| POWER SUPPLY                                                                                                                            |                                                                                                                             |       |       |                 |      |

| Input Supply Range, V <sub>DD</sub>                                                                                                     |                                                                                                                             | 8.5   |       | 80              | V    |

| Input Supply Current, I <sub>DD</sub>                                                                                                   | No external resistor $V_{\text{IN}}$ to $\text{INTV}_{\text{CC}}$ , no load on $\text{DV}_{\text{CC}}$                      |       | 12    | 18              | mA   |

|                                                                                                                                         | $5~\text{k}\Omega$ pull-up on INTV <sub>CC</sub> from V <sub>DD</sub> , 48 V, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V |       | 1.8   |                 | mA   |

| Input Supply Undervoltage Lockout, V <sub>DD(UVLO)</sub>                                                                                | V <sub>DD</sub> rising                                                                                                      | 5.75  | 6     | 6.35            | V    |

|                                                                                                                                         | V <sub>DD</sub> falling                                                                                                     | 5.25  | 5.5   | 5.85            | V    |

| Input Supply Undervoltage Lockout Hysteresis, $\Delta V_{DD(HYST)}$                                                                     | $T_A = 25^{\circ}C, V_{DD} = 48 \text{ V}$                                                                                  |       | 0.5   |                 | V    |

| INTV <sub>CC</sub> Output Voltage, INTV <sub>CC</sub>                                                                                   | $V_{DD}$ = 8.5 V and 80 V, $I_{LOAD}$ = 0 mA and –4 mA                                                                      | 4.5   | 5     | 5.5             | V    |

| INTV <sub>CC</sub> Undervoltage Lockout, INTV <sub>CC(UVLO)</sub>                                                                       | INTV <sub>CC</sub> falling                                                                                                  | 3.4   | 3.89  | 4.45            | V    |

|                                                                                                                                         | INTV <sub>CC</sub> rising                                                                                                   | 3.6   | 4     | 4.5             | V    |

| $\begin{array}{l} \text{INTV}_{\text{CC}} \text{ Undervoltage Lockout Hysteresis,} \\ \Delta \text{INTV}_{\text{CC(UVLO)}} \end{array}$ | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                                               |       | 115   |                 | mV   |

| DV <sub>CC</sub> Output Voltage, DV <sub>CC</sub>                                                                                       | V <sub>DD</sub> = 8.5 V, 80 V, I <sub>LOAD</sub> = 0 mA                                                                     | 4.5   | 5     | 5.5             | V    |

| DV <sub>CC</sub> Undervoltage Lockout, DV <sub>CC(UVLO)</sub>                                                                           | DV <sub>CC</sub> falling                                                                                                    | 1.7   | 2     | 2.5             | V    |

|                                                                                                                                         | DV <sub>CC</sub> rising                                                                                                     | 1.9   | 2.2   | 2.5             | V    |

| DV <sub>CC</sub> Undervoltage Lockout Hysteresis,                                                                                       | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                                               |       | 150   |                 | mV   |

| GATE DRIVE                                                                                                                              |                                                                                                                             |       |       |                 |      |

| External N-Channel Gate Drive at GATE (V <sub>GATE</sub> – $V_{SOURCE}$ ), $\Delta V_{GATE}^{-1}$                                       | $V_{DD}$ = 8.5 V to 80 V, $I_{GATE}$ = 0 $\mu A$ and $-10 \mu A$                                                            | 10    | 12    | 14              | V    |

| GATE Pull-Up Current, I <sub>GATE(UP)</sub>                                                                                             | Gate drive on, V <sub>GATE</sub> = V <sub>SOURCE</sub> = 0 V                                                                | -35   | -53   | <del>-</del> 70 | μA   |

| GATE Pull-Down Current, I <sub>GATE(DN)</sub>                                                                                           | Gate drive on, V <sub>GATE</sub> = 58 V, V <sub>SOURCE</sub> = 48 V                                                         |       | 12    | 15              | mA   |

| GATE Fast Pull-Down Current, I <sub>GATE(FST)</sub>                                                                                     | Fast turn off, V <sub>GATE</sub> = 58 V, V <sub>OUT</sub> = 48 V, T <sub>A</sub> = 25°C, V <sub>DD</sub>                    |       | 1     |                 | Α    |

| Gate-Source Voltage for FET-Bad and Power-Failed Faults, V <sub>TH(GS)</sub>                                                            |                                                                                                                             | 6     | 8     | 10              | V    |

| ΔSENSE High to GATE Low Propagation Delay,  †PHL(SENSE)                                                                                 | ILIM = 0000, $\Delta V_{SNS}$ = 0 to 100 mV step, $\Delta V_{GATE}$ = 6 V, $C_{GATE}$ = 10 nF,                              |       | 0.5   | 1               | μs   |

| GATE Off Propagation Delay: OV, t <sub>PHL(GATE)OV</sub>                                                                                | OV = high, ΔV <sub>GATE</sub> = 6 V gate open                                                                               |       | 1     | 2               | μs   |

| GATE ON Propagation Delay:OV, t <sub>PHL(GATE)OV</sub>                                                                                  | OV = low                                                                                                                    | 0     | 5     | 10              | μs   |

| GATE Off Propagation Delay: UV, t <sub>PHL(GATE)UV</sub>                                                                                | UV = low, ΔV <sub>GATE</sub> = 6 V gate open                                                                                | 0.3   | 2     | 3               | μs   |

| GATE Off Propagation Delay: EN, t <sub>PHL(GATE)EN</sub>                                                                                | EN = low, ΔV <sub>GATE</sub> = 6 V gate open                                                                                | 15    | 40    | 70              | μs   |

| $V_{DD}$ to Source Threshold Voltage for Power Bad Faults, $V_{DS(POWER\_BAD)}$                                                         | V <sub>DD</sub> to source falling                                                                                           | 1.6   | 2.0   | 2.4             | V    |

| FET Bad Fault Threshold (VDD-SOURCE) to start FETBAD timer, V <sub>TH,FET-BAD</sub>                                                     | V <sub>DD</sub> to source rising                                                                                            | 140   | 200   | 260             | mV   |

| TIMING                                                                                                                                  |                                                                                                                             |       |       |                 |      |

| Power-Good Delay, t <sub>DL(PG)</sub>                                                                                                   |                                                                                                                             | 172   | 181   | 190             | ms   |

| Debounce Delay, Auto-Retry Delay Following                                                                                              |                                                                                                                             | 86.1  | 90.6  | 95.2            | ms   |

| Undervoltage Fault, t <sub>DL(DB)</sub>                                                                                                 |                                                                                                                             |       |       |                 |      |

| FET BAD Delay, t <sub>DL(FETBAD)</sub>                                                                                                  |                                                                                                                             | 0.138 | 0.145 | 0.152           | Sec  |

| Auto-Retry Delay Following Overcurrent Fault, input/output Fault, or FET Bad Fault, t <sub>DL(RTRY)</sub>                               |                                                                                                                             | 8.82  | 9.28  | 9.74            | Sec  |

| Auto-Retry Counter Reset Delay, t <sub>DL(RTCRST)</sub>                                                                                 | VIN_UV_ FAULT_RETRY, VIN_OV_ FAULT_RETRY, OC_ FAULT_RETRY, OT_ FAULT_RETRY, OP_FAULT_RETRY = 001 to 110                     | 88.2  | 92.8  | 97.4            | Sec  |

| OP1 Fault Unit Delay, t <sub>DL(OP1-UNIT)</sub>                                                                                         | Delay = OP TIMER(Value) × Unit Delay                                                                                        | 1.08  | 1.13  | 1.19            | ms   |

analog.com Rev. 0 | 3 of 44

# **ELECTRICAL CHARACTERISTICS**

Table 1. Electrical Characteristics (Continued)

| Parameter                                                     | Test Conditions/Comments                                                                    | Min                      | Тур                      | Max                      | Unit |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| CURRENT LIMIT                                                 |                                                                                             |                          |                          |                          |      |

| Current-Limit Sense Voltage Threshold, (V <sub>SENSE+</sub> - | ILIM = 0001                                                                                 | 5.67                     | 6                        | 6.33                     | mV   |

| $V_{SENSE-}$ ), $\Delta V_{SNS}$                              | ILIM = 1111                                                                                 | 18.55                    | 20                       | 21.45                    | mV   |

| Current-Limit Sense Voltage Linearity, $\Delta V_{SNS}$       |                                                                                             |                          | 0                        | ±100                     | μV   |

| Foldback Factor, ΔV <sub>SNS</sub>                            | 30%                                                                                         | 15                       | 30                       | 45                       | %    |

| Fast Pull-Down Threshold Multiplier, $V_{(TH)FPD}$            | $T_A = 25^{\circ}C, V_{DD} = 48 \text{ V}$                                                  |                          | 3                        |                          |      |

| SENSE+ Input Current, I <sub>SENSE+(IN)</sub>                 | SENSE- = SENSE+ = V <sub>DD</sub>                                                           | 0                        | 120                      | 250                      | μA   |

| SENSE- Input Current, I <sub>SENSE-(IN)</sub>                 | V <sub>DD</sub> - Source = 5 V                                                              | 4                        | 5                        | 6                        | μA   |

| OVERCURRENT TIMER                                             |                                                                                             |                          |                          |                          |      |

| TMR Fault Threshold, V <sub>TMR(H)</sub>                      | V <sub>TMR</sub> rising                                                                     | 2.5                      | 2.56                     | 2.62                     | V    |

| TMR Low Threshold, V <sub>TMR(L)</sub>                        | V <sub>TMR</sub> falling                                                                    | 0.18                     | 0.2                      | 0.22                     | V    |

| TMR Pull-Up Current, I <sub>TMR(UP)</sub>                     | V <sub>TMR</sub> = 0 V                                                                      | <b>-15</b>               | -20                      | -25                      | μA   |

| TMR Pull-Down Current, I <sub>TMR(DN)</sub>                   | V <sub>TMR</sub> = 2.56 V                                                                   | 3                        | 5                        | 7                        | μA   |

| INPUT PINS                                                    |                                                                                             |                          |                          |                          |      |

| UV/OV/FB Threshold Voltage, V <sub>(TH)UV/OV/FB</sub>         | V <sub>PIN</sub> rising                                                                     | 2.51                     | 2.56                     | 2.61                     | V    |

| OV Threshold Voltage, V <sub>(TH)OV</sub>                     | V <sub>OV</sub> falling                                                                     | 2.3                      | 2.5                      | 2.6                      | V    |

| OV Hysteresis, ΔV <sub>(HYST)OV</sub>                         | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                               |                          | 55                       |                          | mV   |

| UV Threshold Voltage, V <sub>(TH)UVF</sub>                    | V <sub>UV</sub> falling                                                                     | 2.15                     | 2.2                      | 2.25                     | V    |

| FB Threshold Voltage, V <sub>(TH)FB</sub>                     | V <sub>FB</sub> falling                                                                     | 2.3                      | 2.5                      | 2.61                     | V    |

| FB Hysteresis, ∆V <sub>(HYST)FB</sub>                         | $T_A = 25^{\circ}C, V_{DD} = 48 \text{ V}$                                                  |                          | 79                       |                          | mV   |

| UV Hysteresis, ΔV <sub>(HYST)UV</sub>                         | $T_A = 25^{\circ}C, V_{DD} = 48 \text{ V}$                                                  |                          | 360                      |                          | mV   |

| UV Retry Threshold Voltage, V <sub>(TH)UVR</sub>              | V <sub>UVR</sub> rising                                                                     | 1                        | 1.1                      | 1.2                      | V    |

| UV Retry Threshold Voltage, V <sub>(TH)UVR</sub>              | V <sub>UVR</sub> falling                                                                    | 0.95                     | 1.0                      | 1.05                     | V    |

| UV Retry Threshold Hysteresis, ΔV <sub>(HYST)UVR</sub>        | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                               |                          | 100                      |                          | mV   |

| ADR0, ADR1, Input High Threshold, V <sub>ADR(H)</sub>         |                                                                                             | INTV <sub>CC</sub> – 0.8 | INTV <sub>CC</sub> – 0.5 | INTV <sub>CC</sub> – 0.2 | V    |

| ADR0, ADR1, Input Low Threshold, V <sub>ADR(L)</sub>          |                                                                                             | 0.2                      | 0.5                      | 0.8                      | V    |

| ADR0, ADR1, Input Current, I <sub>ADR(IN)</sub>               | V <sub>PIN</sub> = 1 V, V <sub>PIN</sub> = INTV <sub>CC</sub> - 0.85 V                      |                          |                          | ±10                      | μA   |

| EN Threshold Voltage, V <sub>EN(TH)</sub>                     | V <sub>EN</sub> rising                                                                      | 1.25                     | 1.28                     | 1.31                     | V    |

| ` '                                                           | V <sub>EN</sub> falling                                                                     | 1.225                    | 1.26                     | 1.295                    | V    |

| EN Hysteresis, $\Delta_{VEN(HYST)}$                           | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                               |                          | 20                       |                          | mV   |

| GPIO1-8 Pin Threshold Voltage, V <sub>(TH)GPIO</sub>          | V <sub>GPIO</sub> rising                                                                    | 1.25                     | 1.28                     | 1.31                     | V    |

| (,                                                            | V <sub>GPIO</sub> falling                                                                   | 1.225                    | 1.26                     | 1.295                    | V    |

| GPIO1-8 Pin Hysteresis, ΔV <sub>(HYST)GPIO</sub>              | $T_A = 25^{\circ}C, V_{DD} = 48 \text{ V}$                                                  |                          | 20                       |                          | mV   |

| VDSFB Internal Resistor, R <sub>VDSFB</sub>                   | Gate on                                                                                     | 75                       | 120                      | 150                      | kΩ   |

| VDSFB Leakage Current, I <sub>LEAK, VDSFB</sub>               | VDSFB = 0 V, V <sub>DD</sub> = 80 V, gate off                                               |                          | 0                        | ±1                       | μA   |

| SOURCE Input Current, I <sub>SOURCE</sub>                     | V <sub>SOURCE</sub> = 48 V, gate on                                                         |                          |                          | 300                      | μA   |

|                                                               | V <sub>SOURCE</sub> = 0 V, gate off                                                         |                          |                          | -200                     | μA   |

|                                                               | V <sub>SOURCE</sub> = 2 V, gate off                                                         | 0                        |                          | 500                      | μA   |

| OV, UV, EN, FB Input Current, I <sub>INPUT</sub>              | OV, UV, EN, FB = 2.5 V                                                                      |                          | 0                        | ±1                       | μA   |

| OUTPUT PINS                                                   |                                                                                             |                          |                          |                          |      |

| GPIO1-8 Output Low Voltage, V <sub>OL</sub>                   | I <sub>GPIO1 to GPIO8</sub> = 3 mA                                                          |                          | 0.2                      | 0.5                      | V    |

| GPIO1-8 Leakage Current, I <sub>LEAK,GPIO</sub>               | GPIO4, GPIO8 = 6 V, GPIO1, GPIO2, GPIO6 = 80 V,<br>GPIO3, GPIO5, GPIO7 = INTV <sub>CC</sub> |                          | 0                        | ±1                       | μA   |

| ADC                                                           |                                                                                             |                          |                          |                          |      |

| Resolution (No Missing Codes) <sup>2</sup>                    | All channels                                                                                | 12                       |                          |                          | Bits |

| Full-Scale Voltage, V <sub>FS</sub>                           | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                               | -                        |                          |                          |      |

|                                                               | (ADC+ - ADC-)                                                                               |                          | 32                       |                          | mV   |

|                                                               | ,                                                                                           |                          |                          |                          |      |

|                                                               | V <sub>DS</sub>                                                                             |                          | 320                      |                          | mV   |

analog.com Rev. 0 | 4 of 44

# **ELECTRICAL CHARACTERISTICS**

Table 1. Electrical Characteristics (Continued)

| Parameter                                                       | Test Conditions/Comments                                                                                  | Min         | Тур   | Max      | Unit |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------|-------|----------|------|

|                                                                 | V <sub>DD</sub> /SOURCE, 25.6 V range                                                                     |             | 25    |          | V    |

|                                                                 | V <sub>DD</sub> /SOURCE, 100 V range                                                                      |             | 102.4 |          | V    |

| LSB Step Voltage, LSB                                           | (ADC+ - ADC-), T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                              |             | 7.8   |          | μV   |

|                                                                 | $V_{DS}$                                                                                                  |             | 78    |          | μV   |

|                                                                 | V <sub>DD</sub> /SOURCE, 25 V range                                                                       |             | 6.25  |          | mV   |

|                                                                 | V <sub>DD</sub> /SOURCE, 100 V range                                                                      |             | 25    |          | mV   |

| Offset Error, V <sub>OS</sub>                                   | ADC+ – ADC                                                                                                |             |       | ±20      | LSB  |

| , 103                                                           | $V_{DD}/SOURCE$ , $T_A = 25^{\circ}C$ , $V_{DD} = 48 \text{ V}$                                           |             |       | ±10      | LSB  |

|                                                                 | V <sub>DS</sub>                                                                                           | -10         |       | 50       | LSB  |

| Integral Nonlinearity, INL                                      | (ADC+ - ADC-), V <sub>DD</sub> /SOURCE, V <sub>DS</sub> , T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V   |             | ±1    |          | LSB  |

| Full-Scale Error, FSE                                           | (ADC+ - ADC-), V <sub>DD</sub> /SOURCE                                                                    |             |       | ±1       | %    |

|                                                                 | V <sub>DS</sub>                                                                                           | -3          |       | +1       | %    |

| Refresh Rate in Continuous Mode, Internal Oscillator,           | (ADC+ - ADC-), V <sub>DD</sub> /SOURCE, power                                                             | 3.36        | 3.53  | 3.71     | kHz  |

| f <sub>CONV</sub>                                               | V <sub>DS</sub>                                                                                           | 1.68        | 1.77  | 1.86     | kHz  |

| Individual Channel Conversion Time, Internal Oscillator,        | (ADC+ - ADC-), V <sub>DS</sub>                                                                            | 269         | 283   | 310      | μs   |

| t <sub>CONV</sub>                                               | V <sub>DD</sub> /SOURCE                                                                                   | 269         | 283   | 310      | μs   |

| ADC+ Input Current, I <sub>ADC+</sub>                           | $V_{(ADC+)} = V_{DD} = 48 \text{ V}, V_{(ADC-)} = V_{DD} - 21.3 \text{ mV}$                               | 200         | 73    | 132      | μA   |

| ADC- Input Current, I <sub>ADC-</sub>                           |                                                                                                           |             | 0     | ±1       | μA   |

| EMPERATURE MEASUREMENT                                          | $V_{(ADC+)} = V_{DD} = 48V, V_{(ADC-)} = V_{DD} - 21.3 \text{ mV}$                                        |             | U     | <u> </u> | μA   |

|                                                                 |                                                                                                           |             | 40    |          | Dita |

| Resolution (No Missing Codes) <sup>2</sup>                      |                                                                                                           |             | 10    |          | Bits |

| Refresh Rate in Continuous Mode, f <sub>TCONV</sub>             | T 05°0 W 40 W                                                                                             | 070         | 3.45  | 754      | Hz   |

| Full-Scale Temperature Range, R <sub>TFS</sub>                  | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                             | -273        |       | 751      | °C   |

| Temperature Measurement Range, R <sub>TOP</sub>                 | $T_A = 25^{\circ}\text{C}, V_{DD} = 48 \text{ V}$                                                         | <b>-</b> 55 |       | 175      | °C   |

| Remote Temperature Error, η = 1.004, T <sub>RMT</sub>           | $-40^{\circ}$ C to 125°C <sup>3</sup> , T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                     |             | ±1    | ±10      | °C   |

| Temperature LSB Step, LSB <sub>TEMP</sub>                       | $T_A = 25^{\circ}C, V_{DD} = 48 \text{ V}$                                                                |             | 1     |          | °C   |

| TEMP Current, I <sub>TEMP</sub>                                 | Low level, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                  |             | 10    |          | μA   |

|                                                                 | Midlevel, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                   |             | 80    |          | μA   |

|                                                                 | High level, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                 |             | 150   |          | μA   |

| MBus INTERFACE <sup>4</sup>                                     |                                                                                                           |             |       |          |      |

| SDAO Output Low Voltage, V <sub>SDAO(OL)</sub>                  | ISDAO = 20 mA                                                                                             |             |       | 0.5      | V    |

| SDAO Input Current, I <sub>SDAO</sub>                           | SDAO = 5 V                                                                                                |             | 0     | ±1       | μA   |

| SDAI, SCL Input Threshold, V <sub>SDAI,SCL(TH)</sub>            |                                                                                                           | 0.9         | 1.1   | 1.35     | V    |

| SDAI, SCL Input Current, I <sub>SDAI,SCL</sub>                  | SDAI, SCL= 5 V                                                                                            |             | 0     | ±1       | μA   |

| SMBus INTERFACE TIMING <sup>2</sup> , <sup>4</sup>              |                                                                                                           |             |       |          |      |

| SCL Clock Frequency, f <sub>SCL</sub>                           | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                             | 10          |       | 1000     | kHz  |

| SCL Low Period, t <sub>I OW</sub>                               | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                             | 0.40        |       |          | μs   |

| SCL High Period, t <sub>HIGH</sub>                              | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                             | 0.20        |       |          | μs   |

| Data Setup Time, t <sub>SU.DAT</sub>                            | SDAI setup from SCL ↑ for data, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                             | 20          |       |          | ns   |

| Data Hold Time, t <sub>HD,DAT</sub>                             | SDAI hold from SCL ↓ for data, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                              | 0           |       |          | ns   |

| Hold Time Start Bit, t <sub>HD,STA</sub>                        | SCL high after SDAI ↓, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                      | 160         |       |          | ns   |

| Setup Time for Repeated Start, t <sub>SU,STA</sub>              | SCL high setup to SDAI \( \), T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                               | 160         |       |          | ns   |

| Setup Time for Stop bit, t <sub>SU,STO</sub>                    | SCL high setup to SDAI ↑, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                   | 160         |       |          | ns   |

| SDAO delay, t <sub>DEL,SDAO</sub>                               | SDAO $\downarrow$ delay from SCL $\downarrow$ , SEL_1M = 0, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V | 100         | 175   | 405      | ns   |

|                                                                 | SDAO $\downarrow$ delay from SCL $\downarrow$ , SEL_1M = 1, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V | 75          | 125   | 220      | ns   |

| SCL or SDAI Pulse Spike Rejection, t <sub>PW</sub> <sup>2</sup> | T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V                                                             | 55          | 75    | 110      | ne   |

| · · · · · · · · · · · · · · · · · · ·                           | 1 11 ==                                                                                                   |             |       |          | ns   |

| PMBus Stuck Bus Timeout, T <sub>D(STUCK)</sub>                  | $T_A = 25^{\circ}C, V_{DD} = 48 \text{ V}$                                                                | 25          | 30    | 35       | ms   |

analog.com Rev. 0 | 5 of 44

### **ELECTRICAL CHARACTERISTICS**

#### Table 1. Electrical Characteristics (Continued)

| Parameter                                  | Test Conditions/Comments                                         | Min | Тур | Max | Unit |

|--------------------------------------------|------------------------------------------------------------------|-----|-----|-----|------|

| SCL, SDA Input Capacitance, C <sub>X</sub> | SDAI tied to SDAO, T <sub>A</sub> = 25°C, V <sub>DD</sub> = 48 V |     | 5   | 10  | pF   |

<sup>&</sup>lt;sup>1</sup> An internal clamp limits the GATE pin to a minimum of 10 V above SOURCE. Driving this pin to voltages beyond the clamp can damage the device.

analog.com Rev. 0 | 6 of 44

<sup>&</sup>lt;sup>2</sup> Guaranteed by design and characterization.

Remote diode temperature, not LTC4286 temperature. Guaranteed by design and test correlation.

<sup>&</sup>lt;sup>4</sup> The LTC4286 is fully compliant with SMBus 3.1 and operation up to 1 Mbps. In general, the chip can be used in I<sup>2</sup>C bus systems using standard-mode, fast-mode, or fast-mode plus as long as PMBus command protocols are followed. A V<sub>IH</sub>/V<sub>IL</sub> incompatibility between SMBus 3.1 and I<sup>2</sup>C can lead to a DC level violation for I<sup>2</sup>C buses running at 3.5 V or higher.

### **ABSOLUTE MAXIMUM RATINGS**

All currents into pins are positive and all voltages are referenced to GND, unless otherwise specified.

Table 2. Absolute Maximum Ratings

| Parameter                             | Rating                                     |

|---------------------------------------|--------------------------------------------|

| Supply Voltages                       |                                            |

| $V_{DD}$                              | -0.3 V to +100 V                           |

| $INTV_{CC}$ , $DV_{CC}$               | -0.3 V to +5.5 V                           |

| Input Voltages                        |                                            |

| SDAI, SCL                             | -0.3 V to +6 V                             |

| CFIG4                                 | -0.3 V to +1 V                             |

| OV, UV, FB, EN                        | -0.3 V to +100 V                           |

| VDSFB                                 | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| TMR, ADR0, ADR1, CFIG3                | -0.3 V to INTV <sub>CC</sub> + 0.3 V       |

| ADC+, SENSE+                          | $V_{DD}$ - +4.5 V to $V_{DD}$ + 0.3 V      |

| ADC-, SENSE-                          | $V_{DD}$ - +4.5 V to $V_{DD}$ + 0.3 V      |

| CFIG1, CFIG2                          | $V_{DD}$ - +4.5 V to $V_{DD}$ + 0.3 V      |

| SOURCE                                | -0.3 V to +100 V                           |

| GATE - SOURCE1                        | -0.3 V to +10 V                            |

| Output Voltages                       |                                            |

| ISET, CFIG5, CFIG6                    | -0.3 V to DV <sub>CC</sub> + 0.3 V         |

| GPIO1, GPIO2, GPIO6                   | -0.3 V to 100 V                            |

| GPIO3, GPIO5, GPIO7                   | -0.3 V to INTV <sub>CC</sub> + 0.3 V       |

| GATE                                  | -0.3 V to +100 V                           |

| SDAO, GPIO4, GPIO8                    | -0.3 V to +6 V                             |

| Output Currents                       |                                            |

| INTV <sub>CC</sub> , DV <sub>CC</sub> | -5 mA                                      |

| Temperature                           |                                            |

| Operating Range                       | -40°C to +125°C                            |

| Storage Range                         | -65°C to +150°C                            |

An internal clamp limits the GATE pin to a minimum of 10 V above SOURCE. Driving this pin to voltages beyond the clamp may damage the device.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 7 of 44

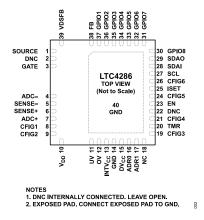

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SOURCE             | N-channel MOSFET Source and ADC Input. Connect this pin to the source of the external N-channel MOSFET. This pin provides a return for the GATE pull-down circuit, is used as an input to the 200 mV and 2 V V <sub>DS</sub> comparators that are used for FET-BAD faults and Power_Good, respectively. The SOURCE pin also serves as an ADC input to monitor the output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2, 22   | DNC                | Do not connect. Leave open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3       | GATE               | Gate Drive Output for External N-channel MOSFET. Internal 50 $\mu$ A current source charges the gate of the MOSFET No compensation capacitors are required on the GATE pin, but an RC network from this pin to ground can be used to set the turn-on output voltage slew rate. During turn-off, there is a 10 mA pull-down current to SOURCE and a 1 mA pull-down current to GND. During a short-circuit or undervoltage lockout ( $V_{DD}$ , INTV <sub>CC</sub> ), a 1 A pull-down between GATE and SOURCE is activated.                                                                                                                                                                                                                                                                                            |

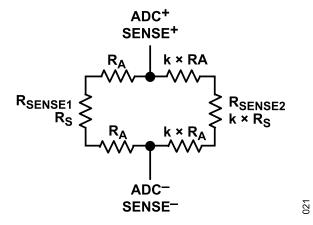

| 4       | ADC-               | Negative Kelvin ADC Current Sense Input. Connect this pin to the output side of the current sense resistor or a resistive averaging network when using multiple sense resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5       | SENSE-             | Negative Kelvin Current Sense Input. Connect this pin to the MOSFET side of the current sense resistor. The current-limit circuit controls the GATE pin to limit the sense voltage between the SENSE+ and SENSE- pins to the limit value selected by the ISET pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6       | SENSE+             | Positive Kelvin Current Sense Input. Connect this pin to the V <sub>DD</sub> side of the current sense resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7       | ADC+               | Positive Kelvin ADC Current Sense Input. Connect this pin to the input side of the current sense resistor or a resistive averaging network when using multiple sense resistors. Must be connected to the same trace as $V_{DD}$ or a resistive averaging network, which adds up to 1 $\Omega$ to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8       | CFIG1              | Configuration Input. Tie to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9       | CFIG2              | Configuration Input. Tie to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10      | $V_{DD}$           | Supply Voltage Input. This pin has an undervoltage lockout threshold of 6 V. V <sub>DD</sub> is an input for the FET-BAD comparator with a 200 mV threshold. It is also an input for the power bad comparator with a 2 V threshold. The ADC can be configured to measure the voltage at this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11      | UV                 | Undervoltage Comparator Input. Connect this pin to an external resistive-divider from $V_{DD}$ to GND. If the UV pin falls below 2.2 V, an undervoltage occurs, and the MOSFET turns off. If the UV pin rises above 2.56 V, the MOSFET turns on after a debounce delay of 90.6 ms. Pulling this pin below 1 V adds one retry to the retry counter for an OC, FET_BAD, OT, or OP fault, which is linked to the FAULT# GPIO output in MFR_FLT_CONFIG if that fault has zero remaining retries. If overcurrent auto-retry is required, then tie this pin to the GPIO2 pin, which is configured as a FAULT# output reporting OC and FET_BAD faults by default. Tie to INTV <sub>CC</sub> if unused or connect to a GPIO pin with a 4.7 k $\Omega$ pull-up to INTV <sub>CC</sub> if only the auto-retry function is used. |

| 12      | OV                 | Overvoltage Comparator Input. Connect OV to an external resistive voltage-divider from V <sub>DD</sub> to GND. An overvoltage fault occurs if this pin rises above the 2.56 V threshold. When the OV pin voltage falls back below the 2.5 V falling threshold, the GATE pin turns on again immediately. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13      | INTV <sub>CC</sub> | Internal Supply Decoupling Output. Connect a capacitor no smaller than 0.1 µF from this pin to the ground. Up to 5 mA can be drawn from this pin to power 5 V application circuitry. This pin is current-limited and drops to GND to reduce heating in an overcurrent condition. Overloading this pin can disrupt internal operation. To reduce heating,                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

analog.com Rev. 0 | 8 of 44

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 3. Pin Function Descriptions (Continued)

| Pin No.  | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                  | this pin can act as a shunt regulator by connecting a resistor to $V_{DD}$ or another supply such that 10 mA flows to INTV <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14       | GND              | Device Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15       | DV <sub>CC</sub> | 5 V Internal Logic Supply Output. This is an output of the internal linear regulator with an UVLO threshold of DVCC (UVLO). The voltage at this pin powers up the logic control circuitry and SMBus interface. Bypass this pin with a 0.1 μF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16, 17   | ADR0, ADR1       | Serial Bus Address Inputs. Tying these pins to ground (L), open (NC) or INTV <sub>CC</sub> (H) configures one of nine possible addresses. See Table 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18       | NC               | Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19       | CFIG3            | Configuration Input. Tie to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20       | TMR              | Current-Limit Timer. Connect a capacitor between this pin and ground to set a 128 ms/ $\mu$ F duration for current limit before the MOSFET is turned off. If configured to auto-retry or if the UV pin is toggled low, the MOSFET turns on again following a cool-down time of 9.28 s.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 21       | CFIG4            | Configuration Input. Tie to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23       | EN               | Active High Enable Input. EN is typically used to indicate that a board is present. The external MOSFET can only be turned on when EN is active and the ON bit in the OPERATION register is set. See Table 4 for the ON bit defaults at power-up. Any transition on this pin sets the EN_CHANGED bit in MFR_SPECIFIC_STATUS.                                                                                                                                                                                                                                                                                                                                                                          |

| 24       | CFIG5            | Configuration Input. Tie to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25       | ISET             | Current-Limit Adjustment Input. The ISET voltage is compared with seven threshold voltages generated by a resistive voltage-divider from INTV $_{CC}$ . The result sets the current-limit voltage to be one of eight discrete values from 6 mV to 20 mV in 2 mV increments. When ISET is connected to ground, the current-limit threshold is set to 6 mV. When ISET is connected to INTV $_{CC}$ , current-limit threshold is set to 20 mV (see Table 5).                                                                                                                                                                                                                                             |

| 26       | CFIG6            | Initial ON Configuration Input. Tie to GND to turn on automatically, tie to 1.6 V with a resistive divider to remain off awaiting further instructions. For more details, see Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27       | SCL              | SMBus-compatible Clock Input, high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 28       | SDAI             | Serial Bus Data Input. A high impedance input for shifting in address, command, or data bits. Normally tied to SDAO to form the SDA line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 29       | SDAO             | Serial Bus Data Output. Open-drain output for sending data back to the controller or acknowledging a write operation. Normally tied to SDAI to form the SDA line. An external pull-up resistor or current source is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 30       | GPIO8            | OP1_STATUS# Indicator Output. This pin is pulled low when the ADCs measure a power level above the OP1 threshold. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 31       | GPIO7            | Comparator Output. This pin is the output of the comparator on the GPIO6 pin. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 32       | GPIO6            | Comparator Input. This pin has a 1.28 V threshold. The output of the comparator is available on GPIO7. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 33       | GPIO5            | This pin has a reserved function by default. Leave it open unless changing its configuration register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 34       | GPIO4            | IOUT_OC_STATUS# Indicator Output. When the LTC4286 is in current limit, this open-drain output is pulled low to indicate an overcurrent condition. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 35       | GPIO3            | Temperature Sensor Input. Connect to an MMBT3904 transistor for use as a remote temperature sensor. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 36       | GPIO2            | FAULT# Output. This pin pulls low when an overcurrent or FET-BAD fault occurs. This pin can be tied to the UV pin to clear faults and auto-retry after a fault occurs. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 37       | GPIO1            | Power-Good# Indicator Output. This open drain pull-down pulls low when power is good, as determined by the FB pin and GATE pin voltages. Tie to GND if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 30 to 37 | GPIO1 to GPIO8   | General-purpose I/O with open-drain output drivers. Several digital I/O functions are available for these pins. Those functions can be assigned by configuration to any of the eight pins. With few exceptions, the pins behave identically. GPIO1, GPIO2, and GPIO6 can be externally pulled as high as $V_{DD}$ . The others must not be pulled any higher than DV <sub>CC</sub> . The external temperature sensor function is available on GPIO3 only. Individual GPIO pin descriptions further refer to the hardware default configuration. By default, all alerts are disabled, and no GPIO pins are assigned to ALERT#, which can be changed after power-up by writing configuration registers. |

| 38       | FB               | Power-Good Input. Connect this pin to an external resistive divider from SOURCE to GND. When the voltage at this pin drops below 2.56 V, power is not considered good. The power bad condition can result in a GPIO Power Good# pin pulling low or going high impedance depending on the GPIO pin configuration. Also a power bad fault is logged in this condition if a GATE pin is high. Tie to INTV <sub>CC</sub> if unused.                                                                                                                                                                                                                                                                       |

analog.com Rev. 0 | 9 of 44

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

### Table 3. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                                                                                                                           |

|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39      | VDSFB      | VDS Foldback Sense Input. This pin is used to monitor the drain to source voltage of the external MOSFETs, which is used to set the foldback current limit. VDSFB is tied to SOURCE for 12 V applications, and an additional 10 k $\Omega$ /V is added for higher operating voltages, to set the proper gain of the foldback circuit. |

| 40      | EPAD (GND) | Exposed Pad. Connect exposed pad to GND.                                                                                                                                                                                                                                                                                              |

analog.com Rev. 0 | 10 of 44

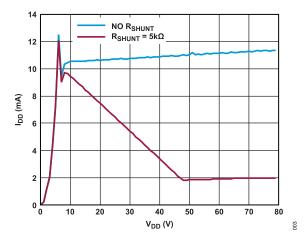

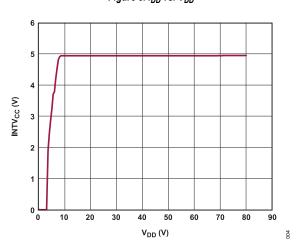

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 3.  $I_{DD}$  vs.  $V_{DD}$

Figure 4. INTV $_{\rm CC}$  vs.  $V_{\rm DD}$

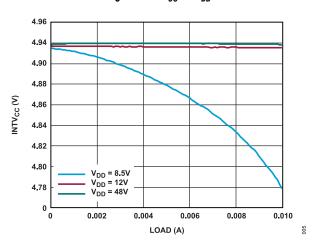

Figure 5. INTV<sub>CC</sub> vs. Load at  $V_{DD}$  = 8.5 V, 12 V, and 48 V

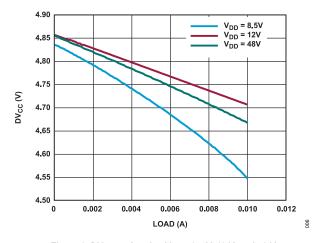

Figure 6. DV<sub>CC</sub> vs. Load at  $V_{\rm DD}$  = 8.5 V, 12 V, and 48 V

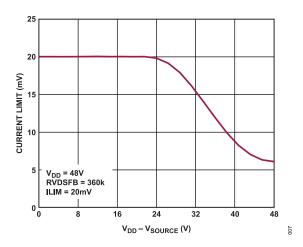

Figure 7. Current-Limit Foldback Profiles

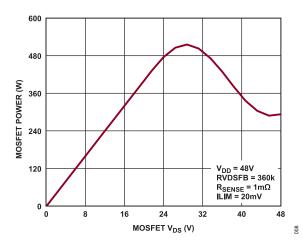

Figure 8. MOSFET Power vs. V<sub>DS</sub>

analog.com Rev. 0 | 11 of 44

### TYPICAL PERFORMANCE CHARACTERISTICS

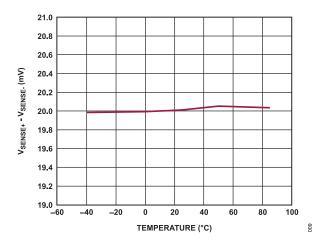

Figure 9. Current-Limit Threshold vs. Temperature

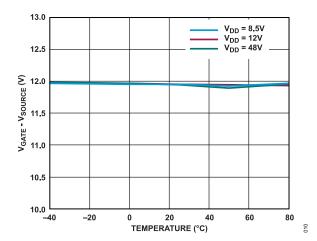

Figure 10.  $V_{GATE}$  –  $V_{SOURCE}$  vs. Temperature at  $V_{DD}$  = 8.5 V, 12 V, and 48 V

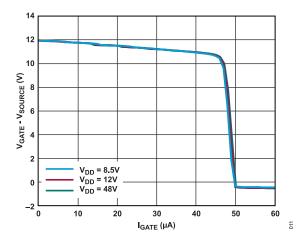

Figure 11.  $V_{GATE}$  –  $V_{SOURCE}$  vs. IGATE (Leak) at  $V_{DD}$  = 8.5 V, 12 V, and 48 V

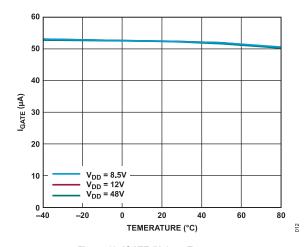

Figure 12. IGATE (Up) vs. Temperature

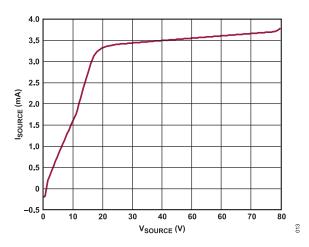

Figure 13. I<sub>SOURCE</sub> vs. V<sub>SOURCE</sub>

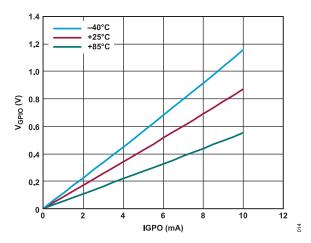

Figure 14. V<sub>OL</sub> GPIO1, GPIO2, GPIO6 vs. IGPO

analog.com Rev. 0 | 12 of 44

# **TYPICAL PERFORMANCE CHARACTERISTICS**

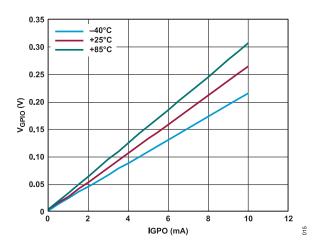

Figure 15.  $V_{OL}$  GPIO3, GPIO5, GPIO7 vs. IGPO

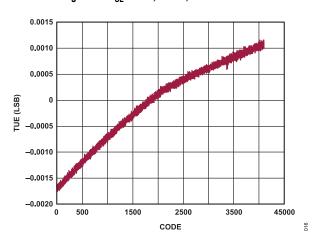

Figure 16. ADC TUE vs. Code (64x Average)

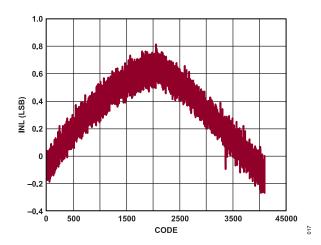

Figure 17. ADC INL vs. Code (64x Average)

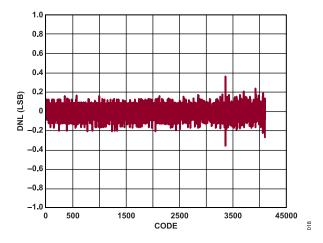

Figure 18. ADC DNL vs. Code (64x Average)

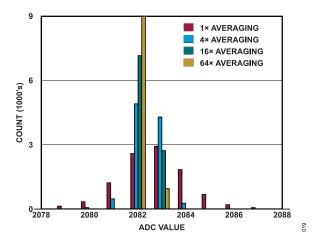

Figure 19. 12-Bit Current ADC Noise Histogram (1x, 4x, 16x, and 64x Average)

analog.com Rev. 0 | 13 of 44

#### THEORY OF OPERATION