## 42V Quad, Gangable, Synchronous, Monolithic Step-Down Regulator

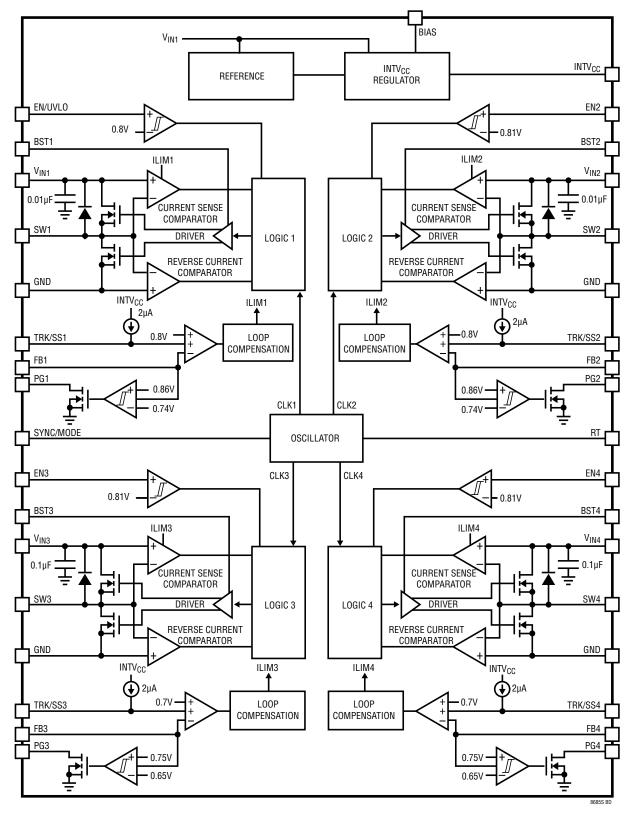

The LT<sup>®</sup>8685S is a highly flexible, four channel, current

mode, monolithic regulator able to power a wide range

of automotive and industrial applications while occupying

The LT8685S combines two 42V capable 2.5A buck reg-

ulators with two 8V capable 4A buck regulators. The two

42V regulators may be combined to provide up to 5A of

output current using a single inductor. Similarly, the two

8V regulators may be combined to provide up to 8A of

output current using a single inductor. Individual channel

enable, track/soft-start and power good pins provide flex-

ible power supply sequencing and control. The LT8685S

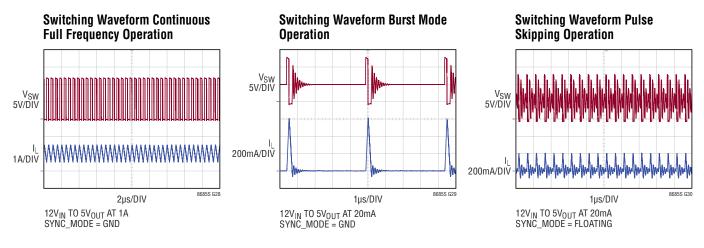

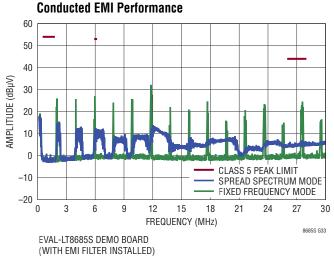

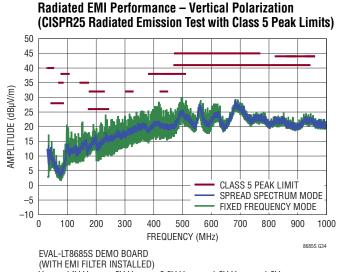

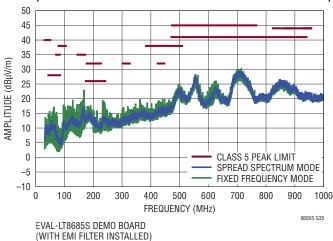

features a Silent Switcher 2 architecture, plus selectable

spread spectrum mode, to provide ultralow EMI/EMC

emissions while delivering high efficiency at high switch-

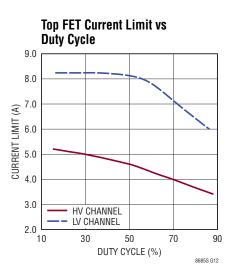

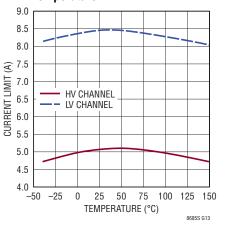

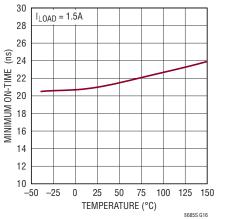

The LT8685S incorporates thermal shutdown and individ-

ual channel cycle-by-cycle current limit for short circuit

All registered trademarks and trademarks are the property of their respective owners.

DESCRIPTION

minimal board space.

ing frequencies.

protection and robust operation.

## **FEATURES**

- Silent Switcher<sup>®</sup>2 Architecture

- Ultralow EMI Emissions

- Optional Spread Spectrum Modulation

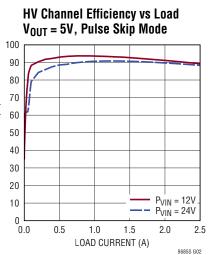

- Two High Voltage Synchronous Buck Regulators

- 3V to 42V Input Voltage Range

- Output Currents Up to 2.5A per Channel

- Channels May Be Connected in Parallel Using a Single Inductor

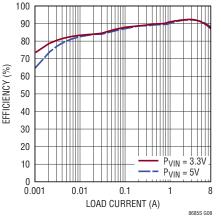

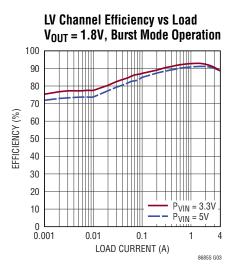

- Two Low Voltage Synchronous Buck Regulators

- 3V to 8V Input Voltage Range

- Output Currents Up to 4A per Channel

- Channels May Be Connected in Parallel Using a Single Inductor

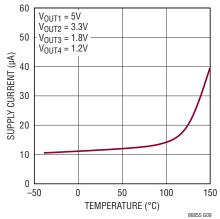

- 12µA I<sub>O</sub> All Channels Active and No-Load

- Flexible Supply Sequencing and Control

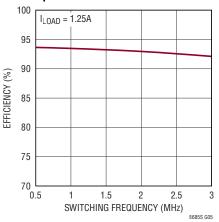

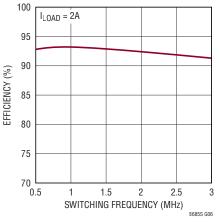

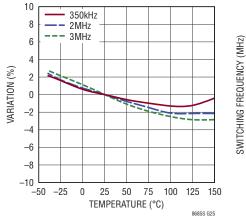

- Adjustable and Synchronizable: 350kHz to 3MHz

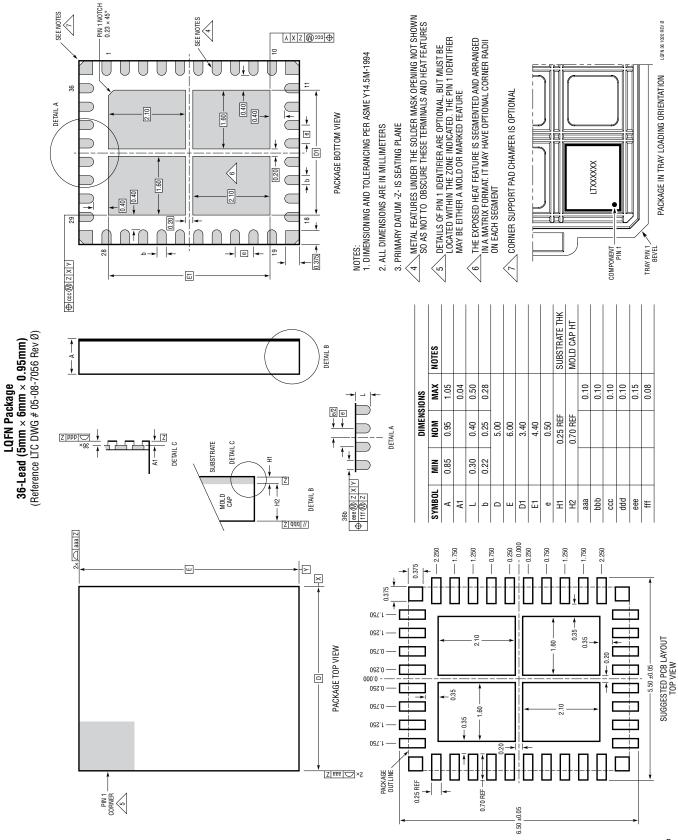

- Available in 36-Lead LQFN (5mm × 6mm)

- AEC-Q100 Qualified for Automotive Applications

## **APPLICATIONS**

- **Automotive Systems**

- Industrial Controls and Power Supplies

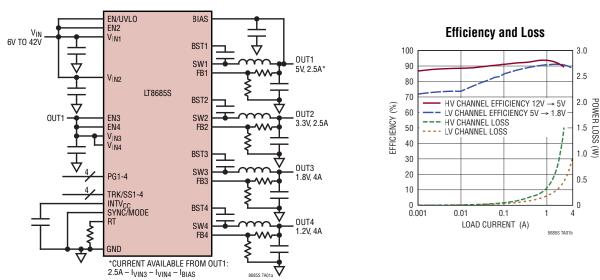

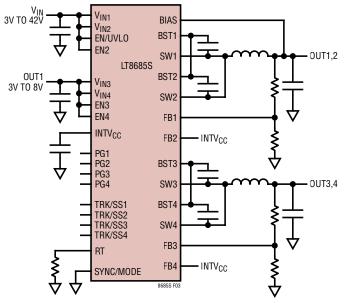

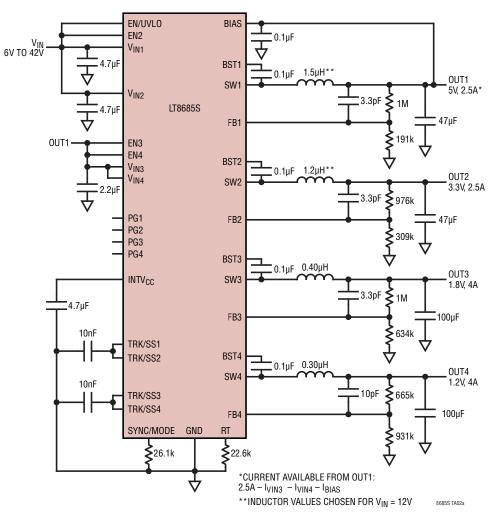

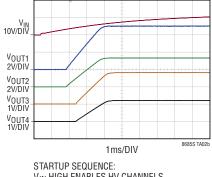

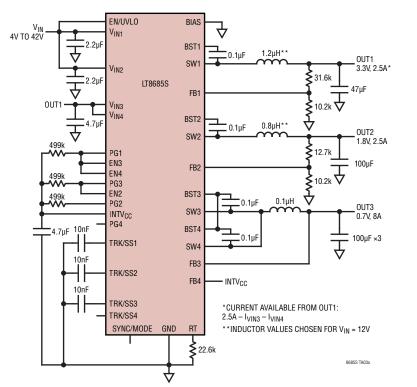

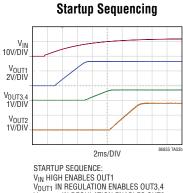

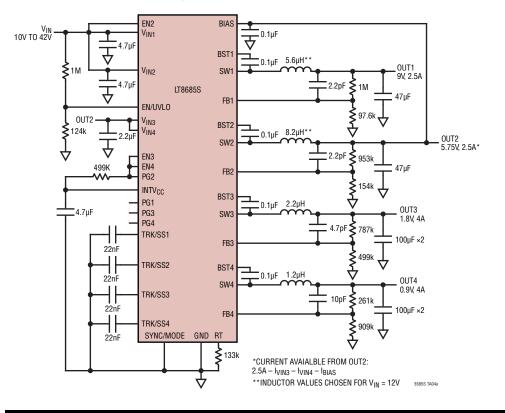

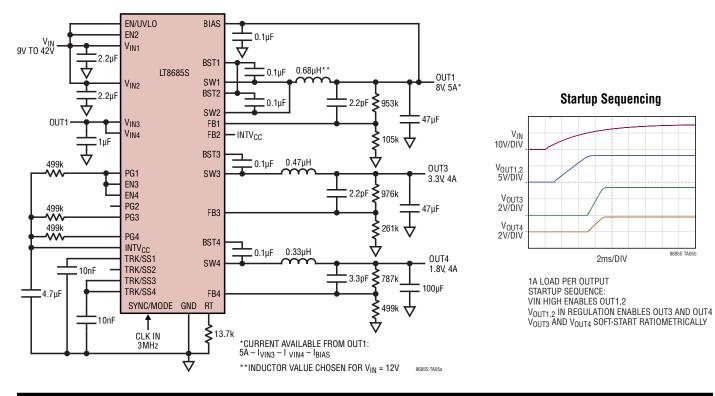

## TYPICAL APPLICATION

42V Input, Quad Output 2MHz Step-Down Regulator

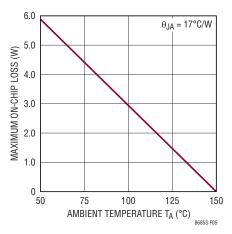

POWER LOSS

## **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1) |

|-------|----|

|-------|----|

| V <sub>IN1</sub> , V <sub>IN2</sub> 0.3V to 42V  |

|--------------------------------------------------|

| V <sub>IN3</sub> , V <sub>IN4</sub> –0.3V to 10V |

| EN/UVLO, EN2, EN3, EN442V                        |

| PG1, PG2, PG3, PG4, SYNC/MODE6V                  |

| BIAS0.3V to 14V                                  |

| FB1, FB2, FB3, FB44V                             |

| TRK/SS1, TRK/SS2, TRK/SS3, TRK/SS44V             |

| Operating Junction Temperature (Notes 2, 3)      |

| LT8685SR40°C to 150°C                            |

| Storage Temperature Range65°C to 150°C           |

| Maximum Reflow (Package Body)                    |

| Temperature                                      |

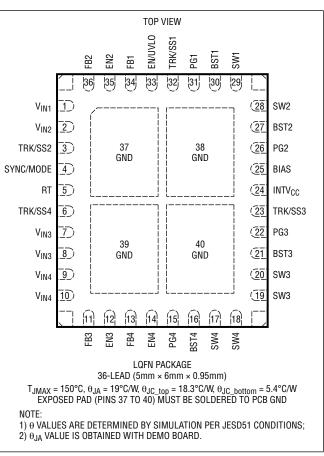

## PIN CONFIGURATION

## ORDER INFORMATION

| PAD OR PART MARK                                                                                                                                                                              |                        | IARKING          | PACKAGE                                                   | MSL            | TEMPERATURE RANGE                             |                     |                |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-----------------------------------------------------------|----------------|-----------------------------------------------|---------------------|----------------|--|

| PART NUMBER                                                                                                                                                                                   | TAPE AND REEL          | BALL FINISH      | DEVICE                                                    | FINISH CODE    | TYPE*                                         | RATING              | (SEE NOTE 2)   |  |

| LT8685SRV#PBF                                                                                                                                                                                 | LT8685SRV#TRPBF        | Au (RoHS)        | 8685S                                                     | e4             | LQFN (Laminate Package<br>with QFN Footprint) | 3                   | -40°C to 150°C |  |

| AUTOMOTIVE PRODUCTS**                                                                                                                                                                         |                        |                  |                                                           |                |                                               |                     |                |  |

| LT8685SRV#WPBF                                                                                                                                                                                | LT8685SRV#WTRPBF       | Au (RoHS)        | 8685S                                                     | e4             | LQFN (Laminate Package<br>with QFN Footprint) | 3                   | -40°C to 150°C |  |

| <ul> <li>Pad or ball finish code is per IPC/JEDEC J-STD-609.</li> <li>Tape and reel specifications.</li> <li>Recommended LGA and BGA PCB Assembly and Manufacturing<br/>Procedures</li> </ul> |                        |                  |                                                           |                |                                               | y and Manufacturing |                |  |

| Parts ending with PBF and RoHS are WEEE compliant.                                                                                                                                            |                        |                  | <ul> <li>LGA and BGA Package and Tray Drawings</li> </ul> |                |                                               |                     |                |  |

| *The LT8685S pack                                                                                                                                                                             | age has the same dimen | sions as a stand | lard 5mm × 6n                                             | nm QFN package |                                               |                     |                |  |

\*\*Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C.  $V_{IN1} = V_{IN2} = 12V$ ,  $V_{IN3} = V_{IN4} = 5V$ ,  $f_{SW} = 2$ MHz unless otherwise specified.

| Total Operating Input Current, Burst         V <sub>OUT1</sub> = V <sub>BUS</sub> = 5V, V <sub>OUT2</sub> = 3.3V, V <sub>OUT3</sub> = 1.8V,<br>V <sub>OUT4</sub> = 1.2V, V <sub>SYNCANOC</sub> = 0V, No Load         12         µµ           Total Operating Input Current, Pulse-Skipping         Carl = 5V, V <sub>OUT3</sub> = 3.3V, V <sub>OUT4</sub> = 1.2V,<br>V <sub>SYNCANOC</sub> = 18V, V <sub>OUT4</sub> = 1.2V,         1100         µµ           Switching Frequency         Rg = 154k<br>Rg = 22 6k<br>Rg = 13.7k         0.128         0.35         0.45         MHH           SYNC Threshold Voltage         V <sub>11</sub> 0         1.5         0.4         MH           SYNC Threshold Voltage         V <sub>11</sub> 0         1.5         0.4         M           SYNC Threshold Voltage         V <sub>11</sub> 0         1.5         0.4         M           SYNC MODE Pin Input Current         V <sub>SWICANODE</sub> = 6V         75         µµ           Internal V <sub>CC</sub> Regulator         3.4         M         M           Internal V <sub>CC</sub> Indervoltage Lockout         Falling         2.3         2.4         2.5         M           BIAS Pin Threshold         0         -160         0         0.00         m         M           Minimum Input Voltage (CH1 Only)         0         2.8         3         M           Feedback Reference Voltage         0         0.10         mA         M         MA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PARAMETER                                                             | CONDITIONS                                                                                            |   | MIN   | ТҮР  | MAX   | UNITS             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---|-------|------|-------|-------------------|

| Voirt = 12V. Vsworword = 0V. No Löäd         Voirt = 5V. Vourt = 5V. Vourt = 12V. Vourt = | Quiescent Current, Shutdown                                           |                                                                                                       |   |       | 0.5  | 1.5   | μA                |

| Switching Frequency         Rat = 154k         Image: state of the s         | Total Operating Input Current, Burst                                  |                                                                                                       |   |       | 12   |       | μA                |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Total Operating Input Current, Pulse-Skipping                         | $V_{OUT1} = 5V, V_{OUT2} = 3.3V, V_{OUT3} = 1.8V, V_{OUT4} = 1.2V, V_{SYNC/MODE} = Floating, No Load$ |   |       | 1100 |       | μA                |

| V <sub>H</sub> •         1.5         V           SYNC/MODE = 6V         75 $\mu$ product           Internal V <sub>CC</sub> Regulator         3.4         V           Internal V <sub>CC</sub> Undervoltage Lockout         Falling         2.3         2.4         2.5         V           BIAS Pin Threshold         2.3         2.4         2.5         V         V           BIAS Pin Threshold         4.5         V         V         V         V         V           Channels 1 to 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Switching Frequency                                                   | R <sub>RT</sub> = 22.6k                                                                               | • | 1.8   | 2    | 2.25  | MHz<br>MHz<br>MHz |

| Internal V <sub>CC</sub> Regulator         Internal V <sub>CC</sub> Undervoltage Lockout         Falling         3.4         V           Internal V <sub>CC</sub> Undervoltage Lockout         Falling         2.3         2.4         2.5         V           BIAS Pin Threshold         4.5         V         4.5         V           Channels 1 to 2         0.786         0.8         0.812         V           Feedback Reference Voltage         0.786         0.8         0.812         V           Feedback Reference Voltage         0.01         %         %         %           Peak Current Limit         4.2         4.8         5.4         #           Power FET On-resistance         1swri, Isw2 = 0.1A         210         mcCurrent           Synchronous Switch (Bottom)         Iswri, Isw2 = 0.1A         110         mcCurrent           EN/UVLO Threshold         EN/UVLO Falling         0.78         0.8         0.82         V           EN/UVLO Thysteresis         100         mM         mcCurrent         -250         0         250         mc           EN/UVLO Threshold         EN/UVLO = 42V         -250         0         250         mc           EN/UVLO Threshold         EN/E Falling         0.78         0.81         0.84         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SYNC Threshold Voltage                                                |                                                                                                       | • | 1.5   |      | 0.4   | V<br>V            |

| Internal Voc. Undervoltage Lockout         Falling         2.3         2.4         2.5         V           BIAS Pin Threshold         4.5         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V         V<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SYNC/MODE Pin Input Current                                           | V <sub>SYNC/MODE</sub> = 6V                                                                           |   |       | 75   |       | μA                |

| BIAS Pin Threshold         4.5         V           Channels 1 to 2         Minimum Input Voltage (CH1 Only) <ul> <li>0.786</li> <li>0.8</li> <li>0.176</li> <li>0.786</li> <li>0.8</li> <li>0.8</li> <li>0.8</li> <li>0.110</li> <li>0.786</li> <li>0.8</li> <li>0.8</li> <li>0.786</li> <li>0.8</li> <li>0.01</li> <li>0.01<!--</td--><td>Internal V<sub>CC</sub> Regulator</td><td></td><td></td><td></td><td>3.4</td><td></td><td>V</td></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Internal V <sub>CC</sub> Regulator                                    |                                                                                                       |   |       | 3.4  |       | V                 |

| Channels 1 to 2           Minimum Input Voltage (CH1 Only) <ul></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Internal V <sub>CC</sub> Undervoltage Lockout                         | Falling                                                                                               |   | 2.3   | 2.4  | 2.5   | V                 |

| Minimum Input Voltage (CH1 Only)         East 3         V           Feedback Reference Voltage         0.786         0.8         0.812         V           Feedback Input Current          -100         0         100         nA           VFB1, VFB2 Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %///         %///           Peak Current Limit         4.2         4.8         5.4         A           Power FET On-resistance         210         mC.         mC.         mC.           Main Switch (Top)         I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A         210         mC.         mC.           Synchronous Switch (Bottom)         I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A         210         mC.         mC.           EN/UVLO Threshold         EN/UVLO Falling         0.78         0.8         0.82         V           EN/UVLO Hysteresis         100         mV         mV         mV////////////////////////////////////                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BIAS Pin Threshold                                                    |                                                                                                       |   |       | 4.5  |       | V                 |

| Feedback Reference Voltage         0.786         0.8         0.812         V           Feedback Input Current         0         -100         0         100         nA           VFB1, VFB2 Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %A           Peak Current Limit         4.2         4.8         5.4         A           Power FET On-resistance<br>Main Switch (Top)<br>Synchronous Switch (Bottom)         I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A         210         mGC           EN/UVLO Threshold         EN/UVLO Falling         0.78         0.8         0.82         V           EN/UVLO Input Current         V <sub>EN</sub> /UVLO = 42V         -250         0         250         nA           EN/UVLO Input Current         V <sub>EN/</sub> UVLO = 42V         -250         0         250         nA           EN2 Hysteresis         50         mW         -250         0         250         nA           EN2 Hysteresis         50         mW         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         -10         -7.5         -0.5         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         -250         0         250         nA           P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Channels 1 to 2                                                       | ·                                                                                                     |   |       |      |       |                   |

| Feedback Input Current         •         -100         0         100         n/A           VFB1, VFB2 Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %/A           Peak Current Limit         4.2         4.8         5.4         /A           Power FET On-resistance<br>Main Switch (Top)<br>Synchronous Switch (Bottom)         Isw1, Isw2 = 0.1A<br>Isw1, Isw2 = 0.1A         210         mG           Synchronous Switch (Bottom)         EN/UVLO Threshold         EN/UVLO Threshold         0.78         0.8         0.82         V           EN/UVLO Threshold         EN/UVLO Falling         0.78         0.8         0.82         V         V           EN/UVLO Input Current         V <sub>EN/</sub> UVLO = 42V        250         0         250         n/A           EN/UVLO Input Current         V <sub>EN/</sub> UVLO = 42V         -250         0         250         n/A           EN/UVLO Input Current         V <sub>EN/2</sub> = 42V         -250         0         250         n/A           EN/UVLO Input Current         V <sub>EN2</sub> = 42V         -250         0         250         n/A           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Ealing         = -10         -7.5         -4.5         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>F</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Minimum Input Voltage (CH1 Only)                                      |                                                                                                       |   |       | 2.8  | 3     | V                 |

| VERI, VFB2 Line Regulation         V <sub>UIN1</sub> = 3V to 42V         0.01         %/A           Peak Current Limit         4.2         4.8         5.4         //           Power FET On-resistance<br>Main Switch (Top)<br>Synchronous Switch (Bottom)         I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A<br>I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A         210         mG           EN/UVLO Threshold         EN/UVLO Falling         0.78         0.8         0.82         V           EN/UVLO Hysteresis         110         mC         mG         mG         mG         mG           EN/UVLO Hysteresis         100         mV         100         mV         mV         mG           EN/UVLO Input Current         V <sub>EN</sub> /UVLO = 42V         -250         0         250         nA           EN2 Threshold         EN2 Falling         0.78         0.81         0.84         V           EN2 Hysteresis         50         mV         mV         mV         mV         mV           EN2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         -10         -7.5         -4.5         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> C 0.1V         500         1200         G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Feedback Reference Voltage                                            |                                                                                                       | • | 0.786 | 0.8  | 0.812 | V                 |

| Peak Current Limit         4.2         4.8         5.4         A           Power FET On-resistance<br>Main Switch (Top)<br>Synchronous Switch (Bottom)         I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A<br>I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A         210         mG           EN/UVLO Threshold         EN/UVLO Falling         0.78         0.8         0.82         V           EN/UVLO Threshold         EN/UVLO Falling         0.78         0.8         0.82         V           EN/UVLO Hysteresis         100         mV         100         mV           EN/UVLO Input Current         V <sub>EN/</sub> UVLO = 42V         -250         0         250         nA           EN2 Threshold         EN2 Falling         0.78         0.81         0.84         V           EN2 Hysteresis         50         mV         50         mV           EN2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         -10         -7.5         -4.5         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Feedback Input Current                                                |                                                                                                       | • | -100  | 0    | 100   | nA                |

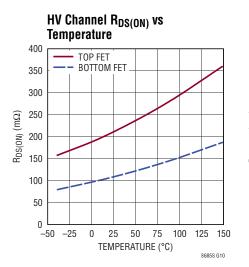

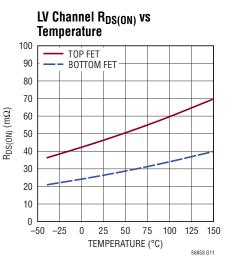

| Power FET On-resistance<br>Main Switch (Top)<br>Synchronous Switch (Bottom) $I_{SW1}$ , $I_{SW2} = 0.1A$ 210<br>110         mG<br>MG           EN/UVLO Threshold         EN/UVLO Falling         •         0.78         0.8         0.82         V           EN/UVLO Threshold         EN/UVLO Falling         •         0.78         0.8         0.82         V           EN/UVLO Threshold         EN/UVLO = 42V         -250         0         250         nA           EN/UVLO Input Current         V <sub>EN</sub> /UVLO = 42V         -250         0         250         nA           EN/UVLO Input Current         V <sub>EN</sub> /UVLO = 42V         -250         0         250         nA           EN/2 Hysteresis         50         mV         50         mV           EN/2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising         •         4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         •         -10         -7.5         -4.5         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>FG2</sub> = 6V         -250         0         250         nA           Pgood Pu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>FB1</sub> , V <sub>FB2</sub> Line Regulation                   | V <sub>VIN1</sub> = 3V to 42V                                                                         |   |       | 0.01 |       | %/V               |

| Main Switch (Top)<br>Synchronous Switch (Bottom)         I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A<br>I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A         210<br>110         mcc.<br>mcc.           EN/UVLO Threshold         EN/UVLO Falling         •         0.78         0.8         0.82         V           EN/UVLO Threshold         EN/UVLO Falling         •         0.78         0.8         0.82         V           EN/UVLO Hysteresis         100         mN         100         mN           EN/UVLO Input Current         V <sub>EN</sub> /UVLO = 42V         -250         0         250         nA           EN2 Threshold         EN2 Falling         •         0.78         0.81         0.84         V           EN2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising         •         4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         •         -10         -7.5         -4.5         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         CL           T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Peak Current Limit                                                    |                                                                                                       |   | 4.2   | 4.8  | 5.4   | A                 |

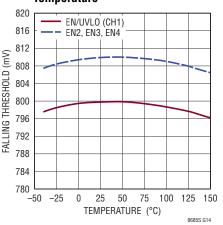

| EN/UVLO Hysteresis         100         mN           EN/UVLO Input Current         V <sub>EN</sub> /UVLO = 42V         -250         0         250         nA           EN2 Threshold         EN2 Falling         0.78         0.81         0.84         N           EN2 Hysteresis         50         mN         0.78         0.81         0.84         N           EN2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising         4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         -10         -7.5         -4.5         %           Pgood Lawage         V <sub>PG1</sub> , V <sub>FG2</sub> = 6V         -250         0         250         nA           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         0.0         0.0           RK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         µA           Channels 3 to 4         -100         0         100         nA           Feedback Reference Voltage         0.688         0.7         0.712         N           Feedback Input Current         0.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Main Switch (Top)                                                     |                                                                                                       |   |       |      |       | mΩ<br>mΩ          |

| EN/UVLO Input Current $V_{EN/}UVLO = 42V$ $-250$ 0         250         nA           EN2 Threshold         EN2 Falling         0.78         0.81         0.84         V           EN2 Hysteresis         50         mV         50         mV           EN2 Input Current $V_{EN2} = 42V$ $-250$ 0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising         4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling $-10$ $-7.5$ $-4.5$ %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling $-10$ $-7.5$ $-4.5$ %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V $-250$ 0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         GC           TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2 $\mu$ A           Feedback Reference Voltage          0.688         0.7         0.712         V           Feedback Input Current         V <sub>VIN1</sub> = 3V to 42V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EN/UVLO Threshold                                                     | EN/UVLO Falling                                                                                       | • | 0.78  | 0.8  | 0.82  | V                 |

| EN2 Threshold         EN2 Falling         0.78         0.81         0.84         N           EN2 Hysteresis         50         mN           EN2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising         4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising         -10         -7.5         -4.5         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling         -10         -7.5         -4.5         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         0.0         0.0         0.0         0.0         0.0           TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         µA         0.688         0.7         0.712         V           Feedback Reference Voltage          0.688         0.7         0.712         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EN/UVLO Hysteresis                                                    |                                                                                                       |   |       | 100  |       | mV                |

| EN2 Hysteresis         50         mV           EN2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising          4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising          -10         -7.5         -4.5         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling          -10         -7.5         -4.5         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         GC           TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         µA           Channels 3 to 4           0.688         0.7         0.712         V           Feedback Input Current            0         0         100         nA           V <sub>FB3</sub> , V <sub>FB4</sub> Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %/V         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EN/UVLO Input Current                                                 | $V_{EN}/UVLO = 42V$                                                                                   |   | -250  | 0    | 250   | nA                |

| EN2 Input Current         V <sub>EN2</sub> = 42V         -250         0         250         nA           Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising          4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Railing          -10         -7.5         -4.5         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>FB2</sub> Falling          1.2         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         GC           TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         µA           Channels 3 to 4           -100         0         100         nA           Feedback Input Current         V <sub>VIN1</sub> = 3V to 42V         0.01         %/V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EN2 Threshold                                                         | EN2 Falling                                                                                           |   | 0.78  | 0.81 | 0.84  | V                 |

| Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Rising         4.5         7.5         10         %           Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling          -10         -7.5         -4.5         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>FB2</sub> e 6V         1.2         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         GC           TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         µA           Feedback Reference Voltage         0.688         0.7         0.712         V           Feedback Input Current         V <sub>VIN1</sub> = 3V to 42V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EN2 Hysteresis                                                        |                                                                                                       |   |       | 50   |       | mV                |

| Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling <ul> <li>-10</li> <li>-7.5</li> <li>-4.5</li> <li>%</li> </ul> Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> V <sub>FB1</sub> , V <sub>FB2</sub> Falling <ul> <li>1.2</li> <li>%</li> <li>1.2</li> <li>%</li> <li>Pgood Leakage</li> <li>V<sub>PG1</sub>, V<sub>PG2</sub> = 6V</li> <li>-250</li> <li>0</li> <li>250</li> <li>nA</li> <li>Pgood Pull-Down Resistance</li> <li>V<sub>PG1</sub>, V<sub>PG2</sub> = 0.1V</li> <li>500</li> <li>1200</li> <li>GC</li> <li>TRK/SS1, TRK/SS2 Pull-Up Current</li> <li>V<sub>TRK/SS1</sub>, V<sub>TRK/SS2</sub> = 0V</li> <li>2</li> <li>µA</li> <li>Channels 3 to 4</li> <li>Feedback Reference Voltage</li> <li>0.688</li> <li>0.7</li>                             0.712                             N <li>-100</li>                            0                          100                           nA</ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EN2 Input Current                                                     | V <sub>EN2</sub> = 42V                                                                                |   | -250  | 0    | 250   | nA                |

| Pgood Hysteresis         1.2         %           Pgood Leakage         V <sub>PG1</sub> , V <sub>PG2</sub> = 6V         -250         0         250         nA           Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         GC           TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         μA           Channels 3 to 4           Feedback Reference Voltage         •         0.688         0.7         0.712         V           Feedback Input Current         V <sub>VIN1</sub> = 3V to 42V         •         0.01         %/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pgood Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> | V <sub>FB1</sub> , V <sub>FB2</sub> Rising                                                            | • | 4.5   | 7.5  | 10    | %                 |

| Pgood Leakage $V_{PG1}$ , $V_{PG2} = 6V$ $-250$ $0$ $250$ $nA$ Pgood Pull-Down Resistance $V_{PG1}$ , $V_{PG2} = 0.1V$ $500$ $1200$ $GC$ TRK/SS1, TRK/SS2 Pull-Up Current $V_{TRK/SS1}$ , $V_{TRK/SS2} = 0V$ $2$ $\mu A$ Channels 3 to 4 $edback$ Reference Voltage $0.688$ $0.7$ $0.712$ $N$ Feedback Input Current $-100$ $0$ $100$ $nA$ $V_{FB3}$ , $V_{FB4}$ Line Regulation $V_{VIN1} = 3V$ to $42V$ $0.01$ $\%/N$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pgood Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub> | V <sub>FB1</sub> , V <sub>FB2</sub> Falling                                                           | • | -10   | -7.5 | -4.5  | %                 |

| Pgood Pull-Down Resistance         V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V         500         1200         G           TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         μA           Channels 3 to 4         •         0.688         0.7         0.712         V           Feedback Reference Voltage         •         0.688         0.7         0.712         V           Feedback Input Current         •         -100         0         100         nA           V <sub>FB3</sub> , V <sub>FB4</sub> Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pgood Hysteresis                                                      |                                                                                                       |   |       | 1.2  |       | %                 |

| TRK/SS1, TRK/SS2 Pull-Up Current         V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V         2         μA           Channels 3 to 4         •         0.688         0.7         0.712         V           Feedback Reference Voltage         •         0.688         0.7         0.712         V           Feedback Input Current         •         -100         0         100         nA           V <sub>FB3</sub> , V <sub>FB4</sub> Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pgood Leakage                                                         | $V_{PG1}, V_{PG2} = 6V$                                                                               |   | -250  | 0    | 250   | nA                |

| Channels 3 to 4         •         0.688         0.7         0.712         V           Feedback Reference Voltage         •         0.688         0.7         0.712         V           Feedback Input Current         •         -100         0         100         nA           V <sub>FB3</sub> , V <sub>FB4</sub> Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pgood Pull-Down Resistance                                            | V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V                                                            |   |       | 500  | 1200  | Ω                 |

| Feedback Reference Voltage         •         0.688         0.7         0.712         V           Feedback Input Current         •         -100         0         100         nA           V <sub>FB3</sub> , V <sub>FB4</sub> Line Regulation         V <sub>VIN1</sub> = 3V to 42V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TRK/SS1, TRK/SS2 Pull-Up Current                                      | V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V                                                      |   |       | 2    |       | μA                |

| Feedback Input Current         •         -100         0         100         nA           VFB3, VFB4 Line Regulation         VVIN1 = 3V to 42V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Channels 3 to 4                                                       | · ·                                                                                                   |   |       |      |       | . <u> </u>        |

| VFB3, VFB4 Line Regulation         VVIN1 = 3V to 42V         0.01         %/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Feedback Reference Voltage                                            |                                                                                                       | • | 0.688 | 0.7  | 0.712 | V                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Feedback Input Current                                                |                                                                                                       | • | -100  | 0    | 100   | nA                |

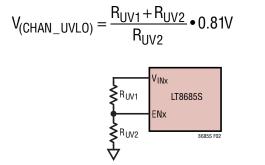

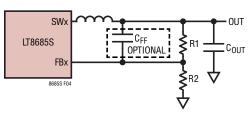

| Peak Current Limit 7 8.2 9.4 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>FB3</sub> , V <sub>FB4</sub> Line Regulation                   | V <sub>VIN1</sub> = 3V to 42V                                                                         |   |       | 0.01 |       | %/V               |