# 16-Bit, 8-Channel, 500 kSPS/1 MSPS, Easy Drive Multiplexed SAR ADC

#### **FEATURES**

- Easy Drive

- Reduced analog input and reference drive requirements

- ▶ On-chip reference buffer (WLCSP only)

- Overvoltage protection up to 5 mA on each analog input

- Long acquisition phase, ≥71.5% (715 ns/1000 ns) of cycle time at 1 MSPS

- ▶ High performance

- Sample rate: 500 kSPS (AD4697) or 1 MSPS (AD4698)

- ▶ INL: ±1 LSB maximum

- ▶ Guaranteed 16-bit, no missing codes

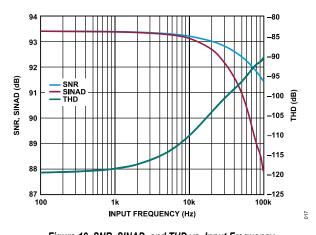

- ► SINAD: 93 dB typical, f<sub>IN</sub> = 1 kHz

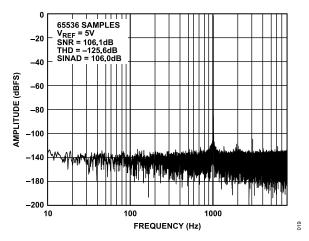

- ▶ Oversampled dynamic range: 111.2 dB, OSR = 64

- Small footprint, high channel density

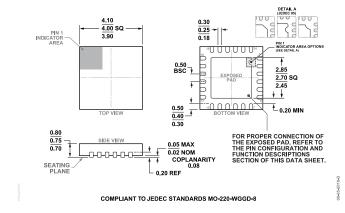

- 24-lead, 4.00 mm × 4.00 mm LFCSP

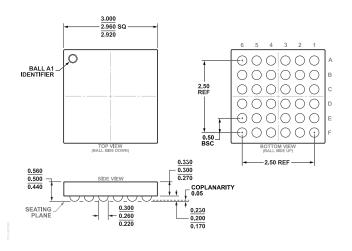

- ▶ 36-lead, 2.960 mm × 2.960 mm WLCSP

- Easy Drive features support system level designs with fewer components

- Enhanced digital functionality

- ▶ First conversion accurate, no latency or pipeline delay

- ▶ Fast conversion time and dual-/quad-SDO modes allow low SPI clock rates

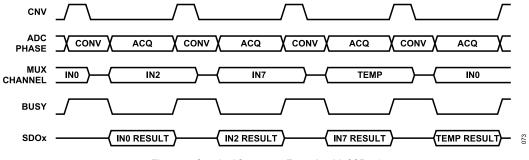

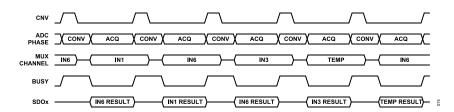

- ► Customizable channel sequencer

- On-chip oversampling and decimation

- ► Threshold detection alerts

- Offset and gain correction

- Autonomous conversion (autocycle) mode

- ▶ 1.14 V to 1.98 V logic SPI

- Low power

- $\blacktriangleright$  8 mW at f<sub>S</sub> = 1 MSPS and 4 mW at f<sub>S</sub> = 500 kSPS

- 4 µW standby power dissipation with the internal LDO disabled

- ▶ Internal LDO enables 2.7 V to 5.5 V, single analog supply operation

- ▶ Wide operating temperature range: -40°C to +125°C

#### **APPLICATIONS**

- Photodiode monitoring

- Medical instrumentation

- Vital signs monitoring

- ▶ Electronic test and measurement

- Automated test equipment

- Instrumentation and process control

- Battery-powered equipment

#### Rev. B

# **GENERAL DESCRIPTION**

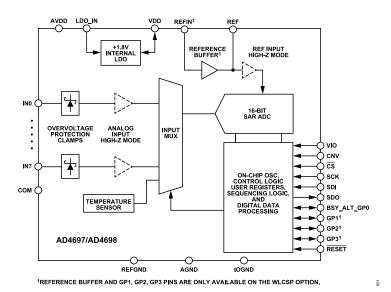

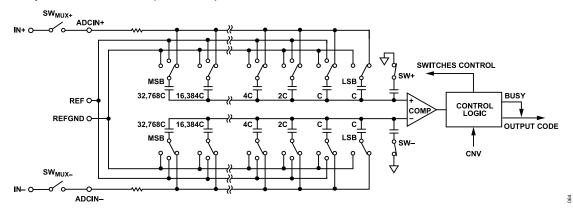

The AD4697/AD4698 are compact, high accuracy, low power, 8-channel, 16-bit, 500 kSPS/1 MSPS, multiplexed input precision, successive approximation register (SAR) analog-to-digital converters (ADCs) with Easy Drive features and extensive digital functionality.

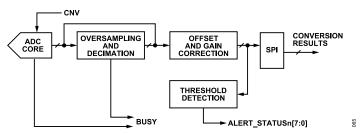

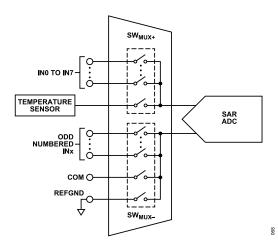

The AD4697/AD4698 are optimal for use in space constrained, multichannel, precision data acquisition systems and monitoring circuits. The AD4697/AD4698 feature a true 16-bit SAR ADC core with no missing codes, an 8-channel, low crosstalk multiplexer, a flexible channel sequencer, overvoltage protection clamp circuits on each analog input, on-chip oversampling and decimation, threshold detection and alert indicators, and an autonomous conversion (autocycle) mode.

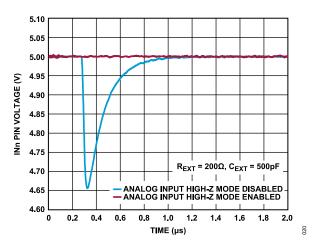

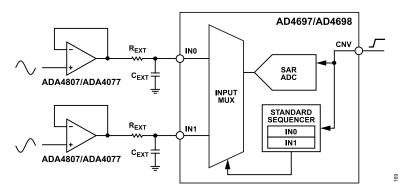

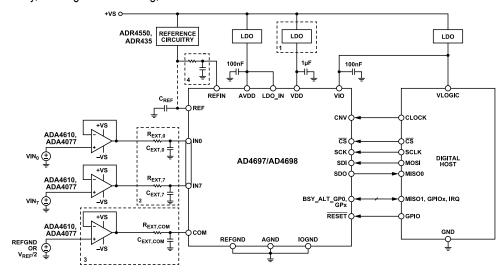

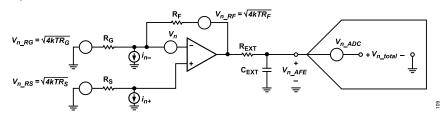

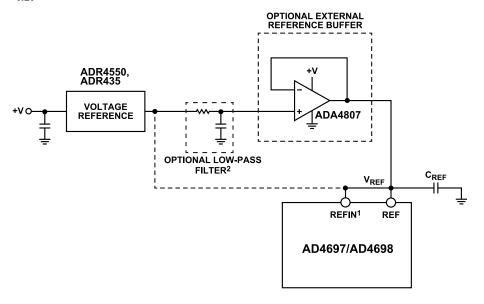

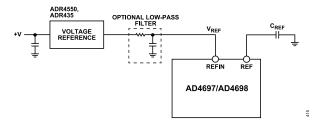

The AD4697/AD4698 Easy Drive features relax the drive requirements of the analog front end (AFE) and reference circuitry. Analog input high-Z mode and reference input high-Z mode simplify system designs, reduce component count, and increase channel density by removing the need for dedicated high speed ADC drivers and reference buffers. The WLCSP option of the AD4697/AD4698 includes an internal reference buffer, which provides a true, buffered reference input.

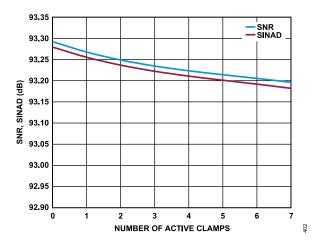

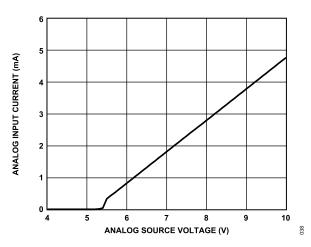

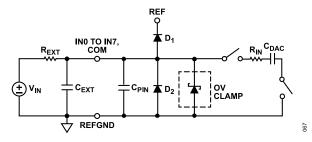

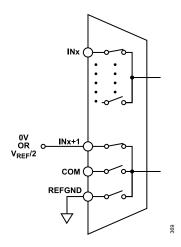

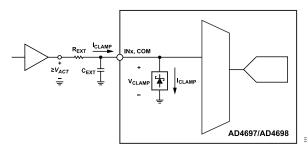

Input overvoltage protection clamps on each analog input protect the AD4697/AD4698 from overvoltage events and prevent overvoltage events on one channel from degrading performance on other channels (see Figure 27).

Advanced digital functionality makes the AD4697/AD4698 compatible with a variety of low power digital hosts. The low serial peripheral interface (SPI) clock rate requirements, on-chip customizable channel sequencers, and oversampling and decimation reduce the burden on the digital host system. Autocycle mode and threshold detection features enable low power, interrupt driven firmware design by performing conversions autonomously and generating alerts based on channel specific threshold limits.

The AD4697/AD4698 are available in a 4.00 mm  $\times$  4.00 mm, 24-lead lead frame chip scale package (LFCSP) and a 2.960 mm  $\times$  2.960 mm, 36-lead wafer level chip scale package (WLCSP). All packages are specified with operation from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .

# **TABLE OF CONTENTS**

| A polications                                                                                                                                                                                                                                                                                                                                                                           | 1   | Channel Sequencing Modes             |                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------|----------------------------------|

| Applications                                                                                                                                                                                                                                                                                                                                                                            |     | Digital Interface                    |                                  |

| General Description                                                                                                                                                                                                                                                                                                                                                                     |     | Register Configuration Mode          |                                  |

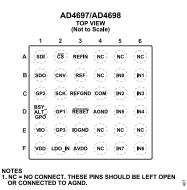

| Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                | 4   | Conversion Mode                      |                                  |

| Specifications                                                                                                                                                                                                                                                                                                                                                                          |     | Autocycle Mode                       |                                  |

| Timing Specifications                                                                                                                                                                                                                                                                                                                                                                   | 10  | General-Purpose Pins                 | 65                               |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                | .12 | Device Reset                         | 66                               |

| Thermal Resistance                                                                                                                                                                                                                                                                                                                                                                      |     | Applications Information             |                                  |

| Electrostatic Discharge (ESD) Ratings                                                                                                                                                                                                                                                                                                                                                   | .12 | Analog Front-End Design              | 71                               |

| ESD Caution                                                                                                                                                                                                                                                                                                                                                                             | .12 | Analog Input Overvoltage Protection  |                                  |

| Pin Configuration and Function Descriptions                                                                                                                                                                                                                                                                                                                                             | 13  | Reference Circuitry Design           | 74                               |

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                                     |     | Optimizing Reference Buffer Startup  |                                  |

| Terminology                                                                                                                                                                                                                                                                                                                                                                             |     | Converting Between Codes and Volts   |                                  |

| Theory of Operation                                                                                                                                                                                                                                                                                                                                                                     | .28 | Oversampling for Noise Reduction     |                                  |

| Overview                                                                                                                                                                                                                                                                                                                                                                                |     | Digital Interface Operation          |                                  |

| Converter Operation                                                                                                                                                                                                                                                                                                                                                                     | .28 | Device Configuration Recommendations | 85                               |

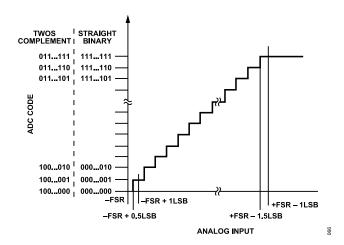

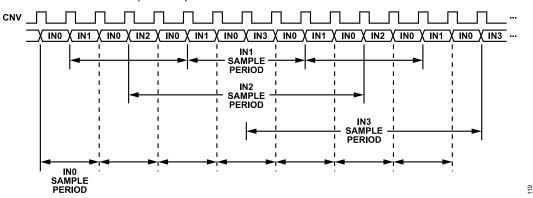

| Transfer Function                                                                                                                                                                                                                                                                                                                                                                       | 30  | Effective Channel Sample Rate        |                                  |

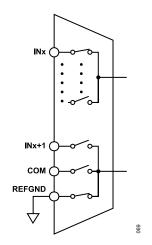

| Analog Inputs                                                                                                                                                                                                                                                                                                                                                                           |     | Layout Guidelines                    |                                  |

| Input Overvoltage Protection Clamps                                                                                                                                                                                                                                                                                                                                                     | .35 | Evaluating AD4697/AD4698 Performance |                                  |

| Temperature Sensor                                                                                                                                                                                                                                                                                                                                                                      |     | Register Information                 |                                  |

| Voltage Reference Input                                                                                                                                                                                                                                                                                                                                                                 | .36 | Register Overview                    |                                  |

| Power Supplies                                                                                                                                                                                                                                                                                                                                                                          |     | Register Details                     |                                  |

| Oversampling and Decimation                                                                                                                                                                                                                                                                                                                                                             |     | Outline Dimensions                   |                                  |

| Offset and Gain Correction                                                                                                                                                                                                                                                                                                                                                              |     | Ordering Guide                       |                                  |

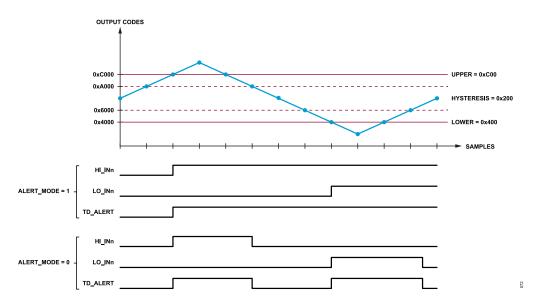

| Threshold Detection and Alert Indicators                                                                                                                                                                                                                                                                                                                                                |     | Evaluation Boards                    | 109                              |

| Busy Indicator                                                                                                                                                                                                                                                                                                                                                                          | .42 |                                      |                                  |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                        |     |                                      |                                  |

| 6/2023—Rev. A to Rev. B                                                                                                                                                                                                                                                                                                                                                                 |     |                                      |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                         |     |                                      |                                  |

| •                                                                                                                                                                                                                                                                                                                                                                                       |     |                                      | -                                |

|                                                                                                                                                                                                                                                                                                                                                                                         |     |                                      |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                         |     |                                      | 5                                |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      | 5<br>10                          |

| Change to Timing Specifications SectionChange to Table 7                                                                                                                                                                                                                                                                                                                                |     |                                      | 5<br>10<br>13                    |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      | 5<br>10<br>13                    |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      | 5<br>10<br>13<br>14              |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      | 5<br>10<br>14<br>18<br>21        |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      | 10<br>13<br>14<br>18<br>21       |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      | 10<br>14<br>18<br>21             |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      | 10<br>13<br>14<br>18<br>21<br>25 |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      |                                  |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      |                                  |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      |                                  |

| Change to Timing Specifications Section Change to Table 7 Changes to Table 8 Changes to Figure 18 Changes to Figure 35 Changes to Figure 47 Added Figure 63; Renumbered Sequentially Changes to Offset Error Section Deleted Offset Error Match Section Changes to Gain Error Section Deleted Gain Error Match Section Added Full-Scale Error Section                                   |     |                                      |                                  |

| Change to Timing Specifications Section                                                                                                                                                                                                                                                                                                                                                 |     |                                      |                                  |

| Change to Timing Specifications Section Change to Table 7 Changes to Table 8 Changes to Figure 18 Changes to Figure 35 Changes to Figure 47 Added Figure 63; Renumbered Sequentially Changes to Offset Error Section Deleted Offset Error Match Section Changes to Gain Error Section Deleted Gain Error Match Section Added Full-Scale Error Section                                   |     |                                      |                                  |

| Change to Timing Specifications Section Change to Table 7 Changes to Table 8 Changes to Figure 18 Changes to Figure 35 Changes to Figure 47. Added Figure 63; Renumbered Sequentially Changes to Offset Error Section Deleted Offset Error Match Section Changes to Gain Error Section Deleted Gain Error Match Section Added Full-Scale Error Section Change to Power Supplies Section |     |                                      |                                  |

# **TABLE OF CONTENTS**

| Change to Standby Power Dissipation, Internal LDO Enabled Parameter, Table 1             | 5   |

|------------------------------------------------------------------------------------------|-----|

| Changes to Table 6 Title                                                                 |     |

| Changes to Figure 3 and Table 8 Title                                                    |     |

| Changes to Figure 43                                                                     |     |

| Changes to Overvoltage Reduced Current Mode Section                                      |     |

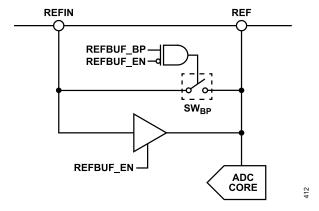

| Changes to Internal Reference Buffer Section                                             | 37  |

| Change to Alert Indicator on General-Purpose Pins Section                                | 40  |

| Change to Busy Indicator on General-Purpose Pins Section                                 | 42  |

| Changes to Figure 77                                                                     | 45  |

| Changes to Checksum Protection Section                                                   |     |

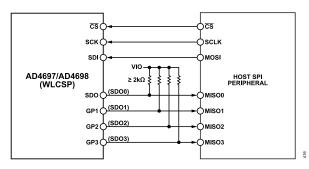

| Change to Serial Data Output Modes Section                                               | 55  |

| Changes to General-Purpose Pins Section                                                  | 65  |

| Changes to Analog Front-End Noise in Pseudobipolar Mode Section                          | 73  |

| Changes to Reference Circuitry Design Section                                            | 74  |

| Change to Reference Circuit Design for Driving REF Input Section                         | 75  |

| Changes to Reference Circuit Design for Internal Reference Buffer Section and Figure 117 | 76  |

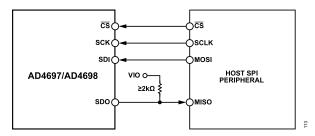

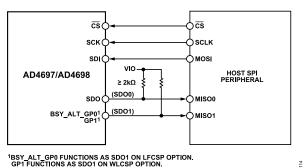

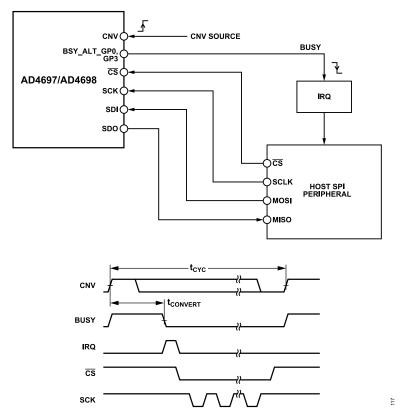

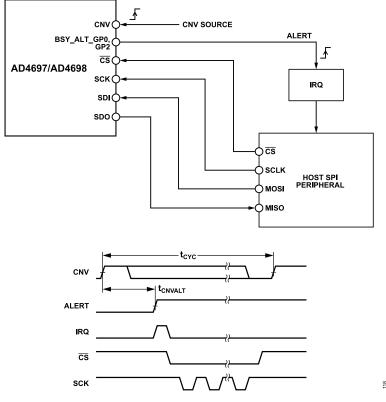

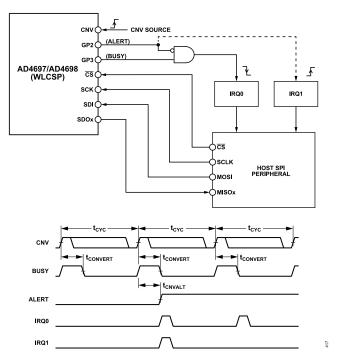

| Changes to SPI Peripheral Connections Section and Figure 120                             | 78  |

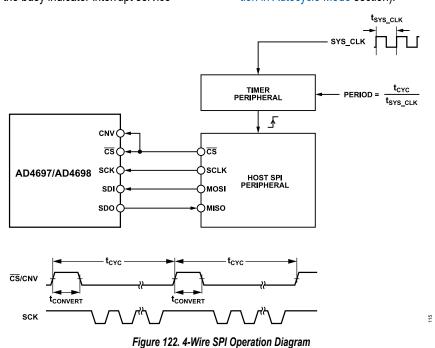

| Changes to SPI Peripheral Synchronization in Conversion Mode Section and Figure 125      | 79  |

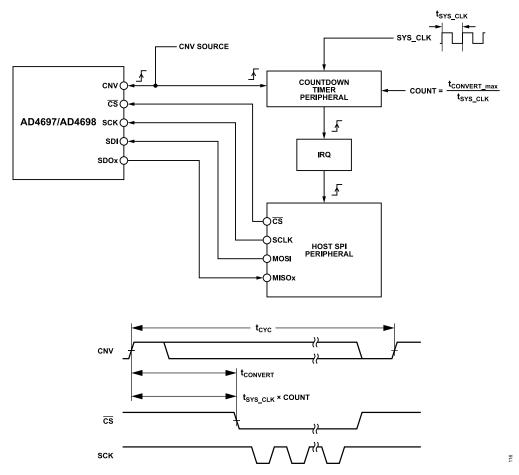

| Change to SPI Peripheral Synchronization in Autocycle Mode Section                       | 83  |

| Change to Conversion Mode SPI Clock Frequency Requirements Section                       | 84  |

| Changes to Ordering Guide                                                                | 108 |

| Added Evaluation Boards                                                                  | 109 |

4/2022—Revision 0: Initial Version

analog.com Rev. B | 3 of 109

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

analog.com Rev. B | 4 of 109

AVDD = 2.7 V to 5.5 V, LDO\_IN = 2.4 V to 5.5 V with internal low dropout (LDO) enabled, LDO\_IN = AGND with internal LDO disabled, VDD = 1.71 V to 1.89 V with internal LDO disabled, VIO = 1.14 V to 1.98 V, AGND = REFGND = IOGND = 0 V, reference voltage ( $V_{REF}$ ) = 2.4 V to 5.1 V, REF =  $V_{REF}$  with internal reference buffer disabled, REFIN =  $V_{REF}$  with internal reference buffer enabled, reference buffer boost mode enabled, sample rate ( $f_S$ ) = 1 MSPS for the AD4698,  $f_S$  = 500 kSPS for the AD4697, input frequency ( $f_{IN}$ ) = 1 kHz, digital output load capacitance = 20 pF, autocycle mode disabled, analog input high-Z mode enabled, reference input high-Z mode enabled, busy indicator and alert indicator not enabled on general-purpose pins, no active overvoltage protection clamps, and  $T_A$  = -40°C to +125°C, unless otherwise noted.

Table 1

| Parameter                                 | Test Conditions/Comments                                            | Min                       | Тур                 | Max                    | Unit             |

|-------------------------------------------|---------------------------------------------------------------------|---------------------------|---------------------|------------------------|------------------|

| RESOLUTION                                |                                                                     | 16                        |                     |                        | Bits             |

| ANALOG INPUT <sup>1, 2</sup>              |                                                                     |                           |                     |                        |                  |

| Input Voltage Range                       | Positive ADC input voltage (IN+) – negative ADC input voltage (IN-) |                           |                     |                        |                  |

| Unipolar Mode                             |                                                                     | 0                         |                     | +V <sub>REF</sub>      | V                |

| Pseudobipolar Mode                        |                                                                     | -V <sub>REF</sub> /2      |                     | +V <sub>REF</sub> /2   | V                |

| Operating Input Voltage                   |                                                                     |                           |                     |                        |                  |

| IN+ - REFGND                              | IN- = REFGND                                                        | 0                         |                     | +V <sub>REF</sub>      | V                |

|                                           | IN- = COM, odd numbered input                                       | -0.1                      |                     | V <sub>REF</sub> + 0.1 | V                |

| IN REFGND                                 | IN- = COM, odd numbered input                                       |                           |                     |                        |                  |

|                                           | Unipolar mode                                                       | -0.1                      |                     | V <sub>REF</sub> + 0.1 | V                |

|                                           | Pseudobipolar mode                                                  | V <sub>REF</sub> /2 – 0.1 | V <sub>REF</sub> /2 | $V_{REF}/2 + 0.1$      | V                |

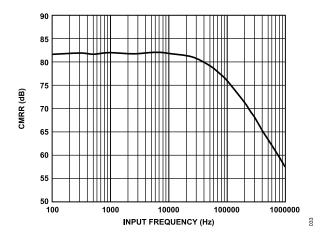

| Common-Mode Rejection Ratio (CMRR)        | f <sub>IN</sub> = 250 kHz, IN− = COM, odd numbered input            |                           | 69.5                |                        | dB               |

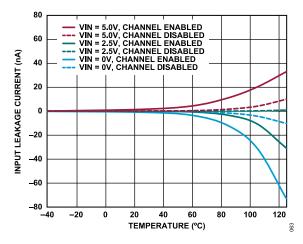

| Analog Input Leakage Current <sup>3</sup> | IN+ = 5 V, IN- = 0 V                                                |                           | 2                   |                        | nA               |

| SAMPLING DYNAMICS                         |                                                                     |                           |                     |                        |                  |

| Sample Rate                               | Autocycle mode disabled                                             |                           |                     |                        |                  |

| AD4697                                    |                                                                     |                           |                     | 500                    | kSPS             |

| AD4698                                    |                                                                     |                           |                     | 1                      | MSPS             |

| Autocycle Sample Period                   | Autocycle mode enabled                                              |                           |                     |                        |                  |

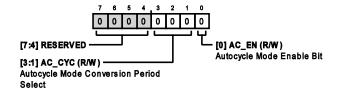

|                                           | $AC_CYC = 0x0$                                                      | 8.5                       | 10                  | 11.5                   | μs               |

|                                           | AC_CYC = 0x1                                                        | 17                        | 20                  | 23                     | μs               |

|                                           | AC_CYC = 0x2                                                        | 34                        | 40                  | 46                     | μs               |

|                                           | AC_CYC = 0x3                                                        | 68                        | 80                  | 92                     | μs               |

|                                           | AC_CYC = 0x4                                                        | 85                        | 100                 | 115                    | μs               |

|                                           | AC_CYC = 0x5                                                        | 170                       | 200                 | 230                    | μs               |

|                                           | AC_CYC = 0x6                                                        | 340                       | 400                 | 460                    | μs               |

|                                           | AC_CYC = 0x7                                                        | 680                       | 800                 | 920                    | μs               |

| Aperture Delay                            | _                                                                   |                           | 2                   |                        | ns               |

| Aperture Jitter                           |                                                                     |                           | 0.5                 |                        | ps rms           |

| DC ACCURACY                               | V <sub>REF</sub> = 5 V                                              |                           |                     |                        |                  |

| No Missing Codes                          |                                                                     | 16                        |                     |                        | Bits             |

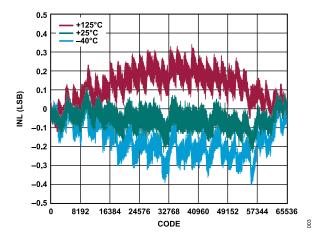

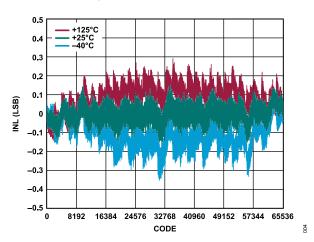

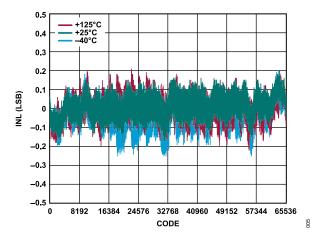

| Integral Nonlinearity Error (INL)         | Oversampling ratio (OSR) = 1                                        |                           |                     |                        |                  |

| , , ,                                     | LFCSP, $T_A = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$        | -1                        | ±0.4                | +1                     | LSB              |

|                                           | WLCSP, T <sub>A</sub> = 0°C to +70°C                                | -2                        | ±0.4                | +2                     | LSB              |

|                                           | WLCSP, $T_A = -40$ °C to +125°C                                     | -2.5                      | ±0.4                | +2.5                   | LSB              |

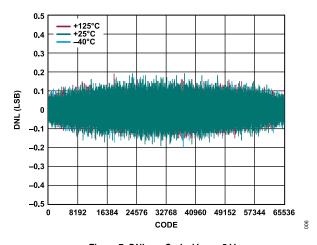

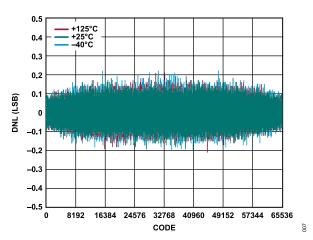

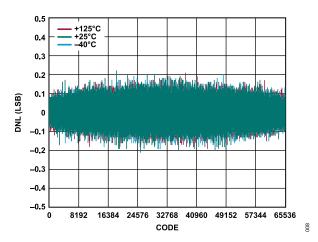

| Differential Nonlinearity Error (DNL)     | OSR = 1                                                             | -0.6                      | ±0.3                | +0.6                   | LSB              |

| Transition Noise                          |                                                                     |                           | 0.5                 |                        | LSB rms          |

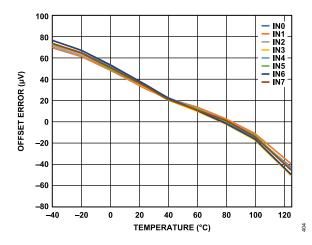

| Offset Error <sup>4</sup>                 |                                                                     | -360                      | ±30                 | +360                   | μV               |

| Offset Error Drift <sup>5</sup>           |                                                                     |                           | ±1.1                |                        | μV/°C            |

| Offset Error Match <sup>4</sup>           |                                                                     | -230                      | ±25                 | +230                   | μV               |

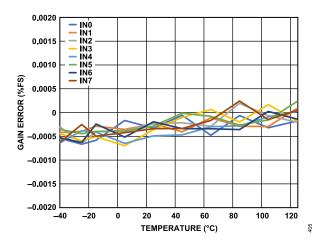

| Gain Error <sup>4</sup>                   |                                                                     | -0.0125                   | ±0.001              | +0.0125                | %FS <sup>6</sup> |

analog.com Rev. B | 5 of 109

Table 1. (Continued)

| Parameter                              | Test Conditions/Comments                                                           | Min    | Тур            | Max         | Unit     |

|----------------------------------------|------------------------------------------------------------------------------------|--------|----------------|-------------|----------|

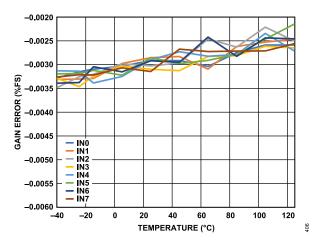

| Gain Error Drift                       |                                                                                    |        | ±0.08          |             | ppm/°C   |

| Gain Error Match <sup>4</sup>          |                                                                                    | -0.012 | ±0.002         | +0.012      | %FS      |

| Full-Scale Error                       |                                                                                    | -11    | ±0.6           | +11         | LSB      |

| Full-Scale Error Drift                 |                                                                                    |        | ±0.25          |             | ppm/°C   |

| AC PERFORMANCE                         | AVDD = 5 V                                                                         |        |                |             |          |

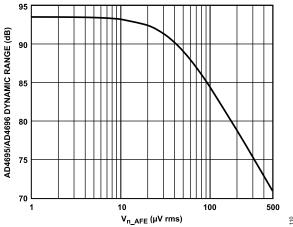

| Dynamic Range                          | V <sub>REF</sub> = 5 V                                                             |        |                |             |          |

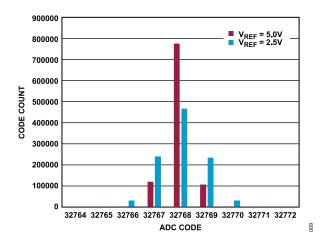

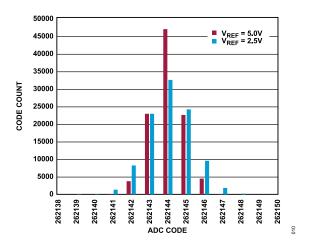

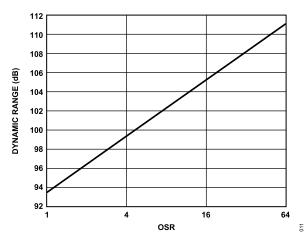

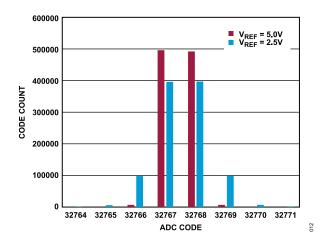

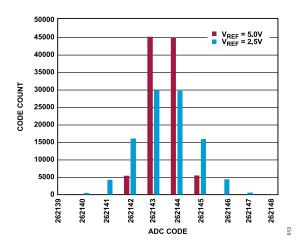

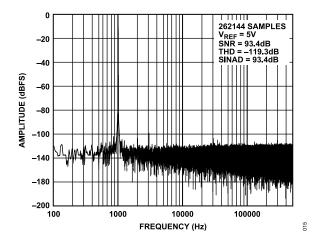

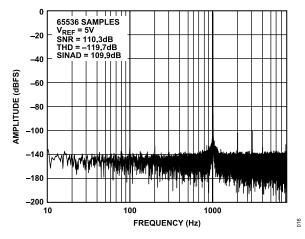

| ,                                      | OSR = 1                                                                            |        | 93.4           |             | dB       |

|                                        | OSR = 4                                                                            |        | 99.3           |             | dB       |

|                                        | OSR = 16                                                                           |        | 105.3          |             | dB       |

|                                        | OSR = 64                                                                           |        | 111.2          |             | dB       |

| Input RMS Noise                        | OSR = 1                                                                            |        | 37.8           |             | μV rms   |

| '                                      | OSR = 4                                                                            |        | 19.2           |             | μV rms   |

|                                        | OSR = 16                                                                           |        | 9.6            |             | μV rms   |

|                                        | OSR = 64                                                                           |        | 4.9            |             | μV rms   |

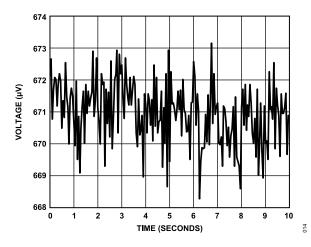

| 1/f Noise                              | Bandwidth = 0.1 Hz to 10 Hz                                                        |        | 5              |             | μV p-p   |

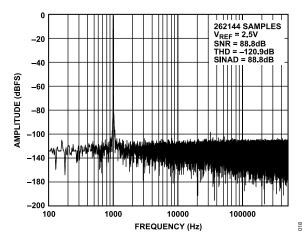

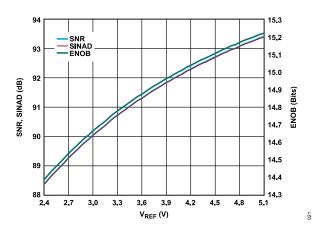

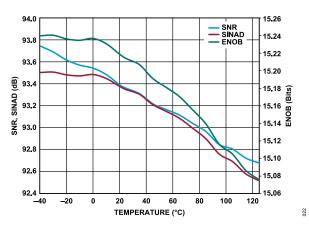

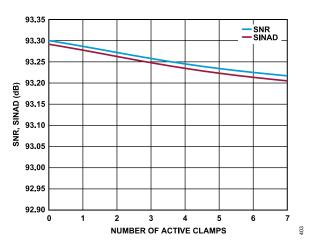

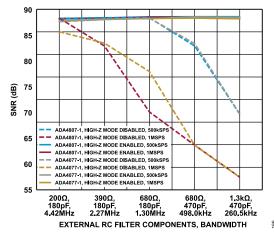

| Signal-to-Noise Ratio (SNR)            | $V_{RFF} = 5 \text{ V}, f_{IN} = 1 \text{ kHz}$                                    | 91.25  | 93             |             | dB       |

| Olgital to Holse Hado (OHH)            | $V_{RFF} = 4.096 \text{ V}, f_{IN} = 1 \text{ kHz}$                                | 31.20  | 91.3           |             | dB       |

|                                        | $V_{REF} = 4.000 \text{ V}, N_{IN} = 1 \text{ kHz}$                                |        | 87             |             | dB       |

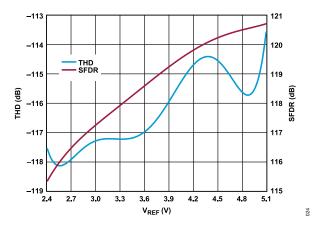

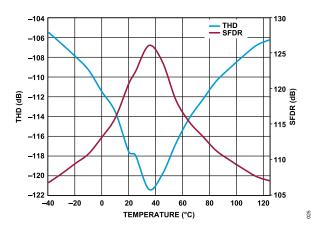

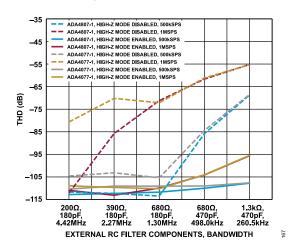

| Total Harmonic Distortion (THD)        | $V_{RFF} = 5 \text{ V, } f_{IN} = 1 \text{ kHz}$                                   |        | -117           |             | dB       |

| Total Harmonic Distortion (TTD)        | $V_{REF} = 4.096 \text{ V}, f_{IN} = 1 \text{ kHz}$                                |        | -117.5         |             | dB       |

|                                        | 112                                                                                |        | -117.3<br>-119 |             | dB       |

| Signal to Naise and Distortion (SINAD) | $V_{REF} = 2.5 \text{ V}, f_{IN} = 1 \text{ kHz}$                                  |        | -119           |             | ub       |

| Signal-to-Noise-and-Distortion (SINAD) | V 5V5 4111-                                                                        | 04.4   | 00             |             | -ID      |

| LFCSP                                  | V <sub>REF</sub> = 5 V, f <sub>IN</sub> = 1 kHz                                    | 91.1   | 93             |             | dB       |

|                                        | $V_{REF} = 4.096 \text{ V}, f_{IN} = 1 \text{ kHz}$                                |        | 91.3           |             | dB       |

|                                        | $V_{REF} = 2.5 \text{ V}, f_{IN} = 1 \text{ kHz}$                                  |        | 87             |             | dB       |

| WLCSP                                  | $V_{REF} = 5 \text{ V}, f_{IN} = 1 \text{ kHz}$                                    | 89     | 93             |             | dB       |

| Spurious-Free Dynamic Range (SFDR)     | $V_{REF} = 5 V$                                                                    |        | 121            |             | dB       |

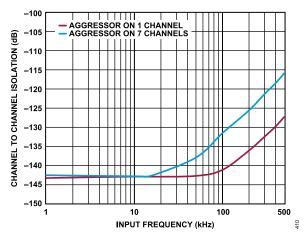

| Channel to Channel Isolation           | $f_{IN} = 100 \text{ kHz}$                                                         |        |                |             |          |

|                                        | LFCSP                                                                              |        | -126           |             | dB       |

|                                        | WLCSP                                                                              |        | -130           |             | dB       |

| Channel to Channel Memory              | $f_{IN}$ = 100 kHz, $f_S$ = 1 MSPS                                                 |        | -100           |             | dB       |

|                                        | $f_{IN}$ = 100 kHz, $f_{S}$ = 500 kSPS                                             |        | -110           |             | dB       |

| −3 dB Input Bandwidth                  |                                                                                    |        | 11.7           |             | MHz      |

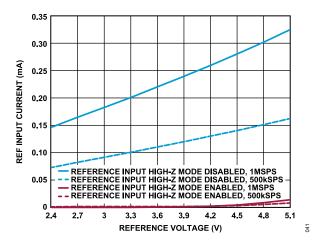

| REFERENCE INPUT <sup>7</sup>           |                                                                                    |        |                |             |          |

| V <sub>REF</sub> Range                 | REF input, internal reference buffer disabled                                      | 2.4    |                | AVDD + 0.25 | V        |

|                                        | REFIN input, internal reference buffer disabled                                    |        | REF            |             | V        |

|                                        | REFIN input, internal reference buffer enabled                                     | 2.4    |                | AVDD - 0.3  | V        |

| REF Leakage Current                    | V <sub>REF</sub> = 5 V                                                             |        |                |             |          |

| LFCSP                                  | No active overvoltage protection clamps                                            |        | 165            |             | nA       |

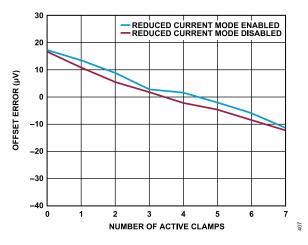

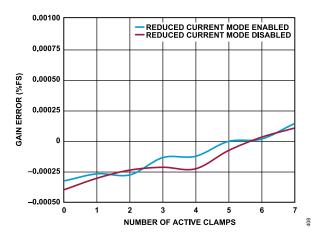

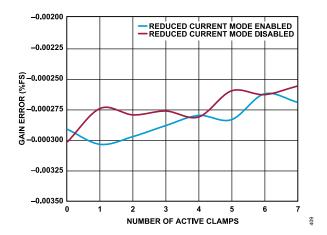

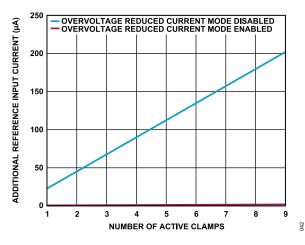

|                                        | All clamps active, overvoltage reduced current mode disabled                       |        | 200            |             | μΑ       |

|                                        | All clamps active, overvoltage reduced current mode enabled                        |        | 4              |             | μА       |

| WLCSP                                  | Internal reference buffer disabled                                                 |        | 165            |             | nA       |

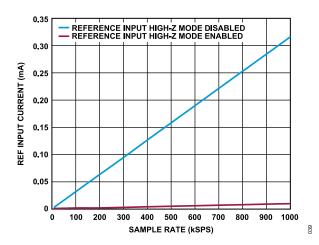

| REF Average Input Current              | V <sub>REF</sub> = AVDD = 5 V, internal reference buffer disabled                  |        |                |             |          |

| · · · · · · · · · · · · · · · · · · ·  | f <sub>S</sub> = 10 kSPS, unipolar mode                                            |        | 3.3            |             | μA       |

| Reference High-Z iviode Disabled       |                                                                                    | 1      |                |             | 11.      |

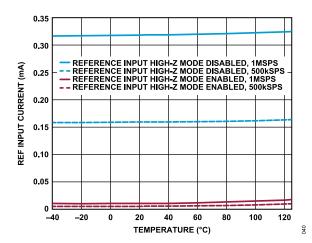

| Reference High-Z Mode Disabled         | 1 -                                                                                |        | 160            |             | uΑ       |

| Reference High-Z Mode Disabled         | f <sub>S</sub> = 500 kSPS, unipolar mode<br>f <sub>S</sub> = 1 MSPS, unipolar mode |        | 160<br>320     |             | μA<br>μA |

analog.com Rev. B | 6 of 109

Table 1. (Continued)

| Parameter                                                                  | Test Conditions/Comments                                      | Min T                  | ур Мах                  | Unit  |

|----------------------------------------------------------------------------|---------------------------------------------------------------|------------------------|-------------------------|-------|

|                                                                            | f <sub>S</sub> = 500 kSPS, pseudobipolar mode                 | 1                      | 95                      | μA    |

|                                                                            | f <sub>S</sub> = 1 MSPS, pseudobipolar mode                   | 3                      | 90                      | μA    |

| Reference High-Z Mode Enabled                                              | f <sub>S</sub> = 10 kSPS, unipolar mode                       | 0                      | .3                      | μA    |

|                                                                            | f <sub>S</sub> = 500 kSPS, unipolar mode                      | 6                      |                         | μA    |

|                                                                            | f <sub>S</sub> = 1 MSPS, unipolar mode                        | 1                      | 2                       | μA    |

|                                                                            | f <sub>S</sub> = 10 kSPS, pseudobipolar mode                  | 0                      | .4                      | μA    |

|                                                                            | f <sub>S</sub> = 500 kSPS, pseudobipolar mode                 | 1                      | 1                       | μA    |

|                                                                            | f <sub>S</sub> = 1 MSPS, pseudobipolar mode                   | 2                      | 2                       | μA    |

| REFIN Current                                                              | V <sub>REF</sub> = 5 V                                        |                        |                         |       |

| Internal Reference Buffer Enabled                                          | No active overvoltage protection clamps                       | 1                      | 6                       | nA    |

|                                                                            | All clamps active, overvoltage reduced, current mode disabled | 2                      | 00                      | μA    |

|                                                                            | All clamps active, overvoltage reduced, current mode enabled  | 4                      | .5                      | μA    |

| REFIN Input Capacitance                                                    | WLCSP, internal reference buffer enabled                      | 5                      | 0                       | pF    |

| Internal Reference Buffer Output Current Limit                             | Reference buffer boost mode disabled                          | 3                      | .5                      | mA    |

| ·                                                                          | Reference buffer boost mode enabled                           | 1                      |                         | mA    |

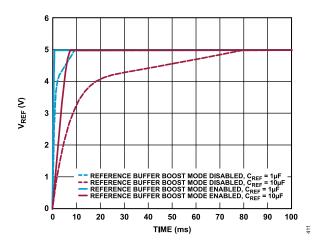

| Internal Reference Buffer Turn-On Time <sup>8</sup> (t <sub>REFBUF</sub> ) | V <sub>REF</sub> = 5 V                                        |                        |                         |       |

| Reference Buffer Boost Mode Disabled                                       | REF decoupling capacitor (C <sub>REF</sub> = 1 μF)            | 1                      | 0                       | ms    |

|                                                                            | C <sub>REF</sub> = 10 μF                                      | 8                      | 0                       | ms    |

| Reference Buffer Boost Mode Enabled                                        | C <sub>REF</sub> = 1 µF                                       | 1                      | .2                      | ms    |

|                                                                            | C <sub>REF</sub> = 10 μF                                      | 10                     |                         | ms    |

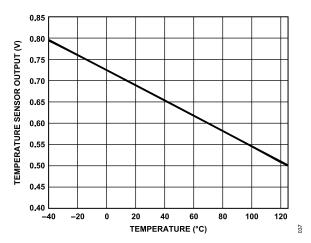

| FEMPERATURE SENSOR                                                         | 1                                                             |                        |                         |       |

| Temperature Sensor Voltage                                                 | T <sub>A</sub> = 25°C                                         | 6                      | 80                      | mV    |

| ·                                                                          | T <sub>A</sub> = 0°C                                          | 7                      | 25                      | mV    |

| Temperature Sensitivity                                                    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$          |                        | 1.8                     | mV/°0 |

| OVERVOLTAGE CLAMP                                                          |                                                               |                        |                         |       |

| External Series Resistance (R <sub>EXT</sub> ) <sup>9</sup>                | For stable clamp operation                                    |                        |                         |       |

| ( EAT)                                                                     | Overvoltage reduced current mode disabled                     |                        | 2000                    | Ω     |

|                                                                            | Overvoltage reduced current mode enabled                      |                        | 1000                    | Ω     |

| External Series Capacitance (C <sub>EXT</sub> ) <sup>9</sup>               | For stable clamp operation                                    | 500                    |                         | pF    |

| Clamp Input Current                                                        | For each active clamp                                         |                        | 5                       | mA    |

| Clamp Activation Voltage                                                   | '                                                             |                        | V <sub>REF</sub> + 0.55 | V     |

| Clamp Deactivation Voltage                                                 |                                                               | V <sub>REF</sub> + 0.1 | TILL STOCK              | V     |

| Input Clamping Voltage                                                     | Clamp current (I <sub>CLAMP</sub> ) = 5 mA                    |                        | <sub>REF</sub> + 0.2    | V     |

| Activation Time                                                            | CLAWIF)                                                       |                        | 0                       | ns    |

| Deactivation Time                                                          |                                                               | 1                      | 00                      | ns    |

| DIGITAL INPUTS                                                             |                                                               |                        |                         |       |

| Logic Levels                                                               |                                                               |                        |                         |       |

| Input Low Voltage (V <sub>IL</sub> )                                       |                                                               | -0.3                   | +0.3 × VIO              | V     |

| Input High Voltage (V <sub>IH</sub> )                                      |                                                               | 0.7 × VIO              | 3.6                     | V     |

| Input Current (I <sub>L</sub> )                                            |                                                               | -1                     | +1                      | μA    |

| Input Pin Capacitance                                                      |                                                               | 5                      |                         | pF    |

| DIGITAL OUTPUTS                                                            |                                                               |                        |                         | L.    |

| Conversion Mode Data Format                                                | Unipolar mode                                                 |                        | Straight binary         |       |

|                                                                            | Pseudobipolar mode                                            |                        | os complement           |       |

|                                                                            | , standorpoint mode                                           | I W                    | complainont             |       |

| Logic Levels                                                               | ·                                                             |                        |                         |       |

| Logic Levels Output Low Voltage (V <sub>OL</sub> )                         | Digital output current = +500 μA                              |                        | 0.4                     | V     |

analog.com Rev. B | 7 of 109

Table 1. (Continued)

| Parameter                                                                                                   | Test Conditions/Comments                   | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------|------|------|------|------|

| POWER REQUIREMENTS                                                                                          |                                            |      |      |      |      |

| AVDD to AGND                                                                                                |                                            | 2.7  |      | 5.5  | V    |

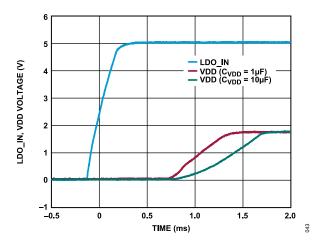

| LDO_IN to AGND                                                                                              | Internal LDO enabled                       | 2.4  |      | 5.5  | V    |

| · -                                                                                                         | Internal LDO disabled                      |      | 0    |      | V    |

| VDD to AGND                                                                                                 | Internal LDO disabled                      | 1.71 | 1.8  | 1.89 | V    |

| VIO to IOGND                                                                                                |                                            | 1.14 |      | 1.98 | V    |

| POWER SUPPLY CURRENT <sup>10</sup>                                                                          |                                            |      |      |      |      |

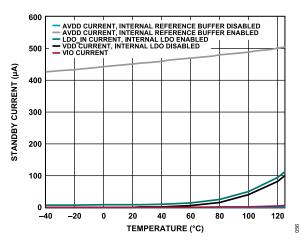

| Standby Current                                                                                             |                                            |      |      |      |      |

| AVDD                                                                                                        | AVDD = 5 V                                 |      |      |      |      |

| /WDD                                                                                                        | Internal reference buffer disabled         |      | 160  |      | nA   |

|                                                                                                             | Internal reference buffer enabled          |      | 450  |      | μA   |

| LDO_IN                                                                                                      | LDO_IN = 5 V                               |      | 430  |      | μΛ   |

| LDO_IN                                                                                                      | Internal LDO enabled                       |      | 9    |      |      |

|                                                                                                             | Internal LDO disabled                      |      | 0.3  |      | μA   |

| VDD                                                                                                         | -                                          |      | 0.3  |      | μA   |

| VDD                                                                                                         | VDD = 1.8 V, internal LDO disabled         |      | 4.5  |      |      |

|                                                                                                             | Internal reference buffer disabled         |      | 1.5  |      | μA   |

|                                                                                                             | Internal reference buffer enabled          |      | 5    |      | μA   |

| VIO                                                                                                         | VIO = 1.8 V                                | 250  |      |      | nA   |

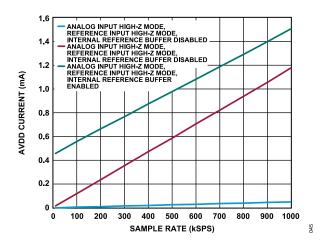

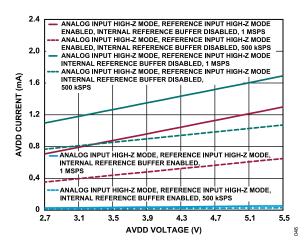

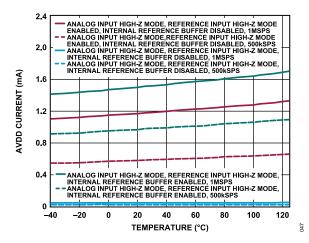

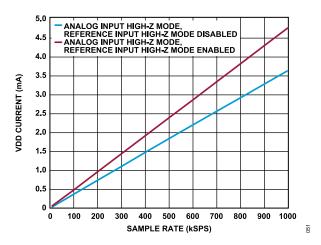

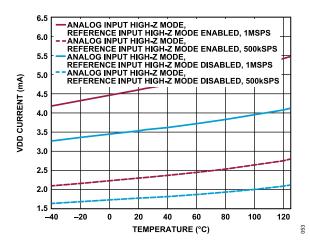

| AVDD Current (Conversion Mode)                                                                              | AVDD = 5 V                                 |      |      |      |      |

| Internal Reference Buffer Disabled, Reference<br>High-Z Mode Disabled, Analog Input High-Z Mode<br>Disabled | f <sub>S</sub> = 10 kSPS                   |      | 680  |      | nA   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                  |      | 26   |      | μA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                    |      | 52   |      | μA   |

| Internal Reference Buffer Disabled, Reference<br>High-Z Mode Enabled, Analog Input High-Z Mode<br>Enabled   | f <sub>S</sub> = 10 kSPS                   |      | 13   |      | μA   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                  |      | 0.64 | 0.73 | mA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                    |      | 1.28 | 1.46 | mA   |

| Internal Reference Buffer Enabled, Reference<br>High-Z Mode Enabled, Analog Input High-Z Mode<br>Enabled    | f <sub>S</sub> = 10 kSPS, REFIN = 4.096 V  |      | 450  |      | μA   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS, REFIN = 4.096 V |      | 1    | 1.14 | mA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS, REFIN = 4.096 V   |      | 1.5  | 1.78 | mA   |

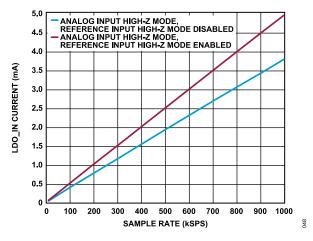

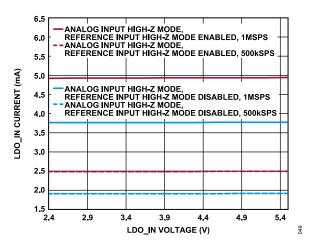

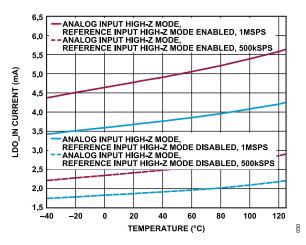

| LDO IN Current (Conversion Mode)                                                                            | LDO_IN = 5 V, internal LDO enabled         |      |      |      |      |

| Reference High-Z Mode Disabled, Analog Input<br>High-Z Mode Disabled                                        | f <sub>S</sub> = 10 kSPS                   |      | 52   |      | μA   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                  |      | 2    |      | mA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                    |      | 4    |      | mA   |

| Reference High-Z Mode Enabled, Analog Input<br>High-Z Mode Enabled                                          | f <sub>S</sub> = 10 kSPS                   |      | 64   |      | μA   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                  |      | 2.6  | 3.3  | mA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                    |      | 5.2  | 6.6  | mA   |

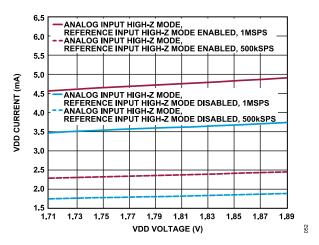

| VDD Current (Conversion Mode)                                                                               | VDD = 1.8 V, internal LDO disabled         |      |      |      |      |

| Reference High-Z Mode Disabled, Analog Input<br>High-Z Mode Disabled                                        | f <sub>S</sub> = 10 kSPS                   |      | 42   |      | μA   |

| •                                                                                                           | f <sub>S</sub> = 500 kSPS                  |      | 2    |      | mA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                    |      | 4    |      | mA   |

| Reference High-Z Mode Enabled, Analog Input<br>High-Z Mode Enabled                                          | f <sub>S</sub> = 10 kSPS                   |      | 53   |      | μA   |

analog.com Rev. B | 8 of 109

Table 1. (Continued)

| Parameter                                                                                                   | Test Conditions/Comments                                   | Min | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|------|------|------|

|                                                                                                             | f <sub>S</sub> = 500 kSPS                                  |     | 2.5  | 3.2  | mA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                                    |     | 5    | 6.4  | mA   |

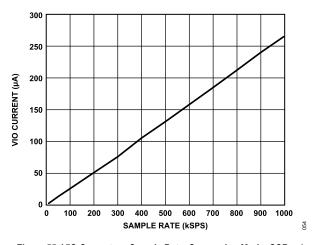

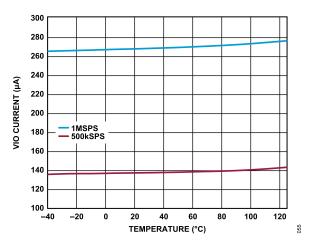

| VIO Dynamic Current                                                                                         | VIO = 1.8 V                                                |     |      |      |      |

| Register Configuration Mode                                                                                 | Streaming mode, SCK frequency (f <sub>SCK</sub> ) = 50 MHz |     | 125  |      | μA   |

| Conversion Mode                                                                                             | Status bits enabled                                        |     |      |      |      |

|                                                                                                             | f <sub>S</sub> = 10 kSPS                                   |     | 3.5  |      | μA   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                                  |     | 162  |      | μA   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                                    |     | 325  | 360  | μA   |

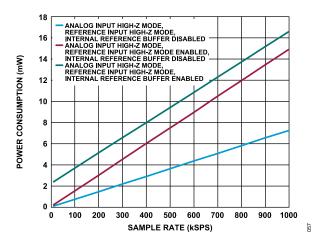

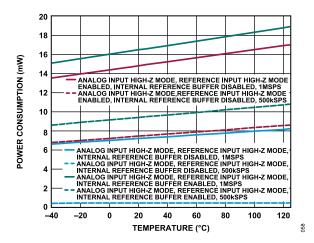

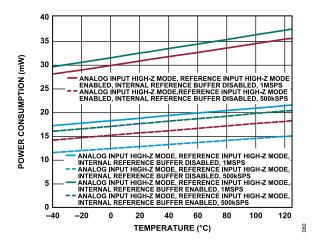

| POWER DISSIPATION <sup>10</sup>                                                                             | AVDD = 5 V, VIO = 1.8 V                                    |     |      |      |      |

| Standby Power Dissipation                                                                                   |                                                            |     |      |      |      |

| Internal LDO Disabled                                                                                       | VDD = 1.8 V, internal reference buffer disabled            |     | 4    |      | μW   |

|                                                                                                             | VDD = 1.8 V, internal reference buffer enabled             |     | 2.3  |      | mW   |

| Internal LDO Enabled                                                                                        | LDO IN = 5 V, internal reference buffer disabled           |     | 46   |      | μW   |

|                                                                                                             | LDO_IN = 5 V, internal reference buffer enabled            |     | 2.3  |      | mW   |

| Power Dissipation, Internal LDO Disabled                                                                    | LDO IN = AGND, VDD = 1.8 V                                 |     |      |      |      |

| Internal Reference Buffer Disabled, Reference<br>High-Z Mode Disabled, Analog Input High-Z Mode<br>Disabled | $f_S = 10 \text{ kSPS}$                                    |     | 85   |      | μW   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                                  |     | 4    |      | mW   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                                    |     | 8    |      | mW   |

| Internal Reference Buffer Disabled, Reference<br>High-Z Mode Enabled, Analog Input High-Z Mode<br>Enabled   | f <sub>S</sub> = 10 kSPS                                   |     | 170  |      | μW   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                                  |     | 8    | 9.8  | mW   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                                    |     | 16   | 19.5 | mW   |

| Internal Reference Buffer Enabled, Reference<br>High-Z Mode Enabled, Analog Input High-Z Mode<br>Enabled    | f <sub>S</sub> = 10 kSPS, REFIN = 4.096 V                  |     | 2.4  |      | mW   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS, REFIN = 4.096 V                 |     | 9.8  | 11.8 | mW   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS, REFIN = 4.096 V                   |     | 17.1 | 21.1 | mW   |

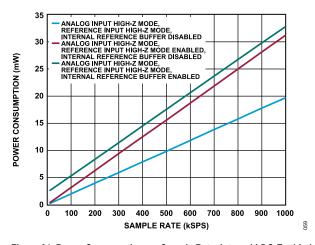

| Power Dissipation, Internal LDO Enabled                                                                     | LDO_IN = 5 V                                               |     |      |      |      |

| Internal Reference Buffer Disabled, Reference<br>High-Z Mode Disabled, Analog Input High-Z Mode<br>Disabled | $f_S = 10 \text{ kSPS}$                                    |     | 270  |      | μW   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                                  |     | 10.5 |      | mW   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                                    |     | 21   |      | mW   |

| Internal Reference Buffer Disabled, Reference<br>High-Z Mode Enabled, Analog Input High-Z Mode<br>Enabled   | f <sub>S</sub> = 10 kSPS                                   |     | 395  |      | μW   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS                                  |     | 16.5 | 20.5 | mW   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS                                    |     | 33   | 41.0 | mW   |

| Internal Reference Buffer Enabled, Reference<br>High-Z Mode Enabled, Analog Input High-Z Mode<br>Enabled    | f <sub>S</sub> = 10 kSPS, REFIN = 4.096 V                  |     | 2.6  |      | mW   |

|                                                                                                             | f <sub>S</sub> = 500 kSPS, REFIN = 4.096 V                 |     | 18.3 | 22.5 | mW   |

|                                                                                                             | f <sub>S</sub> = 1 MSPS, REFIN = 4.096 V                   |     | 34.1 | 42.6 | mW   |

| Autocycle Mode Power Dissipation                                                                            | LDO_IN = 5 V, internal LDO enabled, autocycle mode enabled |     |      |      |      |

|                                                                                                             | AC_CYC = 0x0                                               |     | 2.3  |      | mW   |

|                                                                                                             | AC_CYC = 0x7                                               |     | 0.2  |      | mW   |

analog.com Rev. B | 9 of 109

#### Table 1. (Continued)

| Parameter             | Test Conditions/Comments             | Min | Тур | Max  | Unit |

|-----------------------|--------------------------------------|-----|-----|------|------|

| TEMPERATURE RANGE     |                                      |     |     |      |      |

| Specified Performance | T <sub>MIN</sub> to T <sub>MAX</sub> | -40 |     | +125 | °C   |

- 1 See the Channel Configuration Options section for a detailed description of unipolar mode, pseudobipolar mode, and the channel pin assignment options.

- <sup>2</sup> IN+ and IN- represent the analog inputs connected to the positive and negative inputs of the AD4697/AD4698 ADC core via the internal multiplexer (see the Multiplexer section and Channel Configuration Options section).

- The analog input leakage current specification refers to the input current of the analog input pins during periods when the ADC is not performing conversions and the analog input voltage is already settled.

- Offset error and gain error specifications are taken with the offset and gain correction registers set to the default values, which correspond to no offset or gain correction.

See the Offset and Gain Correction section for more information.

- Offset error, gain error, and full-scale error drift utilize the box method across the full operating temperature range of -40°C to +125°C.

- <sup>6</sup> %FS is the percentage of the ADC full scale (see the Transfer Function section for a definition of full scale).

- The REFIN pin and internal reference buffer are only available on the WLCSP model of the AD4697/AD4698. All specifications and conditions regarding REFIN or the internal reference buffer are therefore only relevant for WLCSP model.

- The reference buffer turn-on time specification refers to the amount of time between the reference buffer being enabled and the REF voltage settling to 0.01% accuracy (see the Internal Reference Buffer section).

- 9 Rext and Cext refer to the resistor and capacitor, respectively, that make up the recommended external RC filters at the analog inputs (see the External RC Filter section).

- <sup>10</sup> For the power supply current and power dissipation specifications where analog input high-Z mode is enabled, analog input high-Z mode is set to be enabled for all channels. The power consumption scales with the percentage of conversions performed with analog input high-Z mode enabled.

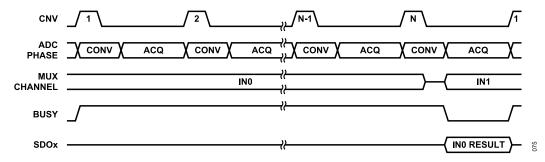

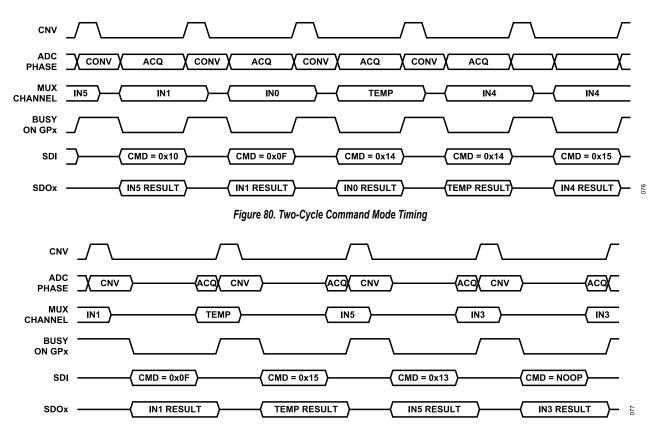

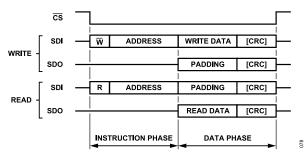

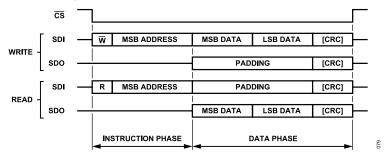

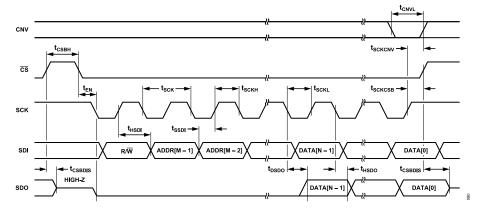

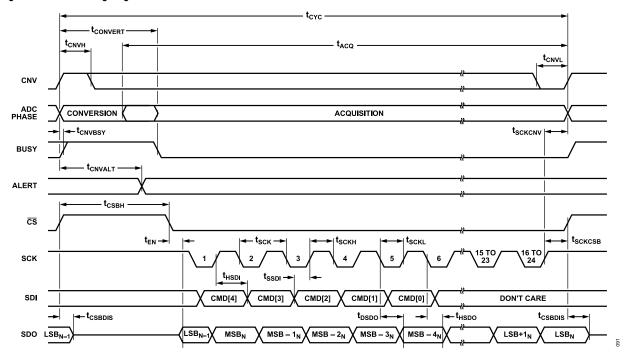

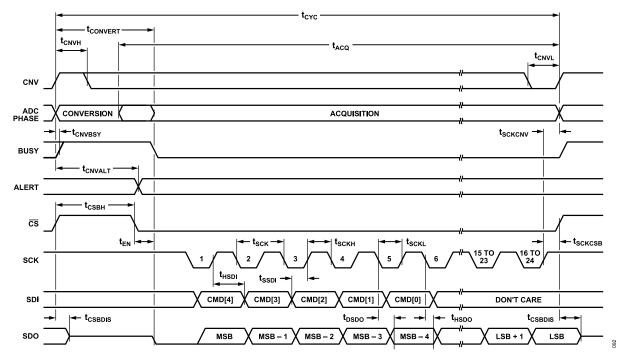

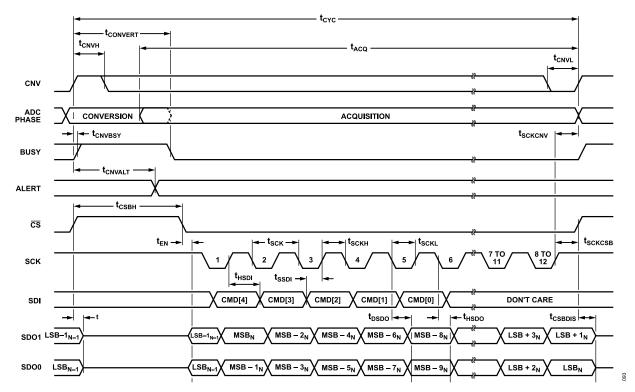

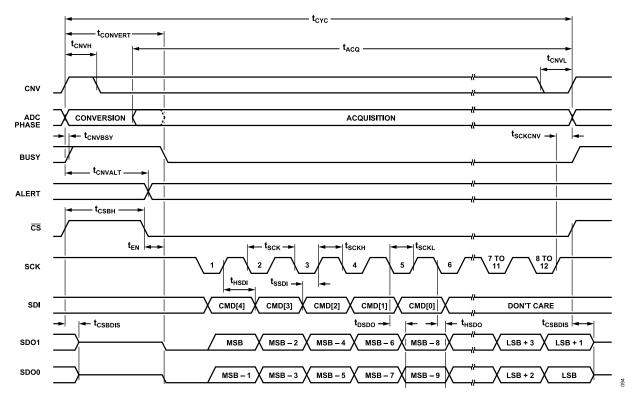

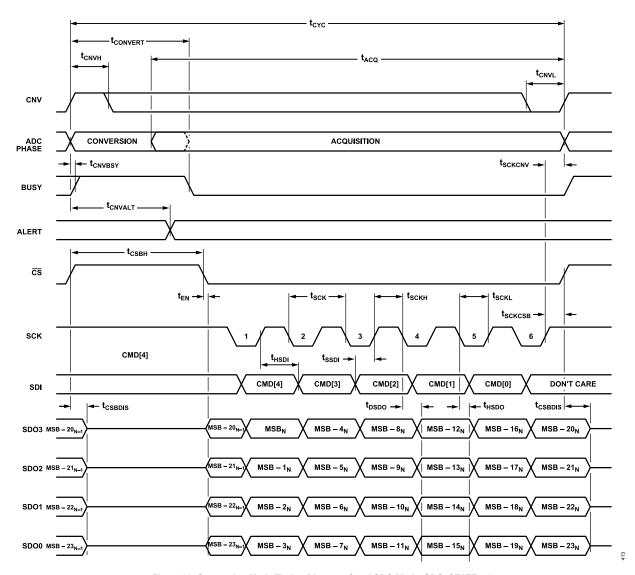

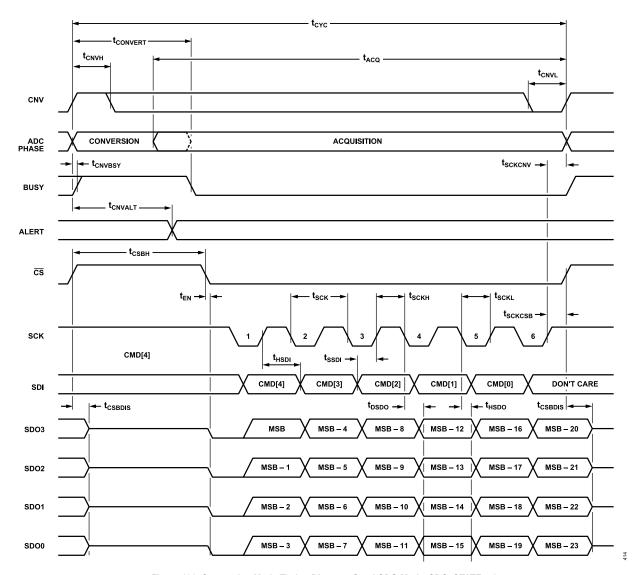

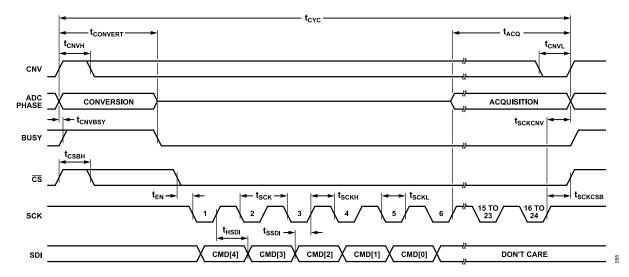

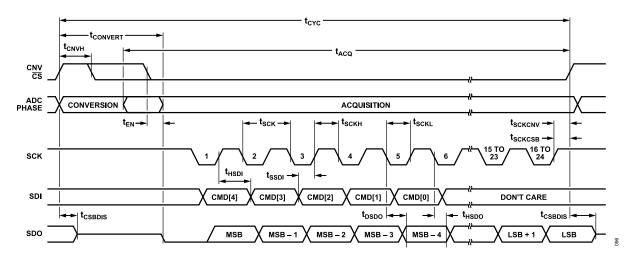

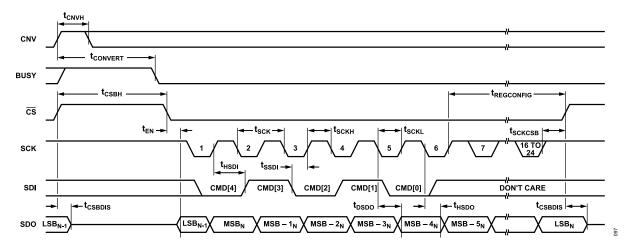

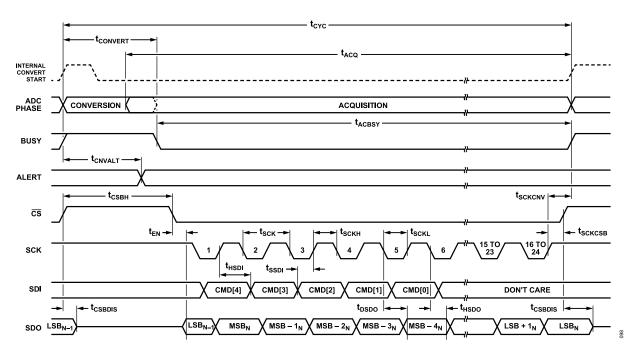

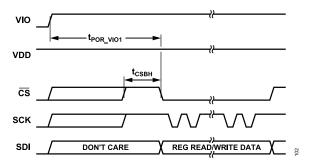

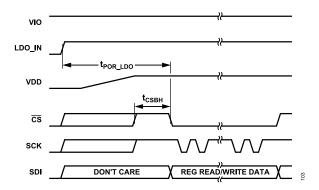

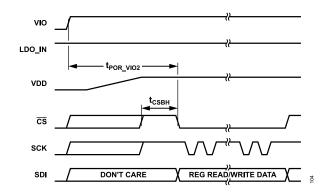

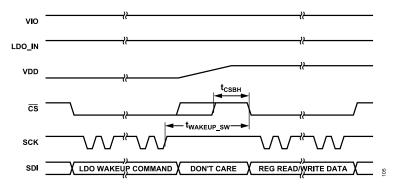

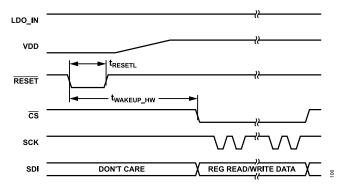

### **TIMING SPECIFICATIONS**

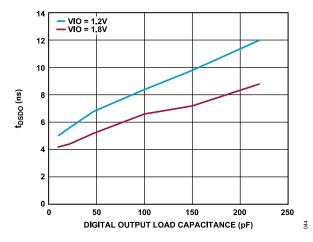

AVDD = 2.7 V to 5.5 V, LDO\_IN = 2.4 V to 5.5 V with internal LDO enabled, LDO\_IN = AGND with internal LDO disabled, VDD = 1.71 V to 1.89 V with internal LDO disabled, VIO = 1.14 V to 1.98 V, AGND = REFGND = IOGND = 0 V,  $V_{REF}$  = 2.4 V to 5.1 V,  $f_S$  = 1 MSPS for the AD4698,  $f_S$  = 500 kSPS for the AD4697, digital output load capacitance = 20 pF, autocycle mode disabled, no active overvoltage protection clamps, and  $T_A$  =  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise noted.

Table 2.

| Table 2.                                                                  |                      |      | - <u>-</u> - |      |      |  |  |  |  |  |  |

|---------------------------------------------------------------------------|----------------------|------|--------------|------|------|--|--|--|--|--|--|

| Parameter <sup>1</sup>                                                    | Symbol               | Min  | Тур          | Max  | Unit |  |  |  |  |  |  |

| Conversion Time                                                           | t <sub>CONVERT</sub> |      | 380          | 415  | ns   |  |  |  |  |  |  |

| Acquisition Time                                                          | t <sub>ACQ</sub>     |      |              |      |      |  |  |  |  |  |  |

| Two-Cycle Command Mode, Standard Sequencer, or Advanced Sequencer Enabled |                      |      |              |      |      |  |  |  |  |  |  |

| $f_S = 1 MSPS$                                                            |                      | 715  |              |      | ns   |  |  |  |  |  |  |

| $f_S = 500 \text{ kSPS}$                                                  |                      | 1715 |              |      | ns   |  |  |  |  |  |  |

| Single-Cycle Command Mode <sup>2</sup> Enabled                            |                      |      |              |      |      |  |  |  |  |  |  |

| CNV Period (Time Between Conversions)                                     | t <sub>CYC</sub>     |      |              |      |      |  |  |  |  |  |  |

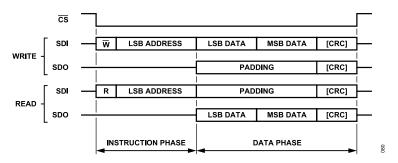

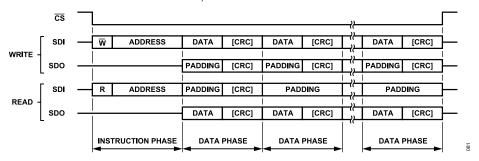

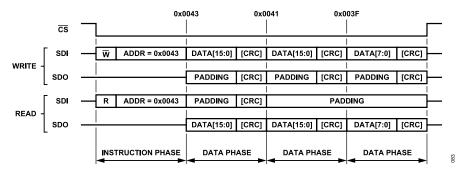

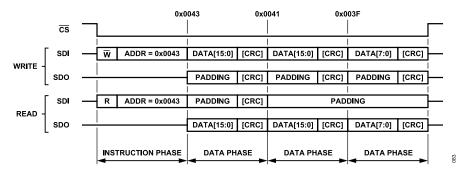

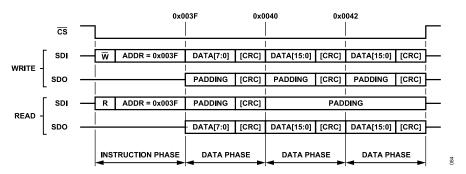

| f <sub>S</sub> = 1 MSPS, Autocycle Mode Disabled                          |                      | 1000 |              |      | ns   |  |  |  |  |  |  |