AVAILABLE

# **HDTV** Anti-Aliasing Filters with Triple-Input Mux

# **General Description**

The MAX7472/MAX7473 triple-channel anti-aliasing filters and buffers with triple-input mux are ideal for highdefinition (HD) and standard-definition (SD) television (TV) applications. Compatible with 1080i, 720p, 480p, and 480i scanning system standards as well as computer format signals, the MAX7472/MAX7473 support component video (Y PB PR, GsBR, and RGBHV) as well as composite (CVBS) and S-video (Y/C).

The MAX7472/MAX7473 limit the input bandwidth for anti-aliasing and out-of-band noise reduction prior to digital conversion by an ADC or video decoder. The frequency response of the MAX7472/MAX7473 can be continuously varied in 256 linear steps from below SD response to beyond HD response through an I<sup>2</sup>C interface. The adjustable cutoff frequency allows filter optimization for sampling rate and noise reduction. The MAX7472/MAX7473 also include 3:1 multiplexers for selection of three complete sets of video inputs through the I<sup>2</sup>C interface.

The MAX7472/MAX7473 drive a 2VP-P video signal into a standard 150 $\Omega$  load. The inputs are AC-coupled and the outputs can be either DC- or AC-coupled. The MAX7472 has a gain of 0dB and the MAX7473 has a gain of +6dB. Both devices are available in a 28-pin TQFN package and are fully specified over the uppercommercial (0°C to +85°C) temperature range.

HDTV (LCD, PDP, DLP, CRT) Set-Top Boxes Personal Video Recorders Home Theaters

Typical Operating Circuit appears at end of data sheet.

**Applications**

## Features

- Continuously Variable Anti-Aliasing Filter 5MHz to 34MHz in 256 Steps

- 3:1 Input Mux on Each Video Filter

- Supports All Standard Video and Computer Input Formats 480i, 480p, 720p, 1080i

- QVGA, VGA, SVGA, XGA, SXGA, UXGA Y PB PR, GsBR, RGBHV, Y/C, CVBS

- Accepts Any Input Sync Format Sync on Y, Sync on G, External Sync (Positive or Negative) Sync on All Channels

- Buffered Outputs Drive Standard 150Ω Video Load 0dB (MAX7472) +6dB (MAX7473)

- DC- or AC-Coupled Outputs

- Single +5V Analog and +3.3V Digital Supplies

- 5mW Power-Down Mode

- Lead (Pb)-Free 28-Pin TQFN Package

## **Ordering Information**

| PART          | PIN-PACKAGE | PKG CODE | BUFFER<br>GAIN (dB) |

|---------------|-------------|----------|---------------------|

| MAX7472UTI+   | 28 TQFN-EP* | T2855-8  | 0                   |

| MAX7473UTI+** | 28 TQFN-EP* | T2855-8  | +6                  |

|               |             |          | -                   |

Note: All devices are specified over the 0°C to +85°C operating temperature range.

+Indicates lead-free packaging.

\*EP = Exposed pad. \*\*Future product—contact factory for availability.

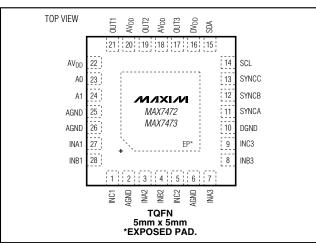

## Pin Configuration

## M/X/M

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND0.3V to +6V<br>DV <sub>DD</sub> to DGND0.3V to +4V |

|----------------------------------------------------------------------------|

| AGND to DGND0.3V to +0.3V                                                  |

| INA_, INB_, INC_ to AGND                                                   |

| 0.3V to the lower of $(AV_{DD} + 0.3V)$ and +6V                            |

| OUT_ to AGND0.3V to the lower of $(AV_{DD} + 0.3V)$ and +6V                |

| SYNC_, A_ to AGND                                                          |

| 0.3V to the lower of $(AV_{DD} + 0.3V)$ and +6V                            |

| SCL, SDA to DGND0.3V to + 6V                                               |

| Maximum Current into Any Pin                           |               |

|--------------------------------------------------------|---------------|

| (except AV <sub>DD</sub> , DV <sub>DD</sub> , and OUT) | ±50mA         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )  |               |

| 28-Pin TQFN (derate 34.5mW/°C above +70°C)             | 2758mW        |

| Operating Temperature Range                            | 0°C to +85°C  |

| Storage Temperature Range65                            | 5°C to +150°C |

| Junction Temperature                                   | +150°C        |

| Lead Temperature (soldering, 10s)                      | +300°C        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = 2.7V$  to 3.6V,  $R_{LOAD} = 150\Omega$  to AGND,  $C_{IN} = 0.1\mu$ F,  $T_A = 0^{\circ}$ C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.)

| PARAMETER                   | SYMBOL            | CONDITIONS                                                                    | MIN | ТҮР  | MAX  | UNITS   |

|-----------------------------|-------------------|-------------------------------------------------------------------------------|-----|------|------|---------|

| Filter Deesk and Deenenee   | 0                 | HD: f = 100kHz to 30MHz, relative to 100kHz<br>(Note 1)                       | -3  | -0.6 | +1   | dD      |

| Filter Passband Response    | Apb               | SD: f = 100kHz to 5.75MHz, relative to 100kHz (Note 2)                        |     | ±0.1 | ±1.0 | dB      |

| Filter Stopband Attenuation | ٨٥٦               | HD: f = 74MHz (Note 1)                                                        | 45  | 57   |      | dB      |

| Filter Stopband Attenuation | A <sub>SB</sub>   | SD: f = 27MHz (Note 2)                                                        |     | 63   |      | uв      |

|                             |                   | HD: 100kHz to 30MHz, relative to 100kHz<br>(Note 1)                           |     | 20   |      |         |

| Group-Delay Deviation       | Δt <sub>G</sub>   | SD: 100kHz to 5.75MHz, relative to 100kHz (Note 2)                            |     | 15   |      | ns      |

|                             |                   | HD: channel to channel, 100kHz to 2MHz<br>(Note 1)                            | 5   |      | - ns |         |

| Group-Delay Matching        |                   | SD: channel to channel, 100kHz to 500kHz<br>(Note 2)                          | 1.5 |      |      |         |

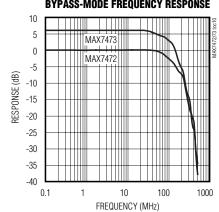

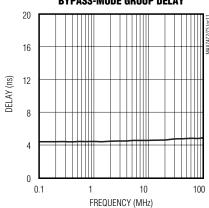

| Bypass Frequency Response   |                   | -3dB, bypass mode, independent of filter setting                              |     | 100  |      | MHz     |

| SD Differential Gain        | dG                | 5-step modulated staircase (Note 2)                                           |     | 0.25 |      | %       |

| SD Differential Phase       | dø                | 5-step modulated staircase (Note 2)                                           |     | 0.25 |      | Degrees |

| Signal-to-Noise Ratio       | SNR               | Output signal (2V <sub>P-P</sub> ) to RMS noise (100kHz<br>to 30MHz) (Note 1) |     | 69   |      | dB      |

| SD Line-Time Distortion     | HDIST             | Deviations in a line with an 18µs, 100 IRE bar,<br>1 line = 63.5µs (Note 2)   | 0.3 |      | %    |         |

| SD Field-Time Distortion    | V <sub>DIST</sub> | Deviations in 130 lines with 18µs, 100 IRE bars (Note 2)                      |     |      | 0.3  | %       |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = 2.7V \text{ to } 3.6V, R_{LOAD} = 150\Omega \text{ to AGND}, C_{IN} = 0.1\mu\text{F}, T_A = 0^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}$ . Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

| PARAMETER                                  | SYMBOL           | CONDITIO                            | NS       | MIN      | ТҮР        | MAX                  | UNITS |

|--------------------------------------------|------------------|-------------------------------------|----------|----------|------------|----------------------|-------|

| Oleana Ostilia a Tina                      | 1                | To 1% with 100 IRE step             | Positive |          | 350        |                      |       |

| Clamp Settling Time                        |                  | (Note 3)                            | Negative |          | 650        |                      | Н     |

| Minimum Functional Input Sync<br>Amplitude |                  |                                     |          | 125      |            |                      | mV    |

| Low-Frequency Gain                         |                  | T <sub>A</sub> = +25°C, MAX7472 (No | te 1)    | -0.5     | 0          | +0.5                 | dB    |

| Low-Frequency Gain                         |                  | T <sub>A</sub> = +25°C, MAX7473 (No | te 1)    | 5.5      | 6          | 6.5                  | uВ    |

| Low-Frequency Gain Matching                |                  | 100kHz                              |          |          | 0.05       |                      | dB    |

| Maximum Input Voltage<br>Amplitude         |                  | MAX7472<br>MAX7473                  |          |          | 2.4<br>1.2 |                      | Vp-p  |

| Maximum Output Voltage<br>Amplitude        |                  | DC to 30MHz                         |          |          | 2.4        |                      | VP-P  |

| Output Clamping Level Variation            |                  | (Notes 1, 4)                        |          |          |            | ±120                 | mV    |

| Mux Crosstalk                              | 1                |                                     |          |          | -80        |                      | dB    |

| Channel-to-Channel Isolation               |                  |                                     |          |          | 62         |                      | dB    |

| Power-Supply Rejection Ratio               | PSRR             |                                     |          |          | 50         |                      | dB    |

| DIGITAL INPUTS (A1, A0, SYNC               | _)               | ·                                   |          |          |            |                      |       |

| Input Logic High Voltage                   | VIH              |                                     |          | 2.0      |            |                      | V     |

| Input Logic Low Voltage                    | VIL              |                                     |          |          |            | 0.8                  | V     |

| Input Leakage Current                      | l <sub>IN</sub>  | $V_{IN} = 0$ to $DV_{DD}$           |          |          | ±1         | ±10                  | μA    |

| Input Capacitance                          | CIN              |                                     |          |          | 6          |                      | рF    |

| DIGITAL INPUTS (SDA, SCL)                  |                  |                                     |          |          |            |                      |       |

| Input Logic High Voltage                   | VIH              |                                     |          | 0.7 x D\ | /DD        |                      | V     |

| Input Logic Low Voltage                    | VIL              |                                     |          |          | 0.3        | 8 x DV <sub>DD</sub> | V     |

| Input Hysteresis                           | VHYST            | -                                   |          | 0.05 x D | VDD        |                      | V     |

| Input Leakage Current                      | l <sub>IN</sub>  | $V_{IN} = 0$ to $DV_{DD}$           |          |          | ±0.1       | ±10                  | μA    |

| Input Capacitance                          | CIN              |                                     |          |          | 6          |                      | pF    |

| DIGITAL OUTPUT (SDA)                       | 1                |                                     |          | 1        |            |                      |       |

| Output Logic Low Voltage                   | Vol              | I <sub>SINK</sub> = 3mA             |          |          |            | 0.4                  | V     |

| Tri-State Leakage Current                  | ١L               | $V_{IN} = 0$ to $DV_{DD}$           |          |          | ±0.1       | ±10                  | μA    |

| Tri-State Output Capacitance               | COUT             |                                     |          |          | 6          |                      | pF    |

| POWER REQUIREMENTS                         |                  | 1                                   |          |          |            |                      |       |

| Analog Supply Voltage Range                | AV <sub>DD</sub> |                                     |          | 4.75     | 5          | 5.25                 | V     |

| Digital Supply Voltage Range               | DVDD             |                                     |          | 2.7      | 3.3        | 3.6                  | V     |

| Analog Supply Current                      | IAVDD            | Normal operation, no load           |          |          | 180        | 200                  | mA    |

|                                            | 'AVDD            | Power-down mode, no load            | k        |          | 1          | 1.5                  |       |

| Digital Supply Current                     | IDVDD            |                                     |          |          | 25         |                      | μA    |

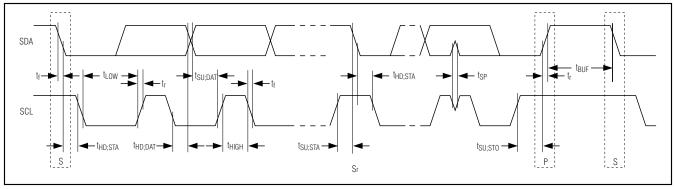

## **TIMING CHARACTERISTICS**

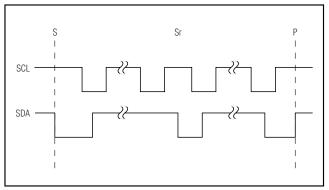

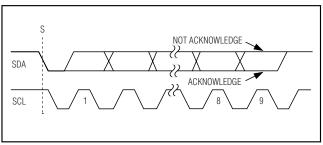

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = 2.7V \text{ to } 3.6V, T_A = 0^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Figure 1)

| PARAMETER                                                  | SYMBOL              | CONDITIONS                                            | MIN           | ТҮР | МАХ | UNITS |

|------------------------------------------------------------|---------------------|-------------------------------------------------------|---------------|-----|-----|-------|

| Serial Clock Frequency                                     | fSCL                |                                                       | 0             |     | 400 | kHz   |

| Bus Free Time Between STOP (P)<br>and START (S) Conditions | tBUF                |                                                       | 1.3           |     |     | μs    |

| Hold Time (Repeated) START (Sr)<br>Condition               | <sup>t</sup> HD;STA | After this period, the first clock pulse is generated | 0.6           |     |     | μs    |

| SCL Pulse-Width Low                                        | tLOW                |                                                       | 1.3           |     |     | μs    |

| SCL Pulse-Width High                                       | thigh               |                                                       | 0.6           |     |     | μs    |

| Setup Time for a Repeated START<br>(Sr) Condition          | <sup>t</sup> SU;STA |                                                       | 0.6           |     |     | μs    |

| Data Hold Time                                             | thd;dat             | (Note 5)                                              | 0             |     | 0.9 | μs    |

| Data Setup Time                                            | tsu;dat             |                                                       | 100           |     |     | ns    |

| Rise Time of Both SDA and SCL<br>Signals, Receiving        | tr                  |                                                       | 0             |     | 300 | ns    |

| Fall Time of Both SDA and SCL<br>Signals, Receiving        | tf                  |                                                       | 0             |     | 300 | ns    |

| Fall Time of SDA Signal,<br>Transmitting                   | tf                  | (Note 6)                                              | 20 +<br>0.1Cb |     | 300 | ns    |

| Setup Time for STOP (P) Condition                          | tsu;sto             |                                                       | 0.6           |     |     | μs    |

| Capacitive Load for Each Bus Line                          | Cb                  |                                                       |               |     | 400 | pF    |

| Pulse Width of Spikes Suppressed by the Input Filter       | tsp                 | (Note 7)                                              | 0             |     | 50  | ns    |

Note 1: The filter passband edge is set to code 255.

Note 2: The filter passband edge is set to code 40.

Note 3: 1H is the total line period, depending on the video standard. For NTSC, this is 63.5µs, for HDTV, the line period is 29.64µs.

Note 4: The clamp level is at the sync tip for signals with sync pulses, and is at the blanking level otherwise.

Note 5: A master device must provide a hold time of at least 300ns for the SDA signal (referred to V<sub>IL</sub> of the SCL signal) to bridge the undefined region of SCL's falling edge.

Note 6:  $C_b$  = total capacitance of one bus line in pF.  $t_R$  and  $t_F$  measured between 0.3V<sub>DD</sub> and 0.7V<sub>DD</sub>.

Note 7: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

Figure 1. 2-Wire Serial-Interface Timing Diagram

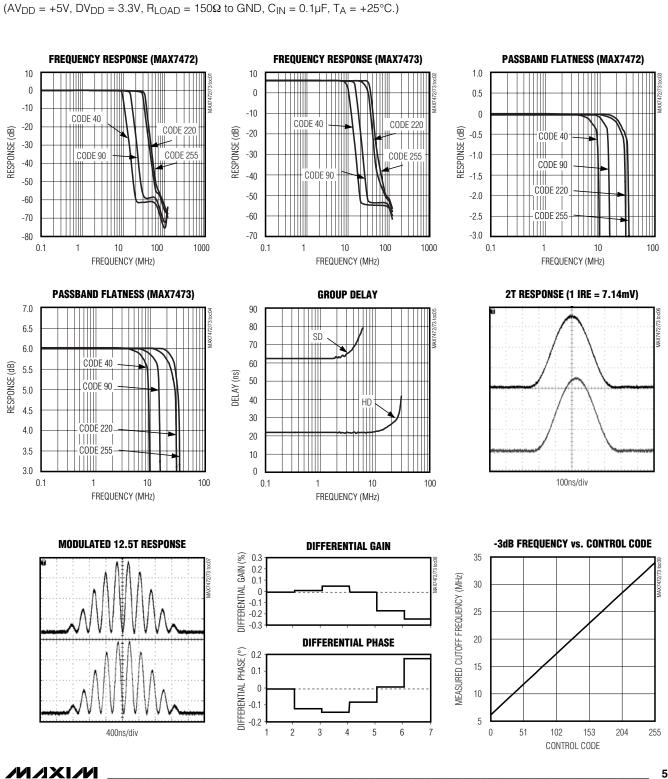

**Typical Operating Characteristics**

MAX7472/MAX7473

5

## **Pin Description**

| PIN          | NAME             | FUNCTION                                                                                                                                                          |

|--------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | INC1             | Channel C Input 1. AC-couple INC1 with a series 0.1µF capacitor.                                                                                                  |

| 2, 6, 25, 26 | AGND             | Analog Ground. Connect all AGND pins to the ground plane. See the <i>Power-Supply Bypassing and Layout Considerations</i> section.                                |

| 3            | INA2             | Channel A Input 2. AC-couple INA2 with a series 0.1µF capacitor.                                                                                                  |

| 4            | INB2             | Channel B Input 2. AC-couple INB2 with a series 0.1µF capacitor.                                                                                                  |

| 5            | INC2             | Channel C Input 2. AC-couple INC2 with a series 0.1µF capacitor.                                                                                                  |

| 7            | INA3             | Channel A Input 3. AC-couple INA3 with a series 0.1µF capacitor.                                                                                                  |

| 8            | INB3             | Channel B Input 3. AC-couple INB3 with a series 0.1µF capacitor.                                                                                                  |

| 9            | INC3             | Channel C Input 3. AC-couple INC3 with a series 0.1µF capacitor.                                                                                                  |

| 10           | DGND             | Digital Ground. See the Power-Supply Bypassing and Layout Considerations section.                                                                                 |

| 11           | SYNCA            | Channel A External Sync Input. Connect to ground if not used.                                                                                                     |

| 12           | SYNCB            | Channel B External Sync Input. Connect to ground if not used.                                                                                                     |

| 13           | SYNCC            | Channel C External Sync Input. Connect to ground if not used.                                                                                                     |

| 14           | SCL              | I <sup>2</sup> C-Compatible Serial Clock Input                                                                                                                    |

| 15           | SDA              | I <sup>2</sup> C-Compatible Serial Data Input/Output                                                                                                              |

| 16           | DV <sub>DD</sub> | Digital Power Supply. Bypass to DGND with a 0.1µF capacitor. See the <i>Power-Supply Bypassing and Layout Considerations</i> section.                             |

| 17           | OUT3             | Video Output 3. OUT3 can be either AC- or DC-coupled.                                                                                                             |

| 18, 20, 22   | AV <sub>DD</sub> | Analog Power Supply. Bypass each AV <sub>DD</sub> input to AGND using a 0.1µF capacitor. See the <i>Power-Supply Bypassing and Layout Considerations</i> section. |

# **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                               |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | OUT2 | Video Output 2. OUT2 can be either AC- or DC-coupled.                                                                                                                                                                                                                  |

| 21  | OUT1 | Video Output 1. OUT1 can be either AC- or DC-coupled.                                                                                                                                                                                                                  |

| 23  | AO   | Address Bit 0                                                                                                                                                                                                                                                          |

| 24  | A1   | Address Bit 1                                                                                                                                                                                                                                                          |

| 27  | INA1 | Channel A Input 1. AC-couple INA1 with a series 0.1µF capacitor.                                                                                                                                                                                                       |

| 28  | INB1 | Channel B Input 1. AC-couple INB1 with a series 0.1µF capacitor.                                                                                                                                                                                                       |

| _   | EP   | Exposed Pad. The exposed pad is located on the package bottom and is internally connected to AGND. Connect EP to the analog ground plane. Do not route any PC board traces under the package. See the <i>Power-Supply Bypassing and Layout Considerations</i> section. |

# **Detailed Description**

The MAX7472/MAX7473 are complete video anti-aliasing solutions ideal for fixed-pixel HDTV display technologies such as plasma and LCD, which digitize the input video signal and then scale the resolution to match the native pixel format of the display. With a software-selectable corner frequency ranging from 5MHz to 34MHz, the MAX7472/MAX7473 support both SD and HD video signals including 1080i, 720p, 480p, and 480i. Higher bandwidth computer resolution signals are also supported.

Integrated lowpass filters limit the analog video input bandwidth for anti-aliasing and out-of-band noise reduction prior to sampling by an ADC or video decoder. By allowing the corner frequency to be adjusted from below SD resolution to beyond HD resolutions in 256 steps, the filter's corner frequency can be optimized dynamically for a specific input video signal and the sampling frequency of the ADC or video decoder. The MAX7472/MAX7473 provide a filter-bypass mode to support applications requiring a passband greater than 34MHz.

An I<sup>2</sup>C interface allows a microcontroller to configure the MAX7472/MAX7473s' performance and functionality

including the mux, the clamp voltage, the filter's corner frequency, the sync source (internal/external), and filter bypassing.

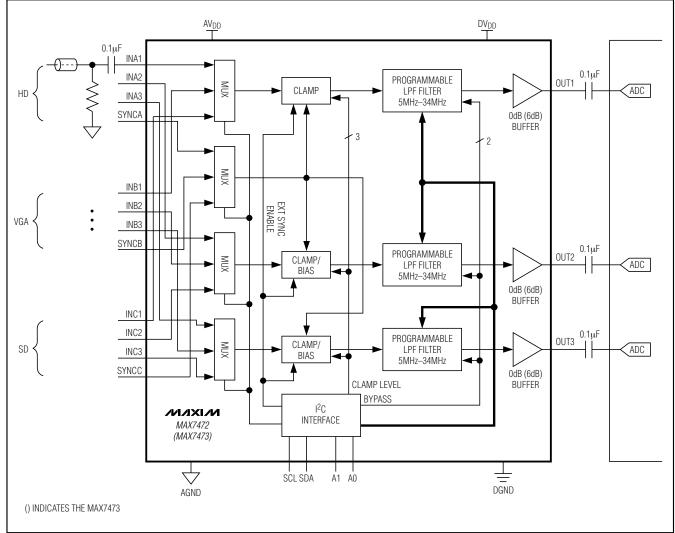

The *Typical Operating Circuit* shows the block diagram and typical external connections of the MAX7472/MAX7473.

## Sync Detector and Clamp Levels

The MAX7472/MAX7473 use a video clamp circuit to establish a DC offset for the incoming video signal after the AC-coupling capacitor. This video clamp sets the DC bias level of the circuit at the optimum operating point.

The MAX7472/MAX7473 support both internal and external sync detection. Selection of internal vs. external detection is achieved by programming the command byte (see Table 3). After extracting the sync information from channel 1 or an external sync (SYNCA, SYNCB, or SYNCC), the MAX7472/MAX7473 clamp the video signal during the sync tip portion of the video. Select one of two possible clamp levels according to the input signal format. Use the low level when the input signal contains sync information such as Y (luma) or CVBS signals. Use the high level for bipolar signals such as C (chroma) or PB/PR. See Table 1.

| Table 1. | Clamp | Levels |

|----------|-------|--------|

|----------|-------|--------|

| INPUT SIGNAL FORMAT                                   | CLAMP LEVEL |           |           |  |  |

|-------------------------------------------------------|-------------|-----------|-----------|--|--|

| INPUT SIGNAL FORMAT                                   | CHANNEL 1   | CHANNEL 2 | CHANNEL 3 |  |  |

| Y PB PR                                               | Low         | High      | High      |  |  |

| GsBR                                                  | Low         | High      | High      |  |  |

| CVBS Y C                                              | Low         | Low       | High      |  |  |

| Y P <sub>B</sub> P <sub>R</sub> (sync on all signals) | Low         | Low       | Low       |  |  |

| R G B H V                                             | High        | High      | High      |  |  |

## Component/Composite Selection

The MAX7472/MAX7473 accept component or composite inputs. The sync detection path provides an additional selectable color burst filter to improve sync detection.

#### External Sync Detection

When filtering a video signal without embedded sync information, such as computer formats (RGBHV) with separate sync signals, use the external sync mode (see Table 3) and apply the horizontal sync source to the SYNCA, SYNCB, or SYNCC pin. The sync detector determines when the clamp circuit is turned on.

The MAX7472/MAX7473 can detect positive or negative polarity external syncs with TTL logic levels. Use the I<sup>2</sup>C interface to program the polarity of the external sync signal.

#### **Filter**

The internal video filter delivers an optimized response with a steep transition band to achieve a wide passband along with excellent stopband rejection. In addition, the filter is optimized to provide an excellent timedomain response with low overshoot.

## Setting the Filter Frequency

The frequency response (-3dB cutoff frequency) of the filter in the MAX7472/MAX7473 can be varied from less than the SD passband to beyond the HD passband in 256 linear steps through the I<sup>2</sup>C interface. Use the command byte to write to the Frequency register followed by the 8-bit data word that corresponds to the desired frequency. See Table 6.

The Frequency register sets the -3dB point. Set this frequency accordingly to achieve the desired flat passband response.

## **Optimizing the Frequency Response**

Select the frequency according to the resolution of the video-signal format. High-definition signals require higher bandwidth and standard-definition signals require less bandwidth. The actual bandwidth contained in the video signal is a function of the visual resolution of the signal. This bandwidth is typically less than what is indicated by the format resolution (1080i, 720p, 480p, and 480i). For more information on this topic, see Application Note 750: *Bandwidth Versus Video Resolution* on the Maxim website (www.maximic.com). See Table 6.

The frequency response can be optimized to improve the overall performance. There are a number of considerations, one of the most important being the sampling rate of the subsequent ADC or video decoder in the system. In oversampled systems, the sampling rate is significantly more than the desired passband response. The extra frequency span between the passband and the sampling rate contains noise that can be eliminated by setting the corner frequency of the filter to just pass the desired bandwidth. This results in a higher signalto-noise ratio of the overall system.

#### Filter Bypass

The MAX7472/MAX7473 offer selectable filter bypassing that allows the input video signals to bypass the internal filters reaching the output buffers unfiltered. The filter-bypass mode is enabled/disabled through the command byte (see Table 3).

## **Output Buffer**

Each output buffer can drive a 2VP-P signal into a 150 $\Omega$  video load. The MAX7472/MAX7473 can drive a DC- or AC-coupled load. The output DC level is controlled to limit the DC voltage on the cable so that the blanking level of the video signal is always less than 1V, meeting the digital TV specification. As a result, output AC-coupling capacitors can be eliminated when driving a cable, thus eliminating the normal adverse effects caused by these capacitors such as line- and field-time distortion, otherwise known as droop. See the *Output Considerations* section for more information.

## Gain Options

The MAX7472 features an overall gain of 0dB, while the MAX7473 features an overall gain of +6dB. Use the +6dB option (MAX7473) when driving a back-matched cable. Use the 0dB option (MAX7472) when driving an ADC or video decoder with an input range the same as the input to the MAX7472. To add flexibility, the MAX7472 accepts input signals up to 2VP-P, twice the standard video-signal range.

## **Output Clamp Level**

The MAX7472/MAX7473 output can be DC- or AC-coupled. The nominal output clamp level in the DC-coupled case depends on the clamp voltage setting and can be determined according to Table 2.

## Table 2. Output Clamp Level

| CLAMP SETTING | OUTPUT CLAMP LEVEL (mV)<br>(typ) |

|---------------|----------------------------------|

| Low           | ±100                             |

| High          | ±100                             |

As shown in the *Sync Detector and Clamp Levels* section, the low clamp level is used for signals with sync information and determines the voltage level of the sync tip, while the high clamp level is used for signals without sync information and sets the blanking level.

The absolute voltage level of the output signal is relative to the output clamp level. A video signal containing sync information (i.e., CVBS or Y) is unipolar above the clamp level and conversely, a video signal without sync (i.e., P<sub>B</sub>, P<sub>R</sub>, or C) is bipolar around the clamp level.

#### **Multiplexers**

The MAX7472/MAX7473 provide four 3:1 multiplexers programmable through the I<sup>2</sup>C interface to select which of three separate channels (channels A, B, C) is to be connected to each video input. The fourth multiplexer is used in conjunction with external sync detection and determines which channel's external sync is to be connected to the external sync input.

See Table 3 and the *Serial Interface* section for more information on how to select a particular channel. After selecting a channel with a command byte, bits CS7 and CS6 of the Channel Selection register reflect the channel setting (Table 7).

#### **Power-Down Mode**

The MAX7472/MAX7473 include a power-down mode that reduces the supply current from 180mA (typ) to 1mA (typ) by powering down the analog circuitry. The I<sup>2</sup>C interface remains active allowing the device to return to full-power operation. The clamp settling time (see the *Electrical Characteristics* table) limits the wake-up time of the MAX7472/MAX7473. After exiting the power-down mode, the MAX7472/MAX7473 resume normal operation using the settings stored prior to power-down. The command byte controls the powerdown and wake-up modes (see Table 3). A software reset sets the Control/Status register to its default conditions. The Frequency register and the Channel Selection register are not affected.

## **Power-On Reset (POR)**

The MAX7472/MAX7473 include a power-on reset (POR) circuit that resets the internal registers and  $I^{2}C$  interface to their default condition (see Tables 4–7).

## **Serial Interface**

The MAX7472/MAX7473 feature an I<sup>2</sup>C-compatible, 2-wire serial interface consisting of a bidirectional serial data line (SDA) and a serial clock line (SCL). SDA and

SCL facilitate bidirectional communication between the MAX7472/MAX7473 and the master at rates up to 400kHz.

Once a command byte is written to the MAX7472/ MAX7473, the command interpreter changes the Control/Status register and the Channel Selection register accordingly. See the *Control/Status Register* and *Channel-Selection Register* sections for more information. The command interpreter also controls access to the Frequency register (see the *Command Byte (Write Cycle)* section).

The MAX7472/MAX7473 are transmit/receive slave-only devices, relying upon a master to generate a clock signal. The master (typically a microcontroller) initiates data transfer on the bus and generates SCL.

A master device communicates to the MAX7472/ MAX7473 by transmitting the proper address (see the *Slave Address* section) followed by a command and/or data words. Each transmit sequence is framed with a START (S) or REPEATED START (Sr) condition and a STOP (P) condition.

The SDA driver is an open-drain output, requiring a pullup resistor  $(2.4k\Omega \text{ or greater})$  to generate a logichigh voltage. Optional resistors  $(24\Omega)$  in series with SDA and SCL protect the device inputs from high-voltage spikes on the bus lines. Series resistors also minimize crosstalk and undershoot of the bus signals.

#### Bit Transfer

Each SCL rising edge transfers 1 data bit. Nine clock cycles are required to transfer the data into or out of the MAX7472/MAX7473. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high are read as control signals (see the *START and STOP Conditions* section). When the serial interface is inactive, SDA and SCL idle high.

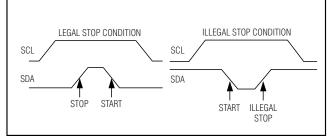

#### START and STOP Conditions

A master device initiates communication by issuing a START condition, a high-to-low transition on SDA with SCL high (Figure 2). The master terminates transmission by a STOP condition (see the *Acknowledge Bit (ACK)* and *Not-Acknowledge Bit (NACK)* section). A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 2). The STOP condition frees the bus. If a repeated START condition is generated instead of a STOP condition, the bus remains active. When a STOP condition or incorrect address is detected, the MAX7472/MAX7473 then ignore all communication on the I<sup>2</sup>C bus until the next START or REPEATED START condition, minimizing digital noise and feedthrough.

## Early STOP Conditions

The MAX7472/MAX7473 recognize a STOP condition at any point during transmission except when a STOP condition occurs in the same high pulse as a START condition (Figure 3). This condition is not a legal I<sup>2</sup>C format; at least one clock pulse must separate any START and STOP conditions. The MAX7472/MAX7473 discard any data received during a data transfer aborted by an early STOP condition.

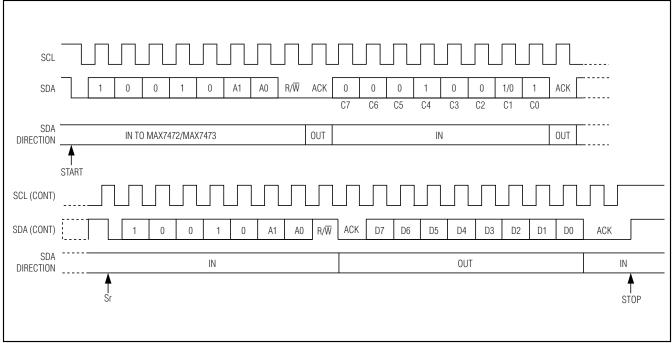

#### **REPEATED START (Sr) Conditions**

An Sr condition is used to indicate a change in direction of data flow (see the *Read Cycle* section). Sr can also be used when the bus master is writing to several I<sup>2</sup>C devices and does not want to relinquish control of the bus. The MAX7472/MAX7473 serial interface supports continuous write operations with (or without) an Sr condition separating them.

#### Acknowledge Bit (ACK) and Not-Acknowledge Bit (NACK)

Successful data transfers are acknowledged with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the MAX7472/MAX7473 (slave) generate acknowledge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low during the high period of the clock pulse (Figure 4). To generate a not acknowledge, the receiver allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse (ninth pulse) and leaves it high during the high period of the clock pulse. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the master should reattempt communication at a later time.

The MAX7472/MAX7473 generate an acknowledge bit when receiving an address or data by pulling SDA low during the ninth clock pulse. When transmitting data during a read, the MAX7472/MAX7473 do not drive SDA during the ninth clock pulse (i.e., the external pullups define the bus as a logic high) so that the receiver of the data can pull SDA low to acknowledge receipt of data.

#### Slave Address

A bus master initiates communication with a slave device by issuing a START condition followed by the 7-bit slave address (Figure 5). When idle, the MAX7472/MAX7473

Figure 2. START/STOP Conditions

Figure 3. Early STOP Conditions

Figure 4. Acknowledge and Not-Acknowledge Bits

wait for a START condition followed by its slave address. The serial interface compares each address bit by bit, allowing the interface to power down and disconnect from SCL immediately if an incorrect address is detected. After recognizing a START condition followed by the correct address, the MAX7472/MAX7473 are ready to accept or send data. The least significant bit (LSB) of the address byte (R/W) determines whether the master is writing to or reading from the MAX7472/MAX7473 (R/W = 0 selects a write condition, R/W = 1 selects a read condi-

# MAX7472/MAX7473

# **HDTV Anti-Aliasing Filters with Triple-Input Mux**

tion). After receiving the proper address, the MAX7472/MAX7473 (slave) issue an ACK by pulling SDA low for one clock cycle.

The MAX7472/MAX7473 slave address consists of 5 fixed bits A6–A2 (set to 10010) followed by 2 pin-programmable bits A1 and A0. The most significant address bit (A6) is transmitted first, followed by the remaining bits. Addresses A1 and A0 can also be driven dynamically if required, but the values must be stable when they are expected in the address sequence.

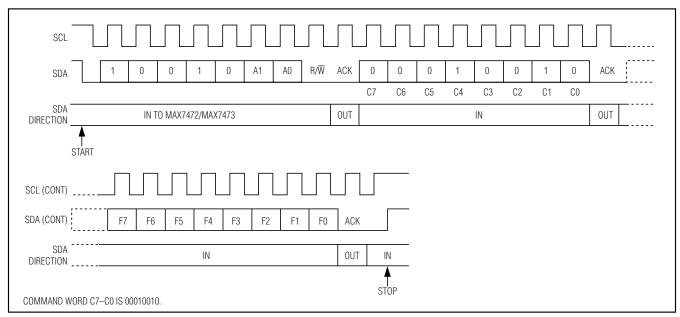

#### Command Byte (Write Cycle)

A write cycle begins with the bus master issuing a START condition followed by 7 address bits (Figure 5) and a write bit (R/W = 0). After successfully receiving

its address, the MAX7472/MAX7473 (slave) issue an ACK. The MAX7472/MAX7473 recognize the next byte after a successfully received address as the command byte (Table 3).

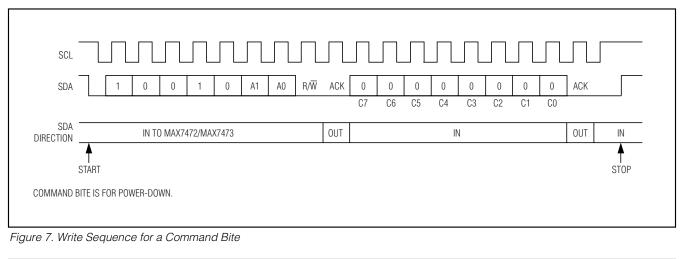

Use the command byte to configure the MAX7472/ MAX7473. While most of the commands listed in Table 3 modify the functionality of the MAX7472/ MAX7473, some commands prepare the device for further data transfers (see the *Control/Status Register*, *Frequency Register*, and *Channel-Selection Register* sections.) When the write cycle is prematurely aborted, the register is not updated. Figures 6 and 7 show examples of write sequences.

Figure 5. Slave-Address Byte Definition

Figure 6. Write Sequence to Update the Frequency Register

#### COMMAND BYTE: INDIVIDUAL BIT DEFINITIONS DESCRIPTION C7 C6 C4 C2 C1 C0 C5 СЗ Power-down. Wake-up; resume normal operation using the frequency/status previously stored (unless power has been cycled). Set clamp voltage level for IN1 to low. Set clamp voltage level for IN1 to high. Set clamp voltage level for IN2 to low. Set clamp voltage level for IN2 to high. Set clamp voltage level for IN3 to low. Set clamp voltage level for IN3 to high. Select component input, color-burst filter disabled. Select composite input, color-burst filter enabled. Select internal svnc. Select external sync. Select positive polarity for the external sync. Select negative polarity for the external sync. Enable filters. Disable filters. Enter bypass mode. Reset status to the default status as outlined in the Control/Status register Ο table. This command does not affect the Frequency register and the Channel Selection register. Request reading the Control/Status register. The interface expects an Sr condition to follow with address and read/write set to read so that data can be driven onto the bus. Load the Frequency register with the data byte following the command word. Request reading the Frequency register. The interface expects an Sr condition to follow with address and read/write set to read so that data can be driven onto the bus. Select Input A Select Input B. Select Input C Request reading the Channel Selection register. The interface expects an Sr condition to follow with address and read/write set to read so that data can be driven onto the bus.

## Table 3. Command Byte Definition

MAX7472/MAX7473

Figure 8. Basic Read Sequence

#### Read Cycle

In read mode (R/W = 1), the MAX7472/MAX7473 write the contents of the Status, Channel Selection, or Frequency register to the bus. When the command byte indicates a read operation of either the Status or the Frequency register, the serial interface expects an Sr condition to follow the command byte. After sending an Sr, the master sends the MAX7472/MAX7473 slave address byte followed by the R/W bit (set to 1 to indicate a read). The slave device (MAX7472/MAX7473) generates an ACK for the second address word and immediately after the ACK clock pulse, the direction of data flow reverses. The slave (MAX7472/MAX7473) then transmits 1 byte of data containing the value of the register that was selected in the command byte. Figure 8 shows a basic read sequence.

**Note:** To read the contents of the Status, Channel Selection, or Frequency register, the master must first write a command byte, requesting to read the Status, Channel Selection, or Frequency register.

MAX7472/MAX7473

## Control/Status Register

The MAX7472/MAX7473 store their status in an 8-bit register that can be read back by the master. The individual bits of the Control/Status register are summarized in Tables 4 and 5. The power-on default value of this register is 03h.

## Table 4. Control/Status Register

| CONTROL/STATUS REGISTER |    |    |    |    |    |    |    |

|-------------------------|----|----|----|----|----|----|----|

| S7                      | S6 | S5 | S4 | S3 | S2 | S1 | S0 |

## Frequency Register

The frequency response (-3dB passband edge) of the MAX7472/MAX7473 can be continuously varied in 256 linear steps by changing the codes in the Frequency register (Table 6). See the *Command Byte* (*Write Cycle*) section for a write sequence to update the Frequency register.

## Table 5. Control/Status Register Bit Description

| BIT | DESCRIPTION                                                                               |

|-----|-------------------------------------------------------------------------------------------|

| S7  | 0 = component input signal selected (default).<br>1 = composite input signal selected.    |

| S6  | 0 = internal sync enabled (default).<br>1 = external sync enabled.                        |

| S5  | 0 = external sync: positive polarity (default).<br>1 = external sync: negative polarity.  |

| S4  | 0 = normal operation mode (default).<br>1 = power-down mode.                              |

| S3  | 0 = filters enabled (default).<br>1 = bypass mode—no filtering.                           |

| S2  | 0 = clamp voltage for IN1 set to low (default).<br>1 = clamp voltage for IN1 set to high. |

| S1  | 0 = clamp voltage for IN2 set to low.<br>1 = clamp voltage for IN2 set to high (default). |

| SO  | 0 = clamp voltage for IN3 set to low.<br>1 = clamp voltage for IN3 set to high (default). |

## Table 6. Suggested Frequency Register Setting for Various Video-Signal Formats

| VIDEO-SIGNAL<br>FORMAT             | F7 | F6 | F5 | F4 | F3 | F2 | F1 | F0 | CODE NUMBER | APPROXIMATE<br>FREQUENCY<br>(-3dB) (MHz) |

|------------------------------------|----|----|----|----|----|----|----|----|-------------|------------------------------------------|

| Standard-Definition<br>Interlaced  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 40          | 10                                       |

| Standard-Definition<br>Progressive | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 90          | 15                                       |

| High-Definition Low<br>Bandwidth   | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 220         | 30                                       |

| High-Definition High<br>Bandwidth  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 255         | 34 (default)                             |

|     |     | CHANN | NEL-SELEC | CTION REC | SISTER |     |     | DESCRIPTION                   |

|-----|-----|-------|-----------|-----------|--------|-----|-----|-------------------------------|

| CS7 | CS6 | CS5   | CS4       | CS3       | CS2    | CS1 | CS0 | DESCRIPTION                   |

| 0   | 0   | Х     | Х         | Х         | Х      | Х   | Х   | Channel A selected (default). |

| 0   | 1   | Х     | Х         | Х         | Х      | Х   | Х   | Channel B selected.           |

| 1   | 0   | Х     | Х         | Х         | Х      | Х   | Х   | Channel C selected.           |

# Table 7. Channel-Selection Register

X = Don't care.

## Channel-Selection Register

The MAX7472/MAX7473 store channel selection in an 8-bit register that can be read back by the master. The individual bits of the Channel Selection register are summarized in Table 7. The power-on default selects channel A.

*I<sup>2</sup>C Compatibility* The MAX7472/MAX7473 are compatible with existing I<sup>2</sup>C systems supporting standard I<sup>2</sup>C 8-bit communications. The general call address is ignored, and CBUS formats are not supported. The devices' address is compatible with 7-bit I<sup>2</sup>C addressing protocol only. Ten-bit address formats are not supported.

## \_Applications Information

## **Input Considerations**

Use 0.1µF ceramic capacitors to AC-couple the inputs. The input cannot be DC-coupled. The internal clamp circuit stores a DC voltage across the input capacitors to obtain the appropriate output DC voltage level. Increasing the value of these capacitors to improve line-time distortion is not necessary due to the extremely low input leakage current yielding a very low line-time distortion performance.

The MAX7472/MAX7473 provide a high input impedance to allow a nonzero source impedance to be used such as when the input is connected directly to a backmatched video cable, ensuring the external resistance determines the termination impedance.

## **Output Considerations**

The MAX7472/MAX7473 outputs can be DC- or ACcoupled. The MAX7473, with +6dB gain, is typically connected to a 75 $\Omega$  series back-match resistor followed by the video cable. Because of the inherent divide-by-two of this configuration, the blanking level of the video signal is always less than 1V, which complies with digital TV requirements.

The MAX7472, with 0dB gain, is typically connected to an ADC or video decoder. This can be a DC or AC connection. If a DC connection is used, ensure that the DC input requirements of the ADC or video decoder are compatible.

When using an AC connection, choose an AC-coupling capacitor value that ensures that the lowest frequency content in the video signal is passed and the line-time distortion is kept within desired limits. The selection of this value is a function of the input impedance and more importantly, the input leakage of the circuit being driven. Use a video clamp to reestablish the DC level if not already included in the subsequent circuit.

The outputs of the MAX7472/MAX7473 are fully protected against short-circuit conditions either to ground or to the positive supply of the device.

## Power-Supply Bypassing and Layout Considerations

The MAX7472/MAX7473 operate from a single +5V analog supply and +3.3V digital supply. Bypass each AV<sub>D</sub> to AGND with a 0.1µF capacitor with an additional 1µF capacitor in parallel for low-frequency decoupling. Determine the proper power-supply bypassing necessary by taking into account the desired disturbance level tolerable on the output, the power-supply rejection of the MAX7472/MAX7473, and the amplitude and frequency of the disturbance signals present in the vicinity of the MAX7472/MAX7473. Use an extensive ground plane to ensure optimum performance. The three AV<sub>D</sub> inputs (pins 18, 20, and 22) that supply the individual channels can be connected together and bypassed as one provided the components are close to the pins. Bypass DVDD to DGND with a 0.1µF capacitor. Connect all ground pins to a low-impedance ground plane as close to the device as possible.

Place the input termination resistors as close to the device as possible. Alternatively, the terminations can be placed further from the device if the PC board traces are designed to be a controlled impedance of 75 $\Omega$ . Minimize parasitic capacitance as much as possible to avoid performance degradation in the upper frequency range possible with the MAX7472/MAX7473.

Refer to the MAX7472/MAX7473 evaluation kit for a proven PC board layout.

## **Exposed Pad and Heat Dissipation**

The MAX7472/MAX7473 TQFN package provides an exposed pad on the bottom side of the package. This pad is electrically connected to AGND and must be soldered to the ground plane for proper thermal conductivity. Do not route any PC board traces under the package.

The MAX7472/MAX7473 typically dissipate 900mW of power; therefore, pay attention to heat dispersion. Use at least a two-layer board with a good ground plane. To maximize heat dispersion, place copper directly under the MAX7472/MAX7473 package to match the outline of the plastic encapsulated area. Repeat the same with the bottom ground plane layer and place as many vias as possible connecting the top and bottom layers to thermally connect to the ground plane.

Maxim has evaluated a four-layer board using FR-4 material and 1oz copper with equal areas of metal on the top and bottom side coincident with the plastic encapsulated areas of the package. The two middle layers are used as power and ground planes. The board has 21, 15-mil, plated-through via holes between top, bottom, and ground plane layers. Thermocouple measurements confirm device temperatures to be safely within maximum limits.

\_Typical Operating Circuit

Chip Information

PROCESS: BICMOS

# **Revision History**

Pages changed at Rev 1: 1, 2, 10, 17, 19

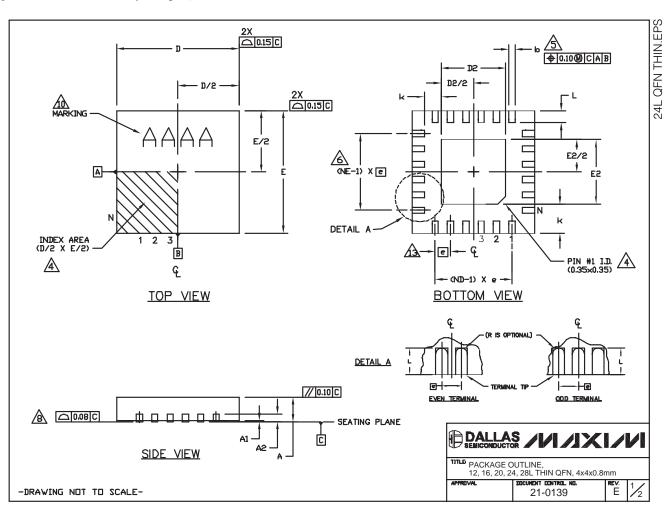

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

# **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

|                                                                                      |                                                                                                                                                         |                                                                                                                                                      |                                                                                                                           |                                                                                                                                        |                                                                                                                                      | DIWF                                                                                                                              | INSIE                                                                                                          | IN2                                                                   |                                                                                             |                                                                            |                                        |                                                          |                                                            |                                |                             |      | E                  | XPUS         | εIJ          | PAU              |              |        | UN2  |            |  |    |  |    |  |               |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------|------------------------------------------------------------|--------------------------------|-----------------------------|------|--------------------|--------------|--------------|------------------|--------------|--------|------|------------|--|----|--|----|--|---------------|

| PKG                                                                                  | 12                                                                                                                                                      | <u>2L 4x</u>                                                                                                                                         | :4                                                                                                                        | 16                                                                                                                                     | L 4x                                                                                                                                 | 4                                                                                                                                 | 20                                                                                                             | L 4x                                                                  | 4                                                                                           | 2                                                                          | 4L 4×                                  | (4                                                       | 28                                                         | <u>3L 4×</u>                   | <b>&lt;</b> 4               | Р    | PKG.               |              | D2           |                  | D2           |        | D2   | 2          |  | D2 |  | E5 |  | DOWN<br>BONDS |

| REF.                                                                                 | MIN.                                                                                                                                                    | NDM.                                                                                                                                                 | MAX.                                                                                                                      | MIN.                                                                                                                                   | NDM.                                                                                                                                 | MAX.                                                                                                                              | MIN.                                                                                                           | NDM.                                                                  | MAX.                                                                                        | MIN.                                                                       | NDM.                                   | MAX.                                                     | MIN.                                                       | NDM.                           | MAX.                        | Ċ    | CUDES              | MIN.         | NDM.         | MAX.             | MIN.         | NDM.   | MAX. | ALLOV      |  |    |  |    |  |               |

| A                                                                                    | 0.70                                                                                                                                                    | 0.75                                                                                                                                                 | 0.80                                                                                                                      | 0.70                                                                                                                                   | 0.75                                                                                                                                 | 0.80                                                                                                                              | 0.70                                                                                                           | 0.75                                                                  | 0.80                                                                                        | 0.70                                                                       | 0.75                                   | 0.80                                                     | 0.70                                                       | 0.75                           | 0.80                        | Ľ    | T1244-3            | 1.95         | 2.10         | 2.25             | 1.95         | 2.10   | 2.25 | YES        |  |    |  |    |  |               |

| A1                                                                                   |                                                                                                                                                         | 0.02                                                                                                                                                 | 0.05                                                                                                                      | 0.0                                                                                                                                    | 20,0                                                                                                                                 | 0.05                                                                                                                              | 0,0                                                                                                            | 0.02                                                                  | 0.05                                                                                        | 0,0                                                                        | 0.02                                   | 0.05                                                     | 0.0                                                        | 0.02                           | 0.05                        |      | T1244-4            | 1.95         | 2.10         | 2.25             | 1.95         | 2.10   | 2.25 | ND         |  |    |  |    |  |               |

| 82                                                                                   |                                                                                                                                                         | .20 RE                                                                                                                                               | 1                                                                                                                         |                                                                                                                                        | 20 RE                                                                                                                                |                                                                                                                                   |                                                                                                                | 20 RE                                                                 |                                                                                             |                                                                            | .20 RE                                 |                                                          |                                                            | 20 RE                          |                             |      | T1644-3            | 1.95         | 2.10         | 2.25             | 1.95         | 2.10   | 2.25 | YES        |  |    |  |    |  |               |

| b                                                                                    | 0.25                                                                                                                                                    |                                                                                                                                                      | 0.35                                                                                                                      | 0.25                                                                                                                                   | 0.30                                                                                                                                 | 0.35                                                                                                                              | 0.20                                                                                                           |                                                                       | 0.30                                                                                        | 0.18                                                                       | 0.23                                   |                                                          |                                                            | 0.20                           | 0.25                        | l H- | T1644-4            | 1.95         | 2.10         | 2.25             | 1.95         | 2.10   | 2.25 | ND         |  |    |  |    |  |               |

| D                                                                                    | 3,90                                                                                                                                                    | 4.00                                                                                                                                                 | 4,10                                                                                                                      | 3.90                                                                                                                                   | 4.00                                                                                                                                 | 4.10                                                                                                                              | 3.90                                                                                                           | 4.00                                                                  | 4.10                                                                                        | 3.90                                                                       | 4.00                                   | 4.10                                                     | 3.90                                                       | 4.00                           | 4.10                        |      | T2044-2            | 1.95         | 2.10         | 2.25             | 1.95         | 2.10   | 2.25 | YES        |  |    |  |    |  |               |

| E                                                                                    |                                                                                                                                                         | 4.00                                                                                                                                                 | 4.10                                                                                                                      | 3.90                                                                                                                                   | 4.00                                                                                                                                 | 4.10                                                                                                                              | 3.90                                                                                                           |                                                                       | 4.10                                                                                        | 3.90                                                                       | 4.00                                   | 4.10                                                     |                                                            | 4.00                           | 4.10                        |      | T2044-3            | 1.95         | 2.10         | 2.25             | 1.95         | 2.10   | 2.25 | ND         |  |    |  |    |  |               |

| e<br>k                                                                               | 0.25                                                                                                                                                    | 0.80 BS                                                                                                                                              | <u>s</u> t.                                                                                                               | 0.25                                                                                                                                   | 65 BS                                                                                                                                | -                                                                                                                                 | 0.25                                                                                                           | 50 BS                                                                 | L.<br>                                                                                      | 0.25                                                                       | ).50 BS                                |                                                          | 0.25                                                       | 40 BS                          |                             |      | T2444-2<br>T2444-3 | 1.95<br>2.45 | 2.10<br>2.60 | 2.25             | 1.95<br>2.45 | 2.10   | 2.25 | YES<br>YES |  |    |  |    |  |               |

| <u> </u>                                                                             | 0.45                                                                                                                                                    |                                                                                                                                                      | 0.65                                                                                                                      | 0.45                                                                                                                                   | 0.55                                                                                                                                 | 0.65                                                                                                                              |                                                                                                                | 0.55                                                                  | 0.65                                                                                        | 0.30                                                                       | 0.40                                   | 0.50                                                     | 0.30                                                       | 0.40                           | 0.50                        |      | T2444-3            | 2.45         | 2.60         | 2.63             | 2.45         | 2.60   | 2.63 |            |  |    |  |    |  |               |

| N                                                                                    | 0.40                                                                                                                                                    | 12                                                                                                                                                   | 1000                                                                                                                      | 0.40                                                                                                                                   | 16                                                                                                                                   | 0.00                                                                                                                              | 0.40                                                                                                           | 20                                                                    | 0.00                                                                                        | 0.00                                                                       | 24                                     | 1 0.00                                                   |                                                            | 28                             | 0.00                        |      | T2844-1            | 2.50         | 2.60         |                  | 2.50         | 2.60   |      |            |  |    |  |    |  |               |

| ND                                                                                   |                                                                                                                                                         | 3                                                                                                                                                    |                                                                                                                           |                                                                                                                                        | 4                                                                                                                                    |                                                                                                                                   |                                                                                                                | 5                                                                     |                                                                                             |                                                                            | 6                                      |                                                          |                                                            | 7                              |                             |      |                    | 21010        | 2.00         |                  | 2.00         |        |      | 1          |  |    |  |    |  |               |

| NE                                                                                   |                                                                                                                                                         | 3                                                                                                                                                    |                                                                                                                           |                                                                                                                                        | 4                                                                                                                                    |                                                                                                                                   |                                                                                                                | 5                                                                     |                                                                                             |                                                                            | 6                                      |                                                          |                                                            | 7                              |                             |      |                    |              |              |                  |              |        |      |            |  |    |  |    |  |               |